# **Aalborg Universitet**

# Current Limiting Control with Enhanced Dynamics of Grid-Forming Converters during **Fault Conditions**

Taul, Mads Graungaard: Wang, Xiongfei: Davari, Pooya; Blaabjerg, Frede

Published in:

IEEE Journal of Emerging and Selected Topics in Power Electronics

DOI (link to publication from Publisher): 10.1109/JESTPE.2019.2931477

Creative Commons License CC BY 4.0

Publication date: 2020

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Taul, M. G., Wang, X., Davari, P., & Blaabjerg, F. (2020). Current Limiting Control with Enhanced Dynamics of Grid-Forming Converters during Fault Conditions. *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 8(2), 1062-1073. Article 8779657. https://doi.org/10.1109/JESTPE.2019.2931477

# **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 06, 2025

# Current Limiting Control With Enhanced Dynamics of Grid-Forming Converters During Fault Conditions

Mads Graungaard Taul<sup>®</sup>, *Student Member, IEEE*, Xiongfei Wang<sup>®</sup>, *Senior Member, IEEE*, Pooya Davari<sup>®</sup>, *Senior Member, IEEE*, and Frede Blaabjerg<sup>®</sup>, *Fellow, IEEE*

Abstract—With an increasing capacity in the converter-based generation to the modern power system, a growing demand for such systems to be more grid-friendly has emerged. Consequently, grid-forming converters have been proposed as a promising solution as they are compatible with the conventional synchronousmachine-based power system. However, most research focuses on the grid-forming control during normal operating conditions without considering the fundamental distinction between a gridforming converter and a synchronous machine when considering its short-circuit capability. The current limitation of grid-forming converters during fault conditions is not well described in the available literature and present solutions often aim to switch the control structure to a grid-following structure during the fault. Yet, for a future converter-based power system with no or little integration of synchronous machines, the converters need to preserve their voltage-mode characteristics and be robust toward weak-grid conditions. To address this issue, this article discusses the fundamental issue of grid-forming converter control during grid fault conditions and proposes a fault-mode controller which keeps the voltage-mode characteristics of the grid-forming structure while simultaneously limiting the converter currents to an admissible value. The proposed method is evaluated in a detailed simulation model and verified through an experimental test setup.

Index Terms—Current limitation, fault ride-through, grid connection, grid forming control, voltage-source converter.

# I. INTRODUCTION

CRITICAL issue of the power system transitioning toward renewable energy sources is the gradual retirement of the bulk generation supplied by large synchronous machines. Conventional power systems dominated by synchronous machines both facilitate synchronizing torque, damping, and high system inertia which act as the primary ancillary support to the network during disturbances. To that end, during grid fault conditions, synchronous machines

Manuscript received May 7, 2019; revised June 27, 2019; accepted July 23, 2019. Date of publication July 29, 2019; date of current version May 6, 2020. This work was supported by the Reliable Power Electronic-Based Power System (REPEPS) Project at the Department of Energy Technology, Aalborg University as a part of the Villum Investigator Program funded by the Villum Foundation. Recommended for publication by Associate Editor Joseph O. Ojo. (Corresponding author: Mads Graungaard Taul.)

The authors are with the Department of Energy Technology, Aalborg University, 9220 Aalborg, Denmark (e-mail: mkg@et.aau.dk; xwa@et.aau.dk; pda@et.aau.dk, fbl@et.aau.dk).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JESTPE.2019.2931477

are capable of a large short-circuit current injection up to 6–8 pu [1, p. 319-345]. With a growing capacity of converter-based generation to the power system, concern is directed toward the overall stability of the system as power electronics-based generators neither provide inertia and synchronizing torque nor are they capable of providing short-circuit currents much higher than their rated current. Usually, grid-tied converters are controlled as grid-following converters where a voltage-based synchronization unit, often a synchronous-reference frame phase-locked loop (SRF-PLL), is used to align the current reference of the vector current control [2].

However, as the scheme is largely dependent on the assumption of a stiff voltage at the point of connection, this synchronization unit is shown to cause low-frequency oscillations and loss of synchronization during weak-grid and grid fault conditions [3]–[5]. Furthermore, with a trend for connecting generation at all voltage levels and with a future possibility for islanded operation of different parts of the network as a result of a system split, this is not possible with gridfollowing converters as there does not exist a dedicated voltage to act in accordance with. This is a fundamental limitation for grid-following PLL-synchronized converters since they simply follow the external environment. As a result of this, a growing interest has emerged in the research of grid-forming converters to address this issue by emulating the dynamics and beneficial functionalities of synchronous machines including the provision of synthetic inertia and a power-based synchronization mechanism.

Among the grid-forming converters, numerous control schemes exist: *droop control* [6], [7], *Virtual Synchronous Machine* (VISMA/VSM) [8], [9], synchronverter [10]–[12], *Power Synchronization Control* (PSC) [13], [14] and *Synchronous Power Controller* (SPC) [15], [16]. As the control schemes just mentioned do not necessarily specify a voltage magnitude and frequency set-point but modify these based on measurements from the local connection point, these converters may also be referred to as grid-supporting grid-forming converters [17]. It should be noted that grid-following converters may also be categorized as grid-supporting, but they still contain the fundamental issue of requiring to be connected to a stiff ac grid using the synchronization unit. As numerous researchers have identified the possible advantages of the grid-forming converter control during normal operating conditions,

few efforts have been put to analyze and understand its transient characteristics and fault behavior, as replicating the short-circuit behavior of a synchronous machine is not feasible with current-sensitive semiconductor devices.

As described in [17], [18], there are mainly two methods which can provide current limitation and stability for gridforming converter under large-signal disturbances: switching the control structure to the grid-following mode during the fault and limiting the converter currents using a virtual admittance structure. Along these lines, in [19], the converter control is switched to hysteresis control if the permissible allowed current is being exceeded. This method obviously loses all functionalities of the grid-forming control during this period, and how to deal with the saturation of outer control loops is not discussed. In a similar fashion, switching to grid-following control during the fault is proposed in [14], [20]-[22]. This solution needs a backup PLL for the synchronization, which then has its own stability issues for weak-grid conditions. As previously shown, the current limitation can be achieved simply by limiting the current references directly during the fault. However, this will cause wind-up in the outer power loops, which can lead to instability [17]. To circumvent this, several researchers propose the use of virtual resistors, either linear [23] or nonlinear [24] to reduce the converter voltage reference. Also, the influence of a virtual impedance structure on the current limitation is analyzed in [25]. As disclosed, the current limitation is largely depending on the fault location and the selected virtual impedance, which may limit its usefulness in practice as the maximum converter current is desired to be utilized during any fault condition. To that end, the virtual impedance concept may cause problems in parallel operation [24]. In [26], both limitations of the inner current reference and voltage reference reduction using the virtual impedance concept are conducted. In this way, the currents are limited and wind-up in the outer loops are avoided using the virtual impedance concept. Nevertheless, the virtual impedance still has the problem that its accuracy of limitation depends on several unknown factors as previously mentioned.

Conclusively, for the methods that switch to a grid-following structure during the fault, the robust grid-forming properties of the converter are lost. To that end, for the methods that directly limit the current references, either the outer power loops and droop controllers are not considered or wind-up and instability is encountered. To avoid wind-up in the outer power loops while limiting the currents, a virtual impedance may be used. However, the limiting performance of this is variable and depends on several unknown factors, which makes the utilization of it less attractive. Hence, how to deal with saturation in the outer loops alongside how to sustain the grid-forming structure while limiting the converter currents is not well described in the available literature. Thereby, this article aims to describe the issues of the current limitation of grid-forming converters considering the outer loops and their influence on the converter response. Besides this, an enhanced current limiting control method is proposed where the converter currents are precisely limited to the desired value and the converter remains as grid-forming during the fault. This is done by directly limiting the converter current references

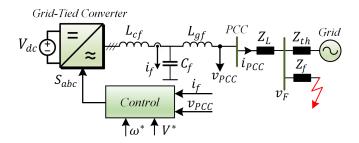

Fig. 1. Overall system of a grid-forming grid-tied VSC connected to an external Thevenin modeled grid with a symmetrical fault occurring close to the  $v_F$  bus.

TABLE I

MAIN PARAMETERS OF THE SYSTEM IN FIG. 1

| Symbol   | Description             | Value         |

|----------|-------------------------|---------------|

| $S_n$    | Rated power             | 7.35 kVA      |

| $V_b$    | Nominal 1-1 voltage     | 400 V (rms)   |

| $V_{dc}$ | dc-link voltage         | 730 V         |

| $f_0$    | Rated frequency         | 50 Hz         |

| $f_{sw}$ | Switching frequency     | 10 kHz        |

| $f_s$    | Sampling frequency      | 10 kHz        |

| $L_{cf}$ | Converter-side inductor | 0.07 pu       |

| $L_{qf}$ | Grid-side inductor      | 0.04 pu       |

| $C_f$    | Filter capacitor        | 0.07 pu       |

| $Z_L$    | Thevenin/Line impedance | 0.04j-0.5j pu |

| SCR      | Short-Circuit Ratio     | 2-25          |

alongside adjusting the outer power references such to avoid wind-up in the outer loops and to keep their advantageous dynamics during the fault.

The remaining parts of this article are structured as follows. Section II describes the structure of the considering grid-forming controller. The issues of grid-forming control during faults are identified and potential solutions for current limitation are tested in Section III. Section IV describes the proposed current limitation method alongside an enhanced fault recovery method using a dynamic damping controller. Subsequently, the proposed fault controller is experimentally verified in Section V. Finally, Section VI concludes this article.

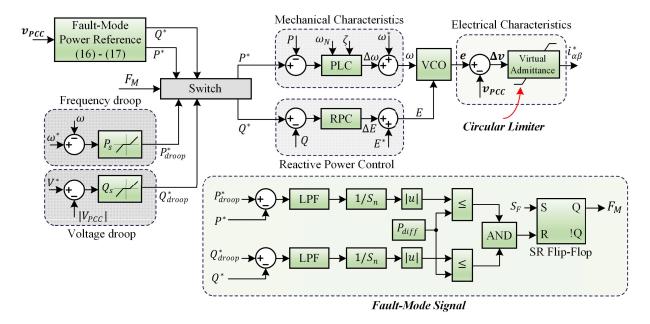

### II. STRUCTURE OF GRID-FORMING CONVERTER

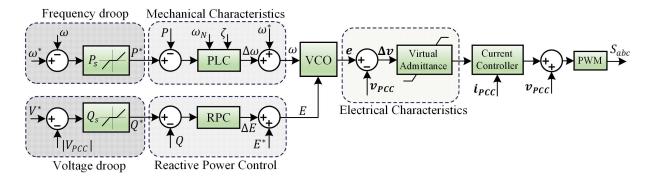

The system under study is a grid-tied grid-forming converter as shown in Fig. 1 where the main parameters of the system can be seen in Table I. The detailed view of the grid-forming control structure, the SPC, is depicted in Fig. 2 [27]. Here, the grid-forming converter is controlled to emulate a conventional synchronous generator with virtual mechanical and electrical characteristics. The mechanical part of the synchronous generator is emulated by virtual inertia and damping, which aims to support the network frequency, and the electrical part is emulated by a virtual stator impedance, which can be used to define the power sharing and power exchange with the grid [28]. The power loop controller (PLC)

Fig. 2. Control block diagram of SPC. The PLC adjusts the frequency, dependent on the active power change from the droop controller with a defined natural oscillating frequency and damping coefficient.

provides the converter with the mechanical property of a synchronous machine and forms the relationship between power balance and the virtual angular frequency of the emulated machine. The reactive power controller (RPC) provides the control with the voltage amplitude of the virtual machine by controlling the reactive power. The virtual angular frequency is integrated to obtain the phase angle, which together with the voltage magnitude forms the inner virtual electromotive force of the emulated machine. Droop control is contained in the outer two loops to determine the active and reactive power references based on the deviation of the network voltage and frequency. The droop controllers replicating the governor/turbine and automatic voltage regulator (AVR) of the synchronous machine are mathematically expressed as

$$P^* = P_s + (\omega^* - \omega)D_P \tag{1}$$

$$Q^* = Q_s + (V^* - |V_{PCC}|)D_O$$

(2)

where  $P_s$  and  $Q_s$  are the external set points of the active and reactive power, respectively,  $\omega$  is the virtual oscillating frequency from the PLC, and  $D_P$ ,  $D_Q$  are the droop gains for the active and reactive power, respectively. To achieve accurate and decoupled control of the active and reactive power, the virtual admittance block in Fig. 2, which specifies the virtual admittance of the stator windings, is included to guarantee an output impedance, which is dominantly inductive. The virtual admittance structure is implemented as

$$\mathbf{i}_{\alpha\beta}^* = \frac{\mathbf{e}_{\alpha\beta} - \mathbf{v}_{\alpha\beta}}{R_v + sL_v} \tag{3}$$

where  $R_v$  and  $L_v$  are the virtual resistance and inductance of the output stator impedance, respectively,  ${\bf e}$  is the virtual EMF calculated from the two outer power loops, and  ${\bf v}$  is the voltage measured at the point of common coupling (PCC). Since the inner current control forms a cascaded loop with the virtual admittance, the bandwidth of the virtual admittance should be set significantly slower than that of the inner current loop. As described in [29], the virtual reactance should be fixed to 0.3 pu of the rated impedance of the converter, which corresponds to a typical reactance value for a grid-connected synchronous machine. Subsequently, the virtual resistance is selected to get a desired cutoff frequency of the virtual admittance low-pass filter. By choosing the cut-off frequency ten times slower than the inner current controller, a virtual resistance of 0.1 pu is selected.

With the virtual admittance selected such that the impedance seen from the converter terminals is highly inductive, the threephase power transfer between the virtual machine and the grid at the sending-end can be determined as

$$P = \frac{3}{2} \frac{EV_g \sin(\delta)}{X} \approx \frac{3}{2} \frac{EV_g \delta}{X} = P_{\text{max}} \delta$$

(4)

$$Q = \frac{3}{2} \left( \frac{E^2 - EV_g \cos(\delta)}{X} \right) \approx \frac{3}{2} \frac{E(E - V_g)}{X}$$

(5)

where  $\delta$  is the phase angle difference between the two sources, X is the total output reactance between the two sources,  $P_{\text{max}}$  is the three-phase nominal active power, and E and  $V_g$  are the peak values of the voltage at the sending end and receiving end, respectively. The SPC uses the internal synchronization mechanism in ac networks similar to a synchronous machine. This inherent power-based synchronization structure is obtained by using a regulator of the active power error, the PLC, to generate the synchronization angle/frequency. Usually, to emulate the characteristic properties of a synchronous machine, but with a simple implementation, the swing equation is employed as

$$\frac{2HS_n}{\omega_0}\frac{d^2\delta}{dt} = P_m - P_e - D\omega_0 \frac{d\delta}{dt} \tag{6}$$

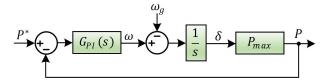

where H is the inertia constant,  $S_n$  is the rated power, D is the total damping coefficient,  $P_m$  is the mechanical power,  $P_e$  is the electrical power,  $\omega_0$  is the rated electrical angular frequency, and  $\delta$  is the load angle of the machine relative to the grid. However, since the damping coefficient of the swing equation introduces a steady-state droop effect given a frequency deviation, a PI controller is used in the PLC instead. With this, the PLC dynamics of the block diagram in Fig. 3 can be expressed as

$$\frac{P(s)}{P^*(s)} = \frac{P_{\text{max}} K_{pp} s + K_{ip} P_{\text{max}}}{s^2 + K_{pp} P_{\text{max}} s + K_{ip} P_{\text{max}}} = \frac{2\zeta \omega_N s + \omega_N^2}{s^2 + 2\zeta \omega_N s + \omega_N^2}.$$

(7)

To emulate the inertia constant and damping ratio of the second-order response, the controller gains should be selected as

$$K_{ip} = \frac{\omega_0}{2HS_n}, \quad K_{pp} = \zeta \sqrt{\frac{2\omega_0}{HS_n P_{\text{max}}}}$$

(8)

where the inertia constant is selected in the range  $H \approx 2-5$  s.

Fig. 3. Block diagram of PLC with a PI controller to form a relationship between active power error and virtual frequency of the machine.

Fig. 4. Small-signal control block diagram of the RPC.

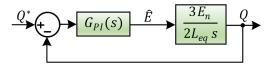

Besides the PLC, the RPC is used to regulate the amplitude of the voltage reference to obtain a given desired reactive power similar as the AVR and exciter of a synchronous machine. Using the three-phase reactive power from (5) and linearizing around Q = 0, i.e.,  $E_0 = V_{g0} = E_n$ , one gets that

$$\hat{Q} = \frac{3}{2} \frac{2E_0 - V_{g0}}{L_{eq}s} \hat{E} = \frac{3E_n}{2L_{eq}s} \hat{E}.$$

(9)

where  $E_n$  is the nominal voltage of the virtual machine. Using a PI controller to regulate the reactive power as shown in Fig. 4, the closed-loop transfer function for the RPC becomes

$$\frac{Q(s)}{Q^*(s)} = \frac{\frac{3E_n K_{pq}}{2L_{eq}} s + \frac{3K_{iq} E_n}{2L_{eq}}}{s^2 + \frac{3E_n K_{pq}}{2L_{eq}} s + \frac{3K_{iq} E_n}{2L_{eq}}}.$$

(10)

The proportional and integral gains can be selected to achieve the desired damping and undamped natural frequency as

$$K_{pq} = \frac{4\zeta \omega_N L_{\text{eq}}}{3E_n}, \quad K_{iq} = \frac{2\omega_N^2 L_{\text{eq}}}{3E_n}.$$

(11)

The equivalent inductance  $L_{eq}$  is the total inductance between the inner machine emf and the grid voltage given as

$$L_{\text{eq}} = L_v + L_{cf} + L_{gf} + L_g + L_L \text{ where } L_v = \frac{X_v V_b^2}{\omega_0 S_n}.$$

(12)

The inner current controller is a proportional-resonant (PR) controller implemented in the  $\alpha\beta$ -reference frame as in [30] and [31].

# III. CONTROL ISSUES WITH GRID-FORMING CONVERTERS DURING GRID FAULTS

This section explains the fundamental issues of grid-forming converter control during grid-fault conditions and initiates the development of the foundation for the proposed fault-mode controller to be described in Section IV.

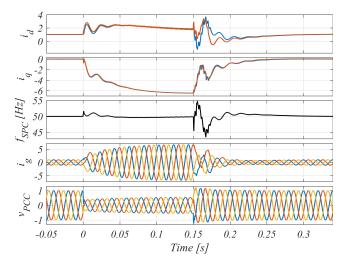

To highlight the control issue of the SPC, a symmetrical three-phase fault is tested as shown in Fig. 5 where its controller parameters for the grid-forming structure is displayed in Table II. To simulate the grid fault, the three-phase voltages of the Thevenin grid is directly controlled to instantaneously change its voltage magnitude when the fault is considered

Fig. 5. Simulated fault response of SPC during a symmetrical fault with a voltage magnitude of 0.3 pu and a grid impedance of 0.04 pu. For the dq-axes currents, the actual (blue) and the reference values (red) are visualized.

to occur. From Fig. 5, it can be observed that the PCC voltage is being highly supported inherently by the grid-forming structure without any control modification during the fault. Even though this is a particularly attractive feature, this voltage support is realized through a large injection of reactive current with a magnitude of 6.7 pu.

As the SPC is a voltage-controlled structure, it simply requests a current reference to maintain the reference voltage in order to satisfy the demands from the outer PLC and RPC. Hence, compared to a grid-following converter, the SPC behaves as a voltage source with controlled amplitude and frequency. In case of short-circuit fault conditions, the controlled voltage source will naturally respond by injecting very high current values to sustain its voltage level. With that, since voltage-source converters (VSCs) must be protected from overcurrent of the semiconductor devices, the current reference must be restricted given it is higher than permitted.

Even though the SPC can provide grid-supporting functionalities, provided that a power reserve is available, which enhances the transient stability of the network, the synchronization stability of the converter may be diminished in case of grid faults when including current limiters [32]. This may indicate that the outer loops have an impact on the response when the current magnitude is limited as their requested voltage reference may be met. Therefore, it is desired to test different limiting strategies to evaluate how a voltage-mode control structure can be employed during symmetrical grid faults. From this, the current limitation is required but during grid faults where the converter may be saturated, synchronization instability may be at risk.

One solution is of course to oversize the converter such that it is able to handle larger currents. However, this comes with an increased converter cost, which is highly undesired. Another approach could be to decrease the virtual admittance to limit the current [23]. However, two issues have been encountered when doing this. At first, the value of admittance needed to achieve a given maximum current is dependent on the voltage sag and control, i.e., it changes for different

TABLE II

CONTROL PARAMETERS OF THE SPC STRUCTURE IN FIG. 2

| Grid-Forming Controller (SPC) | Parameters                                                                   |

|-------------------------------|------------------------------------------------------------------------------|

| Droop Control                 | $D_P = 0, D_Q = 178.7 \text{ VAr/V}$                                         |

| Virtual Admittance            | $R_v=0.1$ pu, $L_v=0.3$ pu                                                   |

| Current Controller            | $K_p = 12, K_r = 2000$                                                       |

| PLC                           | $H=2 \text{ s, } \zeta=0.707, K_{pp}=1.7 \text{e-3}, K_{ip}=10.7 \text{e-3}$ |

| RPC                           | $\zeta=0.707,\omega_N=20$ rad/s, $L_{eq}=29.7$ mH, $E_n=326.6$ V             |

Fig. 6. Simulated fault response of SPC during a symmetrical fault with a voltage magnitude of 0.3 pu. The grid impedance is 0.04 pu and the current reference is limited to 1.2 pu. For the dq-axes currents, the actual (blue) and the reference values (red) are visualized.

fault conditions. One may decrease the admittance until the admissible current is achieved. However, the maximum allowable converter current is independent on any fault condition and control. Therefore, it is easier and more intuitive to implement a direct current limiter on the reference values. Second, if the inductance of the virtual admittance structure is increased for current limitation when a fault is detected, a dcbias may be introduced to the current references as the inductor current cannot change its value instantaneously. Therefore an ac signal with a decaying dc component will occur in the current reference which is not desired. Accordingly, the current limitation will be based on directly limiting the converter current reference to avoid these issues. As the control structure operates with sinusoidal signals, an instantaneous hard limiter will clip the peak of the signal, resulting in a deteriorated output current. To circumvent this, a circular limiter is implemented where the stationary frame current reference is determined as

$$\mathbf{i}_{\alpha\beta}^{*} = \begin{cases} \mathbf{i}_{\alpha\beta} \frac{I_{\lim}}{\sqrt{i_{\alpha}^{2} + i_{\beta}^{2}}} & \text{if } \sqrt{i_{\alpha}^{2} + i_{\beta}^{2}} > I_{\lim} \\ \mathbf{i}_{\alpha\beta} & \text{otherwise} \end{cases}$$

(13)

where  $I_{\text{lim}}$  is selected as 1.2 pu of the nominal converter current. The result of the circular limiter can be examined in Fig. 6. As desired, the output current is limited to 1.2 pu

Fig. 7. Simulated fault response of SPC during a symmetrical fault with a voltage magnitude of 0.3 pu. The grid impedance is 0.04 pu and the power references are limited as shown in (16). For the dq-axes currents, the actual (blue) and the reference values (red) are visualized.

during the fault, the outer control loops injects reactive power to boost the voltage, and the PLC reduces its active power output due to a jump in the virtual frequency. Only the peak-values of  $v_{\rm PCC}$  is shown in Fig. 6 such that the sustained overvoltages after the fault recovery can be easily visualized. During the time 0–0.15 s, the PCC voltage simply drops and is supported as shown in Fig. 5.

In addition, a few things should be perceived. Albeit capacitive reactive current is injected, the converter does not comply with the grid code since the voltage support is decreasing during the fault period ( $i_q$  increases during the fault). Furthermore, due to the high power references of the slow outer loops and the saturation of the current reference, an elongated unsatisfactory postfault response is experienced caused by integrator windup in the outer loops. At this time, the active power is slowly increased to 1.2 pu till it matches the power references to the current limiter where after it returns the desired steady-state condition. Using this, it can be seen that the converter currents can be limited but the fault response and, especially the postfault response needs improvement. One problem of the method just discussed is that the outer power loops are not adjusted to take into account that the converter has very limited margins with respect to the injected currents and actually becomes saturated. To address this issue, it should be possible to limit the converter output current by changing

Fig. 8. Proposed fault-mode control structure of SPC where  $F_M$  selects between droop control and power reference control based on grid code requirements and a circular limiter is used to constrain the current reference.

the active and reactive power references in case of a fault [33]. With this, the admissible converter power is updated when the fault occurs as

$$S_{\text{new}} = \sqrt{\frac{3}{2}} \cdot \frac{V^+ - V^-}{V_b} S_n \tag{14}$$

where  $V^+=(v_\alpha^{+2}+v_\beta^{+2})^{1/2}$  and  $V^-=(v_\alpha^{-2}+v_\beta^{-2})^{1/2}$  are the amplitudes of the positive and negative sequence voltages, respectively. In the case of a symmetrical fault where  $V^-=0$ , the expression reduces to

$$S_{\text{new}} = V_{\text{pu}} S_n. \tag{15}$$

The reactive power reference, which complies with the grid codes, can then be computed as

$$Q^* = \begin{cases} \text{Voltage Droop} & \text{if } V_{\text{pu}} > 0.9\\ 2S_{\text{new}}(1 - V_{\text{pu}}) & \text{if } 0.5 < V_{\text{pu}} < 0.9\\ S_{\text{new}} & \text{otherwise.} \end{cases}$$

(16)

Using the updated apparent power and the reactive power reference, the active power reference that averts destructive overcurrents can be determined as

$$P^* = \sqrt{S_{\text{new}}^2 - Q^{*2}}. (17)$$

In case the reactive power reference is greater than the new rated converter power, the active power reference is set to zero and the reactive power reference is set equal to  $S_{\text{new}}$ . The power limiting method presented in (16) is tested during a symmetrical fault as shown in Fig. 7. Using this, the maximum values of the injected current are reduced to around 3 pu and firmly decreases to 1 pu as the power reference dictate. Despite that, overcurrents are conspicuous for a duration of more than ten fundamental cycles due to the slow transient response of the outer PLC and RPC.

# IV. ENHANCED FAULT RIDE-THROUGH OF GRID-FORMING CONVERTER

Based on the analysis and approaches just described for current limitation, a method is proposed which limits the converter current while keeping the fundamental structure of the grid-forming control during the fault. This is done by combining the two approaches from Section III, i.e., inner current limitation and outer power reference adjustment. In addition, a dynamic virtual damping controller is proposed to enhance the fault recovery process of the grid-forming converter when the fault is cleared.

# A. Current Limitation and Reference Power Adjustment

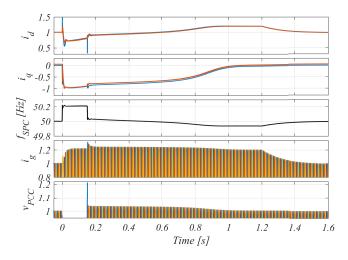

Considering that it is just desired to limit the converter currents and not anything else during the fault, the current reference is still the most logical location to intervene. Therefore, a method where the reference power is adjusted based on the voltage dip during the fault (16) together with the circular current limitation (13) is proposed. As a result of these, the currents will be limited and the reference values set to the outer power controllers will be adjusted based on the grid code requirements. Accordingly, by using the circular limiter to provide precise current limitation alongside realizing that the power update approach from [33] can be reformulated and utilized for a grid-forming converter with outer power loops to avoid instability and wind-up, comprise the contribution and the proposed fault-mode controller. To that end, how to transition between the two power references and how to merge (16) and (17) with the droop operation of the SPC is as well addressed. The proposed structure is depicted in Fig. 8 where  $F_M$  is the fault-mode signal used to switch between the power references from the outer droop controllers and the power reference based on the grid code requirements. The fault signal,  $S_F$ , is set high when the magnitude of

Fig. 9. Simulated fault response of SPC during a symmetrical fault with a voltage magnitude of 0.3 pu. The grid impedance is 0.04 pu and the control structure shown in Fig. 8 is used for the reference power calculation. For the dq-axes currents, the actual (blue) and the reference values (red) are visualized.

the stationary-reference frame voltage vector drops below 0.9 pu. When this occurs with a response time below 1 ms,  $F_M$  takes a logical high state and immediately switches to the fault-mode control. With the proposed method in Fig. 8, the fault-mode control is preserved after the fault recovery until the differences between the per-unit values of the active and reactive power references of the droop controllers and the fault-mode control defined in (16) and (17), fall below  $P_{\text{diff}}$ . Therefore, the time after fault recovery where the faultmode control is activated is depending on  $P_{\text{diff}}$ , the droop coefficients, and the fault recovery response defined by the external network. However, considering the selected droop coefficients are general and selecting  $P_{\text{diff}} = 5\%$  of the nominal power, then the fault-mode control is activated 150 ms after the fault has been cleared. As the difference between the two controllers is small when the fault-mode control is deactivated and since the bandwidths of the outer PLC and RPC are low, the reactivation of the droop controllers happens seamlessly without disturbances in the injected currents and does therefore not affect the performance of the system. Therefore, with this configuration, the characteristics of the virtual machine are kept both during normal as well as fault conditions and the converter current is limited. The only difference between the modes is that the outer power references set by the droop controllers are bypassed during the fault.

The performance of the proposed method when exposed to a symmetrical fault is visualized in Fig. 9. Due to the imbalance between the measured and requested active power during the fault recovery, a frequency response dictated by the dynamics of the virtual mechanical characteristics of the emulated machine emerges. This temporary increase in the virtual oscillating frequency is necessary for the converter to once again pick up the load and keep synchronized with the external grid. By using this control approach, the current injection during the fault comply with the grid code and the postfault response is significantly improved without exceeding the permitted current and without the inconvenience to

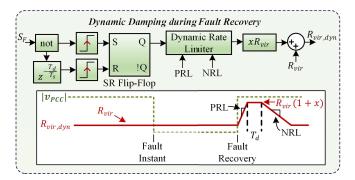

Fig. 10. Dynamic damping during fault recovery where the virtual resistance is increased momentarily during the fault recovery to provide additional system damping. The dynamic virtual resistance,  $R_{vir,dyn}$ , is increased to  $R_{vir}(1+x)$  quickly based on the PRL when the voltage recovers. After a delay of  $T_d$ , the virtual resistance is again lowered to  $R_{vir}$  with the ramp rate defined by the NRL.

adopt a PLL-based grid-following structure during the fault. As proposed in [14], [20], if a grid fault is detected, the power-synchronization control is switched to current-mode control in order to limit the converter currents. This can effectively be done but has the need for a backup PLL which is used in order for the converter to remain synchronized with the grid during the fault. As explained in [4], [5], [34], the PLL is a critical component for the converter stability, especially during low-voltage situations. Accordingly, it is highly advantageous that the method presented in Fig. 8 can limit the converter currents, comply with grid code requirements without switching the fundamentals of the control structure.

# B. Enhanced Fault Recovery Using Dynamic Damping

From Fig. 9, some amount of undesired weakly damped oscillations are experienced during the recovery process. These oscillations are becoming an increasing issue as the SCR is decreasing since an increased sensitivity between the injected currents from the converter and the PCC voltage will emerge. To enhance the fault recovery process, a dynamic damping method is proposed in addition to the fault control presented in the previous section. The fundamental principle is to adaptively decrease the conductivity in the virtual admittance structure momentarily during the recovery period as shown in Fig. 10. The operation is that when the fault is cleared, the output of the SR flip-flop is set high, which increases the virtual resistance from  $R_{\rm vir}$  to  $R_{\rm vir}(1+x)$  at a rate defined by the positive rate limiter (PRL). This increased damping is sustained for a duration of  $T_d$  seconds where after the resistance is again decreased to its postfault value with a rate defined by the negative rate limiter (NRL). The slope defined by the PRL as depicted in Fig. 10 is intentionally drawn low for clear visibility. During the tests conducted, the PRL is set with a slope of 10 000 making the increase in virtual resistance to happen in one sampling period. On the other hand, the NRL is set such that the virtual admittance will ramp down from  $R_{\text{vir}}(1+x)$  to  $R_{\text{vir}}$  in 10 ms. The constant x showed in Fig. 10 can be set manually depending on which virtual damping is needed to provide an acceptable fault recovery response.

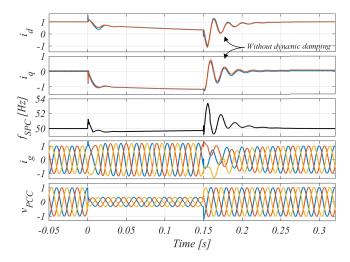

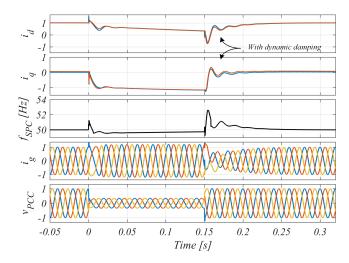

Fig. 11. Identical simulation case study as in Fig. 9 but with dynamic damping activated during the fault recovery as shown in Fig. 10 where x = 1. For the dq-axes currents, the actual (blue) and the reference values (red) are visualized

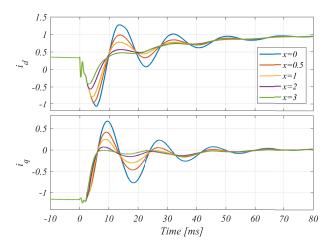

Fig. 12. Influence of dynamic damping on  $i_{dq}$  during fault recovery occurring at 0 s for the test conditions as shown in Fig. 9. The dynamic damping is changed using x from Fig. 10.

Using the proposed dynamic damping during the fault recovery, it can be seen from Fig. 11 that the oscillations in the dq-axes currents have been highly decreased by the use of the dynamic damping controller in Fig. 10. A detailed view of the fault recovery response using different values for the dynamic damping is provided in Fig. 12. Here, the fault is cleared at 0 s and the actual dq-axes currents during the recovery are shown. As it can be clearly seen, the undershoot and overshoot in  $i_d$  and  $i_q$ , respectively, can be significantly reduced by increasing the virtual resistance in the dynamic damping control. The improvements in reducing the undershoot and overshoot during the fault recovery are specifically calculated and presented in Table III where it can be observed that the overshoot in  $i_q$  can be fully eliminated. Such tight control of  $i_q$  has a positive impact on the PCC voltage recovery as injecting positive  $i_q$  will make the converter act as an inductor prolonging the voltage recovery process.

TABLE III

Influence on  $i_{dq}$  Undershoot and Overshoot During Fault Recovery Using Different Dynamic Damping Values of x From Fig. 12

| x in Fig. 10 | $i_d$ undershoot | $i_q$ overshoot |

|--------------|------------------|-----------------|

| 0            | 210 %            | 57 %            |

| 0.5          | 189 %            | 35 %            |

| 1            | 165 %            | 21 %            |

| 2            | 133 %            | 6 %             |

| 3            | 108 %            | 0 %             |

# C. Method Comparison and Weak-Grid Performance

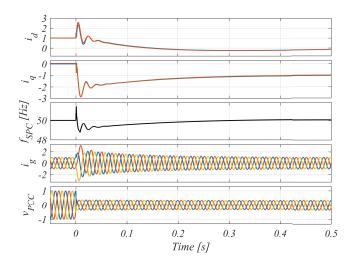

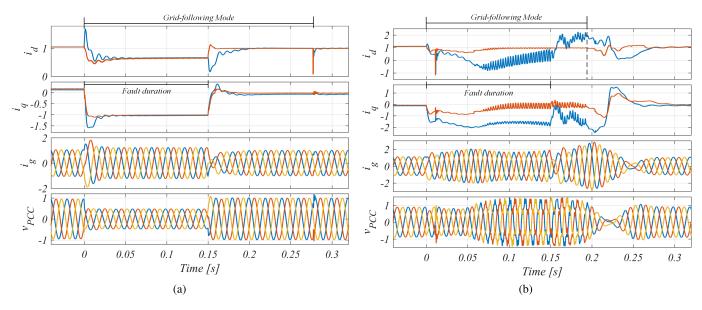

With the fault-mode controller and dynamic damping structure being presented, the proposed SPC is compared to the solution proposed in [22], which represents a comprehensive and implementable fault-mode controller for a grid-forming converter during fault conditions. Here, the control structure is switched to a grid-following PLL-synchronized structure during the fault to limit the converter currents. When the fault has been cleared, the transitioning back to the grid-forming controller is performed using a feedback tracking controller, which after the fault, aligns the phase-angles of the two controllers and perform a seamless switching when aligned. For the comparison, two test cases are considered: a fault where the SCR is 5 and a fault where the SCR is 2, where the latter represents a more realistic case where the grid-forming technology may be utilized. The results of the two cases using the method based on [22] are shown in Fig. 13. In the top of each figure, one can identify the fault duration in addition to the time where the grid-following mode is activated. Besides a temporary overcurrent when entering the fault, it can be appreciated from Fig. 13(a) that the grid-following mode can limit the converter currents and provide a good fault ride-through response. The settling time of  $i_q$  when the fault occurs is 18 ms, whereas during the voltage recovery, the active current settles in 23 ms and the reactive current has a slight overshoot of 0.4 pu before reaching steady state. When decreasing the SCR to 2 as shown in Fig. 13(b), the disadvantage of the PLL-synchronized grid-following structure can be observed. A fully unstable response results where high uncontrolled converter overcurrents arise. The stability is again obtained when the grid-following structure is switched back to the gridforming controller.

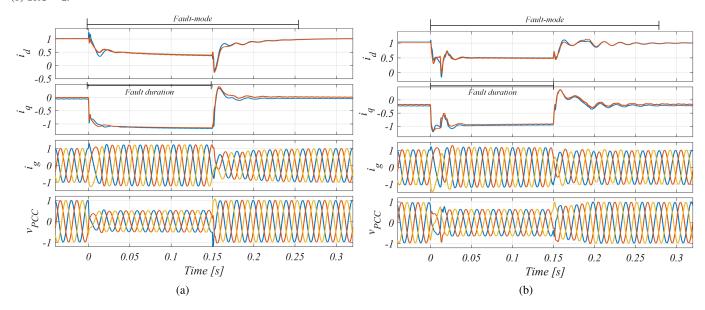

The same two tests are performed using the proposed structure as it can be perceived in Fig. 14. For the case where SCR = 5 [Fig. 14(a)], a similar response as observed with the grid-following structure is obtained. When comparing the transient time performance a slight difference exists. The settling time of  $i_q$  when the fault occurs is decreased to 10 ms, whereas during the voltage recovery, the active current settles in 35 ms and the reactive current has an overshoot of 0.35 pu before reaching steady state. To that end, compared to the small glitch happening in Fig. 13(a), when the grid-following mode is deactivated, the seamless transition of the proposed structure is unnoticeable from Fig. 14(a). For the last test

Fig. 13. Simulated fault response during a symmetrical fault with a voltage magnitude of 0.3 pu. The control structure is based on [22] where the grid-forming controller is switched to grid-following during the fault. For the dq-axes currents, the actual (blue) and the reference values (red) are visualized. (a) SCR = 5. (b) SRC = 2.

Fig. 14. Simulated fault response of proposed SPC using dynamic damping with x = 2 during a symmetrical fault with a voltage magnitude of 0.3 pu. The control structure shown in Fig. 8 is used for the reference power calculation. For the dq-axes currents, the actual (blue) and the reference values (red) are visualized. (a) SCR = 5. (b) SRC = 2.

where the SCR = 2, the results using the proposed structure can be seen in Fig. 14(b). Due to the high line impedance, a significant amount of reactive current needs to be provided in addition to the nominal active power injection. This results in a quite challenging operating condition as the injected current is a bit above nominal when the grid fault occurs. As it can be seen, the dq-axes currents quickly reach their reference values in a stable manner and the recovery process happens with a negligible overshoot in the q-axis current and in a low oscillatory manner. Due to the distorted and temporarily unbalanced voltage and currents around 20 ms into the fault, a jump can be observed in the dq-axes currents. Based on this, the proposed structure is able to limit the converter currents and transition to and from the proposed fault-mode

controller in an appreciated manner, even during very weakgrid conditions.

# V. EXPERIMENTAL VERIFICATION

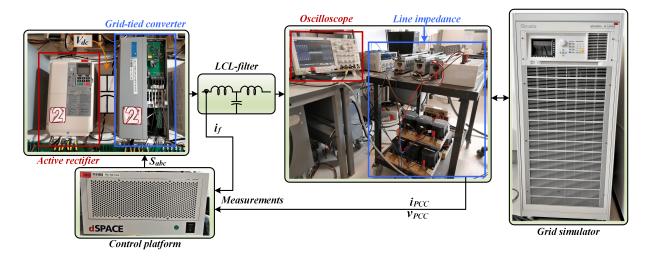

To further verify the proposed fault-mode control and dynamic damping control, these are tested experimentally in the laboratory setup shown in Fig. 15. A Yaskawa D1000 active rectifier is used to control the dc-link voltage to the desired value of 730 V. The converter under test is the grid-tied converter, which is a Danfoss VLT FC-302 15-kVA frequency inverter. The converter currents, grid currents, and PCC voltages are being measured using two types of LEM sensors, whereas only  $i_f$  and  $v_{\rm PCC}$  are being used for

Fig. 15. Laboratory setup used for the experimental verification. The grid-tied converter is controlled using a dSPACE controller and is connected to an inductor-capacitor-inductor (LCL)-filter, a line impedance, and finally, a grid simulator which emulates the voltage sag of the grid fault.

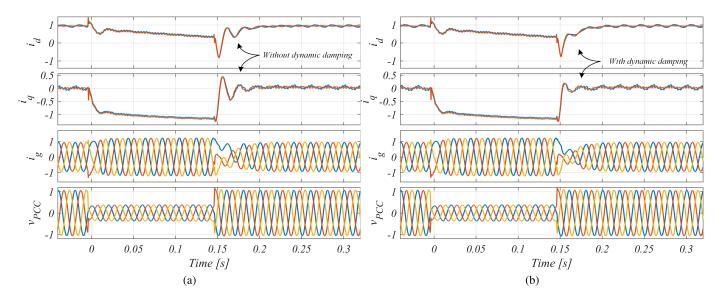

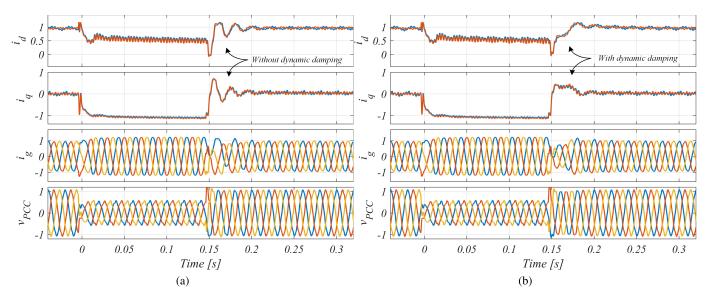

Fig. 16. Experimental validation of the proposed fault mode controller for an SCR of 25. (a) Without dynamic damping during the fault recovery. (b) With dynamic damping during the fault recovery where x = 1 in Fig. 10. For the dq-axes currents, the actual (red) and the reference values (blue) are visualized.

control purposes. Between the Inductor-Capacitor-Inductorfilter and the grid simulator is the line impedance taking values in the range of 0.04–0.2 pu. The grid simulator is a Chroma Regenerative Grid Simulator Model 61845 which is specifically programmed to emulate the grid fault by directly controlling the three-phase voltages at its output. By this, at the fault instant of interest, the amplitudes of the threephase voltages are reduced to 0.3 pu in 0.1 ms. Hereafter, they remain constant for the fault period of 0.15 s and then they increase to their nominal value with the same dynamic response. From the measurements, the actual programming, control, and data acquisition are processed in a dSPACE expansion box consisting of a DS1007 PPC processor board for code actuation, a DS5101 digital waveform output board for pulsewidth modulation (PWM) pulse signal generation, and a DS2004 high-speed A/D board for measuring of the currents and voltages. The parameter values for the setup and control can be seen in Tables I and II, respectively.

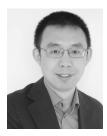

The response without and with the dynamic damping using the proposed fault-mode control is depicted in Fig. 16. The experimental results are in good agreement with the simulation study where it is evident that the dynamic virtual damping provides sufficient damping to achieve an acceptable fault recovery process. Finally, the proposed fault-mode controller is tested experimentally for an *SCR* of 5 as visualized in Fig. 17. Once again, the grid-forming structure is shown to be able to successfully ride through the fault without exceeding the maximum allowed converter current. Also, the weakly damped oscillations during the fault recovery are seen to be more adverse considering the lower SCR. However, the fault recovery is significantly enhanced with the use of dynamic damping control.

Notably, it can be seen from Fig. 17, that the PCC voltage contains higher distortions with a decreasing SCR. This originates as a result of the interaction between the larger line impedance and the voltage feed-forward in the controller.

Fig. 17. Experimental validation of the proposed fault mode controller for an SCR of 5. (a) Without dynamic damping during the fault recovery. (b) With dynamic damping during the fault recovery where x = 3 in Fig. 10. For the dq-axes currents, the actual (red) and the reference values (blue) are visualized.

Accordingly, for lower SCRs, a tradeoff between fast fault recovery response and low harmonic distortion in the PCC voltage must be made by adjusting the voltage feed-forward.

## VI. CONCLUSION

Grid-forming converters are becoming increasingly attractive as potential candidates for converter control of future power electronics-based power systems due to their gridfriendly functionalities. As the converter include currentsensitive semiconductor devices, it cannot sustain the behavior of a voltage source during grid faults as its short-circuit capability is much lower than that of a synchronous generator. This article discusses the issues of current limitation of grid-forming converters and introduces a proposed method, which includes several advantageous properties: instantaneous limitation of the converter currents, compliance with grid code requirements, and circumvention to switch the fundamentals of the control structure during the fault. To that end, enhanced fault recovery is attained by a proposed dynamic virtual damping controller. With this, it is shown that the grid-forming converter can provide grid-supporting functionalities during normal operating conditions and by only modifying the outer power reference generation instead of the inner structure, fault ride-through capability is achieved. The proposed fault mode and dynamic virtual damping controller of the grid-forming converter are tested during very weak-grid conditions and its performance is verified experimentally.

# REFERENCES

- [1] N. Tleis, Power Systems Modelling and Fault Analysis—Theory and Practice. Amsterdam, The Netherlands: Elsevier, 2008.

- [2] Q. Fu, W. J. Du, G. Y. Su, and H. F. Wang, "Dynamic interactions between VSC-HVDC and power system with electromechanical oscillation modes—A comparison between the power synchronization control and vector control," in *Proc. IEEE PES Asia–Pacific Power Energy Eng.* Conf. (APPEEC), Oct. 2016, pp. 949–956.

- [3] J. Z. Zhou, H. Ding, S. Fan, Y. Zhang, and A. M. Gole, "Impact of short-circuit ratio and phase-locked-loop parameters on the small-signal behavior of a VSC-HVDC converter," *IEEE Trans. Power Del.*, vol. 29, no. 5, pp. 2287–2296, Oct. 2014.

- [4] D. Dong, B. Wen, D. Boroyevich, P. Mattavelli, and Y. Xue, "Analysis of phase-locked loop low-frequency stability in three-phase grid-connected power converters considering impedance interactions," *IEEE Trans. Ind. Electron.*, vol. 62, no. 1, pp. 310–321, Jan. 2015.

- [5] M. G. Taul, X. Wang, P. Davari, and F. Blaabjerg, "An overview of assessment methods for synchronization stability of grid-connected converters under severe symmetrical grid faults," *IEEE Trans. Power Electron.*, vol. 34, no. 10, pp. 9655–9670, Oct. 2019.

- [6] S. D'Arco and J. A. Suul, "Virtual synchronous machines— Classification of implementations and analysis of equivalence to droop controllers for microgrids," in *Proc. IEEE Grenoble Conf.*, Jun. 2013, pp. 1–7.

- [7] J. Rocabert, A. Luna, F. Blaabjerg, and P. Rodriguez, "Control of power converters in AC microgrids," *IEEE Trans. Power Electron.*, vol. 27, no. 11, pp. 4734–4749, Nov. 2012.

- [8] H.-P. Beck and R. Hesse, "Virtual synchronous machine," in Proc. 9th Int. Conf. Elect. Power Quality Utilisation, Oct. 2007, pp. 1–6.

- [9] Y. Cheng, R. Hesse, D. Turschner, and H.-P. Beck, "Improving the grid power quality using virtual synchronous machines," in *Proc. Int. Conf. Power Eng., Energy Elect. Drives*, May 2011, pp. 1–6.

- [10] Q.-C. Zhong, P.-L. Nguyen, Z. Ma, and W. Sheng, "Self-synchronized synchronverters: Inverters without a dedicated synchronization unit," *IEEE Trans. Power Electron.*, vol. 29, no. 2, pp. 617–630, Feb. 2014.

- [11] Q.-C. Zhong, "Virtual synchronous machines: A unified interface for grid integration," *IEEE Power Electron. Mag.*, vol. 3, no. 4, pp. 18–27, Dec. 2016.

- [12] H. Wu et al., "Small-signal modeling and parameters design for virtual synchronous generators," *IEEE Trans. Ind. Electron.*, vol. 63, no. 7, pp. 4292–4303, Jul. 2016.

- [13] L. Zhang, L. Harnefors, and H.-P. Nee, "Interconnection of two very weak AC systems by VSC-HVDC links using power-synchronization control," *IEEE Trans. Power Syst.*, vol. 26, no. 1, pp. 344–355, Feb. 2011.

- [14] L. Zhang, L. Harnefors, and H.-P. Nee, "Power-synchronization control of grid-connected voltage-source converters," *IEEE Trans. Power Syst.*, vol. 25, no. 2, pp. 809–820, May 2010.

- [15] W. Zhang, D. Remon, and P. Rodriguez, "Frequency support characteristics of grid-interactive power converters based on the synchronous power controller," *IET Renew. Power Gener.*, vol. 11, no. 4, pp. 470–479, 2017.

- [16] W. Zhang, A. M. Cantarellas, J. Rocabert, A. Luna, and P. Rodriguez, "Synchronous power controller with flexible droop characteristics for renewable power generation systems," *IEEE Trans. Sust. Energy*, vol. 7, no. 4, pp. 1572–1582, Oct. 2016.

- [17] A. D. Paquette and D. M. Divan, "Virtual impedance current limiting for inverters in microgrids with synchronous generators," *IEEE Trans. Ind. Appl.*, vol. 51, no. 2, pp. 1630–1638, Mar. 2015.

- [18] L. Huang, H. Xin, Z. Wang, L. Zhang, K. Wu, and J. Hu, "Transient stability analysis and control design of droop-controlled voltage source converters considering current limitation," *IEEE Trans. Smart Grid*, vol. 10, no. 1, pp. 578–591, Jan. 2019.

- [19] Z. Shuai, W. Huang, C. Shen, J. Ge, and Z. J. Shen, "Characteristics and restraining method of fast transient inrush fault currents in synchronverters," *IEEE Trans. Ind. Electron.*, vol. 64, no. 9, pp. 7487–7497, Sep. 2017.

- [20] S. Mukherjee, P. Shamsi, and M. Ferdowsi, "Improved virtual inertia based control of a grid connected voltage source converter with fault ride-through ability," in *Proc. IEEE NAPS*, Sep. 2016, pp. 1–5.

- [21] K. O. Oureilidis and C. S. Demoulias, "A fault clearing method in converter-dominated microgrids with conventional protection means," *IEEE Trans. Power Electron.*, vol. 31, no. 6, pp. 4628–4640, Jun. 2016.

- [22] K. Shi, W. Song, P. Xu, Z. Fang, and Y. Ji, "Low-voltage ride-through control strategy for a virtual synchronous generator based on smooth switching," *IEEE Access*, vol. 6, pp. 2703–2711, 2017.

- [23] C. Glöckler, D. Duckwitz, and F. Welck, "Virtual synchronous machine control with virtual resistor for enhanced short circuit capability," in *Proc. IEEE PES ISGT-Europe*, Sep. 2017, pp. 1–6.

- [24] A. Gkountaras, S. Dieckerhoff, and T. Sezi, "Evaluation of current limiting methods for grid forming inverters in medium voltage microgrids," in *Proc. IEEE ECCE*, Sep. 2015, pp. 1223–1230.

- [25] F. Welck, D. Duckwitz, and C. Gloeckler, "Influence of virtual impedance on short circuit performance of virtual synchronous machines in the 9-bus system," in *Proc. Conf. Sustain. Energy Supply Energy* Storage Syst. (NEIS), Sep. 2017, pp. 1–7.

- [26] S. F. Zarei, H. Mokhtari, M. A. Ghasemi, and F. Blaabjerg, "Reinforcing fault ride through capability of grid forming voltage source converters using an enhanced voltage control scheme," *IEEE Trans. Power Del.*, to be published.

- [27] P. Rodriguez, I. Candela, and A. Luna, "Control of PV generation systems using the synchronous power controller," in *Proc. IEEE ECCE*, Sep. 2013, pp. 993–998.

- [28] W. Zhang, "Control of grid connected power converters with grid support functionalities," Ph.D. dissertation, Univ. Politecnica Catalunya, Barcelona, Spain, 2017.

- [29] P. Rodriguez, I. Candela, C. Citro, J. Rocabert, and A. Luna, "Control of grid-connected power converters based on a virtual admittance control loop," in *Proc. 15th Eur. Conf. Power Electron. Appl. (EPE)*, Sep. 2013, pp. 1–10.

- [30] A. G. Yepes, F. D. Freijedo, O. Lopez, and J. Doval-Gandoy, "High-performance digital resonant controllers implemented with two integrators," *IEEE Trans. Power Electron.*, vol. 26, no. 2, pp. 563–576, Feb. 2011.

- [31] R. I. Bojoi, G. Griva, M. Guerriero, F. Farina, and F. Profumo, "Current control strategy for power conditioners using sinusoidal signal integrators in synchronous reference frame," *IEEE Trans. Power Electron.*, vol. 20, no. 6, pp. 1402–1412, Nov. 2005.

- [32] L. Huang, L. Zhang, H. Xin, Z. Wang, and D. Gan, "Current limiting leads to virtual power angle synchronous instability of droop-controlled converters," in *Proc. IEEE Power Energy Soc. Gen. Meeting (PESGM)*, Jul. 2016, pp. 1–5.

- [33] E. Afshari et al., "Control strategy for three-phase grid-connected PV inverters enabling current limitation under unbalanced faults," *IEEE Trans. Ind. Electron.*, vol. 64, no. 11, pp. 8908–8918, Nov. 2017.

- [34] S. Ma, H. Geng, L. Liu, G. Yang, and B. C. Pal, "Grid-synchronization stability improvement of large scale wind farm during severe grid fault," *IEEE Trans. Power Syst.*, vol. 33, no. 1, pp. 216–226, Jan. 2018.

Mads Graungaard Taul (S'17) received the B.Sc. and M.Sc. degrees in energy technology with specializing in electrical energy engineering and power electronics and drives from Aalborg University, Aalborg, Denmark, in 2016 and 2019, respectively, where he is currently pursuing the Ph.D. degree in power electronic systems with the Department of Energy Technology.

His current research interests include renewable energy sources and grid-connected converters, especially modeling and control of power electronic-

based power systems under grid fault conditions.

**Xiongfei Wang** (S'10–M'13–SM'17) received the B.S. degree in electrical engineering from Yanshan University, Qinhuangdao, China, in 2006, the M.S. degree in electrical engineering from the Harbin Institute of Technology, Harbin, China, in 2008, and the Ph.D. degree in energy technology from Aalborg University, Aalborg, Denmark, in 2013.

Since 2009, he has been with the Department of Energy Technology, Aalborg University, where he became an Assistant Professor in 2014, an Associate Professor in 2016, a Full Professor, and a Research

Program Leader for Electronic Power Grid Infrastructure in 2018. His current research interests include modeling and control of grid-interactive power converters, stability and power quality of power electronic-based power systems, active and passive filters.

Dr. Wang was a recipient of six IEEE Prize Paper Awards, the Outstanding Reviewer Award of IEEE TRANSACTIONS ON POWER ELECTRONICS in 2017, and the IEEE PELS Richard M. Bass Outstanding Young Power Electronics Engineer Award in 2018. He was selected into Aalborg University Strategic Talent Management Program in 2016. He serves as an Associate Editor for the IEEE TRANSACTIONS ON POWER ELECTRONICS, the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, and the IEEE JOURNAL OF EMERGING AND SELECTED TOPICS IN POWER ELECTRONICS.

**Pooya Davari** (S'11–M'13–SM'19) received the B.Sc. and M.Sc. degrees in electronic engineering from the University of Mazandaran, Babolsar, Iran, in 2004 and 2008, respectively, and the Ph.D. degree in power electronics from the Queensland University of Technology (QUT), Brisbane, Australia, in 2013.

From 2005 to 2010, he was involved in several electronics and power electronics projects as a Development Engineer. From 2010 to 2014, he investigated and developed high-power high-voltage power electronic systems for multidiscipli-

nary projects, such as ultrasound application, exhaust gas emission reduction, and tissue-materials sterilization. From 2013 to 2014, he was a Lecturer with QUT. He joined as a Post-Doctoral Researcher with the Department of Energy Technology, Aalborg University, Aalborg, Denmark, in 2014, where he is currently an Associate Professor. His current research interests include EMI/EMC in power electronics, WBG-based power converters, active frontend rectifiers, harmonic mitigation in adjustable-speed drives, and pulsed power applications.

Dr. Davari is currently a member of Joint Working Group six and Working Group eight at the IEC Standardization TC77A. He received a research grant from the Danish Council of Independent Research in 2016.

**Frede Blaabjerg** (S'86–M'88–SM'97–F'03) received the Ph.D. degree in electrical engineering from Aalborg University, Aalborg, Denmark, in 1995.

He was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor of power electronics and drives in 1998. Since 2017, he has been a Villum Investigator. His current research interests include power electronics and its applications such as in

wind turbines, PV systems, reliability, harmonics and adjustable speed drives. He has authored or coauthored more than 600 journal papers in power electronics and its applications. He is the coauthor of more than four monographs and editor of ten books in power electronics and its applications.

Dr. Blaabjerg was a recipient of 30 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award 2014, and the Villum Kann Rasmussen Research Award 2014. He received the Honoris Causa from University Politehnica Timisoara (UPT), Timisoara, Romania, and Tallinn Technical University (TTU), Tallinn, Estonia. He was the Editor-in-Chief of the IEEE Transactions on Power Electronics from 2006 to 2012. He has been a Distinguished Lecturer for the IEEE Power Electronics Society from 2005 to 2007 and for the IEEE Industry Applications Society from 2010 to 2011 as well as 2017 to 2018. From 2019 to 2020, he serves the President for the IEEE Power Electronics Society. He is the Vice-President of the Danish Academy of Technical Sciences as well. He was nominated in 2014–2018 by Thomson Reuters to be among the 250 most cited researchers in engineering in the world.