#### **Aalborg Universitet**

### An Overview of Condition Monitoring Techniques for Capacitors in DC-Link **Applications**

Zhao, Zhaoyang; Davari, Pooya; Lu, Weiguo; Wang, Huai; Blaabjerg, Frede

Published in: I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2020.3023469

Publication date: 2021

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Zhao, Z., Davari, P., Lu, W., Wang, H., & Blaabjerg, F. (2021). An Overview of Condition Monitoring Techniques for Capacitors in DC-Link Applications. *I E E Transactions on Power Electronics*, *36*(4), 3692-3716. Article 9195018. https://doi.org/10.1109/TPEL.2020.3023469

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

# An Overview of Condition Monitoring Techniques for Capacitors in DC-Link Applications

Zhaoyang Zhao, Student Member, IEEE, Pooya Davari, Senior Member, IEEE, Weiguo Lu, Member, IEEE, Huai Wang, Senior Member, IEEE, and Frede Blaabjerg, Fellow, IEEE

Abstract—Capacitors are widely used in dc links of power electronic converters to balance power, suppress voltage ripple, and store short-term energy. Condition monitoring (CM) of dc-link capacitors has great significance in enhancing the reliability of power converter systems. Over the past few years, many efforts have been made to realize CM of dc-link capacitors. This paper gives an overview and a comprehensive comparative evaluation of them with emphasis on the application objectives, implementation methods, and monitoring accuracy when being used. First, the design procedure for the condition monitoring of capacitors is introduced. Second, the main capacitor parameters estimation principles are summarized. According to these principles, various possible CM methods are derived in a step-by-step manner. On this basis, a comprehensive review and comparison of CM schemes for different types of dc-link applications are provided. Finally, application recommendations and future research trends are presented.

*Index Terms*—Condition monitoring, ceramic capacitors, dc link, electrolytic capacitors, film capacitors, reliability.

#### I. INTRODUCTION

C-LINK capacitors are an important part in the majority of electronic converters, which contribute to suppressing dc-link voltage ripple, absorbing harmonics, and balance the instantaneous power difference between the front-end and rear-end of converter systems [1], [2]. In some applications, they are also served to provide sufficient energy for transient and abnormal operations [3], [4]. However, capacitors are sensitive to thermal and electrical stresses and have the main disadvantage of finite lifespan and high degradation failure rate [6]–[8]. As reported in [8], about 30% of the faults in converters are caused by the degradation of capacitors, which makes them to be considered as the weakest link in power electronic systems [8]. With regard to this, monitoring the

Manuscript received May 27, 2020; revised July 31, 2020; accepted September 8, 2020. This work was supported by THE VELUX FOUNDATIONS under the VILLUM Investigator Grant REPEPS (Award Ref. No.: 00016591). (Corresponding authors: Huai Wang; Weiguo Lu)

- Z. Zhao is with the State Key Laboratory of Power Transmission Equipment & System Security and New Technology, Chongqing University, Chongqing 400044, China, and also with the Department of Energy Technology, Aalborg University, Aalborg 9220, Denmark (e-mail: zhaoyang.z@foxmail.com).

- P. Davari, H. Wang and F. Blaabjerg are with the Department of Energy Technology, Aalborg University, Aalborg 9220, Denmark (e-mail: pda@et.aau.dk; hwa@et.aau.dk; fbl@et.aau.dk).

- W. Lu is with the State Key Laboratory of Power Transmission Equipment & System Security and New Technology, Chongqing University, Chongqing 400044, China (e-mail: luweiguo@cqu.edu.cn).

degradation state of capacitors and scheduling maintenance before serious degradation or break down occurs have great significance for ensuring the reliable operation of dc-link applications and preventing possible catastrophic failures [9], [10].

In the last two decades, many efforts [11]-[101] have been made to realize the condition monitoring (CM) for capacitors in dc-link applications. Some of them are designed for capacitors dismantled from converters, i.e., offline schemes [11]-[24]. Others are implemented on-site in a real system, i.e., real-online and quasi-online schemes. Here, different types of dc-link applications are considered, such as adjustable speed drive (ASD) systems [25]-[47], photovoltaic (PV) grid-connected inverters [48]-[55], power factor correction (PFC) converters [56]-[61], and dc/dc buck and boost converters [62]-[101]. Moreover, the implementation methods are various. Some schemes monitor the dc-link capacitors using the existing voltage and current information, which can be obtained directly from controllers. Others are based on the signals sampled from additional hardware circuits and sensors. Generally, the research objective and implementation methods of condition monitoring are various. It is of great necessity to review these CM techniques for the following purposes.

- 1) Summarize the existing CM techniques and provide a reference for the researchers in this field.

- 2) Benchmark different CM schemes and identify the advantages and limitations of them, in order to provide suggestions for industrial application.

- 3) Analyze the existing challenges and explore future research opportunities.

Recently, some overview papers have been published to review the CM techniques for dc-link capacitors. In [102], Wang et al. reviewed the reliability of dc-link capacitors. However, their work mainly focuses on the reliability-oriented design. Only a brief discussion on the condition monitoring of dc-link capacitors is given. On this basis, Soliman et al. [103] give a review of the condition monitoring of capacitors in power electronic converters. Their work mainly focuses on the classification of the CM techniques. Based on three-category classification methods, the CM techniques are reviewed. Although the above-mentioned review papers give a comparison and analysis for CM techniques of capacitors, there are the following limitations.

1) A large amount of latest CM techniques for dc-link capacitors have emerged in recent years, which are not

considered in [102], [103]. Thereby, it is worth to investigate and discuss on the feasibility of the new state-of-the-art techniques.

- 2) A comprehensive design procedure of condition monitoring for capacitors is not given in [102], [103], which is important for industry application and academic research.

- 3) There is a lack of summarizing of monitoring principles and how to obtain the possible CM methods based on the basic principles.

- 4) No assessment of CM schemes for different types of dc-link applications is provided. For a certain type of converter, such as ASD systems, PV inverters, it is difficult to compare the existing CM schemes.

Therefore, the main goal of this paper is to provide a better understanding of both industry and academia on the suitability, feasibility, and implementation of CM schemes by answering the following: 1) What are the possible methods for the condition monitoring of capacitors and how to implement them? 2) For a given dc-link application (e.g., ASD systems), what is the difference between the existing CM schemes and how to choose the best one? To answer these questions, this paper gives an overview with emphasis on the derivation of CM methods and the discussion of different types of dc-link applications. The main contribution is given as follows.

- 1) A comprehensive design procedure of condition monitoring for capacitors is presented.

- 2) Summarizes the main capacitor parameters estimation principles and derives the various possible CM methods in a step-by-step manner.

- 3) Discussion and comparison of the existing CM schemes for main dc-link applications including ASD systems, PV inverters, PFC converters, and dc/dc converters. Based on this, giving suggested solutions for industrial applications.

This paper is organized as follows: Section II presents the design procedure of condition monitoring for capacitors. The derivation of CM methods is introduced in Section III. Section IV to Section VII are dedicated to suitability investigation of CM techniques for different types of dc-link applications. Finally, the suggested solutions for industrial applications, future challenges, and opportunities are drawn in Section VIII.

## II. DESIGN PROCEDURE FOR CONDITION MONITORING OF DC-LINK CAPACITORS

#### A. Capacitors for DC-Link Applications

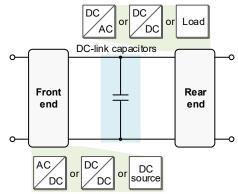

The typical structure of power electronic systems with dc-link capacitors is shown in Fig. 1. Based on the ripple current limitation of capacitors, a capacitor bank is usually placed at dc link based on series-parallel configuration. Generally, three types of capacitors are used in dc-link applications, which are the Aluminum Electrolytic Capacitors (Al-Caps), Metallized Polypropylene Film Capacitors (MPPF-Caps), and Multi-Layer Ceramic Capacitors (MLC-Caps) [102]. Fig. 2(a) shows a simplified model of the three types of capacitors, where C is the capacitance,  $R_{\rm ESR}$  and  $L_{\rm ESL}$  represent the equivalent series resistance (ESR) and the equivalent series inductance (ESL),  $R_{\rm p}$  denotes the insulation

Fig. 1. Typical structure of power electronic systems with dc-link capacitors.

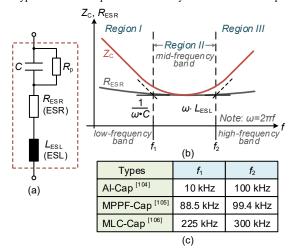

Fig. 2. Equivalent circuit model and impedance characteristics of capacitors. (a) Equivalent circuit model. (b) Impedance characteristics. (c) Typical values of  $f_1$ ,  $f_2$ , where the types of Al-Cap, MPPF-Cap, and MLC-Cap are SLPX [104] (470  $\mu$ F/450 V ), B32778-JX [105] (480  $\mu$ F/450 V) and KCM55WC71E107MH13 [106] (100  $\mu$ F/25 V) respectively.

resistance. According to the model, the dissipation factor (DF) is defined as  $\tan \delta = \omega \cdot R_{\text{ESR}} \cdot C$ . The impedance  $Z_{\text{C}}$  of capacitors is expressed as

$$Z_{\rm C} = \sqrt{R_{\rm ESR}^2 + \left(2\pi f \cdot L_{\rm ESL} - \frac{1}{2\pi f \cdot C}\right)^2}.$$

(1)

Using (1), Fig. 2(b) shows the impedance characteristics of capacitors [103]. It is found that the impedance is dominated by the capacitance C in Region I (i.e., low-frequency band,  $f \le f_1$ ),  $R_{\rm ESR}$  in Region II (i.e., mid-frequency band,  $f_1 \le f \le f_2$ ), and  $L_{\rm ESL}$ in Region III (i.e., high-frequency band,  $f \ge f_2$ ). Taking an Al-Cap, an MPPF-Cap and an MLC-Cap as examples, Fig. 2(c) gives the typical values of  $f_1$  and  $f_2$  at 25 °C [104]–[106], where the types of capacitor are SLPX (Al-Cap, 470  $\mu$ F/ 450 V), B32778-JX (MPPF-Cap, 480  $\mu F/$ 450 KCM55WC71E107MH13 (MLC-Cap, 100  $\mu$ F/ 25 V), respectively. Notice that C and  $R_{ESR}$  are the main degradation indicators of capacitors. Thereby, Region I and Region II (i.e., low-frequency and mid-frequency bands) are considered for CM, which is discussed in the following.

#### B. Design Procedure for Condition Monitoring

With the degradation of dc-link capacitors, a series of physical and chemical changes occur in the inside of capacitors,

Note: ≜ Suitable indicators for Al-Caps, ● suitable indicators for MPPF-Caps, ■ suitable indicators for MLC-Caps, † indicator increases, † indicator decreases

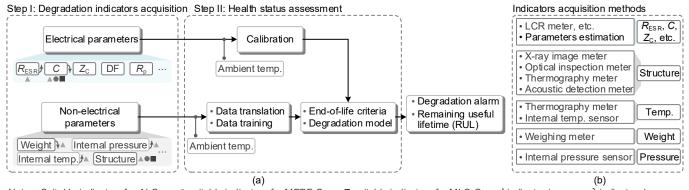

Fig. 3. Condition monitoring procedure for dc-link capacitors. (a) Condition monitoring procedure. (b) Degradation indicators acquisition methods.

TABLE I TYPICAL END-OF-LIFE CRITERIA OF CAPACITORS

|             | Al-Caps                        | MPPF-Caps      | MLC-Caps               |

|-------------|--------------------------------|----------------|------------------------|

| End-of-life | $C/C_0 < 80\%$                 | $C/C_0 < 95\%$ | C/C <sub>0</sub> < 90% |

| criteria    | $R_{\rm ESR}/R_{\rm ESR0} > 2$ | C/C() < 7570   | C/C0 < 7070            |

C - capacitance,  $R_{\rm ESR}$  - equivalent series resistance,  $C_0$  -initial capacitance,  $R_{\rm ESR0}$  -initial equivalent series resistance.

which will cause electrical parameters (e.g.,  $R_{\rm ESR}$ , C,  $Z_{\rm C}$ , DF,  $R_p$ ), and non-electrical parameters (e.g., weight, structure, internal temperature, internal pressure) to be changed [107]. Generally, these parameters can be chosen as the degradation indicators of capacitors. Based on this, Fig. 3(a) presents a condition monitoring procedure for dc-link capacitors. It mainly includes two steps, i.e., degradation indicators acquisition (Step I) and capacitor health status assessment (Step II). For Step I, Fig. 3(b) lists some commonly used parameter acquisition methods. It is found that industrial instruments including weighting meters [108], [109], X-ray image meters [110], optical inspection meter [111], acoustic detection meter [112], thermography meter [113], etc., are widely used to non-electrical parameters. Moreover, temperature sensors [114] and internal pressure sensors [115] are employed to obtain the internal temperature and pressure of capacitors. Due to the electrical parameters and non-electrical parameters of capacitors are easily influenced by the ambient temperature, which should be considered in Step II.

Considering the electrical characteristics of capacitors, the preferred indicators and their change trends for different types of capacitors are given in Fig. 3. Notice that some electrical parameters, such as  $Z_{\rm C}$ , DF, and  $R_{\rm p}$  can indicate the degradation of capacitors, however, it is difficult to measure them or use them to define the degradation level of capacitors. they are not the best lifetime indicators for CM. Similarly, the suitable non-electrical indicators are shown in Fig. 3. For Al-Caps, MPPF-Caps, and MLC-Caps, the change of internal structure can be used for condition monitoring. However, the changes in weight, internal pressure, and internal temperature are more suitable for Al-Caps.

Generally, electrical parameters can be measured using LCR meter, impedance analyzer, etc. However, parameter estimation based methods are widely used to estimate the electrical parameters of dc-link capacitors due to the capacitors are not

needed to be dismantled from converters in most cases, which will be detailed discussed in Section III.

#### 1) End-of-Life Criteria

As mentioned above,  $R_{\rm ESR}$  and C are the preferred electrical indicators for the condition monitoring of capacitors. In [102], the typical end-of-life criteria for Al-Caps, MPPF-Caps, and MLC-Caps have been summarized, as shown in Table I. Different from the electrical parameters, the non-electrical parameters of capacitors are dependent on capacity, materials, rated voltages and currents. Hence, there are no uniform end-of-life criteria for capacitors when choosing the non-electrical parameters as the degradation indicators. Generally, two categories of methods are applied to define the end-of-life criteria of capacitors.

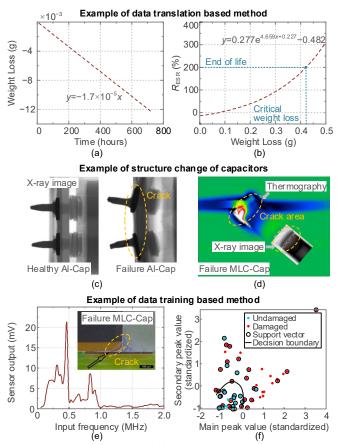

One category is to construct the relationship between electrical parameters and non-electrical parameters, i.e., data translation method. For Al-Caps, capacitor weight, internal pressure, and internal temperature are suitable non-electrical indicators. Taking weight loss as an example, Fig. 4(a) shows the average weight loss of an Al-Cap (Nichicon PW series, 450 V/68  $\mu$ F), Fig. 4(b) gives the relationship between weight loss and  $R_{\rm ESR}$  changes [108]. It is found that the weight of capacitors decreases with the degradation of capacitors, the critical weight loss can be defined at a 200% increase in  $R_{\rm ESR}$ . However, the weight change is in milligrams, which requires high-accuracy measurement devices.

Another non-electrical parameter based method is to identify the failure status of capacitors using the structure change of capacitors. Taking the X-ray image based method as an example, Fig. 4(c) shows the X-ray images of a healthy Al-Cap and a failure Al-Cap. However, due to the uncertainty of structure change, it is difficult to construct the relationship between the electrical parameters and structure change. Similarly, the main physical degradation indicator of MLC-Caps and MPPF-Caps is the structure change of capacitors [e.g., internal crack of MLC-Caps, as shown in Fig. 4(d)], which is difficult to construct the relationship between the electrical parameters and non-electrical parameters. Usually, some data training algorithms are used to distinguish the damaged and undamaged capacitors. In [112], an acoustics detection based method is applied to detect the micro-crack of capacitors, as shown in Fig. 4(e).

Fig. 4. Example of CM methods based on non-electrical parameters. (a) Average weight loss of a type of Al-Cap (Nichicon PW series, 450 V/68  $\mu$ F) [108]. (b) Weight loss versus  $R_{\rm ESR}$  changes of this type of Al-Cap [108]. (c) X-ray images of a healthy Al-Cap and a failure Al-Cap [109]. (d) Thermography and X-ray image of a failure MLC-Cap [113]. (e) Acoustic response of a failure MLC-Cap [112]. (f) SVM classifier fitted into observed MLC-Cap features [112].

Based on the acoustic response of MLC-Caps, the damaged and undamaged capacitors can be distinguished using a support vector machine (SVM) classifier, as shown in Fig. 4(f).

In summary, non-electrical parameters based CM schemes generally required high-cost measurement instruments. Moreover, there are no uniform end-of-life criteria, which are not the best schemes for condition monitoring.

#### 2) Degradation Models

Degradation models are used to calculate the remaining useful lifetime (RUL) of capacitors, which are generally based on electrical parameters. A simple degradation model of Al-Caps is described as [116], [117]

$$\begin{cases} C(t) = C_0 \cdot (1 + A_{AI} \cdot t) \\ R_{ESR}(t) = R_{ESR0} \cdot e^{B_{AI} \cdot t} \end{cases}$$

(2)

where t represents the operation time,  $C_0$  and  $R_{\rm ESR0}$  are the initial capacitance and ESR, respectively.  $A_{\rm Al}$  and  $B_{\rm Al}$  describe temperature-dependent degradation rates, which can be determined experimentally. For MPPF-Caps, the degradation model based on C is defined as [118]

$$C(t) = A_{\text{MPPF}} + \lambda_1 \cdot \lambda_2 \cdot e^{-(\lambda_1 \cdot t)}$$

(3)

where  $A_{\text{MPPF}}$  is a parameter which depends on  $C_0$ , and  $\lambda_1$ ,  $\lambda_2$  depend on the component characteristics and the applied

TABLE II EXPERIMENTAL PARAMETERS OF DEGRADATION MODELS

| Cap. types   | Experimental parameters                                | Test condition |

|--------------|--------------------------------------------------------|----------------|

| Al-Cap [116] | $A_{\rm al} = -4.899 \times 10^{-6}$                   | 300 kHz @      |

| Al-Cap [110] | $B_{\rm al} = 9.547 \times 10^{-5}$                    | 54.85−126.85°C |

| MPPF-Cap     | $\lambda_1 = 4.91 \times 10^{-8}, \ \lambda_2 = 0.001$ | Rated voltage  |

| [118]        | $\lambda_1 = 4.91 \times 10^{-8}, \lambda_2 = 0.001$   | @ 85 °C        |

| MLC-Cap      | k equals to 0 (for COG-type), 2.5                      | 2 times rated  |

| [119]        | (for X7R-type), 7 (for Y5V-type).                      | voltage @ 125℃ |

Fig. 5.  $R_{\rm ESR}$  and C variations versus temperature of a new capacitor (Type: SLPX 470  $\mu{\rm F}/$  450 V, datasheet [104]). (a)  $R_{\rm ESR}$  versus temperature. (b) C versus temperature.

stresses. Similarly, the degradation model of MLC-Caps is [119]

$$C(t) = C_0 \left( 1 - k \cdot \log t \right) \tag{4}$$

where k represents the maximum percent capacitance loss per decade hour, which is changed with the materials of capacitors. Taking the experimental results in [116], [118], and [119] as examples, Table II lists the experimental parameters of degradation models.

#### 3) Electrical Parameters Calibration

It is noticed that the electrical parameters of capacitors are easily influenced by the operating frequency, ambient temperature, which needs to be calibrated in condition monitoring systems [120], [121]. Usually, the operating frequency of capacitors in converters is dependent on the known switching frequency, however, the ambient temperature is changing. Taking the Al-Cap (Type: SLPX 470  $\mu$ F/ 450 V) as an example, Figs. 5(a) and 5(b) show  $R_{\rm ESR}$  and C variations versus temperature, respectively [104], which are given from a manufacturer datasheet. It is found that C increases as the ambient temperature  $T_a$  increases and  $R_{\rm ESR}$  decreases as  $T_a$  increases. The relationship between  $R_{\rm ESR}$ , C of a new capacitor and ambient temperature is given as [59]

$$\begin{cases} R_{\rm ESR} (T_{\rm a}) = \alpha_{\rm Al} + \beta_{\rm Al} e^{-T_{\rm a}/\gamma_{\rm Al}} \\ C(T_{\rm a}) = \chi_{\rm Al} + \lambda_{\rm Al} e^{-T_{\rm a}/\nu_{\rm Al}} \end{cases}, T_{\rm min} < T_{\rm a} < T_{\rm max}$$

(5)

where  $\alpha_{Al}$ ,  $\beta_{Al}$ ,  $\gamma_{Al}$ ,  $\chi_{Al}$ ,  $\lambda_{Al}$ , and  $\nu_{Al}$  are characteristics coefficients of capacitors, which are determined experimentally.  $T_{\min}$  and  $T_{\max}$  represent the minimum and maximum operating

temperatures of capacitors respectively, which are defined by the manufactures. For SLPX-type capacitors,  $T_{min}$  and  $T_{max}$  are -40 °C and +85 °C, respectively. Referring to Fig. 5, the variations of  $R_{\rm ESR}$  and C at different frequencies are different. Therefore, it is needed to define the estimation frequency to establish the relationships in (5) before condition monitoring. Assuming the estimation frequencies of  $R_{\rm ESR}$  and C are 10 kHz and 120 Hz respectively,  $\alpha_{Al}$ ,  $\beta_{Al}$ ,  $\gamma_{Al}$ ,  $\chi_{Al}$ ,  $\lambda_{Al}$ , and  $\nu_{Al}$  of this type of capacitor are 0.19, 1.16, 12.38, 489, -38.13, and 41.62, respectively. Notice that the relationship between C and  $T_a$  in (5) is based on the physical meaning of capacitors. It also can be written as  $C(T_a) = \gamma_{Al} + \lambda_{Al} \times T_a + \nu_{Al} \times T_a^2$  [56], which is based on the polynomial fitting. Here,  $\chi_{Al}$ ,  $\lambda_{Al}$ , and  $\nu_{Al}$  are 448.5, 0.84, and -0.0049, respectively. Although the relationship between  $R_{\rm ESR}$ , C, and  $T_{\rm a}$  can be constructed, it is recommended to monitor the capacitors at a relatively low temperature (e.g. 25 °C) due to the influence of degradation on  $R_{\rm ESR}$  and C is not significant at high temperatures [31].

The capacitance C of MPPF-Caps and MLC-Caps are also influenced by the temperature. For MPPF-Caps, the effects of temperature on C are dependent on the capacitor materials. For polypropylene (PP) capacitors, C decreases as the ambient temperature increases. For polyethylene terephthalate (PET) and Polyethylene naphthalate (PEN) capacitors, C increases as the ambient temperature increases. Generally, the relationship between ambient temperature  $T_a$  and capacitance is [122]

$$C(T_{\rm a}) = \alpha_{\rm MPPF} \cdot C_{\rm 20^{\circ}C} (T_{\rm a} - T_{\rm test}) + C_{\rm test}$$

(6)

where  $C_{\rm test}$  and  $T_{\rm test}$  are the capacitance and temperature under the testing condition,  $C_{20^{\circ}{\rm C}}$  is the reference capacitance at 20 °C.  $\alpha_{\rm MPPF}$  is the temperature coefficient,  $\alpha_{\rm MPPF}$  of PP, PET, and PEN capacitors are  $-250\times10^{-6}/K$ ,  $600\times10^{-6}/K$ , and  $200\times10^{-6}/K$  respectively. Similarly, the relationships between ambient temperature  $T_{\rm a}$  and capacitance of MLC-Caps can be constructed. Taking Class I MLC-CAps as an example, the relationship is [123]

$$C(T_a) = \alpha_{\text{MLC}} \cdot C_{\text{test}} (T_a - T_{\text{test}}) + C_{\text{test}}$$

(7)

where  $C_{\text{test}}$  represents the capacitance at  $T_{\text{test}}$  (i.e., 25 °C). According to the result of data fitting [124],  $\alpha_{\text{MLC}}$  is defined as 0.001629. For Class II and Class III ceramic capacitors, the relationship between C and  $T_{\text{a}}$  can also be constructed in the same way.

## III. DERIVATION OF CM METHODS FOR DC-LINK CAPACITORS

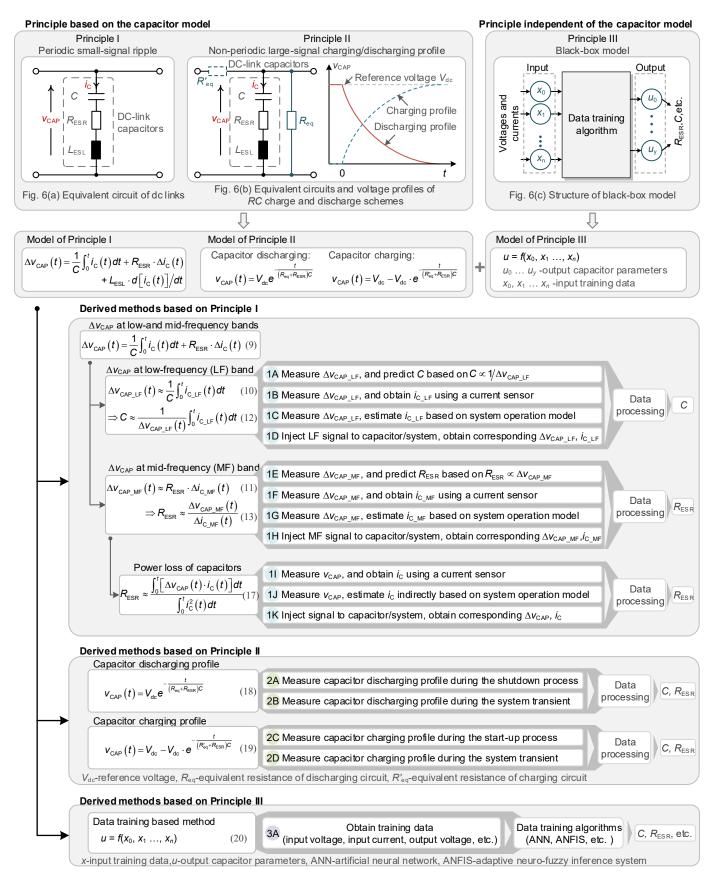

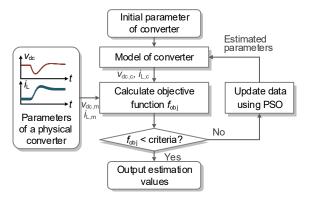

Comparing with industrial instruments measurement based methods, the parameters estimation based methods are more economic, which can be implemented without impairing the power converter operation. Fig. 6 presents a derivation procedure for parameters estimation methods of dc-link capacitors. The key steps are discussed as follows.

#### A. Parameters Estimation Principles

According to the dependence on the capacitor model, two main categories of principles are generally used to estimate the electrical parameters of dc-link capacitors. One is to estimate the parameters based on the capacitor impedance model, another is independent of the capacitor model. Furthermore,

according to the type of needed electrical signals, the first category principle includes two sub-types, i.e., periodic small-signal ripples based principle (Principle I) and non-periodic large-signal charging/discharging profiles based principle (Principle II). The second category principle treats the power electronic system as a black box, which does not need the specific capacitor model and converter model. Here, we define it as Principle III (i.e., black-box model).

Fig. 6(a) shows the equivalent circuit of dc-link capacitors, where  $v_{\text{CAP}}$  and  $i_{\text{C}}$  denote the voltage and current of capacitors respectively. Based on Ohm's law, the capacitor voltage ripple  $\Delta v_{\text{CAP}}$  and capacitor current ripple  $\Delta i_{\text{C}}$  having the following relationship

$$\Delta v_{\text{CAP}}(t) = \frac{1}{C} \int_{0}^{t} i_{\text{C}}(t) dt + R_{\text{ESR}} \cdot \Delta i_{\text{C}}(t) + L_{\text{ESL}} \cdot \frac{di_{\text{C}}(t)}{dt}.$$

(8)

Considering that  $L_{\rm ESL}$  is very small (on the order of 10–100 nH [41]) at the working frequency of converters (i.e., low-and mid-frequency bands in Fig. 2), which can be ignored in dc-link capacitors. Hence, (8) can be written as

$$\Delta v_{\text{CAP}}(t) = \frac{1}{C} \int_0^t i_{\text{C}}(t) dt + R_{\text{ESR}} \cdot \Delta i_{\text{C}}(t). \tag{9}$$

Furthermore,  $\Delta v_{CAP}$  at low-frequency band and mid-frequency band can be simplified as

$$\Delta v_{\text{CAP\_LF}}(t) \approx \frac{1}{C} \int_0^t i_{\text{C\_LF}}(t) dt$$

(10)

$$\Delta v_{\text{CAP MF}}(t) \approx R_{\text{ESR}} \cdot \Delta i_{\text{C MF}}(t)$$

(11)

where  $\Delta v_{\text{CAP\_LF}}$ ,  $\Delta i_{\text{C\_LF}}$  denote the ripples at low-frequency band, and  $\Delta v_{\text{CAP\_MF}}$ ,  $\Delta i_{\text{C\_MF}}$  indicate them at mid-frequency band. From (10) and (11), C and  $R_{\text{ESR}}$  can be estimated as

$$C \approx \frac{1}{\Delta v_{\text{CAP\_LF}}(t)} \int_0^t i_{\text{C\_LF}}(t) dt$$

(12)

$$R_{\rm ESR} \approx \frac{\Delta v_{\rm CAP\_MF}(t)}{\Delta i_{\rm CMF}(t)}.$$

(13)

From (12) and (13), it is easily found that C is inversely proportional to the voltage ripple  $\Delta v_{\text{CAP}}$  and  $R_{\text{ESR}}$  is proportional to  $\Delta v_{\text{CAP}}$  for a given  $i_{\text{C}}$ . Hence, (12) and (13) can be simplified as (14) and (15) when  $i_{\text{C}}$  is given.

$$C \propto 1/\Delta v_{\text{CAP LF}}$$

(14)

$$R_{\rm ESR} \propto \Delta v_{\rm CAP~MF}.$$

(15)

Referring to (11), the main power loss of capacitors is caused by  $R_{\rm ESR}$ . Considering different harmonic frequencies, the total power loss  $P_{\rm loss}$  of capacitors is

$$P_{\text{loss}} = \sum_{k=1}^{n} R_{\text{ESR},k} I_{\text{C_RMS},k}^{2}$$

(16)

where  $R_{\rm ESR,k}$  and  $I_{\rm C\_RMS,k}$  represent the ESR and the root mean square (RMS) current for each harmonic k [126]. Although (16) can be used to calculate ESR, it is difficult to determine  $R_{\rm ESR,k}$  for each harmonic k. Moreover, the end-of-life criteria (e.g.,  $R_{\rm ESR}/R_{\rm ESR0} > 2$ ) provided by manufacturers are usually based on a frequency region (i.e., mid-frequency band) without considering a specified frequency. As discussed in [38],  $R_{\rm ESR}$  calculated by the average power loss  $P_{\rm loss}$  and the total RMS current  $I_{\rm C\_RMS}$  can approximately represent the actual ESR of

- Note:1) The methods 1A and 1E, 1B and 1F, 1C and 1G, 1D and 1H can be grouped together respectively when using (9). Here, C and R<sub>ESR</sub> are approximately estimated under the same frequency, such as low frequency or mid frequency.

- 2) Fig. 6(b), Eqs. (17) and (18) are examples of Principle II. For different charging or discharging modes, the profiles and equations are different.

Fig. 6. Derivation procedure for parameters estimation methods of dc-link capacitors.

capacitors in power electronic converters. Therefore,  $R_{\rm ESR}$  is approximately calculated as

$$R_{\rm ESR} \approx \frac{\overline{P}_{\rm loss}}{I_{\rm c_{\rm LMS}}^2} = \frac{\int_0^t \left[ \Delta v_{\rm CAP}(t) \cdot i_{\rm C}(t) \right] dt}{\int_0^t i_{\rm C}^2(t) dt}.$$

(17)

Principle II is based on the large-signal discharging/charging profile, as shown in Fig. 6(b). The left part of Fig. 6(b) shows the equivalent circuit of capacitor discharging and charging schemes, where  $R_{\rm eq}$  and  $R'_{\rm eq}$  represent the equivalent resistances of discharging circuits and charging circuits respectively. The right part gives the discharging and charging profiles, where,  $V_{\rm dc}$  denotes the reference value of capacitor voltage. During the discharging period, the capacitor voltage is expressed as

$$v_{\text{CAP}}\left(t\right) = V_{\text{dc}} e^{-\frac{t}{\left(R_{\text{cq}} + R_{\text{ESR}}\right)C}}.$$

(18)

During the charging period, the capacitor voltage is

$$v_{\text{CAP}}(t) = V_{\text{dc}} - V_{\text{dc}} \cdot e^{-\frac{t}{\left(R'_{\text{eq}} + R_{\text{ESR}}\right)C}}.$$

(19)

By solving (17) and (18),  $R_{\rm ESR}$  and C can be estimated.

Principle III is based on the black-box model, as shown in Fig. 6(c). Here, the power electronic system to be monitored is treated as a black box. Taking the voltage and current signals of systems as input data, the capacitor parameters can be estimated using data training algorithms (e.g., artificial neural network) without considering the specific capacitor model and converter model. The relationship between capacitor parameters and input signals can be obtained using training algorithms, i.e.,

$$u = f(x_0, x_1 ..., x_n)$$

(20)

where  $u_0 u_y$  denote the output capacitor parameters, and  $x_0$ ,  $x_1 x_n$  are the input training data.

#### B. Derivation of Condition Monitoring Methods

Based on the three key principles, the condition monitoring methods for dc-link capacitors can be derived in a step by step manner. There exist 16 derived methods, as shown in Fig. 6.

#### 1) Derived Methods based on Principle I

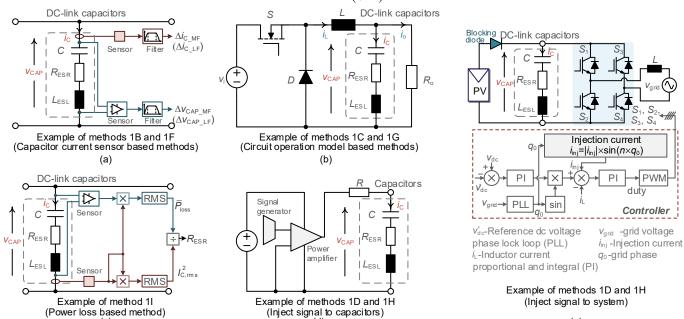

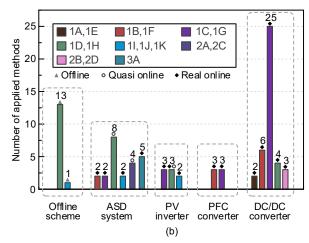

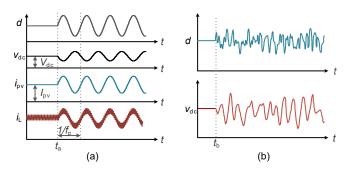

There exist 11 derived methods based on Principle I, where methods 1A and 1E use the voltage ripple to approximately estimate the capacitor parameters without dependency on the capacitor current. The methods 1B-1D, 1F-1H and 1I-1K utilize sampled or estimated capacitor current to calculate  $R_{\rm ESR}$  or C, which are illustrated using the examples in Fig. 7.

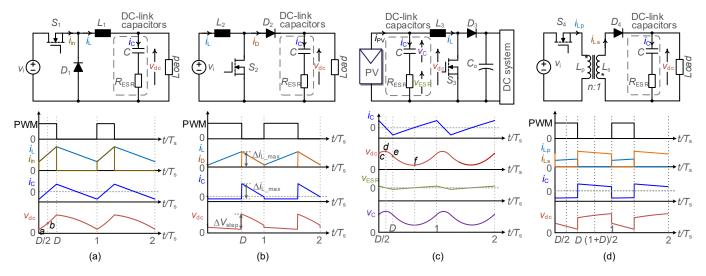

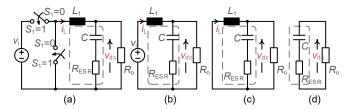

Fig. 7(a) shows an implementation example of methods 1B and 1F. Here, the capacitor current is directly sampled by a current sensor. To accurately obtain  $R_{\rm ESR}$  or C, a band-pass filter and a low-pass filter are required respectively. To avoid using capacitor current sensors, the methods 1C and 1G utilize the circuit operation model to indirectly obtain  $i_{\rm C}$ . Referring to Fig. 7(b), taking a buck converter as an example, it is easily found that  $i_{\rm C}=i_{\rm L}-i_{\rm o}$ , where  $i_{\rm L}$  and  $i_{\rm o}$  are inductor current and load current respectively.

The implementation of schemes 1D and 1H can be divided into two categories. One is to inject current into the tested capacitor directly, as shown in Fig. 7(d). Here, a signal generation circuit including a signal generator and a power amplifier is employed to inject current signals at given frequencies to the tested capacitor. The injected signal can be sinusoidal waves, square waves, triangle waves, etc. Another is to inject a perturbation signal into the power electronic systems. Taking a photovoltaic (PV) grid-connected inverter as an example, Fig. 7(e) gives the implementation scheme. Here, a current at hth harmonic frequency is injected into the grid, which causes (h-1)th and (h+1)th voltage and current ripples to appear on the dc-link capacitors. Then,  $R_{\rm ESR}$  and C can be estimated using the voltage and current ripples at (h-1)th or (h+1)th.

Fig. 7. Implementation examples of derived methods based on Principle I. (a) Example of methods 1B and 1F. (b) Example of methods 1C and 1G based on a buck converter. (c) Examples of methods 1I. (d) Example of method 1D and 1H, here, extra signals are injected to capacitors. (e) Example of method 1D and 1H based on a PV inverter, here, extra signals are injected to systems.

TABLE III DESCRIPTION OF DERIVED METHODS 1A-1H

| Derived methods | Description                             |

|-----------------|-----------------------------------------|

| 1A, 1E          | Capacitor voltage based methods         |

| 1B, 1F          | Capacitor current sensor based methods  |

| 1C, 1G          | Circuit operation model based methods   |

| 1D, 1H          | External signal injection based methods |

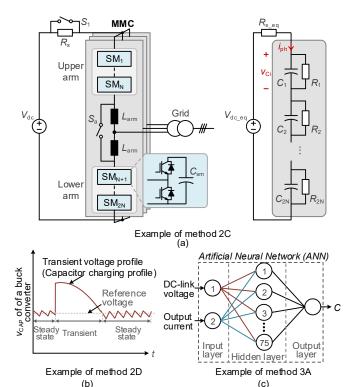

Fig. 8. Implementation examples of derived methods based on Principles II and III. (a) Example of method 2C based on an MMC. (b) Example of method 2D based on a buck converter. (c) Example of method 3A.

Notice that the methods 1A and 1E, 1B and 1F, 1C and 1G, 1D and 1H can be grouped together respectively when using (9). The description is listed in Table III. Here, C and  $R_{\rm ESR}$  are approximately estimated under the same frequency, such as low frequency or mid frequency.

According to (17),  $R_{\rm ESR}$  can be calculated using power losses of capacitors. Fig. 7(c) shows the implementation of the method 1I. It is similar to the method 1B, however, a band-pass filter is not required. The implementation of method 1J and 1K are similar to 1G and 1H, respectively.

#### 2) Derived Methods based on Principles II and III

There exist 4 derived methods based on Principle II, where 2A, 2B are based on the discharging profile, and 2C, 2D are based on the charging profile.

The methods 2A and 2C obtain the discharging or charging profiles during the shutdown process or start-up process of converters. Referring to Fig. 6(b), during the shutdown process of converter, the dc-link capacitors discharge through the equivalent resistor  $R_{\rm eq}$ . The capacitor parameters can be estimated based on the discharging profile and (18). During the start-up process of converter, the capacitors charge through  $R'_{\rm eq}$ . The capacitor parameters can be estimated based on the

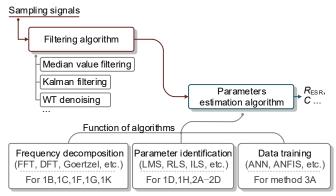

Note: FFT-fast Fourier transform, DFT-discrete Fourier transform,LMS-least mean squares,RLS-recursive least squares, ILS-iterative least squares, ANN-artificial neural network, ANFIS-adaptive neuro fuzzy inference system, WT-wavelet transform.

Fig. 9. Data processing procedure for condition monitoring.

charging profile and (19). Taking modular multilevel converters (MMCs) as an example, the left part of Fig. 8(a) shows the circuit of a three-phase MMC, which including the detailed circuit of a sub-module (SM) [127]. During the DC-side start-up process, the power switches  $S_1$  turns OFF and S<sub>a</sub> turns ON, the equivalent circuit of a signal-phase MMC is given in the right part of Fig. 8(a). Here,  $R_s$  and  $R_{seq}$  represent the equivalent start-up resistance with/without considering the resistance of diodes, N denotes the number of SM in each arm,  $C_i$  and  $R_i$  are the capacitance and resistance of the *i*-th SM. Referring to the right part of Fig. 8(a), the capacitors are charged through  $R_{\rm s}$  eq during this start-up process. Assuming each SM has the same phase current  $i_{ph}$  and the same capacitor voltage  $v_{Ci}$ , the capacitances can be estimated using the equivalent DC voltage  $V_{\rm dc}$  eq,  $R_{\rm s}$  eq and the charging profile [see Fig. 6(b)].

Similar to the shutdown and start-up processes, the capacitors will be discharged or charged during transients. Taking buck converters as examples, Fig. 8(b) shows the voltage profile (i.e., capacitor charging profile) during an unloading transient. Based on the relationship between charging profile and capacitor parameters,  $R_{\rm ESR}$  and C can be estimated [99].

The method 3A is based on Principle III, an implementation example is shown in Fig. 8(c). Here, an artificial neural network (ANN) algorithm is used to estimate the capacitance for an ac/dc/ac system. Taking dc-link voltage and output current as training data, the capacitance can be estimated based on the data training algorithm.

#### C. Data Processing

Referring to Fig. 6, data processing is a key link of the condition monitoring for dc-link capacitors. Fig. 9 shows the general procedure of data processing for condition monitoring. First, the sampling signals are filtered using filtering algorithms including median value filtering, Kalman filtering, wavelet transform denoising, etc. Then parameter estimation algorithms are employed to obtain capacitor parameters. For methods 1B, 1C, 1F,1G, and 1K, the key issue is to obtain the low-frequency or mid-frequency components of capacitor voltage and capacitor current. Usually, frequency decomposition

algorithms including fast Fourier transform (FFT) algorithm, discrete Fourier transform (DFT) algorithm, Goertzel algorithm, etc., are used to extract the low-frequency or mid-frequency components of  $v_{\text{CAP}}$  and  $i_{\text{C}}$ .

For methods 1D, 1H, and 2A-2D, adaptive filter algorithms including least mean squares (LMS) algorithm, recursive least squares (RLS) algorithm, iterative least squares (ILS) algorithm, etc. are widely used to identify  $R_{\rm ESR}$  and C in equations (9)–(11), (18) and (19). Moreover, some optimization algorithms, such as particle swarm optimization (PSO) algorithm, genetic algorithm (GA) can be used to identify capacitor parameters.

For method 3A, data training algorithms including artificial neural network (ANN) algorithm, adaptive neuro-fuzzy inference system (ANFIS) algorithm, support vector regression (SVR) algorithm, etc., are widely used for condition monitoring.

## IV. APPLICATION OF DERIVED CONDITION MONITORING METHODS

#### A. Overview of the Application of CM Methods

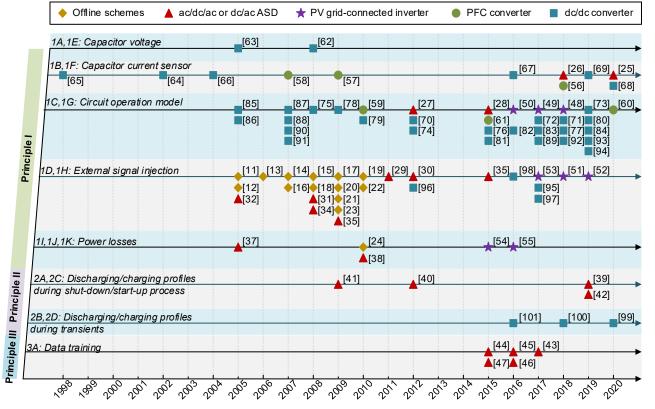

Based on the derived methods, various condition monitoring techniques for dc-link capacitors have been proposed in [11]–[109]. Fig. 10 gives the development history of these techniques. It is found that the research on the condition monitoring techniques for dc-link capacitors started at the end of the 1990s, and it has become a hot issue in the past decade. Fig. 11(a) shows a statistical analysis of CM techniques for different types of dc-link applications, where the offline

schemes estimate the capacitor parameters under the case that the capacitors are dismantled from converters, which can be applied for all types of converters. Different from offline schemes, real-online or quasi-online schemes (CM under special test conditions, such as start-up and shutdown process) can be implemented on-site in a real system, which are widely used for condition monitoring of capacitors in adjustable speed drive (ASD) systems, photovoltaic (PV) inverters, power factor correction (PFC) converters, dc/dc converters, etc.

From Fig. 11(a), it is found that the dc-dc converters and ac/dc/ac or dc/ac ASD systems are the most popular research objectives. More than 60% of CM techniques are proposed for these two types of applications. For different dc-link applications, Fig. 11(b) gives the distribution of CM methods, where the ordinate shows the number of applied methods. Taking ASD systems and dc/dc converters as examples, it is found the signal injection based method (1D, 1H) and circuit operation model based method (1C, 1G) are widely used respectively. Moreover, from the perspective of availability, Fig. 11(b) illustrates that the real-online scheme is the most popular one for CM.

For different types of dc-link applications, the detailed discussions of CM methods are given in Section V to Section VII. Offline monitoring techniques are independent of topologies of converters, which are investigated in the following part.

#### B. Offline Monitoring Techniques

1) Implementation of offline monitoring schemes

Generally, industrial instruments including LCR meter,

Fig. 10. Development history of the condition monitoring techniques for dc-link capacitors.

Fig. 11. Statistics of condition monitoring techniques for dc-link applications. (a) Statistics of research objects. (b) Condition monitoring schemes for different types of dc-link applications.

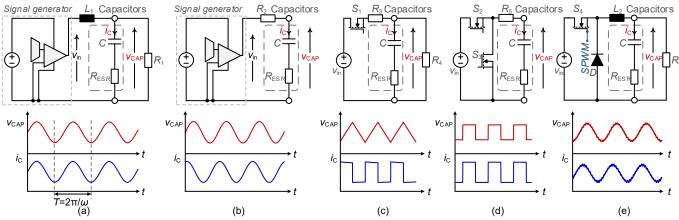

Fig. 12. Schematics of CM schemes for dismantled capacitors, here,  $L_{\rm ESL}$  is ignored. (a) LC circuit with sinusoidal signal injection scheme. [12]. (b) RC circuit with sinusoidal signal injection scheme [13]–[19]. (c) Charge-discharge circuit scheme [19], [20]. (d) Square wave signal injection scheme [21], [22]. (e) Buck converter scheme [23].

impedance analyzer, etc., can be used for the offline measurement of  $R_{\rm ESR}$  and C of capacitors. Considering the high price of these instruments, various low-cost offline measurement techniques have been presented in [11]–[24]. Ignoring  $L_{\rm ESL}$ , a simple offline scheme is shown in Fig. 12 (a). Here, a sinusoidal signal is injected into an LC circuit, then  $R_{\rm ESR}$  near the resonance frequency  $\omega$  of an Al-Cap is estimated as [11], [12]

$$R_{\rm ESR} = \sqrt{\left(\frac{v_{\rm CAP}L_{\rm l}C\omega}{v_{\rm in}}\right)^2 - \frac{1}{\omega^2}} / C \tag{21}$$

where  $v_{in}$  is the injected sinusoidal signal. However, this scheme ignores the effect of frequency on  $R_{ESR}$  and C.

To overcome the aforementioned shortcomings, [13]–[19] use an RC circuit to estimate the capacitor parameters. Referring to Fig. 12(b), a modulated sinusoidal signal is injected to the RC circuit, which causes sinusoidal voltage  $v_{\text{CAP}}$  and current  $i_{\text{C}}$  on the capacitor. According to the relationship between  $v_{\text{CAP}}$  and  $i_{\text{C}}$ ,  $i_{\text{ESR}}$  and  $i_{\text{C}}$  can be estimated by using analysis algorithms, such as Laplace transform [13], Newton-Raphson (NR) algorithm [14], [15], discrete Fourier transform (DFT) [16], [17], and least mean square (LMS) algorithm [18]–[19].

Besides the sinusoidal signal generation circuit, a charge-discharge circuit is proposed in [19], [20], as shown in Fig. 12(c). Using the LMS algorithm, the capacitor parameters are calculated based on the relationship between  $v_{\text{CAP}}$  and  $i_{\text{C}}$ . In [21], [22], another RC circuit scheme is proposed, as shown in Fig. 12(d). Here, the injection signal is a square wave, which is different from that of Fig. 12(b). Using  $v_{\text{CAP}}$  and  $v_{\text{in}}$ , C and  $R_{\text{ESR}}$  are estimated at low-frequency and high-frequency bands respectively. Referring to Fig. 12(e), a buck converter with a sinusoidal pulse width modulator (SPWM) is also proposed for offline measurement of capacitors [23]. Using DFT,  $R_{\text{ESR}}$  and C are calculated based on the analysis of  $v_{\text{CAP}}$  and  $i_{\text{C}}$ .

All of the above-mentioned schemes are implemented based on methods 1D and 1H. Different from that, [24] utilizes the power loss on capacitors to estimate capacitor parameters. Referring to Fig. 12(b), a low-frequency sinusoidal current is injected into the capacitor, then  $R_{\rm ESR}$  and C are calculated as

$$\begin{cases}

R_{\text{ESR}} = \overline{P}T / \int_{0}^{T} i_{C}^{2}(t) dt \\

C = T / 2\pi \sqrt{\left(\int_{0}^{T} v_{\text{CAP}}^{2}(t) dt\right) / \left(\int_{0}^{T} i_{C}^{2}(t) dt\right) - R_{\text{ESR}}^{2}}

\end{cases} (22)$$

TABLE IV ESTIMATION ERROR OF SINUSOIDAL WAVE INJECTION CIRCUIT WITH DIFFERENT ALGORITHM

| Injection<br>signal        | Methods | Algori-<br>thms | Error of $C \delta_{\mathrm{C}}$ | Error of $R_{\rm ESR}$ $\delta_{ m R}$ | Ref.         |

|----------------------------|---------|-----------------|----------------------------------|----------------------------------------|--------------|

| a: :11                     | 1D, 1H  | Laplace         | δ <sub>C_120Hz</sub> =17.6%      | δ <sub>R_750Hz</sub> =18%              | [13]<br>[14] |

| Sinusoidal<br>wave circuit |         | NR              | $\delta_{C_{120Hz}}=1.5\%$       | $\delta_{R_{120Hz}}=19.8\%$            | [14]         |

| [Fig. 12(b)]               |         | DFT             | $\delta_{C_{120Hz}} = 1.5\%$     | $\delta_{R_{1kHz}}=5.9\%$              | [17]         |

|                            |         | LMS             | $\delta_{C_{120Hz}} = 0.8\%$     | $\delta_{R_{lkHz}}=0.3\%$              | [19]         |

|                            | 1K      | N/A             | $\delta_{\rm C~50Hz}$ =4.7%      | $\delta_{R}_{50Hz}=3.5\%$              | [24]         |

NR-Newton Raphson algorithm, DFT-discrete Fourier transform algorithm, LMS-least mean square algorithm.

Table V Estimation Error for Different Types of Signal-Injection Circuit

| Signal injection circuit                 | Algorithms | Error of $C \delta_{\mathbb{C}}$                                                      | Error of $R_{\rm ESR}$ $\delta_{ m R}$                      | Ref. |

|------------------------------------------|------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------|------|

| Sinusoidal wave circuit [Fig. 12(b)]     | LMS        | $\delta_{C_{120Hz}} = 0.8\%$<br>$\delta_{C_{1kHz}} = 0.3\%$                           | $\delta_{R_{120Hz}} = 1.6\%$<br>$\delta_{R_{1kHz}} = 9.7\%$ | [19] |

| Charge-discharge<br>circuit [Fig. 12(c)] | LMS        | $\delta_{\text{C}_{120\text{Hz}}} = 1.9\%$<br>$\delta_{\text{C}_{1k\text{Hz}}} = 1\%$ | $\delta_{R_{120Hz}} = 4.1\%$<br>$\delta_{R_{1kHz}} = 0.4\%$ | [19] |

| Square-wave circuit [Fig. 12(d)]         | N/A        | δ <sub>C_1kHz</sub> =4.9%                                                             | $\delta_{R_{150kHz}}=8.8\%$                                 | [22] |

| Buck converter [Fig. 12(e)]              | DFT        | N/A                                                                                   | δ <sub>R_1kHz</sub> =3%                                     | [23] |

LMS-least mean square algorithm, DFT-discrete Fourier transform algorithm.

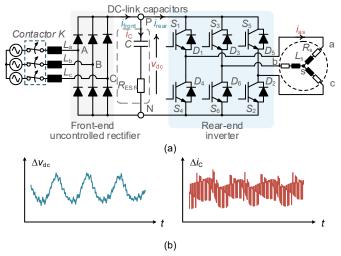

Fig. 13. Adjustable speed drive (ASD) system with a front-end diode rectifier [26], here,  $L_{\rm ESL}$  is ignored. (a) System structure. (b) Capacitor voltage ripple and current ripple.

where T is the period of the sinusoidal signal and  $\overline{P}$  is the capacitor average power.

#### 2) Discussion of offline monitoring schemes

As mentioned above, the offline schemes are mainly based on methods 1D, 1H and 1K (i.e., signal injection scheme). Various data processing algorithms including Laplace transform, DFT, LMS, etc., are used. To compare the estimation accuracy of these algorithms, Table IV lists the estimation errors of C and  $R_{\rm ESR}$ . Here, sinusoidal signal injection scheme [see Fig. 12(b)] is taken as examples. It illustrates that the estimation errors of the Laplace transform and NR algorithm are relatively high. And, the NR algorithm is not suitable for the estimation of  $R_{\rm ESR}$ . For the DFT algorithm and LMS algorithm, their estimation errors are relatively low and the error of the LMS algorithm is minimum.

To compare the estimation accuracy of different types of signal injection circuit, Table V summarize the estimation error

of these schemes. Due to the lack of data processing algorithms, the estimation accuracy of square-wave circuit [see Fig. 12(d)] is relatively low. For capacitance estimation, the estimation accuracy of sinusoidal wave circuit [see Fig. 12(b)] is larger than that for charge-discharge circuit [see Fig. 12(c)]. And the estimation accuracy decreases as the injection-signal frequency increases. For ESR estimation, the charge-discharge circuit [see Fig. 12(c)] has a relatively high estimation accuracy. And the estimation error decreases as the injection-signal frequency increases.

In summary, a low-frequency sinusoidal current injection based scheme is more suitable for capacitance estimation. A square-wave current with relatively high frequency is more suitable for ESR estimation.

#### V. CM FOR CAPACITORS IN AC/DC/AC OR DC/AC ASD SYSTEMS

Adjustable speed drive (ASD) systems are widely used in industrial and residential applications. Various CM schemes for capacitors in ASD systems have been presented in [25]–[47].

#### A. Implementation of CM Schemes based on Principle I

#### 1) Capacitor current sensor based methods (1B, 1F)

A generic structure of two-stage ASD systems with a front-end diode rectifier is shown in Fig. 13(a). The corresponding dc-link voltage waveform and capacitor current waveform are shown in Fig. 13(b). In [25], [26], a CM scheme based on 1B and 1F is proposed to estimate the capacitor parameters of this system. Firstly, the capacitor voltage ripple and current ripple are directly measured by sensors, as shown in Fig. 7(a). Then data processing algorithms, such as the Goertzel algorithm [25] and fast Fourier transform (FFT) [26] are applied to analyze the sampled waveforms. Based on equations (12) and (13), C and  $R_{\rm ESR}$  are estimated using the extracted mid-frequency and low-frequency components of capacitor current ripple  $\Delta i_{\rm C}$  and voltage ripple  $\Delta v_{\rm CAP}$ .

#### 2) Circuit operation model based methods (1C, 1G)

To avoid using a capacitor current sensor, [27], [28] indirectly obtain capacitor current using  $i_c = i_{front} - i_{rear}$ , where  $i_{front}$  and  $i_{rear}$  represent the front-end current and rear-end current respectively. Referring to Fig. 13(a), when  $i_{rear} = 0$ ,  $i_c$  equals  $i_{front}$ . Based on the estimated capacitor current,  $R_{ESR}$  and C can be calculated using equations (12) and (13).

#### 3) External signal injection based methods (1D, 1H)

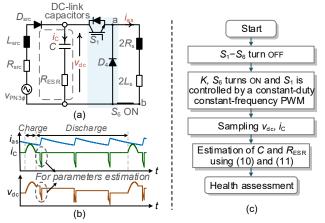

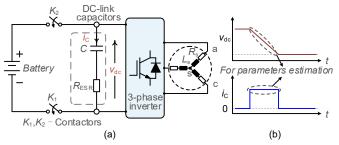

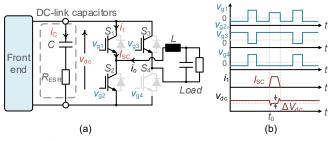

In [29], [30], a signal injection scheme is proposed to estimate the capacitor parameters of ASD systems. Referring to Fig. 13(a), condition monitoring is taken when the motor is stopped. Here, the contactor K is keeping ON. When  $S_6$  is turned ON and  $S_1$  is controlled by a constant-duty constant-frequency PWM, the charge on the capacitor can be discharged through the phase a and phase b windings, which causes voltage and current ripples on the dc link. The equivalent circuit and corresponding waveforms are given in Fig. 14(a) and Fig. 14(b) respectively. Using ripples  $\Delta v_{\rm dc}$  and  $\Delta i_{\rm C}$ , C and  $R_{\rm ESR}$  can be estimated based on equations (10) and (11). The flowchart is shown in Fig. 14(c). In [31], the same method is used for a single-phase motor drive system.

$v_{\rm PN3\phi^-}$  rectified source  $L_{\rm src^-}$  source inductance  $R_{\rm src^-}$  source resistance  $D_{\rm src^-}$  ideal diode  $i_{\rm as^-}$  phase a current  $L_{\rm s^-}$  per-phase stator inductance  $R_{\rm s^-}$  per-phase stator resistance

Fig. 14. Current injection based scheme [29], here,  $L_{\rm ESL}$  is ignored. (a) Equivalent circuit under CM condition. (b) Key waveforms. (c) Flowchart of the monitoring scheme.

Fig. 15. Block diagram for monitoring capacitors in a PWM converter [32], here,  $L_{\rm ESL}$  is ignored. (a) Structure of a PWM converter. (b) Block diagram of a signal injection based scheme.

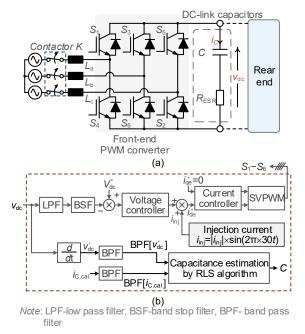

Besides a diode rectifier, a pulse-width modulation (PWM) converter is widely used as the first stage of two-stage ASD systems, as shown in Fig. 15(a). In [32]–[35], Dong-Choon *et al.* utilize current injection-based schemes to estimate the capacitor parameters of PWM converters [front end of Fig. 15(a)] and two-stage ac/dc/ac converters. Referring to Fig. 15(b), at no-load condition, a controlled AC current  $i_{\rm inj}$  with a lower frequency (30 Hz) than the line frequency is injected into the front-end PWM converter, which induces voltage ripples on the dc link. Using (10) as well as the extracted  $v_{\rm dc}$  and  $i_{\rm dc}$  at 30 Hz, C is estimated based on the recursive least square (RLS) algorithm [32], i.e.,

Fig. 16. Variable resistance network based capacitor discharge scheme [39], here,  $L_{\rm ESL}$  is ignored. (a) Variable resistance network. (b) Discharge profile. (c) Flowchart of the monitoring scheme.

$$C = \frac{\text{BPF}\left[i_{\text{C,cal}}\right]}{\text{BPF}\left[v_{\text{dc}}'\right]}$$

(23)

where BPF[·] represents the band-pass filter quantity,  $i_{C,cal}$  is the derived capacitor current based on the system operation mode.

Utilizing the similar schemes, the capacitor parameters of three-phase systems or single-phase systems are estimated in [33]–[35], where [33] is based on current injection and [34], [35] are based on voltage injection. Notice that for an ASD system with a front-end uncontrolled rectifier, it is impossible to inject current signals into the front end at no-load condition. Therefore, [36] injects the AC current signal into the rear-end inverter when the motor operates in the regenerative model.

#### 4) Power losses based method (11)

Based on the estimated method in Fig. 7(d), [37], [38] calculated  $R_{\rm ESR}$  using  $R_{\rm ESR} = P_{\rm dc,rms}/I_{\rm C,rms}^2$ . In [37], the RMS values  $P_{\rm dc,rms}$ ,  $I_{\rm C,rms}^2$  are obtained using analog RMS converters. In [38], the RMS values are calculated in a microcontroller.

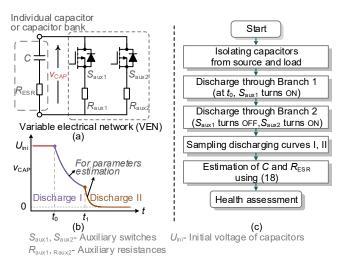

#### B. Implementation of CM Schemes based on Principle II

Usually, the capacitor discharging profile is obtained during the shutdown process of systems. In [39], an auxiliary capacitor-discharge network is proposed for two-stage ac/dc/ac converters. Referring to Fig. 16 (a), a variable electric network (VEN) consisting of auxiliary switches and resistors is connected in parallel with dc-link capacitors (individual capacitor or capacitor bank). After the converter shuts down, the dc-link capacitors are isolated from the power source and load. The charge in capacitors can be released through the auxiliary resistor net. By controlling the switching of auxiliary switches  $S_{\text{aux}1}$  and  $S_{\text{aux}2}$ , a two-period discharge trajectory is formulated, as shown in Fig. 16(b). Sampling the discharge profile, C and  $R_{\text{ESR}}$  can be estimated based on (18). The flowchart is shown in Fig. 16(c).

Besides the additional discharging path, motor windings and impedance networks in the converter systems are used to form a discharge path. In [40], a constant-current discharge scheme is

Fig. 17. Constant-current discharge based scheme [40], here,  $L_{\rm ESL}$  is ignored. (a) Electrical configuration of an electric vehicle. (b) Constant-current discharge profiles.

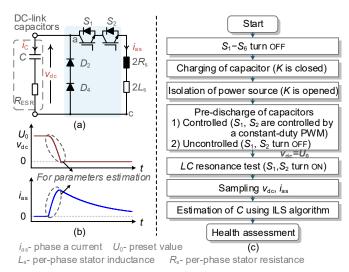

Fig. 18. *LC*-resonance based capacitor-charge scheme [41], here, *L*<sub>ESL</sub> is ignored. (a) Equivalent circuit under CM condition. (b) Capacitor discharging profile. (c) Flowchart of the monitoring scheme.

proposed to monitoring the capacitors in ASD system for electric vehicles. Referring to Fig. 17(a), when the motor is stopped, capacitors and inverter are isolated from the power source ( $K_1$  and  $K_2$  are opened). Here, the capacitors start to discharge through the windings. By controlling the inverter, the capacitors can discharge at a constant current, as shown in Fig. 17(b). Using the discharge profiles  $v_{dc}$  and  $i_C$ , the capacitance can be estimated using (18). In [41], an LC-resonance capacitor-discharge profile based scheme is proposed for an ASD system [see Fig. 13(a)]. The condition monitoring is taken when the system is before start up. Fig. 18(a) shows the equivalent circuit of the rear-end inverter under the capacitor monitoring condition. By turning on  $S_1$  and  $S_2$ , the capacitor, phase a and phase c windings can form an LC-resonant circuit during the capacitor discharging period. The discharging profile is shown in Fig. 18(b). By sampling the discharge trajectories  $v_{dc}$  and  $i_{as}$ , the capacitance can be calculated by iterative least squares (ILS) algorithm. The detailed monitoring flowchart is shown in Fig. 18(c).

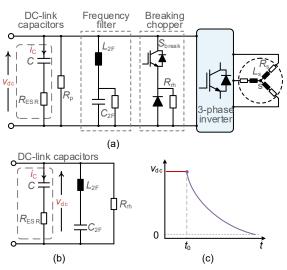

Considering the impedance networks in the converter systems, a discharging profile based scheme is proposed for ASD systems in railway power trains [42], as shown in Fig. 19(a). When the motor is stopped, the dc-link is isolated from the source and motor. By controlling the switch  $S_{\text{break}}$ , a C-LC-R-type discharge path is formed, as shown in Fig. 19(b).

Fig. 19. Capacitor discharge through impedance networks in an ASD system for railway power trains [42], here,  $L_{\rm ESL}$  is ignored. (a) Structure of a general traction scheme. (b) Equivalent circuit under CM condition. (c) Discharging profile.

According to the discharging profile in Fig. 19(c), C is estimated using LMS algorithm.

#### C. Implementation of CM Schemes based on Principle III

In [43]–[46], artificial neural network (ANN) algorithm based schemes are proposed to estimate the capacitor parameters of ASD system. An implementation example is given in Fig. 8(c). The key issue of these schemes is to obtain and define a suitable training data set. To accurately obtain the relationship between capacitor parameters and input training data (such as input current, input voltage, dc-link voltage, output current, output voltage), different capacitance and load conditions must be considered in the training process. Besides the ANN algorithm, an adaptive neuro-fuzzy inference system (ANFIS) algorithm is employed to train data to monitor the capacitor health state in [47].

#### D.Discussions of CM Schemes for Capacitors in ASD Systems

Table VI summarizes the CM schemes for capacitors in ASD systems. Brief remarks are given as follows.

- 1) The derived schemes based on 1B, 1F, and 1I can real-online estimate capacitor parameters, however, capacitor current sensors, additional signal processing circuits, and complex algorithms are required [25], [26], [37], [38].

- 2) The derived schemes based on 1C and 1G can real-online estimate capacitor parameters without a capacitor current sensor. However, the estimation accuracy is relative low [27], [28].

- 3) The derived schemes based on 3A are real-online estimate schemes, which have relatively estimation accuracy. Additional sensors and hardware circuits are not required. However, complexly training algorithms and a large amount of training data are required, which is the maximum challenge [43]–[47].

- 4) The derived schemes in [29]–[36] (based on 1D, 1H) and [40]–[42] (based on 2A) are quasi-online schemes,

without additional current sensors and hardware circuits. The estimation accuracy is relatively high, however, some complex control of systems needs to be considered.

In summary, from the perspective of estimation accuracy and hardware cost, the schemes based on signal injection (1D, 1H), discharging profile (2A), and data training (3A) are recommended for condition monitoring of capacitors in ASD systems.

## VI. CM FOR CAPACITORS IN PV GRID-CONNECTED INVERTERS AND PFC CONVERTERS

#### A. CM for Capacitors in PV Grid-connected Inverters

Single-phase inverters are widely used in photovoltaic (PV) systems to feed power from energy sources to the grid. Some condition monitoring schemes of capacitors in single-phase inverters are presented in [48]–[55]. All of these schemes are derived based on Principle I.

#### 1) Circuit Operation Model based Methods (1C, 1G)

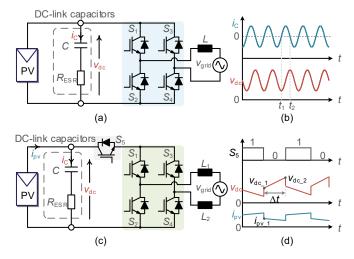

In [48] a derived scheme based method 1C is proposed to estimate C of the input capacitor in a single-phase grid-connected PV H4 inverter, as shown in Fig. 20(a). Here, the average capacitor current  $i_C$  is calculated as  $i_C = i_{pv} - i_{inv} = i_{pv} - i_L(S_1S_4 - S_2S_3)$ , where  $S_1 - S_4$  are the state of the switches. The estimated capacitor current and capacitor voltage waveform are shown in Fig. 20(b). The dc-link voltage is sampled at two special instants  $t_1$  and  $t_2$ , where average capacitor current equals to 0, i.e.,  $i_C(t_1) = i_C(t_2) = 0$ . Thus, the capacitance is calculated using (12), i.e.,

$$C = \frac{\int_{t_1}^{t_2} i_{\rm C}(t) dt}{v_{\rm dc}(t_2) - v_{\rm dc}(t_1)}.$$

(24)

Using the same capacitor current reconstruction method, [49] estimates the capacitor impedance at 2nd harmonic frequency of a PV inverter as  $Z_2 = V_{dc,2}/I_{C,2}$ , where  $V_{dc,2}$  and  $I_{C,2}$  represent the RMS values at 2nd harmonic frequency.

In [50], a condition monitoring scheme is proposed for a PV H5 inverter, as shown in Fig. 20(c), the capacitance is calculated during the zero state, i.e., the power switch  $S_5$  is turned OFF, as shown in Fig. 20(d). Using (10), C is calculated as  $C = (i_{pv} \ _1 \times \Delta t)/(v_{dc} \ _2 - v_{dc} \ _1)$ .

#### 2) External Signal Injection based Methods (1D, 1H)

In [51], a current injection scheme is proposed for a grid-connected PV inverter, as shown in Fig. 7(e). Here, the condition monitoring of capacitors is taken during the night. At night, there is no voltage on the PV panel/string. Here, a current at hth harmonic frequency is injected into the grid, which causes (h-1)th and (h+1)th voltage and current ripples to appear on the dc-link capacitors. Using (9),  $R_{\rm ESR}$  and C can be estimated using the voltage and current ripples at (h-1)th or (h+1)th based on the LMS algorithm. Utilizing the same monitoring scheme, [52] further proposes a health estimation method for individual capacitors in a capacitor bank.

In [53], a short-circuit test scheme is introduced to a dc/ac converter to estimate  $R_{\rm ESR}$  of capacitors, as shown in Fig. 21. Before the short-test, the converter operates in a normal state.

TABLE VI SUMMARY OF CM SCHEMES FOR CAPACITORS IN ASD SYSTEMS

| Method                          | Working principle                                                                                                                                                                                                                                                                                    | Experimental error                                               | Advantages                                                                           | Limitations                                                                                                                                                   |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Capacitor current directly      | [25]: A current sensor is used to sample capacitor current. Then use the Goertzel algorithm to extract low-frequency (300 Hz) and switching-frequency (2.5 kHz) ripples.                                                                                                                             | R <sub>ESR</sub> : <3%<br>C: <1%                                 | Real-online estimation.                                                              | Additional current sensors and filter                                                                                                                         |  |

| measurement (1B,1F)             | [26]: A current sensor is used to sample capacitor current. Then use fast Fourier transform (FFT) algorithm is used to analyze mid-frequency (15 kHz) ripples.                                                                                                                                       | R <sub>ESR</sub> : <3.86%                                        |                                                                                      | circuits, complex algorithms.                                                                                                                                 |  |

| System operation model (1C, 1G) | [27], [28]: Utilizing the operation mode of converters to indirectly acquire capacitor current ripple and sampled voltage ripple to estimate $C$ .                                                                                                                                                   | C: <5.2% <sup>[27]</sup>                                         | Real-online estimation,<br>no additional hardware<br>circuit and current<br>sensors. | Small-amplitude ripple measurement, estimated $i_C$ .                                                                                                         |  |

| Giamal.                         | [29]-[31]: The power switches are controlled to realize the charge and discharge (through the motor windings) of capacitors, then sample the constructed waveforms to estimate parameters.                                                                                                           | R <sub>ESR</sub> : <2% <sup>[31]</sup><br>C: <5% <sup>[31]</sup> | No additional hardware circuits and current sensors.                                 | Quasi-online estimation, motor is<br>stopped, additional control of switches,<br>small-amplitude ripple measurement.                                          |  |

| Signal<br>injection<br>(1D, 1H) | [32]-[36]: Low-frequency ac current or voltage are injected to the front-end ac/dc converter [32]-[35] or rear-end dc/ac converter [36], then use the recursive least squares (RLS) algorithm or support vector regression (SVR) to analyze the corresponding voltage ripple to estimate parameters. | R <sub>ESR</sub> : <3.2% [33]<br>C: <0.4% [34]                   | No additional hardware circuits and current sensors.                                 | Quasi-online estimation, external signal injection, operation in no load condition [32]–[35] or regenerative mode [36].                                       |  |

| Power losses<br>(1I)            | [37], [38]: R <sub>ESR</sub> is calculated using average power losses of capacitors. Analog circuits [37] and an MCU [38] are used to calculate the power losses.                                                                                                                                    | R <sub>ESR</sub> : <1.8 % [38]                                   | Real-online estimation,<br>no need for specific<br>band-pass filter.                 | Additional capacitor current sensor [37], [38], extra power loss calculation circuit [38].                                                                    |  |

| Discharging                     | [39]: Control capacitors discharge through a variable electric network (VEN), then estimate $R_{\rm ESR}$ and $C$ using the discharging profile.                                                                                                                                                     | R <sub>ESR</sub> : <1.3%<br>C: <0.047%                           | High estimation accuracy.                                                            | Quasi-online estimation, additional VEN on dc link, which introduces reliability risks, during shutdown process, need control of switches.                    |  |

| profile (2A)                    | <b>[40]-[42]:</b> Control capacitors discharge through the motor windings [40],[41] and electric network [42] in the converter, then estimate $C$ using the discharging profile.                                                                                                                     | C: <2.1% [41]                                                    | No additional hardware circuits and current sensors.                                 | Quasi-online estimation, motor is<br>stopped, need control of switches [40],<br>[41], electric vehicles application [40],<br>railway trains application [42]. |  |

| Data training (3A)              | [43]–[46]: Using the artificial neural network (ANN) network to train data such as input voltage/current, output input voltage/current, and dc-link voltage to obtain <i>C</i> .                                                                                                                     | C: <2% <sup>[46]</sup>                                           | Real-online estimation,<br>no additional hardware<br>circuit and current             | Need a large amount of training data and complexly algorithms.                                                                                                |  |

| (3A)                            | [47]: Using adaptive neuro-fuzzy inference system (ANIS) algorithm to train voltage data to obtain the capacitor health state.                                                                                                                                                                       | N/A                                                              | sensors.                                                                             | complexity digorithms.                                                                                                                                        |  |

Fig. 20. Single-phase grid-connected PV H4 inverter [48] and H5 inverter [50]. (a) Structure of H4 inverter, here,  $L_{\rm ESL}$  is ignored. (b) Average capacitor current and voltage waveforms. (c) Structure of H5 inverter. (d) Typical waveform of PV voltage and PV current in active and zero state.

Fig. 21. Short-circuit current perturbation for capacitor monitoring in a single-phase inverter [53], here, *L*<sub>ESL</sub> is ignored. (a) Equivalent circuit of a single-phase inverter during short-circuit test. (b) Short-circuit test waveforms.

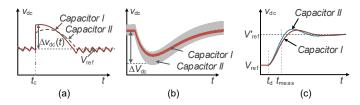

Here,  $S_2$ ,  $S_3$  are ON and  $S_1$ ,  $S_4$  are OFF. At  $t_0$ ,  $S_1$  turns on, a very short time short-circuit test occurs, which causes a capacitor voltage step  $\Delta V_{\rm dc}$ . According to (11),  $R_{\rm ESR}$  is calculated as  $R_{\rm ESR} = \Delta V_{\rm dc} / I_{\rm sc}$ , where  $I_{\rm sc}$  is the short circuit current.

#### 3) Power Losses based Method (1J)

Based on the idea of power losses (i.e., method 1J), [54], [55] proposed a power extraction efficiency (PEE) method to monitor the health state of capacitors. The PEE is defined as  $PEE = P_{av}/P_{max}$ , where  $P_{av}$  and  $P_{max}$  represent the average PV power and maximum PV power. By sampling the PV voltage and current, the PEE is calculated to estimate the health state of capacitors.

- 4) Discussions of CM Schemes for Capacitors in PV Inverter Table VII summarizes the CM schemes for capacitors in PV inverters, the remarks are given as follows.

- a) The CM schemes for capacitors in PV inverters are all based on Principle I.

- b) The signal injection scheme in [51] (based on 1D, 1H) is a quasi-online scheme, which has a relatively high estimation accuracy. However, the CM is implemented during the night and an additional power diode is required. Another injection scheme in [53] is a real-online scheme, which has high applicability. However, the estimation accuracy of *R*<sub>ESR</sub> is relatively low, and high-frequency sampling of short-circuit current is required.

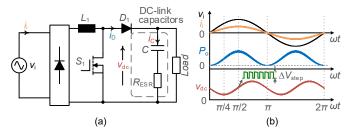

Fig. 22. Topology structure and key waveforms of boost PFC converters, here,  $L_{\rm ESL}$  is ignored [60]. (a) Topology structure. (b) Key waveforms.

- c) The power losses schemes in [54], [55] (based on 1J) and capacitor current estimation scheme in [49] (based on 1C, 1G) can real-online monitoring the health status of capacitors without additional hardware circuits and current sensors. However, specially defined failure criteria are required.

- d) The capacitor current estimation scheme in [49], [50] (based on 1C, 1G) are real-online schemes without additional hardware circuits and current sensors. However, [50] is only suitable for PV H5 inverter, which has a low applicability

In summary, from the perspective of estimation accuracy and hardware cost, the scheme in [48] is recommended for condition monitoring of capacitors in PV inverters.

#### B. CM for Capacitors in PFC converter

Power factor correction (PFC) converters are widely used in ac/dc conversion to improve power factor (PF) and reduce total harmonic correction (THD). The condition monitoring schemes in [56]–[61] are designed for PFC converters, which are derived based on Principle I.

#### 1) Capacitor Current Sensor based Methods (1B, 1F)

Taking a boost PFC converter as an example, Fig. 22(a) shows its topology structure and key waveforms. In [56], C and  $R_{\rm ESR}$  of capacitors are estimated using equations (10) and (11). Here, Prony's algorithm is used to process the sampled voltage and current data. Similar, discrete Fourier transform (DFT) is used in [57]. Moreover, according to (11), [58] calculates  $R_{\rm ESR}$  using  $R_{\rm ESR} = V_{\rm dc,RMS}/I_{\rm C,RMS}$ , where  $V_{\rm dc,RMS}$ ,  $I_{\rm C,RMS}$  are the Root-Mean-Square (RMS) values of  $\Delta \nu_{\rm CAP}$  and  $\Delta i_{\rm C}$ .

#### 2) Circuit Operation model based Methods (1C, 1G)

Referring to Fig. 22(a), the capacitor current can be approximately calculated as  $i_C=i_D-I_D\approx i_L\times PWM-avg(i_L\times PWM)$ , where  $I_D$  is the average diode current. Based on this, [59] used Kalman filter algorithm and (10), (11) to estimate C and  $R_{ESR}$ . Referring to Fig. 22(b), at  $\pi/2$  in a half-line cycle, the peak value of the capacitor current is maximum, which causes the peak value of the voltage ripple to be maximum. According to (11), the ripple voltage step value  $\Delta V_{\text{step}}$  is determined by  $R_{ESR}$  when the switch S<sub>3</sub> turns OFF. Therefore, [60] estimated  $R_{ESR}$  using  $R_{ESR}\approx \Delta V_{\text{step}}/\Delta i_{\text{L_max}}$ , where  $\Delta i_{\text{L_max}}$  is the maximum value of inductor current ripple. Here, wavelet transform (WT) algorithms are used to calculate  $R_{ESR}$ .

| Topology       | Method                                   | Working principle                                                                                                                                                                                                                        | Experimental error                                                     | Advantages                                                                                                   | Limitations                                                                                                                   |  |

|----------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

|                | Cyatana                                  | <b>[48]</b> : Using estimated $i_C$ and capacitor voltage to calculate $C$ . The capacitor voltage is sampled in particular instants $(i_C=0)$ .                                                                                         | C: <2.56%                                                              | Real-online estimation.                                                                                      | Estimated $i_{\mathbb{C}}$ .                                                                                                  |  |

|                | System<br>operation<br>model             | [49]: Using the second harmonic voltage and current to calculate capacitor impedance.                                                                                                                                                    | Z: <17.2%                                                              | no additional hardware<br>circuits and current                                                               | Estimated $i_C$ , low estimation accuracy, no specific values of $R_{\rm ESR}$ and $C$ , specially defined failure criterion. |  |