# **Aalborg Universitet**

# A High Step-Up Interleaved DC-DC Converter with Voltage Multiplier and Coupled Inductors for Renewable Energy Systems

Alghaythi, Mamdouh L.: O'Connell, Robert M.: Islam, Naz E.: Khan, Mohammed Masum Sirai: Guerrero, Josep M.

Published in: **IEEE Access**

DOI (link to publication from Publisher): 10.1109/ACCESS.2020.3007137

Creative Commons License CC BY 4.0

Publication date: 2020

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Alghaythi, M. L., O'Connell, R. M., Islam, N. E., Khan, M. M. S., & Guerrero, J. M. (2020). A High Step-Up Interleaved DC-DC Converter with Voltage Multiplier and Coupled Inductors for Renewable Energy Systems. IEEE Access, 8, 123165-123174. Article 9133374. https://doi.org/10.1109/ACCESS.2020.3007137

# **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 06, 2025

Received June 22, 2020, accepted June 29, 2020, date of publication July 6, 2020, date of current version July 17, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.3007137

# A High Step-Up Interleaved DC-DC Converter With Voltage Multiplier and Coupled Inductors for Renewable Energy Systems

MAMDOUH L. ALGHAYTHI<sup>©</sup>1,2, (Member, IEEE), ROBERT M. O'CONNELL<sup>©</sup>1, (Life Senior Member, IEEE), NAZ E. ISLAM<sup>©</sup>1, (Senior Member, IEEE), MOHAMMED MASUM SIRAJ KHAN<sup>©</sup>3, (Student Member, IEEE), AND JOSEP M. GUERRERO<sup>©</sup>4, (Fellow, IEEE)

Corresponding author: Mamdouh L. Alghaythi (mlagzd@mail.missouri.edu)

This work was supported in part by the Jouf University Grant and in part by the University of Missouri. J. M. Guerrero was supported by VILLUM FONDEN under the VILLUM Investigator Grant (no. 25920): Center for Research on Microgrids (CROM); www.crom.et.aau.dk

**ABSTRACT** This paper proposes a new interleaved non-isolated high step-up dc-dc converter for interfacing renewable energy applications. The proposed converter achieves a very high step-up voltage gain by using two coupled inductors and a voltage multiplier cell. This topology utilizes the interleaved boost converter in the input side, and the input current is shared with low ripple. Moreover, a voltage multiplier cell with the secondary windings of the coupled inductors is employed in the output side to achieve the interleaved energy storage. The voltage stress on the semiconductor switches and the passive components is significantly reduced and lower than the output voltage. The aforementioned converter can be operated without an extreme duty cycle or a high turns ratio. The reverse recovery problem of the diodes is mitigated, and the leakage energy is recycled. Furthermore, by implementing low-voltage-rated MOSFETs with a small ON-resistance, the conduction losses can be reduced, and the efficiency can be improved. The topology is fed by a single input voltage, and the mathematical expression is methodically explored. The operation principle of the proposed converter and the comparison between the proposed converter with other topologies are discussed. The design, parameters selection, and experimental results are thoroughly introduced. A 32 to 800 V-dc is verified and simulated by using PLECS. Consequently, a 400 W hardware prototype is verified to validate the theory and the design.

**INDEX TERMS** Coupled inductors, high voltage gain, high step-up dc-dc converter, high efficiency, interleaved boost converter, PV, renewable energy systems, voltage multiplier.

# I. INTRODUCTION

The demand for renewable energy systems, such as photovoltaic systems, fuel cells and wind turbines, has been robust in recent years. High step-up dc-dc converters are currently being utilized in many applications, such as dc distribution

The associate editor coordinating the review of this manuscript and approving it for publication was Derek Abbott.

systems, data centers and telecom centers. Power electronic converters play a substantial role in power conversion of the distributed generation and the grid integration [1]. Increasing renewable energy sources would exceedingly catalyze the utilize of high step-up dc-dc power electronic converters to integrate renewable energy systems to electric power grid. Furthermore, power electronic converters should be highly efficient and reliable to convert the renewable energies to

<sup>&</sup>lt;sup>1</sup>Department of Electrical Engineering and Computer Science, University of Missouri, Columbia, MO 65211, USA

<sup>&</sup>lt;sup>2</sup>Electrical Engineering Department, Faculty of Engineering, Jouf University, Sakaka 72388, Saudi Arabia

<sup>&</sup>lt;sup>3</sup>Department of Electrical and Computer Engineering, The University of Utah, Salt Lake, UT 84112, USA

<sup>&</sup>lt;sup>4</sup>Center for Research on Microgrids (CROM), Department of Energy Technology, Aalborg University, 9220 Aalborg East, Denmark

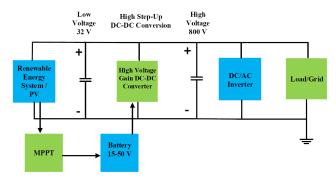

the electric power grid. As a result, using high step-up dcdc converts with high efficiency is required, and it is the main goal to ensure the reliability. PV system technologies are still the most favorable technologies for a huge portion of renewable energy generation [2]. Nowadays, PV systems have the largest growth and installation between other renewable energy systems. Moreover, PV systems are receiving higher power ratings, and the grid side would request the PV inverter to steady the grid voltage. The grid connected PV systems have the advantage over the off-grid PV systems in terms of the growth and the installed PV systems. Since the output voltage of a PV panel is low (from 15 V to 50 V), a high dc-dc converter is compulsory to lift and regulate the output voltage of a PV panel to the voltage level of the DCbus, which would be transferred to an AC voltage through an inverter to the load as shown in Fig. 1. Therefore, integrating a PV panel to a 800 V dc is perceptibly a rigid duty and entails a high step-up dc-dc converter.

FIGURE 1. High step-up dc-dc converter for a PV system.

High step-up dc-dc converters with high efficiency have been proposed in [3]. These converters have utilized active clamps to recycle the leakage energy and mitigate the output diode reverse recovery issue. Diminishing the resonance between the leakage inductance and the capacitance of the devices plays a vital role in alleviating the voltage stresses. In 2013, a novel high step-up dc-dc converter for distributed generation systems has been introduced, and the voltage conversion ratio has been increased due to utilizing a coupled inductor and two capacitors [4]. The proposed converter in [5] has achieved a very high step-up voltage gain by integrating two coupled inductors and switched capacitor techniques. Moreover, the conduction losses have been alleviated due to the low resistance, which would result in increasing the efficiency and reducing the reverse recovery of the diodes. In [6], high efficiency with high step-up dc-dc converter and dual coupled inductors for grid-connected photovoltaic systems has been presented. In addition, this proposed converter has used an integrated regenerative snubber to recycle the leakage energy to the output and has also employed active clamp circuits with a shared clamp capacitor on the active switches. The proposed converters in [7] and [8] have offered a high step-up dc-dc converter by using coupled inductor and voltage-lift technique. In addition, the voltage stress has been reduced, and the conversion efficiency has been improved. In [9], a high step-up voltage gain active-network converter with switched-capacitor but without using a high duty cycle has been provided, and the low voltage components can be utilized to reduce the conduction loss and cost. A cascade cockcroft-walton voltage multiplier has been applied to a transformerless high step-up dc-dc converter, and then the proposed control strategy comprises two different frequencies, one of which has operated at high frequency to mitigate the size of the inductor, and the other one operates at a low frequency to reduce the output voltage ripple [10]. The conventional boost converter theoretically can achieve a high output voltage by using a very large duty cycle. However, operating at the extreme high duty cycles would result in high conduction losses and would make the semiconductors suffer the voltage stress [11]. In [12], a high step up quasi z-source dc-dc converter with coupled inductors has been presented, and the main benefits of the aforementioned converter are low normalized voltage stress on semiconductors compared to the quasi z-source and continous input current. Furthermore, the conventional boost converter experiences a low efficiency due to the instability, power dissipation and complexity of the control part. Cascaded boost converter could be used to increase the output voltage since it consists of two conventional boost converters without using extreme duty cycles. However, using cascaded boost converter would increase the components size and result in high ripples on the input current, and the output diode may experience extreme voltage stress on the switches. In addition, the energy will be processed twice and that would eventually compromise the efficiency. A switched capacitor dual switch high stepup dc-dc is introduced, the waveforms have been explored in the continuous conduction mode and the discontinuous mode, and the conduction losses have been reduced due to the small duty cycle [13]. The aforementioned proposed topologies may suffer from diode reverse recovery and electromagnetic interference problems.

On the other hand, using isolated dc-dc converters is another voltage boost technique to lift the voltage gain which would utilize the coupled inductors and transformers [14]–[19]. Employing high frequency transformers can boost the input voltage and offer the electrical isolation to protect the circuit [20]-[24]. But using a transformer can cause the leakage inductance and reduce the power density [25]–[28]. Coupled inductors have the flexibility compared to transformers to boost the output voltage [29]–[32]. Consequently, achieving a high voltage gain requires an increase in the turns ratio, which may cause the leakage inductance and the voltage spikes in isolated dc-dc converter. Zero current-switching (ZCS) turn-ON soft-switching performance for the switches is utilized, which would reduce the electromagnetic interference (EMI) noises and the switching losses. This paper presents the operational principle of the proposed converter in section II, modes of operation in part A of section II, voltage gain analysis and performance comparison in part B of section II, design consideration and simulation results in

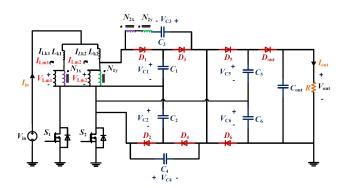

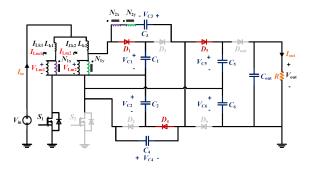

FIGURE 2. The proposed high step-up dc-dc converter.

section III, voltage and current stress on the switches in part A of section III, inductor design in part B of section III, voltage and current stress on the diodes in part C of section III, voltage and current stress on the capacitors in part D of section III, efficiency analysis in part E of section III, experimental results in section IV, and conclusion in section V.

# II. OPERATIONAL PRINCIPLE OF THE PROPOSED CONVERTER

The proposed converter primarily consists of two parts; the first part is the interleaved boost converter with coupled inductors, and the second part is the voltage multiplier cells and the secondary windings, which can extend the voltage gain and mitigate the current ripple. A high step-up interleaved boost converter with coupled inductors and voltage multiplier is shown in Fig. 2. The interleaved boost converter has two coupled inductors, the magnetizing inductors  $L_{m1}$  and  $L_{\rm m2}$ , the leakage inductances  $L_{\rm k1}$  and  $L_{\rm k2}$  and two switches connected to a single source. The secondary windings of the coupled inductors are connected with the voltage multiplier. Voltage multiplier cells have some diodes and capacitors, and they are connected to the load to overcome the voltage discrepancy that may occur. The proposed converter works only in the continuous conduction mode (CCM)since the inductor current does not reach zero and based on that, the operational principle and the steady state analysis are in CCM. The diode reverse recovery can be mitigated by the leakage inductance of the coupled inductors. The proposed converter shares the primary side of the coupled inductors and integrates them to the secondary side. By increasing the phases of the interleaved converter, the ripple on the input current will decrease. Fig. 3 shows the switching signals of the proposed converter, and the phase shift between the switches is 180 degree. In addition, there are some assumptions in order to simplify the circuit; the semiconductor devices are ideal, both inductor currents are operated in the conduction continuous mode, the coupled inductors are modeled ideally with a magnetizing inductor and a leakage inductor and an ideal transformer with a turns ratio of

$$N = \frac{N_{1y}}{N_{1x}} = \frac{N_{2y}}{N_{2x}} \tag{1}$$

FIGURE 3. The Switching signals of the proposed converter.

FIGURE 4. Mode-I of operation for the proposed converter.

# A. MODES OF OPERATION

The operation modes and the typical performance of the proposed converter are presented in the continuous conduction mode (CCM).

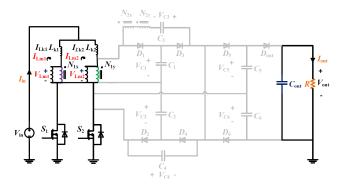

Mode-I:  $S_1$  and  $S_2$  are ON and, they are conducting in the mode as shown in Fig. 4.  $L_{\rm m1}$  and  $L_{\rm m2}$  store the energy. Moreover, the magnetizing inductors  $L_{\rm m1}$  and  $L_{\rm m2}$ , the leakage inductances  $L_{\rm k1}$  and  $L_{\rm k2}$  are charged by the dc input voltage. The magnetizing inductor currents are linearly increased. It can be observed that the diodes of voltage multiplier cells do not conduct, and they are reverse biased. In addition, the output diode  $D_{\rm out}$  is reverse biased, and the capacitor voltages of the voltage multiplier cells remain fixed. Finally, the load energy is supplied by the output capacitor  $C_{\rm out}$ .

Mode-II: In this mode,  $S_1$  is OFF and  $S_2$  is ON as shown in Fig. 5.  $D_1$ ,  $D_4$  and  $D_5$  do not conduct, then they are reverse biased.  $L_{\rm m2}$  stores the energy, and  $L_{\rm m1}$  release the energy. However,  $D_2$ ,  $D_3$ ,  $D_6$  and the output diode  $D_{\rm out}$  are forward biased and conduct in this state. The magnetizing inductance  $L_{\rm m1}$ , the leakage inductance  $L_{\rm k1}$  and the source charge  $C_2$ ,  $C_3$  and  $C_6$ . On the other hand,  $L_{\rm m2}$  and  $L_{\rm k2}$  are charged by the dc input voltage.

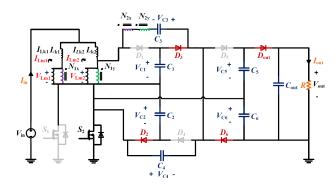

Mode-III:  $S_1$  is ON and  $S_2$  is OFF as shown in Fig. 6.  $D_2$ ,  $D_3$ ,  $D_6$  and the output diode  $D_{\text{out}}$  are reverse biased, and they are OFF. But  $D_1$ ,  $D_4$  and  $D_5$  are conducting, and they are forward biased.  $L_{\text{m2}}$  and the input voltage charge  $C_1$ ,  $C_4$  and

FIGURE 5. Mode-II of operation for the proposed converter.

FIGURE 6. Mode-III of operation for the proposed converter.

$C_5$ .  $L_{\rm m1}$  stores the energy, and the magnetizing inductance  $L_{\rm m2}$ , and the leakage inductance  $L_{\rm k2}$  transfers the energy.

# B. VOLTAGE GAIN ANALYSIS AND PERFORMANCE COMPARISON

The mathematical expression of the voltage gain is calculated in this part. For the second mode, the steady state equations can be expressed as

$$\langle V_{\rm Lm1} \rangle = 0 \tag{2}$$

$$V_{\rm in} = \frac{dI_{\rm Lm1}}{dt} \tag{3}$$

$$V_{\rm in} = \frac{dI_{\rm Lm2}}{dt} \tag{4}$$

$$\int_{0}^{DT_{s}} V_{Lm1} dt + \int_{DT_{s}}^{T_{s}} V_{Lm2} dt = 0$$

(5)

The capacitor voltages for  $C_1$  and  $C_2$  are equal, the magnetizing voltages are identical and can be derived as

$$V_{\rm Lm1} = V_{\rm Lm2} = V_{\rm in} + V_{\rm C1} - V_{\rm C2}$$

(6)

$$V_{\rm Lm1} = V_{\rm Lm2} = V_{\rm in} \tag{7}$$

For mode-III, the capacitor voltages for  $C_1$  and  $C_2$  can be given as

$$V_{\rm C1} = V_{\rm C2} = V_{\rm in} \times \frac{1}{(1-D)}$$

(8)

The capacitor voltages for  $C_5$  and  $C_6$  are twice the capacitor voltages for  $C_1$  and  $C_2$ . By applying the volt-second balance

principle, the ideal voltage gain can be written as, the number of turns ratio is 3 and can be computed as

$$M = \frac{V_{\text{out}}}{V_{\text{in}}} = 2(N+1) \times \frac{1}{(1-D)} = 8 \times \frac{1}{(1-D)}$$

(9)

The voltage gain conversion can be written as

$$V_{\text{out}} = V_{\text{in}} \times \frac{8}{(1-D)} \tag{10}$$

The performance comparison between the proposed converter and other topologies is shown in TABLE 1. The main characteristics include voltage gain, voltage stresses on switches and diodes, total number of components, such as switches, diodes, capacitors and inductors, sharing ground connection and the input current. It can be noted from TABLE 1 that the voltage stresses and the voltage gain of the proposed converter are equal to [6]. In addition, the voltage stress across switches and diodes in [10] are identical to the voltage stress across switches for the proposed converter. However, even though the voltage stress across devices in [10] are identical and reduced, the number of switches is four, which results in increasing the cost and the size of the converter. The converter in [15] suffers from the high voltage stress across switches and diodes, and the stresses across semiconductors are equal to the output voltage, and as a result, the performance of the converter becomes very low, and the input current is discontinuous. The duty cycle in [9] is low, the voltage stresses across power devices are alleviated, the number of components is small, and then the reliability of this converter is high. However, the voltage gain for the converter is low compared to the proposed converter. The topology in [11] has a high voltage stress on diodes compared to the proposed converter, and it is identical to the output voltage. Thus, this converter is not suggested for high stepup applications. Converters in [12], [13] and [14] have a very small duty cycle, which leads to decreasing the power losses, but in [13] the voltage gain ratio is small compared to the proposed converter.

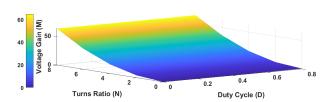

Fig. 7 illustrates that the relationship between the voltage gain (M) and the duty cycle (D) with several turns ration, and it can be observed that as the turns ratio (N) increases, the voltage gain proportionally increases. In addition, the proposed converter offers a high voltage gain without an extreme high duty cycle. The derivation of the turns ration formula will be discussed in part B of section III.

**FIGURE 7.** Voltage gain (M) vs. duty cycle (D) of the proposed converter with several turns ratio (N).

| э. |

|----|

|    |

|    |

| _  |

| Topologies         | Voltage gain $(M)$ $(V_{\rm out}/V_{\rm in})$ | Voltage stress<br>on switches                  | Voltage stress<br>of diodes                        |   | No. o: |   |        | o. of<br>tor cores | Shared<br>grounded | Input<br>Current |

|--------------------|-----------------------------------------------|------------------------------------------------|----------------------------------------------------|---|--------|---|--------|--------------------|--------------------|------------------|

|                    | (vout/vin)                                    |                                                |                                                    | S | D      | C | Single | Coupled            |                    |                  |

| Ref. [5]           | $\frac{2N+4}{1-D}$                            | $\frac{1}{2N+4}$                               | $\frac{N+1}{N+2}$                                  | 2 | 4      | 4 | 0      | 2                  | Yes                | Continuous       |

| Ref. [6]           | $\frac{2(N+1)}{1-D}$                          | $\frac{V_{\text{out}}}{2(N+1)}$                | $\frac{(2N+1)V_{\text{out}}}{2(N+1)}$              | 4 | 2      | 3 | 0      | 2                  | Yes                | Continuous       |

| Ref. [9]           | $\frac{3+D}{1-D}$ $2N$                        | $\frac{V_{ m out}}{2}$                         | $\frac{V_{\text{out}}}{2}$ $2V_{\text{in}}$        | 1 | 1      | 1 | 0      | 2                  | No                 | Discontinuous    |

| Ref. [10]          | $\frac{2N}{1-D}$                              | $\frac{V_{\rm in}}{(1-D)}$                     | $\frac{2V_{\rm in}}{(1-D)}$                        | 4 | 6      | 6 | 1      | 0                  | No                 | Continuous       |

| Ref. [11]          | $\frac{2(N+1)}{1-D}$                          | $\frac{V_{\text{out}}}{2(N+1)}$                | $V_{ m out}$                                       | 4 | 4      | 5 | 2      | 1                  | Yes                | Continuous       |

| Ref. [12]          | $\frac{2+N}{1-D}$                             | $\frac{V_{\rm in}}{(1-2D)}$                    | $\frac{(1+N)V_{\rm in}}{1-2D}$                     | 1 | 4      | 5 | 1      | 1                  | No                 | Continuous       |

| Ref. [13]          | $\frac{3-2D}{1-2D}$                           | $\frac{\dot{V}_{ m out} - \dot{V}_{ m in}}{2}$ | $\frac{V_{\rm out} - V_{\rm in}}{2}$               | 2 | 4      | 3 | 1      | 0                  | No                 | Continuous       |

| Ref. [14]          | $\frac{(1+ND)}{1-D}$                          | $\frac{V_{\text{out}}}{(1+ND)}$                | $\frac{(1-D)NV_{\text{out}}}{(1+ND)V_{\text{in}}}$ | 1 | 2      | 3 | 2      | 1                  | No                 | Continuous       |

| Ref. [15]          | $\frac{1}{1-2D}$                              | $V_o$                                          | $V_{ m out}$                                       | 1 | 2      | 3 | 2      | 0                  | Yes                | Discontinuous    |

| Ref. [16]          | $\frac{2(N+1)}{1-D}$                          | $\frac{V_{\rm in}}{1-D}$                       | $\frac{2NV_{\rm in}}{1-D}$                         | 2 | 4      | 3 | 0      | 2                  | Yes                | Continuous       |

| Ref. [26]          | $\frac{2(N+1)}{1-D}$                          | $\frac{V_{\text{out}}}{2(N+1)}$                | $\frac{NV_{\text{out}}}{N+1}$                      | 2 | 4      | 4 | 0      | 2                  | Yes                | Continuous       |

| Proposed converter | $\frac{2(N+1)}{1-D}$                          | $\frac{V_{\rm in}}{1-D}$                       | $\frac{2V_{\rm in}}{1-D}$                          | 2 | 7      | 7 | 0      | 2                  | No                 | Continuous       |

# III. DESIGN CONSIDERATIONS AND SIMULATION RESULTS

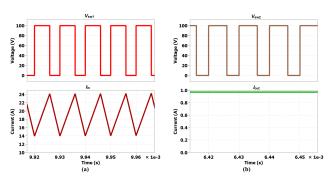

### A. VOLTAGE STRESS ON THE SWITCHES

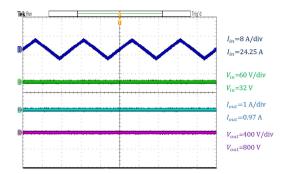

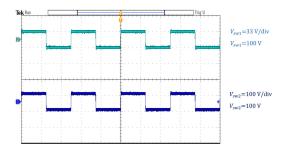

The voltage stress on the switches is significantly reduced to 100 V, the input current is 24.25 A, and the output current is 0.97 A as depicted in Fig. 8. The voltage stress on the switches can be derived as

$$V_{\text{sw1}} = V_{\text{sw2}} = V_{\text{in}} \times \frac{1}{(1-D)}$$

(11)

The peak current stress across the active switches can be expresses as

$$I_{\text{sw1(peak)}} = I_{\text{sw2(peak)}} = \frac{2(N+1)I_{\text{out}}}{(1-D)}$$

(12)

The average current stress on the active switches can be given as

$$I_{\text{sw1(avg)}} = I_{\text{sw2(avg)}} = \frac{(N+1)I_{\text{out}}}{(1-D)}$$

(13)

The benefit of having MOSFETs switches is that MOSFETs can magnificently run at high frequencies. The average current stress across the active switches is 12.125 A. Since the voltage stress across switches is reduced, the low on-state resistance MOSFETs can be used to improve the efficiency.

FIGURE 8. The voltage stress on the active switches, the input current and the output current.

# **B. INDUCTOR DESIGN**

The turns ratios of the coupled inductors play a significant role in determining the voltage and current stress across the power devices. The average magnetizing inductor currents rely on the turns ratio (N). It can be observed that the magnetizing inductor currents of the coupled inductors are balanced because of the charge balance of the capacitors. The average magnetizing inductor currents can be calculated as

$$I_{\text{Lm(avg)}} = I_{\text{Lm1(avg)}} = I_{\text{Lm2(avg)}} = \frac{(N+1)I_{\text{out}}}{(1-D)}$$

(14)

The average input current is twice the average magnetizing inductor currents and can be written as

$$I_{\rm in} = 2 \times I_{\rm Lm1(avg)} = 2 \times I_{\rm Lm2(avg)} \tag{15}$$

$$I_{\rm in} = \frac{2(N+1)I_{\rm out}}{(1-D)} \tag{16}$$

For the second mode, the second leakage inductor current

$$I_{Lk2} = I_{Lm1(avg)} + I_{Lm2(avg)}$$

(17)

For the third mode, the first leakage inductor current

$$I_{Lk1} = I_{Lm1(avg)} + I_{Lm2(avg)}$$

(18)

The magnetizing current ripple can be given as

$$\Delta I_{\rm Lm} = 0.15 \times I_{\rm Lm(avg)} \tag{19}$$

The magnetizing inductances are designed based on the input current and can be calculated as

$$L_{\rm m1} = L_{\rm m2} = \frac{DV_{\rm in}}{f_{\rm sw} \Delta I_{\rm I,m}}$$

(20)

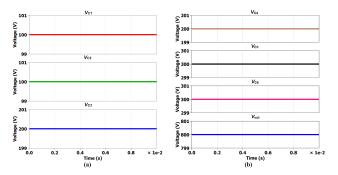

Determining the turns ratio plays a significant role in obtaining the voltage gain, voltage stress on the switches and voltage stress on the diodes. Therefore, since the duty cycle is 0.68, the output voltage is 800 V, and the input voltage is 32 V. The duty cycle D during the steady state is larger than 0.5. The magnetizing voltages and the average magnetizing inductor currents are illustrated in Fig. 9. Each magnetizing voltage is 32 V, and each average magnetizing inductor currents is 12.125 A.

FIGURE 9. The magnetizing voltages and the average magnetizing inductor currents.

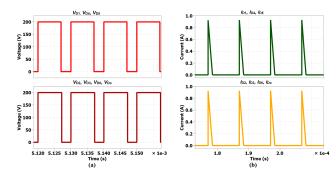

# C. VOLTAGE AND CURRENT STRESS ON THE DIODES

The voltage stress across diodes is twice the voltage stress on active switches. The maximum voltage stress across the diodes can be expressed as

$$V_{\rm D(max)} = V_{\rm in} \times \frac{2}{(1-D)} \tag{21}$$

The average currents stress on the diodes can be derived as

$$I_{\text{D(avg)}} = I_{\text{out}} = \frac{V_{\text{out}}}{R}$$

(22)

FIGURE 10. The voltage and current stresses on the diodes.

FIGURE 11. The voltage stress on capacitors.

The voltage stress across diodes is alleviated to 200 V, and the average currents stress on the diodes is 0.97 A as shown in Fig. 10. It can be noted that the voltage stress across diodes increases when the turns ratio increases. However, it is lower than the output voltage.

# D. VOLTAGE STRESS ON THE CAPACITORS AND **CAPACITOR DESIGN**

The current stress across capacitors can be written as

$$I_{\text{C(rms)}} = I_{\text{out}}$$

(23)

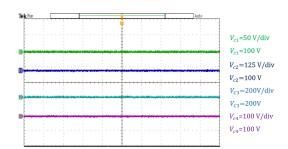

It can be seen that due to the leakage inductances, the reverse recovery problems of the diodes are mitigated. The voltage stress on  $C_1$  is 100 V, on  $C_2$  is 100 V,  $C_3$  is 200 V and on  $C_4$  is 200 V,  $C_5$  is 300 V,  $C_6$  is 300 V, and the output voltage is boosted to 800 V as illustrated above in Fig. 11.

The capacitor design is controlled by the voltage ripple of the capacitors, x is the number of any desired capacitors, and then the output voltage ripple, and the capacitor design can be derived as

$$\Delta V_{\text{out}} = \frac{(1 - D)I_{\text{out(rms)}}}{C_x f_{\text{sw}}}$$

$$C_x = \frac{(1 - D)I_{\text{c(rms)}}}{\Delta V_{\text{cx}} f_{\text{sw}}}$$

(24)

$$C_{\rm x} = \frac{(1 - D)I_{\rm c(rms)}}{\Delta V_{\rm cx} f_{\rm sw}}$$

(25)

# E. EFFICIENCY ANALYSIS

When both switches  $S_1$  and  $S_2$  conduct at the same, power loss would occur. There are two power losses; conduction

**TABLE 2.** Simulation of component parameters.

| Parameter             | Value       |

|-----------------------|-------------|

| Input voltage         | 32 V        |

| Output voltage        | 800 V       |

| Duty Cycle            | 0.68        |

| Load resistance       | $825\Omega$ |

| Magnetizing Inductors | 94 μΗ       |

| Frequency $(f_{sw})$  | 118 kHz     |

| Capacitors            | 10 μF       |

losses and switching losses. The conduction losses are caused by the parasitic resistance of the components. In addition, the conduction loss in switches is caused by the resistance of MOSFETs during conduction time and can be given as

$$P_{\text{sw(con loss)}} = (I_{\text{sw(rms)}} \times I_{\text{sw(rms)}}) R_{\text{DS(on)}}$$

(26)

where  $R_{DS(on)}$  is the drain source when the switch is ON, the switching loss in the switches can be derived as

$$P_{\text{sw(loss)}} = \frac{V_{\text{sw1}}I_{\text{sw}}(T_{\text{on,sw1}} + T_{\text{off,s1}})f_{\text{sw}}}{2} + \frac{V_{\text{sw2}}I_{\text{sw}}(T_{\text{on,sw2}} + T_{\text{off,s2}})f_{\text{sw}}}{2}$$

(27)

The losses in diodes are equal to 2.91 W and include the forward voltage, and the average diode currents, which are identical to the output current and can be expressed as

$$P_{\rm D(loss)} = I_{\rm D(avg)} \times V_{\rm F} \tag{28}$$

where  $V_{\rm F}$  is the forward voltage of the diodes. The power losses in capacitors are caused by the equivalent series resistance of the capacitor and can be derived as

$$P_{\text{C(loss)}} = (I_{\text{C(rms)}} \times I_{\text{C(rms)}}) \times \text{ESR}$$

(29)

The conduction loss of the coupled inductors in the DC resistance can be calculated as

$$P_{L(Cond loss)} = (I_{L(rms)} \times I_{L(rms)}) \times R_{L(DC)}$$

(30)

The core losses of the coupled inductors can be explored by using Steinmetz coefficients.

$$P_{\text{Core(loss)}} = K \times f^{\alpha} \times B_{\text{max}}^{\beta} \times I_{c} \times A_{c}$$

(31)

The total power loss of the proposed converter can be written as

$$P_{\text{loss(total)}} = P_{\text{SW(cond)}} + P_{\text{SW}} + P_{\text{D}} + P_{\text{C}} + P_{\text{L}} + P_{\text{Core(loss)}}$$

(32)

Consequently, the efficiency of the proposed converter can be calculated as

$$\eta = \frac{P_{\text{out}}}{P_{\text{out}} + P_{\text{loss(total)}}}$$

(33)

FIGURE 12. The input current, the input voltage, the output current and the output voltage.

**TABLE 3.** List of components for the experimental parameters.

| Components                      | Description                                                                        |

|---------------------------------|------------------------------------------------------------------------------------|

| MOSFETs $(S_1, S_2)$            | IAUT300N08S5N014 $(R_{\rm ds(on)} = 1.4 {\rm m}\Omega, 80  {\rm V}, 300  {\rm A})$ |

| Diodes $(D_1 - D_{\text{out}})$ | DPG20C300PN (300 V, 10 A, 35 ns)                                                   |

| Capacitors                      | C4ATMBW5100A3NJ (10 µF, 850 V)                                                     |

| $(C_1 - C_{\mathrm{out}})$      |                                                                                    |

| Coupled Inductor                | EDT31 ferrite core, B66397 (94 µH, N87 ma-                                         |

| $(L_{\rm m})$                   | terial)                                                                            |

FIGURE 13. The voltage stress on the capacitors.

FIGURE 14. The voltage stress on the switches.

# **IV. EXPERIMENTAL RESULTS**

A hardware prototype has been built to validate the design and the simulation results. TABLE 3 shows the components and the description of the experimental results.

The switching frequency is selected to be  $118\,\mathrm{kHz}$ , and the load resistance is chosen to be  $825\,\Omega$ . The components used to implement the prototype are shown in TABLE 1. The converter is rated at  $400\,\mathrm{W}$  with input voltage of  $32\,\mathrm{V}$  and

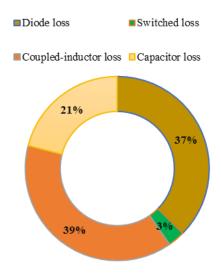

FIGURE 15. The power loss breakdown.

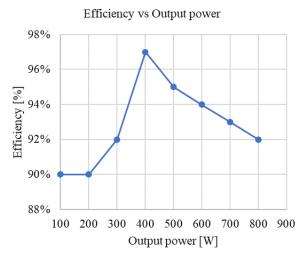

FIGURE 16. The output power (Pout) and the efficiency.

output voltage of 800 V. The active switches are performed by using MOSFETs IAUT300N08S5N014 for their low  $R_{\rm ds(on)}$  and low switching power loss. The high performance and fast recovery DPG20C300PN diodes are selected to achieve the voltage blocking on diodes. The capacitors are accomplished by using film capacitors C4ATMBW5100A3NJ to implement the voltage blocking and the output capacitor on the load. The magnetizing inductor is attained using coupled inductor and magnetic core of EDT31 ferrite core, B66397 and N87 material.

The input current is  $24.25 \, A$ , the input voltage is  $32 \, V$ , the output current is  $0.97 \, A$  and the output voltage is  $800 \, V$  as shown in Fig. 12. The voltage stress on capacitors is depicted in Fig. 13. Fig. 14 shows the voltage stresses on the active switches, which are reduced to  $100 \, V$ .

The power loss breakdown of the proposed converter is illustrated in Fig. 15, and it can be observed that the dominant power losses are the coupled inductor loss, the diode

loss, the capacitor loss and the switch loss. To enhance the efficiency of the proposed converter, more coppers are highly recommended. Fig. 16 illustrates the output power ( $P_{\text{out}}$ ) and the efficiency ( $\eta$ ) of the proposed converter.

The peak efficiency of the proposed converter is 96.7% at the output power of 400 W in diverse loads. In addition, it can be noted that the maximum efficiency occurs at 400 W.

# **V. CONCLUSION**

An interleaved high step-up dc-dc converter with coupled inductors and voltage multiplier has been proposed for renewable energy applications. The proposed converter has been successfully designed to achieve a very high step-up voltage gain without an extreme duty cycle or a high turns ratio. The aforementioned converter was considerably implemented to lift a 32 V to 800 V. The structure of the proposed converter could be extended for a higher step-up voltage gain, and the turns ratio could be increased for further voltage gain. The voltage stress across semiconductors was considerably decreased. The input current ripple was remarkably reduced due to the interleaved structure in the primary side. The reverse recovery problem of the diodes was alleviated, and the leakage energy was recycled. The MOSFETs with a small ON-resistance and low-voltage-rated were utilized to mitigate the conduction losses and the voltage stress on the switches. The analysis of the operational principle for the proposed converter was implemented, and the comparison between the suggested converter and other topologies was introduced. Moreover, the design consideration, simulation results and the experimental verifications were presented thoroughly. A 400 W hardware prototype was tested to verify the theoretical analysis and the design. The maximum efficiency was measured to be 96.7%. Therefore, the proposed converter was greatly suitable for interfacing renewable energy applications, which required high voltage gain and high efficiency.

### **REFERENCES**

- F. Blaabjerg, Y. Yang, K. Ma, and X. Wang, "Power electronics—The key technology for renewable energy system integration," in *Proc. Int. Conf. Renew. Energy Res. Appl. (ICRERA)*, Nov. 2015, pp. 1618–1626.

- [2] F. Blaabjerg and D. M. Ionel, "Renewable energy devices and systems—State-of-the-art technology, research and development, challenges and future trends," *Electr. Power Compon. Syst.*, vol. 43, no. 12, pp. 1319–1328, Jul. 2015.

- [3] Q. Zhao and F. C. Lee, "High-efficiency, high step-up DC-DC converters," IEEE Trans. Power Electron., vol. 18, no. 1, pp. 65–73, Jan. 2003.

- [4] Y. P. Hsieh, J. F. Chen, T. J. Liang, and L. S. Yang, "Novel high step-up DC–DC converter for distributed generation system," *IEEE Trans. Ind. Electron.*, vol. 60, no. 4, pp. 1473–1482, Apr. 2013.

- [5] Y. Zheng and K. M. Smedley, "Interleaved high step-up converter integrating coupled inductor and switched capacitor for distributed generation systems," *IEEE Trans. Power Electron.*, vol. 34, no. 8, pp. 7617–7628, Aug. 2019.

- [6] M. Forouzesh, Y. Shen, K. Yari, Y. P. Siwakoti, and F. Blaabjerg, "High-efficiency high step-up DC-DC converter with dual coupled inductors for grid-connected photovoltaic systems," *IEEE Trans. Power Electron.*, vol. 33, no. 7, pp. 5967–5982, Jul. 2018.

- [7] S.-K. Changchien, T.-J. Liang, J.-F. Chen, and L.-S. Yang, "Step-up DC-DC converter by coupled inductor and voltage-lift technique," *IET Power Electron.*, vol. 3, no. 3, pp. 369–378, May 2010.

- [8] H. Liu, F. Li, and J. Ai, "A novel high step-up dual switches converter with coupled inductor and voltage multiplier cell for a renewable energy system," *IEEE Trans. Power Electron.*, vol. 31, no. 7, pp. 4278–4291, Jul. 2016.

- [9] Y. Tang, T. Wang, and Y. He, "A switched-capacitor-based active-network converter with high voltage gain," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 2959–2968, Jun. 2014.

- [10] C. M. Young, M. H. Chen, and T. A. Chang, "Cascade Cockcroft—Walton voltage multiplier applied to transformerless high step-up DC–DC converter," *IEEE Trans. Ind. Electron.*, vol. 50, no. 3, pp. 1994–2004, Feb. 2013.

- [11] W. Li, X. Xiang, C. Li, W. Li, and X. He, "Interleaved high step-up ZVT converter with built-in transformer voltage doubler cell for distributed PV generation system," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 300–313, Jan. 2013.

- [12] A. Samadian, S. H. Hosseini, M. Sabahi, and M. Maalandish, "A new coupled inductor non-isolated high step up Quasi Z-source DC-DC converter," IEEE Trans. Ind. Electron, vol. 67, no. 7, pp. 5389–5397, Aug. 2019.

- [13] M.-K. Nguyen, T.-D. Duong, and Y.-C. Lim, "Switched-capacitor-based dual-switch high-boost DC-DC converter," *IEEE Trans. Power Electron.*, vol. 33, no. 5, pp. 4181–4189, May 2018.

- [14] W. Hassan, D. D.-C. Lu, and W. Xiao, "Analysis and experimental verification of a single-switch high-voltage gain ZCS DC–DC converter," *IET Power Electron.*, vol. 12, no. 8, pp. 2146–2153, Jul. 2019.

- [15] V. P. Galigekere and M. K. Kazimierczuk, "Analysis of PWM Z-source DC-DC converter in CCM for steady state," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 4, pp. 854–863, Apr. 2012.

- [16] W. Li, Y. Zhao, Y. Deng, and X. He, "Interleaved converter with voltage multiplier cell for high step-up and high-efficiency conversion," *IEEE Trans. Power Electron.*, vol. 25, no. 9, pp. 2397–2408, Sep. 2010.

- [17] W. Li, Y. Zhao, J. Wu, and X. He, "Interleaved high step-up converter with winding-cross-coupled inductors and voltage multiplier cells," *IEEE Trans. Power Electron.*, vol. 27, no. 1, pp. 133–143, Jan. 2012.

- [18] M. L. Alghaythi, R. M. O'Connell, and N. E. Islam, "Design of a high step-up DC-DC power converter with voltage multiplier cells and reduced losses on semiconductors for photovoltaic systems," in *Proc. IEEE Electr. Ship Technol. Symp. (ESTS)*, Aug. 2019, pp. 214–218.

- [19] M. Forouzesh, Y. P. Siwakoti, S. A. Gorji, F. Blaabjerg, and B. Lehman, "Step-up DC–DC converters: A comprehensive review of voltage-boosting techniques, topologies, and applications," *IEEE Trans. Power Electron.*, vol. 32, no. 12, pp. 9143–9178, Dec. 2017.

- [20] L. Zhang, D. Xu, G. Shen, M. Chen, A. Ioinovici, and X. Wu, "A high step-up DC to DC converter under alternating phase shift control for fuel cell power system," *IEEE Trans. Power Electron.*, vol. 30, no. 3, pp. 1694–1703, Mar. 2015.

- [21] W. Li, W. Li, X. Xiang, Y. Hu, and X. He, "High step-up interleaved converter with built-in transformer voltage multiplier cells for sustainable energy applications," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 2829–2836, Jun. 2014.

- [22] S. Lee, P. Kim, and S. Choi, "High step-up soft-switched converters using voltage multiplier cells," *IEEE Trans. Power Electron.*, vol. 28, no. 7, pp. 3379–3387, Jul. 2013.

- [23] O. Abutbul, A. Gherlitz, Y. Berkovich, and A. Ioinovici, "Step-up switching-mode converter with high voltage gain using a switchedcapacitor circuit," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 50, no. 8, pp. 1098–1102, Aug. 2003.

- [24] Q. Zhao and F. C. Lee, "High performance coupled-inductor DC-DC converters," in *Proc. IEEE APEC*, vol. 3, Feb. 2003, pp. 109–113.

- [25] J.-W. Baek, M.-H. Ryoo, T.-J. Kim, D.-W. Yoo, and J.-S. Kim, "High boost converter using voltage multiplier," in *Proc. 31st Annu. Conf. IEEE Ind. Electron. Soc. (IECON)*, Nov. 2005, pp. 6–10.

- [26] X. Hu and C. Gong, "A high gain input-parallel output-series DC/DC converter with dual coupled inductors," *IEEE Trans. Power Electron.*, vol. 30, no. 3, pp. 1306–1317, Mar. 2015.

- [27] T.-J. Liang, S.-M. Chen, L.-S. Yang, J.-F. Chen, and A. Ioinovici, "Ultralarge gain step-up switched-capacitor DC-DC converter with coupled inductor for alternative sources of energy," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 4, pp. 864–874, Apr. 2012.

- [28] Z. J. Yegane and A. Asghari, "A new high step-up DC/DC converter based on integrating coupled-inductor and voltage multiplier cell techniques for renewable energy applications," in *Proc. 11th Power Electron., Drive Syst., Technol. Conf. (PEDSTC)*, Feb. 2020, pp. 4255–4263.

- [29] M. L. Alghaythi, R. M. O'Connell, N. E. Islam, and J. M. Guerrero, "A multiphase-interleaved high step-up DC-DC boost converter with voltage multiplier and reduced voltage stress on semiconductors for renewable energy systems," in *Proc. IEEE Power Energy Soc. Innov. Smart Grid Technol. Conf. (ISGT)*, Feb. 2020, pp. 1–5.

- [30] Y. Xiong, S. Sun, H. Jia, P. Shea, and Z. J. Shen, "New physical insights on power MOSFET switching losses," *IEEE Trans. Power Electron.*, vol. 24, no. 2, pp. 525–531, Feb. 2009.

- [31] T. F. Wu, Y. S. Lai, J. C. Hung, and Y. M. Chen, "Boost converter with coupled inductors and buck-boost type of active clamp," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 4, no. 2, pp. 352–362, Jan. 2016.

- [32] F. Evran and M. T. Aydemir, "Isolated high step-up DC-DC converter with low voltage stress," *IEEE Trans. Power Electron.*, vol. 29, no. 7, pp. 3591–3603, Sep. 2014.

**MAMDOUH L. ALGHAYTHI** (Member, IEEE) received the B.S. degree from Jouf University, Sakaka, Aljouf, Saudi Arabia, in 2012, the M.S. degree from Southern Illinois University, Carbondale, IL, USA, in 2015, and the Ph.D. degree from the University of Missouri, Columbia, MO, USA, in 2020, all in electrical engineering.

He is currently an Assistant Professor with the Electrical Engineering Department, Jouf University. His current research interests include power

electronics, renewable energy systems, high step-up dc-dc converters, smart grids, and power converters. He is a member of the IEEE Power Electronics Society. He received a scholarship from Jouf University and the Excellence Award.

**ROBERT M. O'CONNELL** (Life Senior Member, IEEE) received the M.S. and Ph.D. degrees in electrical engineering from the University of Illinois, Urbana, in 1972 and 1975, respectively.

From 1975 to 1979, he served as a Research Electronic Engineer at the U.S. Air Force and the Director of the Power Electronics Research Center. He is currently a Professor with the Electrical Engineering and Computer Science Department, University of Missouri, Columbia, MO, USA. His

technical interests include power electronic converters, power semiconductors, power system harmonics, and power electronics curriculum development. He is a member of Eta Kappa Nu, Tau Beta Phi, the IEEE Power Electronics, and Education Societies.

NAZ E. ISLAM (Senior Member, IEEE) received the Ph.D. degree from the Rensselaer Polytechnic Institute, Troy, NY, USA, in 1992. He is currently a Professor with the Electrical Engineering and Computer Science Department, University of Missouri, Columbia, MO, USA. He is a Principal Investigator of a project in electronic systems and power semiconductors and has served as a Lead Investigator for a project involving power devices, power electronics, and fabrication studies. His cur-

rent work has been funded by the Air Force Office of Scientific Research.

MOHAMMED MASUM SIRAJ KHAN (Student Member, IEEE) received the B.S. degree in electrical and electronic engineering from the Bangladesh University of Engineering and Technology (BUET), Dhaka, Bangladesh, in 2013, and the M.S. degree in electrical engineering from Florida State University, FL, USA, in 2017. He is currently pursuing the Ph.D. degree in electrical engineering with The University of Utah, USA.

He was a Post-Graduate Intern at the National

Renewable Energy Laboratory (NREL), from June 2017 to August 2018. His current research interests include real-time modeling of power systems, power and energy management of microgrid, and modeling and design of the power electronics converters.

**JOSEP M. GUERRERO** (Fellow, IEEE) received the B.S. degree in telecommunications engineering, the M.S. degree in electronics engineering, and the Ph.D. degree in power electronics from the Technical University of Catalonia, Barcelona, in 1997, 2000, and 2003, respectively.

Since 2011, he has been a Full Professor with the Department of Energy Technology, Aalborg University, Denmark, where he is responsible for the Microgrid Research Program. Since 2014,

he has been the Chair Professor with Shandong University, Jinan, China. Since 2015, he has been a Distinguished Guest Professor with Hunan University, Changsha, China. Since 2016, he has been a Visiting Professor Fellow with Aston University, Birmingham, U.K., and a Guest Professor with the Nanjing University of Posts and Telecommunications, Nanjing, China. In 2019, he became a Villum Investigator by The Villum Fonden, which supports the Center for Research on Microgrids (CROM) at Aalborg University, being the Founder and the Director of the center. He has published more than 500 journal articles in the fields of microgrids and renewable energy systems, which are cited more than 50 000 times. His research interests include power electronics, power converters, distributed energy-storage systems, hierarchical and cooperative control, energy management systems, smart metering and the Internet of Things for ac/dc microgrid clusters and islanded minigrids; recently, specially focused on maritime microgrids for electrical ships, vessels, ferries, and seaports. He specially focused on microgrid technologies applied to offshore wind, maritime microgrids for electrical ships, vessels, ferries, and seaports and space microgrids applied to nanosatellites and spacecrafts. He was elevated as the IEEE Fellow for his contributions on distributed power systems and microgrids, in 2015. He received the Best Paper Award of the IEEE Transactions on Energy Conversion for the period 2014-2015, the Best Paper Prize of the IEEE PES, in 2015, and the Best Paper Award of the Journal of Power Electronics, in 2016. During six consecutive years, from 2014 to 2019, he was awarded by Clarivate Analytics (former Thomson Reuters) as a Highly Cited Researcher. He is an associate editor for many IEEE Transactions. He is an Associate Editor of the IEEE Transactions on Power Electronics, the IEEE Transactions on Industrial Electronics, and the IEEE Industrial Electronics Magazine and an Editor of the IEEE Transactions on Smart Grid and the IEEE TRANSACTIONS ON ENERGY CONVERSION.

. . .