## **Aalborg Universitet**

# Hybrid Transformerless PV Converters with Low Leakage Currents

Analysis and Configuration

Tang, Zhongting; Yang, Yongheng; Wan, Jianghu; Blaabjerg, Frede

Published in: **IET Renewable Power Generation**

DOI (link to publication from Publisher): 10.1049/rpg2.12029

Creative Commons License CC BY 4.0

Publication date: 2021

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Tang, Z., Yang, Y., Wan, J., & Blaabjerg, F. (2021). Hybrid Transformerless PV Converters with Low Leakage Currents: Analysis and Configuration. *IET Renewable Power Generation*, *15*(2), 368-381. https://doi.org/10.1049/rpg2.12029

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 06, 2025

#### ORIGINAL RESEARCH PAPER

# Hybrid transformerless PV converters with low leakage currents: Analysis and configuration

Zhongting Tang<sup>1</sup> Vongheng Yang<sup>1</sup> Jianghu Wan<sup>2</sup> Frede Blaabjerg<sup>1</sup>

#### Correspondence

Jianghu Wan, School of Automation, Central South University, Changsha, 410083, China. Email: wanjianghu@csu.edu.cn

#### Funding information

Novo Nordisk Fonden through the Interdisciplinary Synergy Programme, Grant/Award Number: NNF18OC0034952

### Abstract

This paper proposes a hybrid transformerless photovoltaic (PV) converter with simultaneous AC and DC outputs. It is specifically suitable for residential PV systems due to its high efficiency, versatility and flexibility, while maintaining lower leakage currents. The proposed converter is configured by replacing the control switch of the boost converter with a transformerless voltage-source inverter (VSI), enabling multiple outputs. In addition, a symmetrical boost inductor is adopted to clamp the common-mode voltage as a constant, resulting in low leakage currents. To illustrate the configuration principle, a hybrid converter with a highly efficient and reliable inverter concept (HERIC) as the VSI is exemplified. Besides, the dedicated modulation scheme for the proposed converter is detailed to achieve low leakage currents, reactive power injection and high efficiency. Furthermore, as the shoot-through state of inverter legs is allowable for the proposed converter, i.e. no need to add dead time, the reliability and power quality of the proposed converter can be improved. Simulations and experimental tests are performed on an example hybrid converter (with an HERIC as the VSI) to validate the analysis.

### 1 | INTRODUCTION

The photovoltaic (PV) energy is becoming competitive among various renewable energy sources (i.e. wind, solar thermal, hydro and wave energy) [1]. Attractive policy incentives and the continuous declining price of PV modules enable the fast development of low- and medium-power PV systems for modern commercial and residential applications [2]. As the key to the interface of the PV energy and grid, a smart inverter with high versatility (i.e. multiple sources and loads), high power density, high reliability, high efficiency and high flexibility in grid supporting is of interest in such applications [3, 4].

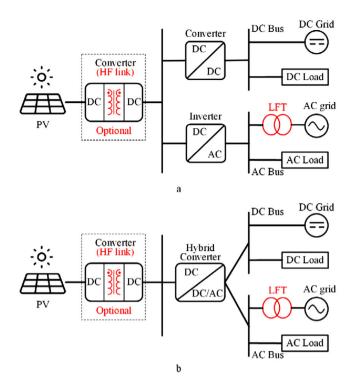

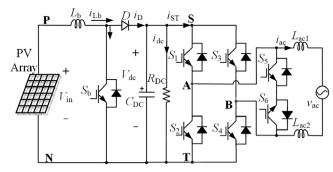

In terms of PV system configurations, the prior-art hybrid converters typically have two structures, as shown in Figure 1, where one PV source is simultaneously converted to DC and AC power at multiple buses. The hybrid converters can be used to convert the PV energy directly (i.e. the input voltage is sufficient) or indirectly (i.e. adding a DC–DC converter after the PV input to achieve a wider range of input voltages, as the optional DC–DC converter shown in Figure 1). As observed in Figure 1(a), the separated power conversions (i.e. a DC–DC

converter and an inverter) are connected to the PV source [5, 6]. In this case, although the DC output is generated by a DC-DC converter and the AC output is obtained through the inversion stage, high costs associated with large system volume are generally incurred. Besides, the disadvantages of the separated cells also exist in the traditional hybrid converter (e.g. high voltage and current stress, large power losses of the control switch in the boost converter [7] and severe distortions due to the dead time and minimum pulse width limitation of the inverter [8, 9]). Thus, to reduce the system cost, while achieving high power density and increasing reliability, the stand-alone hybrid converter was introduced [10-12], as shown in Figure 1(b). Its main advantages include the following: (1) inherent shoot-through capability eliminates the damage risk caused by external interferences (i.e. alleviating the electromagnetic interference—EMI) and decreases the distortion induced by the dead-time effects [8, 9] and (2) fewer power devices are used to perform both DC-DC and DC-AC conversions, compared to the configuration in Figure 1(a) (i.e. high power density but low system costs are possible). For example, Ray and Mishra [10] proposed a family of hybrid converter topologies with one AC and one DC

This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

© 2020 The Authors. IET Renewable Power Generation published by John Wiley & Sons Ltd on behalf of The Institution of Engineering and Technology

IET Renew. Power Gener. 2020;1–14. wileyonlinelibrary.com/iet-rpg

<sup>&</sup>lt;sup>1</sup> Department of Energy Technology, Aalborg University, Aalborg, Denmark

<sup>&</sup>lt;sup>2</sup> School of Automation, Central South University, Changsha, China

**FIGURE 1** Hybrid power converter structures for PV applications. (a) Separated converters. (b) Stand-alone hybrid converters

output, where the switch of the boost converter is replaced by a voltage-source inverter (VSI). In addition, Lee et al. [11, 12] introduced two split-source inverters to enhance the compactness, efficiency, flexible power flow and voltage boosting.

However, when applied to PV systems, the above hybrid converters, which include the traditional hybrid converters and the stand-alone hybrid converters in [10-12], have to address the leakage current issue, as required in the strict grid standards [13, 14]. Thus, either high-frequency transformers (HFTs) or lowfrequency transformers are installed between the PV panels and the AC power grid, as shown in Figure 1, where the HF-link DC-DC converter contains a DC-AC conversion, an HFT and an AC-DC conversion. Although effective galvanic isolation can be attained, the converter with transformers has low power density and high system cost. To achieve multiple outputs and simultaneously low leakage currents, a transformerless hybrid converter was proposed in [15], where the VSI is replaced by a dual-buck inverter to clamp the common-mode voltage (CMV) to zero in each operation mode. While achieving low leakage current, the dual-buck inverter has compromised on the power density and the system cost owing to the inefficient utilization of the AC filter inductors [16].

Notably, many topologies [17] and modulation methods have been reported to suppress the leakage currents for single-phase transformerless inverters in the literature, including the full-bridge inverter with a hybrid modulation scheme [18], DC-decoupling inverters [18, 20], AC-decoupling inverters [21–24] etc. Among the aforementioned inverters, the highly efficient and reliable inverter concept (HERIC) with improved modulation strategies has better performances in leakage current

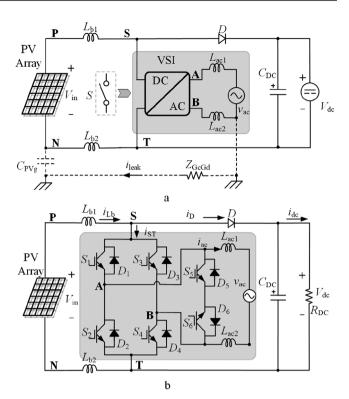

**FIGURE 2** Proposed hybrid transformerless converters. (a) General configuration. (b) Hybrid converter with the HERIC as the VSI

suppression, high efficiency and reactive power injection due to its symmetrical structure [23, 25]. It is worth noting that the reactive power injection, required by standards, e.g. the IEEE Std 1547-2018, is critical in grid-friendly and flexible PV systems [14]. When compared to the hybrid converter with standalone type [10–12, 15], the above transformerless inverters do not have shoot-through protection capability. That is, dead time is required in practice, decreasing the power quality of the grid current.

With the above concerns, to achieve simultaneous AC and DC outputs and to ensure low leakage currents, this paper proposes a hybrid transformerless converter, where the inductor of the conventional boost converter is split into two symmetrical ones (placed at the positive and negative DC rails), as shown in Figure 2(a) [26]. In addition, the switch of the conventional boost converter is replaced with a transformerless VSI. Thus, the proposed hybrid power converter structure can maintain a constant CMV (i.e. leading to low leakage currents) with a dedicated modulation scheme. The configuration principle is demonstrated on the converter taking the HERIC (i.e. owning reactive power injection with the improved modulation method mentioned above) as the VSI in Section 2. Moreover, the modulation and operation modes (i.e. including the operation principle and CMV analysis) of the proposed converter are presented in detail. In Section 3, the steady-state analysis, component design and control strategy are given. Then, Section 4 presents the losses analysis and comparisons with prior-art hybrid converters. Due to the shoot-through capability and symmetrical structure, the proposed converter with the dedicated

modulation method can achieve good performances in terms of low leakage currents, high power quality, reactive power injection, high efficiency and high reliability, while maintaining low system costs. Simulation and experimental results are provided in Section 5, which validates the effectiveness of the proposed hybrid transformerless power converter. Finally, Section 6 gives concluding remarks.

## 2 | CONFIGURATION PRINCIPLE OF THE PROPOSED HYBRID TRANSFORMERLESS CONVERTER

## 2.1 Configuration of the proposed converter

The general configuration of the proposed transformerless hybrid converter is illustrated in Figure 2(a). As shown in Figure 2(a), the following principles are considered when deriving the hybrid converters: (1) two symmetrical boost inductors (i.e.  $L_{\rm b1}$  and  $L_{\rm b2}$  with  $L_{\rm b1} = L_{\rm b2}$ ) are placed at the positive and negative DC rails; (2) a transformerless VSI, which can clamp the CMV to be half of the DC input voltage, is adopted to replace the control switch of the boost converter; (3) a power diode D and an output capacitor  $C_{\rm DC}$  are used for the DC-DC conversion to supply DC loads as well as absorbing the pulsating power generated by the VSI; and (4) symmetrical output Ltype filters are used for good current quality and also to reduce the impact from the differential-mode voltage (DMV), where  $L_{ac1} = L_{ac2} = L_{ac}/2$ . Furthermore, the leakage current path is also exemplified in Figure 2(a), where  $Z_{GcGd}$  is the impedance between the PV parasitic capacitor  $C_{PVg}$  and the ground, and  $\dot{q}_{\rm eak}$  is the leakage current. In Figure 2, **P** and **N** are the positive and negative terminals of the DC input and S and N are the positive and negative input terminals of the VSI, with A and B being its output terminals.

In this paper, the above configuration principle is further elaborated on an HERIC-based hybrid converter. According to Figure 2(a), the VSI of the hybrid transformerless converter can be replaced by an HERIC topology (i.e. including the power devices  $S_{1-6}$  with the anti-parallel diodes  $D_{1-6}$ ) [23], as shown in Figure 2(b). Moreover,  $V_{\rm in}$ ,  $V_{\rm dc}$  and  $v_{\rm ac}$  are the DC input voltage, the DC output voltage and the AC output voltage, respectively.  $i_{\rm Lb}$  is the current of the symmetrical boost inductors,  $i_{\rm ST}$  is the VSI input current,  $i_{\rm D}$  is the power diode current and  $i_{\rm dc}$  is the DC load current. Furthermore,  $i_{\rm ac}$  is the grid current, and its positive direction is defined as the direction from the VSI to the AC grid. Operation modes and the CMV analysis of the proposed converter are then detailed considering a DC load  $R_{\rm DC}$  and an AC grid.

As mentioned previously, the proposed hybrid transformerless PV converter should maintain a constant CMV to suppress leakage current. Therefore, except for the structure of the symmetrical inductors and a transformerless inverter with CMV clamping, a dedicated modulation should also be employed in the proposed hybrid converter, as detailed in the following.

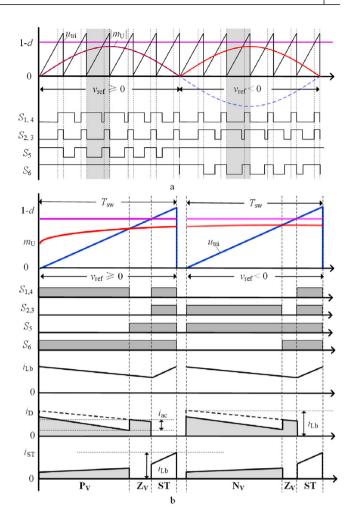

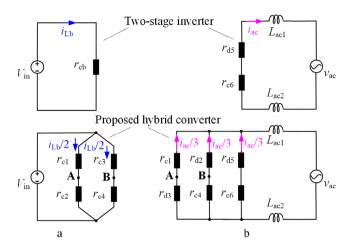

**FIGURE 3** Modulation scheme of the proposed converter, where d represents the **ST** interval and  $m_U$  is the modulation signal. (a) Modulation scheme. (b) Key current waveforms

#### 2.2 | Modulation

For simplicity, only the continuous conduction mode is considered when the hybrid converter is operating as a boost converter. Figure 3(a) shows the modulation method of the proposed converter, where a triangular carrier is adopted, d represents the duty cycle of the shoot-through interval (i.e. representing the ratio of the on-time to the switching period time in a boost converter) and  $m_{\rm U}$  is the duty cycle of the modulation signal with the improved modulation method for the HERIC [i.e. being the same as the unipolar pulse width modulation (PWM)] [25]. Accordingly, there are four operation modes of the proposed converter, i.e. **ST**, **Pv**, **Nv** and **Zv**, where **ST** is the shoot-through mode, **Pv** represents the mode of the DMV  $v_{\rm dm}$  being positive ( $v_{\rm dm} = +V_{\rm dc}$ ), **Nv** denotes the mode of  $v_{\rm dm}$  being negative ( $v_{\rm dm} = -V_{\rm dc}$ ) and **Zv** indicates the mode of  $v_{\rm dm}$  being zero ( $v_{\rm dm} = 0$ ).

According to the zoomed-in view of Figure 3(a) in one switching cycle  $T_{\rm sw}$ , as shown in Figure 3(b), the operation

modes can be expressed as

$$Mode \Leftrightarrow \begin{cases} P_{\rm V}, \ 0 \leq u_{\rm tri} < |m_{\rm U}|, \ v_{\rm ref} > 0 \\ N_{\rm V}, \ 0 \leq u_{\rm tri} < |m_{\rm U}|, \ v_{\rm ref} < 0 \\ Z_{\rm V}, \ |m_{\rm U}| \leq u_{\rm tri} < 1 - d \\ {\rm ST}, \ 1 - d \leq u_{\rm tri} \leq 1 \end{cases}$$

where  $u_{tri}$  is the carrier amplitude.

Key waveforms ( $i_{Lb}$ ,  $i_D$  and  $i_{ST}$ ) are also given in Figure 3(b). Clearly,  $i_{Lb}$  increases in the **ST** mode to boost the voltage, and it decreases in other modes (**Pv**, **Nv** and **Zv**). Based on the Kirchhoff's current law, at the node **S**, the current can be expressed as

$$i_{\rm Lb} = i_{\rm ST} + i_{\rm D} \tag{1}$$

which is consistent with that in Figure 3(b). Notably, although the HERIC can also generate three voltage levels, i.e. zero voltage during the **ST** and **Zv** modes,  $+V_{\rm dc}$  during the **Pv** interval and  $-V_{\rm dc}$  for the **Nv** interval, there are only two voltage levels changing (i.e. between  $+V_{\rm dc}$  and 0 or  $-V_{\rm dc}$  and 0) in half a cycle.

## 2.3 | Analysis of common-mode voltage

When the voltage of parasitic capacitance  $C_{\rm PVg}$  (see Figure 2) changes at a high frequency, large leakage currents will be generated. Then, it increases system power losses, induces EMI issues and poses serious safety problems to personnel and other equipment [27]. According to [13], the distributed generation system must be triggered within a certain time to ensure safety, when the leakage current exceeds 300 mA (root-mean-square (RMS) value). To achieve a low leakage current, the CMV must be a constant or vary at a very low frequency. Assuming  $L_{\rm ac1} = L_{\rm ac2}$ , the DMV impact on the leakage current can be neglected. According to Figure 2(a), the CMV ( $v_{\rm cm}$ ) and the DMV ( $v_{\rm dm}$ ) of the proposed converter can be given as

$$v_{\rm cm} = \frac{v_{\rm AN} + v_{\rm BN}}{2} \tag{2}$$

$$v_{\rm d}m = v_{\rm AT} - v_{\rm BT} \tag{3}$$

where  $v_{\rm AN}$  and  $v_{\rm BN}$  are the voltages of terminals **A** and **B** to **N**,  $v_{\rm AT}$  and  $v_{\rm BT}$  are the voltages of terminals **A** and **B** to **T**, and  $v_{\rm ST}$  represents the voltage of the terminal **S** to **T**, respectively.

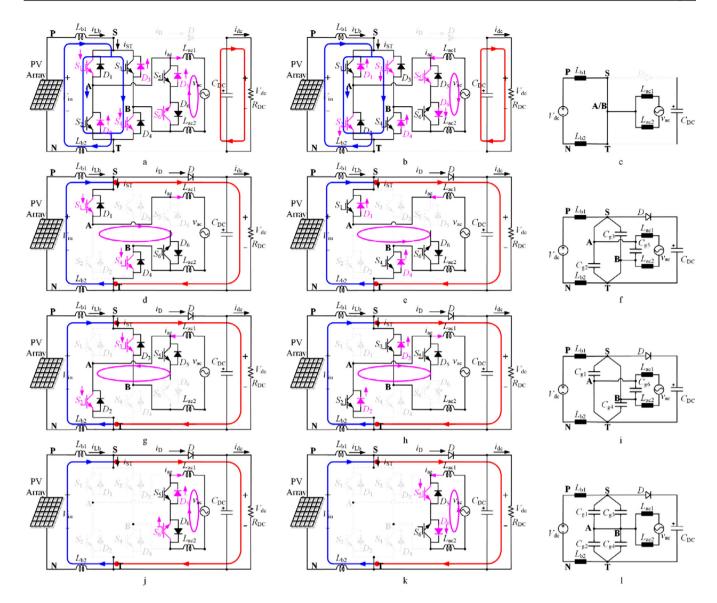

Figure 4 shows the four operation modes (i.e. **ST** mode, **Pv** mode, **Nv** mode and **Zv** mode) and their equivalent circuits, where  $C_{\rm g1-4}$  is the corresponding junction capacitance of the switches  $S_{\rm 1-4}$ . Then, the CMV and DMV can be analyzed in different modes as follows.

a. *ST mode*: Figure 4(a)–(c) illustrates the **ST** mode, during which the HERIC is taken as a boost switch (i.e.  $S_{1-6}$  are ON). Then,  $L_{\rm b1}$  and  $L_{\rm b2}$  are charged by the DC input source.

As shown in Figure 3(b), the boost inductor current  $i_{\rm Lb}$  increases, and  $V_{\rm Lb1} = V_{\rm Lb2} = V_{\rm in}/2$ . The power diode D is reverse-biased, and  $i_{\rm D} = 0$ . The capacitor  $C_{\rm DC}$  is discharged to supply the load  $R_{\rm DC}$ . Figure 4(c) presents the equivalent circuit of the **ST** mode, where the CMV is clamped by  $L_{\rm b1}$  and  $L_{\rm b2}$ , and the terminal voltages  $v_{\rm AN} = v_{\rm BN} = V_{\rm Lb2}$  and  $v_{\rm AT} = v_{\rm BT} = 0$ . Then, the voltages  $v_{\rm cm}$  and  $v_{\rm dm}$  can be expressed as

$$v_{\rm cm} = \frac{v_{\rm AN} + v_{\rm BN}}{2} = \frac{V_{\rm Lb2} + V_{\rm Lb2}}{2} = \frac{V_{\rm in}}{2}$$

(4)

$$v_{\rm dm} = v_{\rm AT} - v_{\rm BT} = 0 - 0 = 0.$$

(5)

The HERIC operates in a freewheeling interval at this time. As shown in Figure 4(a) and (b), there are three bidirectional current paths for the grid current  $i_{ac}$ . When  $i_{ac} \ge 0$ ,  $i_{ac}$  can flow through  $S_6$  and  $D_5$ ,  $S_4$  and  $D_2$  and  $S_1$  and  $D_3$  [i.e. the pink components in Figure 4(a)]. While  $i_{ac} < 0$ , as seen as the pink components in Figure 4(b), the three current paths are flowing through  $S_5$  and  $D_6$ ,  $S_2$  and  $D_4$ , and  $S_3$  and  $D_1$ .

b. **Pv** mode: As shown in Figure 4(d)–(f), the HERIC operates as a VSI in the positive half-cycle (i.e.  $v_{\rm ref} \ge 0$ ).  $S_1$ ,  $S_4$  and  $S_6$  are ON, while  $S_2$ ,  $S_3$  and  $S_5$  are OFF to achieve  $v_{\rm dm} = +V_{\rm dc}$ . As demonstrated in Figure 3(b), the boost current  $i_{\rm Lb}$  decreases, and it simultaneously flows through the diode D and the HERIC. The capacitor  $C_{\rm DC}$  is then charged, and the charging voltage is  $v_{\rm ST} = V_{\rm dc} = V_{\rm in} + V_{\rm Lb1} + V_{\rm Lb2}$ . Additionally,  $v_{\rm ST}$  provides the DC load voltage. As shown in Figure 4(f) (i.e. the equivalent circuit of the Pv mode), the terminal voltages are  $v_{\rm AN} = V_{\rm in} + V_{\rm Lb1}$ ,  $v_{\rm BN} = -V_{\rm Lb2}$ ,  $v_{\rm AT} = V_{\rm in} + V_{\rm Lb1} + V_{\rm Lb2}$  and  $v_{\rm BT} = 0$ . The voltages  $v_{\rm cm}$  and  $v_{\rm dm}$  in this operation mode are calculated as

$$v_{\rm cm} = \frac{v_{\rm AN} + v_{\rm BN}}{2} = \frac{V_{\rm in} + V_{\rm Lb1} - V_{\rm Lb2}}{2} = \frac{V_{\rm in}}{2}$$

(6)

$$v_{\rm d} = v_{\rm AT} - v_{\rm BT} = V_{\rm in} + V_{\rm Lb1} + V_{\rm Lb2} - 0 = V_{\rm dc}$$

(7)

where the symmetrical filter voltages are equal, i.e.  $V_{\rm Lb1} = V_{\rm Lb2}$ . Regarding the HERIC, there is a bidirectional current path for the grid current  $i_{\rm ac}$  in the **Pv** mode, as presented in Figure 4(d) and (e).  $i_{\rm ac} \geq 0$ ,  $i_{\rm ac}$  flows through  $S_1$  and  $S_4$  to achieve  $v_{\rm dm} = V_{\rm dc}$  [i.e. the pink components in Figure 4(d)];  $i_{\rm ac} < 0$ ,  $i_{\rm ac}$  flows through  $D_1$  and  $D_4$  to achieve  $v_{\rm dm} = V_{\rm dc}$  [i.e. the pink components in Figure 4(e)].

c. Nv mode: As presented in Figure 4(g)–(i), the HERIC works in the negative half-cycle (i.e.  $v_{\rm ref} < 0$ ) as a VSI. In this case,  $S_2$ ,  $S_3$  and  $S_5$  are ON, while  $S_1$ ,  $S_4$  and  $S_6$  are OFF to achieve  $v_{\rm dm} = -V_{\rm dc}$ . In the Nv mode, the key current waveforms are shown in Figure 3(b), where the boost filters are in discharging mode to support the operation of the HERIC, to charge the capacitor  $C_{\rm DC}$  and to supply the DC load. Moreover, as observed in Figure 4(i) (i.e. the equivalent circuit of the Nv mode), the terminal voltages are  $v_{\rm ST} = V_{\rm dc} = V_{\rm in} + V_{\rm Lb1} + V_{\rm Lb2}$ , vAN =  $-V_{\rm Lb2}$ ,  $v_{\rm BN} = V_{\rm in} + V_{\rm Lb1}$ ,  $v_{\rm AT} = 0$  and  $v_{\rm BT} = V_{\rm in} + V_{\rm Lb1} + V_{\rm Lb2}$ . Hence,  $v_{\rm cm}$  and  $v_{\rm dm}$  can be given

FIGURE 4 Operation modes and their equivalent circuits of the proposed symmetrical transformerless hybrid converter. (a) ST mode,  $i_{ac} \ge 0$ . (b) ST mode,  $i_{ac} < 0$ . (c) ST mode, equivalent circuit. (d) Pv mode,  $i_{ac} \ge 0$ . (e) Pv mode,  $i_{ac} < 0$ . (f) Pv mode, equivalent circuit. (g) Nv mode,  $i_{ac} \ge 0$ . (h) Nv mode,  $i_{ac} < 0$ . (i) Nv mode, equivalent circuit. (j) Zv mode,  $i_{ac} \ge 0$ . (k) Zv mode,  $i_{ac} < 0$ . (l) Zv mode, equivalent circuit

by

$$v_{\rm cm} = \frac{v_{\rm AN} + v_{\rm BN}}{2} = \frac{-V_{\rm Lb2} + V_{\rm in} + V_{\rm Lb1}}{2} = \frac{V_{\rm in}}{2}$$

(8)

$$v_{\text{d}m} = v_{\text{AT}} - v_{\text{BT}} = 0 - (V_{\text{in}} + V_{\text{Lb1}} + V_{\text{Lb2}}) = -V_{\text{dc}}$$

(9)

in which  $V_{\rm Lb1} = V_{\rm Lb2}$ . As depicted in Figure 4(g) and (h), the HERIC can also provide a bidirectional current path. When  $i_{\rm ac} \geq 0$ ,  $i_{\rm ac}$  flows through  $S_2$  and  $S_3$  to obtain  $v_{\rm dm} = -{\rm Vdc}$ , as shown as the pink components in Figure 4(g). When  $i_{\rm ac} < 0$ ,  $i_{\rm ac}$  flows through  $D_2$  and  $D_3$  to achieve  $v_{\rm dm} = -{\rm Vdc}$ , as presented as the pink components in Figure 4(h).

d.  $\mathbf{Zv}$  mode: In this case, as shown in Figure 4(j)–(l),  $S_5$  and  $S_6$  are ON and  $S_{1-4}$  are OFF. According to the key current waveforms in Figure 3(b),  $i_{\mathrm{Lb}}$  decreased and the boost inductors provide power to the output capacitor and DC load simultaneously. Then, the CMV is clamped by the switch junction capacitors  $C_{\mathrm{g1-4}}$  (i.e. assuming  $C_{\mathrm{g1}} = C_{\mathrm{g2}} = C_{\mathrm{g3}} = C_{\mathrm{g4}}$ ), as depicted in Figure 4(l). Consequently, the voltage of those junction capacitances  $V_{\mathrm{Cg1-4}}$  can be expressed as

$$V_{\text{Cg1-4}} = \frac{V_{\text{in}} + V_{\text{Lb1}} + V_{\text{Lb2}}}{2}.$$

(10)

Notice that the terminal voltages are  $v_{\rm AN} = V_{\rm Cg2} - V_{\rm Lb2}$ ,  $v_{\rm BN} = V_{\rm Cg4} - V_{\rm Lb2}$ ,  $v_{\rm AT} = V_{\rm Cg2}$ ,  $v_{\rm BT} = V_{\rm Cg4}$  and  $V_{\rm Lb1} = V_{\rm Lb2}$ ;

$v_{\rm cm}$  and  $v_{\rm dm}$  in Figure 4(1) can be obtained as

$$v_{\rm cm} = \frac{v_{\rm AN} + v_{\rm BN}}{2} = \frac{\left(V_{\rm Cg2} - V_{\rm Lb2}\right) + \left(V_{\rm Cg4} - V_{\rm Lb2}\right)}{2} = V_{\rm in}$$

(11)

$$v_{dm} = v_{AT} - v_{BT} = V_{Cg2} - V_{Cg4} = 0.$$

(12)

Similarly, the grid current  $i_{\rm ac}$  has a bidirectional path [i.e. shown in Figure 4(j) and (k)].  $i_{\rm ac}$  flows through  $S_6$  and  $D_5$  when  $i_{\rm ac} \geq 0$ , as shown as the pink components in Figure 4(j).  $i_{\rm ac}$  flows through  $S_5$  and  $D_6$  when  $i_{\rm ac} < 0$ , as demonstrated as the pink components in Figure 4(k).

According to the above analysis, the proposed converter can clamp the CMV to be half of the input voltage  $V_{\rm in}$  in all operation modes, i.e. Equations (4), (6), (8), and (11). In addition, it can achieve the bidirectional current path in any operation mode. Therefore, it has a good performance in terms of low leakage currents and flexible reactive power injection (due to the possibility of bidirectional current flow).

## 3 | SYSTEM DESIGN

### 3.1 | Steady-state analysis

Considering a single-switch boost converter [28], the relationship between the DC input voltage  $V_{\rm in}$  and the DC output voltage  $V_{\rm dc}$  can be expressed as

$$\frac{V_{\rm dc}}{V_{\rm in}} = \frac{1}{1 - d} \tag{13}$$

which illustrates that the DC gain of the hybrid converter is also 1/(1-d). The HERIC output will be zero at this moment. Furthermore, the duty cycle of the modulation signal for the DC–AC conversion i.e.  $m_{\rm IL}$  can be calculated as

$$m_{\rm U} = \frac{v_{\rm ac}}{V_{\rm dc}} = \frac{v_{\rm ac} (1 - d)}{V_{\rm in}}$$

(14)

Since the DC–DC and DC–AC conversions should be finished in one switching cycle, d and  $m_U$  should be bounded as

$$d + m_{\text{U}} \le 1. \tag{15}$$

Accordingly, the maximum value of the modulation signal must be  $m_{\rm Umax} \leq 1-d$ , resulting in that the peak of the AC output voltage  $V_{\rm acpeak}$  should be constrained as

$$V_{\text{acpeak}} = m_{\text{Umax}} V_{\text{dc}} \le \frac{V_{\text{in}} (1 - d)}{(1 - d)} = V_{\text{in}}$$

(16)

implying that the input voltage  $V_{\rm dc}$  must be larger than the peak grid voltage  $V_{\rm acpeak}$  to ensure simultaneous DC and AC outputs. This is also the case for conventional VSIs. Notably, the DC–DC gain is adjustable from 1 to infinity in theory.

Moreover, the AC output can be connected to a grid or loads, while the DC output can also be connected to a DC grid or DC

loads. This paper focuses on the low leakage currents and the reactive power injection in the AC side of the proposed converter. Thus, a passive DC load and a grid are considered. As mentioned previously, when applied to PV systems, the hybrid converter can be used to convert the PV energy directly or indirectly. Therefore, if the proposed converter is employed in a single-stage grid-connected PV system, the control strategies should adopt an effective operation [29]. Thus, when designing the control scheme for the proposed converter, the following should be considered.

- V<sub>acpeak</sub> ≤ V<sub>in</sub> ≤ V<sub>dc</sub>. The hybrid converter simultaneously outputs DC and AC power. Generally, the PV input voltage is fluctuating in a small range under various irradiance conditions [29]. Thus, the operation of the hybrid converter will not be affected when the fluctuating voltage is within this range of [V<sub>acpeak</sub>, V<sub>dc</sub>].

- 2.  $V_{\rm acpeak} > \dot{V_{\rm in}}$ . The hybrid converter acts as the conventional boost converter, and the AC grid can be disconnected to ensure the modulation of the VSI according to Equation (16), or the PV energy can be transmitted to DC output. As an alternative, the boost inductor can be replaced by a symmetrical impedance network [30] in a way to improve the boosting.

Notably, there are limitations for the AC and DC output power due to the unidirectional conduction of the power diode D [10]. Hence, the pulsating power of the VSI only can be absorbed by the DC output capacitor  $C_{\rm CD}$  and then consumed at the DC output. That is, the power limitation of the proposed converter can be expressed as

$$P_{\rm dc} \ge P_{\rm r}$$

(17)

where  $P_{\rm dc}$  represents the DC output power, and  $P_{\rm r}=0.5\,V_{\rm m}I_{\rm m}{\rm cos}(2\omega+\varphi)$  is the instantaneous pulsating power, with  $V_{\rm m}$  and  $I_{\rm m}$  being the amplitudes of the grid voltage and current, and  $\varphi$  being the displacement angle. Therefore, the proposed converter can only be operated as a boost converter instead of a VSI, if one output is needed.

#### 3.2 | Component design

The passive components of the hybrid converter include the symmetrical boost inductors  $L_{\rm b1}$  and  $L_{\rm b2}$  (i.e.  $L_{\rm b1} = L_{\rm b2}$ ), the DC output capacitor CDC and the symmetrical L-type filter  $L_{\rm ac1}$  and  $L_{\rm ac2}$  (i.e.  $L_{\rm ac1} = L_{\rm ac2}$ ). Since the AC output filters can be designed following the rules of the prior-art grid-connected VSIs [17–24], the design of  $L_{\rm ac1}$  and  $L_{\rm ac2}$  of the proposed converter is not discussed here. To ensure the operation,  $L_{\rm b1}$ ,  $L_{\rm b2}$  and  $C_{\rm DC}$  should be properly designed in the following.

1. Boost inductors  $L_{b1}$  and  $L_{b2}$ : The design of the boost inductors is related to the current ripple ratio  $\gamma$ , and the optimal value of  $\gamma$  is 0.4 when considering the overall stresses and power density in a converter [31]. Therefore, the boost inductors of

FIGURE 5 General control block diagram for the proposed converter

the proposed converter can be designed as

$$L_{b1} = L_{b2} = \frac{L_b}{2} \ge \frac{V_{in}d}{\gamma I_{Lb} f_{sw}}$$

(18)

where  $L_{\rm b}$  represents the total inductance of the boost inductors,  $I_{\rm Lb}$  is the average value of the boost inductor current  $i_{\rm Lb}$  and  $f_{\rm sw}$  is the switching frequency.

2. DC output capacitor  $C_{DC}$ : The DC output capacitor for the proposed converter is designed to maintain and filter the DC output voltage. At the same time, it balances the pulsating power of the VSI. When considering the DC output ripple voltage of the boost converter, i.e.  $\Delta V_{\rm dc}$ ,  $C_{\rm DC}$  should be designed as

$$C_{\rm DC} \ge \frac{I_{\rm dc}d}{\Delta V_{\rm dc}f_{\rm sw}}$$

(19)

where  $I_{\rm dc}$  is the average value of the DC output current  $i_{\rm dc}$ . As seen from the energy storage perspective, large inductance is generally required to store the same amount of energy, when compared to capacitors. That is, inductors have low cost-effectiveness to balance the inherent pulsating power. Hence, only the DC-link capacitor is considered for the conventional single-phase VSI to maintain power density [32]. Considering the power balance,  $C_{\rm DC}$  should be

$$C_{\rm DC} \ge \frac{P_{\rm r}}{\omega V_{\rm dr} \Delta V_{\rm r}}$$

(20)

in which  $\Delta V_r$  is the required pulsating voltage,  $\omega$  is the grid frequency, and  $P_r$  is the instantaneous pulsating power, respectively. According to Equations (18) and (19), the output capacitor  $C_{\rm DC}$  can be selected as

$$C_{\rm DC} = \max\left(\frac{I_{\rm dc}d}{\Delta V_{\rm dc}f_{\rm sw}}, \frac{P_{\rm r}}{\omega V_{\rm dc}\Delta V_{\rm r}}\right).$$

(21)

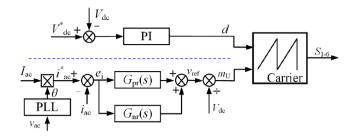

## 3.3 | Basic control

To simplify the control, the PV input voltage  $V_{\rm in}$  is assumed as a constant. The control for the proposed converter includes two parts, as shown in Figure 5. One is the voltage loop with a proportional-integral controller for the DC output, where  $V_{\rm dc}^*$  is the voltage reference. The other is a proportional-resonant con-

**FIGURE 6** Traditional two-stage inverter with the HERIC as the VSI, where  $S_b$  is the boost control switch, the boost converter operates as the **ST** mode, and the HERIC inverter is in the freewheeling interval

troller  $G_{\rm pr}(s)$  with multi-resonant controllers  $G_{\rm nr}(s)$  for the AC regulation, which can achieve zero-error tracking and improve the power quality [8]. Moreover,  $I_{\rm ref}$  is the amplitude of the reference current  $i_{\rm ac}^*$ , and the phase angle  $\theta$  is achieved through the phase-locked loop of  $v_{\rm ac}$  (i.e. performing grid synchronization). In addition, only one resonant controller  $G_{3\rm r}(s)$  is adopted for simplicity. In all, good performances in terms of fast dynamics and good power quality can be achieved in this way.

#### 4 | COMPARISON ANALYSIS

## 4.1 Loss analysis and comparison

The loss analysis and comparison are carried out when the proposed converter adopts insulated-gate bipolar transistor (IGBT) power devices. According to [33], the IGBT losses consist of the conduction losses, switching losses and negligible blocking losses. The proposed converter is then compared with the traditional two-stage inverter with an HERIC, as shown in Figure 6, in terms of power losses. For a fair comparison, the two-stage inverter supplies a DC load  $R_{\rm CD}$  at the DC link, as demonstrated in Figure 6.

Conduction losses: The IGBT conduction losses can be calculated as

$$P_{\rm CT} = \frac{1}{T_{\rm sw}} \int_0^{T_{\rm sw}} \left( V_{\rm ce0} i_{\rm c} + r_{\rm c} i_{\rm c}^2 \right) dt = V_{\rm ce0} I_{\rm cav} + r_{\rm c} I_{\rm crms}^2 \quad (22)$$

in which  $V_{\rm ce0}$  is the IGBT ON-state zero-current collector-emitter voltage, and  $r_{\rm c}$  represents the collector-emitter ON-state resistance [33]. In addition,  $I_{\rm cav}$  and  $I_{\rm crms}$  are the average and RMS IGBT currents. Similarly, the anti-parallel diode conduction losses can be expressed as

$$P_{\rm CD} = \frac{1}{T_{\rm sw}} \int_0^{T_{\rm sw}} \left( V_{\rm d0} i_{\rm d} + r_{\rm d} i_{\rm d}^2 \right) dt = V_{\rm d0} I_{\rm dav} + r_{\rm d} I_{\rm drms}^2$$

(23)

where  $V_{\rm d0}$  is the diode on-state zero-current voltage,  $r_{\rm d}$  represents the diode ON-state resistance [33] and  $I_{\rm dav}$  and  $I_{\rm drms}$  are the average and RMS diode currents, respectively.

**FIGURE 7** Equivalent circuits of the systems when  $S_b$  is ON or in the **ST** mode, where the upper diagrams are the equivalent circuits of two-stage inverter in Fig. 6, and the lower ones are those of the proposed converter, the IGBT ON-state resistance are  $r_{\rm cb} = r_{\rm cl-6} = r_{\rm c}$ , and the diode ON-state resistance are  $r_{\rm dl-6} = r_{\rm d}$ . (a) Boost operation. (b) Freewheeling operation

When operating in the inversion, the conduction losses are identical in both the proposed converter and the traditional two-stage inverter (see Figure 6). Figure 7 shows the equivalent circuit of both converters when  $S_b$  of the two-stage inverter is ON or the proposed converter is in the **ST** mode. Assuming that the grid current  $i_{ac}$  is positive,  $i_{ac}$  flows through  $S_6$  and  $S_5$  of the traditional two-stage inverter at this period. The losses comparison results are presented in Table 1, and the corresponding analysis is in the following.

- As presented in Figure 7(a), the boost inductor current i<sub>Lb</sub> flows through S<sub>b</sub> of the traditional two-stage inverter, while it flows through S<sub>1-4</sub> in the proposed converter. Thus, the conduction losses induced by i<sub>Lb</sub> are almost the same with a difference of V<sub>ce0</sub>I<sub>Lb</sub>.

- 2. In the **ST** mode, the grid current  $i_{ac}$  of the proposed converter has three paths, while  $i_{ac}$  of the traditional two-stage inverter only has one path, resulting in lower conduction losses.

- 3. For the diode D, the diode average current  $I_{\rm dav}$  of the proposed converter is equal to  $I_{\rm dc}$  (i.e. the average of the DC output current  $i_{\rm dc}$ ), while  $I_{\rm dav} = I_{\rm dc} + 2I_{\rm m}/\pi$  in the traditional two-stage inverter (i.e.  $2I_{\rm m}/\pi$  is the average of the grid current  $i_{\rm ac}$ ). That is, the conduction losses of the two-stage inverter are larger than those of the proposed converter, especially when the AC output power is large.

Switching losses: According to [33], the switching losses of the IGBT contains turn-ON losses, turn-OFF losses and reverse-recovery losses, which can be calculated as

$$P_{S} = P_{\text{swT}} + P_{\text{swD}} = (E_{\text{onT}} + E_{\text{offT}} + E_{\text{onD}}) f_{\text{sw}} \frac{V_{\text{ceav}} I_{\text{cav}}}{V_{\text{CC}} I_{\text{CC}}}$$

(24)

where  $P_{\rm swT}$  and  $P_{\rm swD}$  are the switching losses of the IGBT and the anti-parallel diode, and  $E_{\rm onT}$ ,  $E_{\rm offT}$  and  $E_{\rm onD}$  are the

TABLE 1

Loss analysis and comparison of the systems in Figs. 2(b) and 6, supplying the same loads

| Converter          | Conduction losses due to $\dot{t}_{\mathrm{Lb}}$ | Conduction losses due to $i_{ac}$<br>(ST mode)                                              | ${\sf Conduction  losses  of  } D$                                                                                               | Switching losses                                                                                                                                                                                                                                     |

|--------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Proposed converter | $2V_{\rm ce0}I_{\rm Lb} + r_{\rm c}I_{\rm Lb}^2$ | $(V_{cc0} + V_{d0}) \frac{2l_{\rm m}}{\pi} + (r_{\rm c} + r_{\rm d}) \frac{l_{\rm m}^2}{6}$ | $V_{ m d0}I_{ m dc}+r_{ m d}I_{ m dc}^2$                                                                                         | $(E_{\text{onIT}} + E_{\text{offT}}) \frac{\int_{s_W} V_d e I_{\text{lb}}}{V_{\text{CC}} I_{\text{CC}}} + (E_{\text{offT}} + E_{\text{onD}}) \frac{2 I_{s_W} V_d e^{I_{\text{lm}}}}{\pi V_{\text{CC}} I_{\text{CC}}}$                                |

| Two-stage inverter | $V_{\rm ce0}I_{\rm Lb} + r_{\rm c}I_{\rm Lb}^2$  | $(V_{ce0} + V_{d0}) \frac{2I_m}{\pi} + (r_c + r_d) \frac{I_m^2}{2}$                         | $V_{\rm d0}(\frac{2I_{\rm m}}{\pi} + I_{ m dc}) + r_{ m d}(\frac{I_{ m m}^2}{2} + \frac{4I_{ m m}I_{ m dc}}{\pi} + I_{ m dc}^2)$ | $(E_{\text{onT}} + E_{\text{ofFI}}) \frac{f_{\text{sw}}V_{\text{de}}I_{\text{lb}}}{V_{\text{Cc}}I_{\text{CC}}} + (E_{\text{onT}} + E_{\text{ofFI}} + E_{\text{onD}}) \frac{2f_{\text{sw}}V_{\text{de}}I_{\text{m}}}{\pi V_{\text{Cc}}I_{\text{CC}}}$ |

| TABLE 2 | Comparison of the pr | oposed converter and | prior-art converters |

|---------|----------------------|----------------------|----------------------|

|         |                      |                      |                      |

| Category                                    | Traditional two-stage inverter (Figure 6)                                        | BDHC in [10]                                                          | Transformerless hybrid converter in [15]                              | Proposed converter                                                              |

|---------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Device-count                                | Seven IGBTs, one diode                                                           | Four IGBTs, one diode                                                 | Six IGBTs, one diode                                                  | Six IGBTs, one diode                                                            |

| Device stress                               | IGBT: $V_{dc}$ , max $(i_{dc}, i_{ac})$<br>Diode: $V_{dc}$ , $i_{dc}$ + $i_{ac}$ | IGBT: $V_{dc}$ , max $(i_{dc}, i_{ac})$<br>Diode: $V_{dc}$ , $i_{dc}$ | IGBT: $V_{dc}$ , max $(i_{dc}, i_{ac})$<br>Diode: $V_{dc}$ , $i_{dc}$ | IGBT: $V_{dc}$ , max $(i_{dc}/2, i_{ac})$<br>Diode: $V_{dc} - V_{in}/2, i_{dc}$ |

| DC gain                                     | $\frac{1}{1-d}$                                                                  | $\frac{1}{1-d}$                                                       | $\frac{1}{1-d}$                                                       | $\frac{1}{1-d}$                                                                 |

| ${\rm AC~gain}~(V_{\rm acpeak}/V_{\rm in})$ | $\frac{1}{1-d}$                                                                  | 1                                                                     | 1                                                                     | 1                                                                               |

| Dead-time effect                            | Yes                                                                              | No                                                                    | No                                                                    | No                                                                              |

| Leakage currents                            | Low                                                                              | High                                                                  | Low                                                                   | Low                                                                             |

| Power density                               | Low                                                                              | High                                                                  | Low                                                                   | High                                                                            |

| Conversion efficiency                       | Low                                                                              | Low                                                                   | Low                                                                   | High                                                                            |

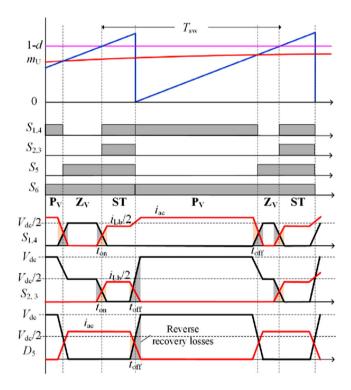

**FIGURE 8** Distribution diagram of the switching losses in positive cycle, where  $t_{\rm on}$  and  $t_{\rm off}$  are the turn-ON time and the turn-OFF time of power switches

turn-ON, turn-OFF and diode reverse-recovery energy, correspondingly, which are provided in the datasheet under certain test conditions (i.e. the test voltage  $V_{\rm CC}$  and current  $I_{\rm CC}$ ). Moreover,  $V_{\rm ceav}$  and  $I_{\rm cav}$  are the average voltage and current of the IGBT, respectively.

With the above, the switching losses can be calculated, and Figure 8 illustrates the switching losses of the proposed converter. As shown in Figure 8, there are turn-ON losses on  $S_{1-4}$  when the mode changes from  $\mathbf{Z}\mathbf{v}$  to  $\mathbf{S}\mathbf{T}$ . Then, from  $\mathbf{S}\mathbf{T}$  to  $\mathbf{P}\mathbf{v}$ , there are turn-OFF losses on  $S_{2,3}$ , and the diode reverse-recovery losses are generated on  $D_5$ . Finally, for  $\mathbf{P}\mathbf{v}$  to  $\mathbf{Z}\mathbf{v}$ , the turn-OFF losses will be generated on  $S_{1,4}$ . Compared to

the switching losses of the traditional two-stage inverter, the switching losses of the proposed converter are reduced by  $2E_{\rm onT}f_{\rm sw}V_{\rm dc}I_{\rm m}/\pi V_{\rm CC}I_{\rm CC}$ , as summarized in Table 1.

## 4.2 | Comparison with prior-art converters

The proposed converter can achieve AC and DC outputs simultaneously. A comparison with the prior-art hybrid converters is shown in Table 2. It can be summarized as follows.

- 1. Low component-count with shoot-through capability: When compared to the traditional two-stage inverter with the HERIC as the VSI (i.e. an example of the separated converters, as shown in Figure 6), the proposed converter has fewer power devices with less current stress and voltage stress to achieve multiple outputs, while maintaining the same DC gain. Additionally, the proposed converter has shoot-through protection, leading to lower EMI and higher reliability, and the power quality can then be improved to a certain extent (i.e. due to the elimination of the dead time). Notably, as presented in Table 2, the AC gain of the proposed converter is lower than that of the traditional two-stage inverter.

- Low leakage currents: Comparing the proposed converter with the BDHC in [10], the leakage currents can be suppressed to a low level (i.e. satisfying the grid standard [13]) with the symmetrical structure. It makes the proposed converter specifically suitable in PV applications.

- 3. High power density: The proposed converter has a higher power density than the transformerless hybrid converter in [15]. Both hybrid converters employ an L-type filter on the AC side. However, since a dual-buck inverter was adopted as the VSI [16], only one inductor is utilized, while the other is idle. That means the L-type filter of the hybrid converter in [15] should be two times in terms of value and volume as that for the proposed converter, resulting in low power density.

- 4. Reactive power injection and independent control: With the modulation scheme in Figure 3(a), the reactive power injection can be flexible injected. Furthermore, the DC gain and AC modulation signal can be controlled independently within the

**TABLE 3** System parameters

| Symbol                     | Values                                                                                                                 |

|----------------------------|------------------------------------------------------------------------------------------------------------------------|

| $V_{in}$                   | 0–200 V                                                                                                                |

| $V_{ m dc}$                | 0–360 V                                                                                                                |

| $v_{\rm ac}$               | 0–110 V                                                                                                                |

| $f_{ m g}$                 | 50 Hz                                                                                                                  |

| $L_{b1}, L_{b2}$           | 0.4 mH                                                                                                                 |

| $C_{ m DC}$                | $2800\mu\mathrm{F}$                                                                                                    |

| $L_{\rm ac1}, L_{\rm ac2}$ | 0.75 mH                                                                                                                |

| $f_{ m sw}$                | $20~\mathrm{kHz}$                                                                                                      |

| $C_{ m PVg}$               | 200 nF                                                                                                                 |

|                            | $V_{ m in}$ $V_{ m dc}$ $v_{ m ac}$ $f_{ m g}$ $L_{ m b1}, L_{ m b2}$ $C_{ m DC}$ $L_{ m ac1}, L_{ m ac2}$ $f_{ m sw}$ |

voltage and power limitations according to Equations (15) and (17). In all, the proposed converter can achieve flexible reactive power injection.

# 5 | SIMULATION AND EXPERIMENTAL RESULTS

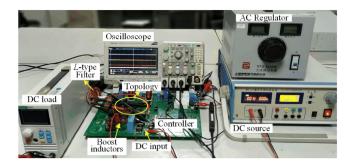

The proposed hybrid transformerless converter is validated through simulations and experimental tests. The power switches  $S_{1-6}$  are from Infineon (part no. IKW30N65NL), and the diode D is from ROHM (part no. RFUH20TF6SFHC9). All the system parameters are detailed in Table 3, where the passive components are designed for a rating of 5 kW, and the PV parasitic capacitance  $C_{\rm PVg}$  is chosen based on [34]. As mentioned, the DC input  $V_{\rm in}$  adopts a DC power supply to demonstrate the proposed converter.

#### 5.1 | Simulation

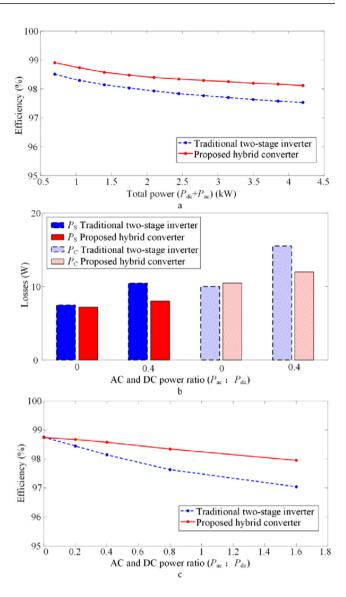

To verify the losses analysis and comparison between the traditional two-stage inverter with the HERIC as the VSI (i.e. as shown in Figure 6) and the proposed converter, simulations are carried out in Piecewise Linear Electrical Circuit Simulation software. The correspondingly thermal-loss models of the power devices are established based on the device datasheets (i.e. Infineon IGBT—IKW30N65NL and ROHM diode—RFUH20TF6SFHC9). The system parameters of the traditional two-stage inverter are the same as those in Table 3. Besides, the input and output voltages are  $V_{\rm in}=140$  V,  $V_{\rm dc}=160$  V and  $v_{\rm ac}=78$  V/ 50 Hz (RMS), and the DC load  $R_{\rm DC}$  is 25.6 in the simulation tests.

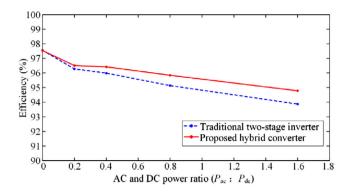

Figure 9 shows simulation results, where  $P_{\rm S}$  and  $P_{\rm C}$  represent the switching losses and the conduction losses of the power devices, respectively. The efficiency of two configurations under  $P_{\rm ac}: P_{\rm dc} = 0.4$  is compared in Figure 9(a), where only the losses of the power devices are considered. In addition, Figure 9(b) shows the switching losses and conduction losses of the IGBT (with an anti-parallel diode) for the two converters

**FIGURE 9** Power losses and efficiency comparison between the traditional two-stage inverter and the proposed converter. (a) Efficiency comparison at different power levels (i.e.  $P_{\rm ac}$ : $P_{\rm dc}=0.4$ ). (b) Power losses comparison of conduction losses and switching losses. (c) Efficiency comparison at different  $P_{\rm ac}$ : $P_{\rm dc}$  and  $P_{\rm T}=1.4~{\rm kW}$

with  $P_{\rm dc}=1.4$  kW and 1 kW, respectively, and the total power being 1.4 kW. Furthermore, when the AC and DC power ratio is varying, the efficiency is also compared, as demonstrated in Figure 9(c), where the total power is 1.4 kW and the limitation in Equation (17) is also considered. The results indicate that only the conduction losses of the traditional two-stage inverter are slightly less than that of the proposed converter under  $P_{\rm ac}$ :  $P_{\rm dc}=0$ . With  $P_{\rm ac}:P_{\rm dc}$  increasing, both the switching losses and the conduction losses of the traditional two-stage inverter become larger than those of the proposed converter. Therefore, the proposed converter can achieve a higher efficiency than the traditional two-stage inverter, which validates the discussion in Section 4.1, and it has fewer components with less current stress and voltage stress.

FIGURE 10 Prototype of the proposed hybrid transformerless converter system

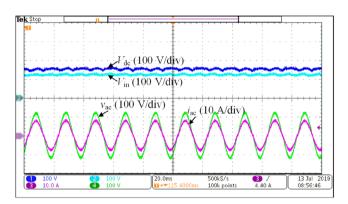

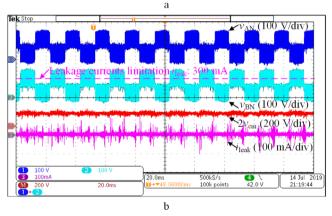

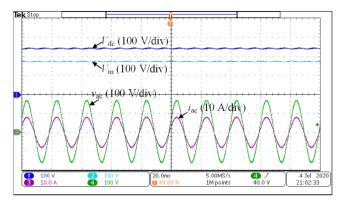

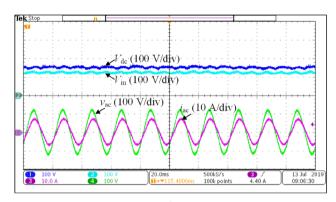

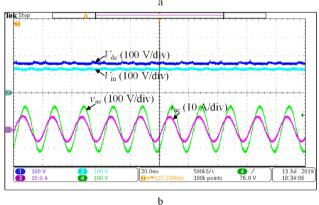

**FIGURE 11** Experimental results of the proposed hybrid transformerless converter under DC gain being 1.143 and maximum modulation signal being 0.7857 (time: 20 ms/div). (a) Input and output waveforms (i.e.  $V_{\rm in}$ ,  $V_{\rm dc}$ ,  $v_{\rm ac}$  and  $i_{\rm ac}$ ). (b) The CMV, inverter output terminal voltages  $v_{\rm AN}$  and  $v_{\rm BN}$ , and the leakage current  $i_{\rm cak}$

# 5.2 | Experiments results

Figure 10 shows the experimental setup of the proposed converter system, where control and modulation algorithms are implemented in a fixed-point digital signal processor from TI (TMS320F2812). The DC output is an ET5420 electronic load, and the AC output is connected to the AC grid, referring to Figure 2(b). The system parameters are the same as in Table 3.

Figures 11 and 12 show the steady-state performances of the proposed symmetrical transformerless hybrid converter with different DC and AC gains. The DC input voltage  $V_{\rm in}$ , the DC

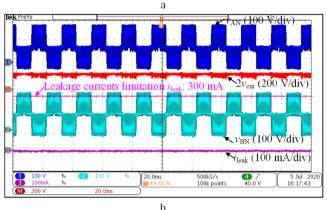

**FIGURE 12** Experimental results of the proposed hybrid transformerless converter under DC gain being 1.444 and maximum modulation signal being 0.867 (time: 20 ms/div). (a) Input and output waveforms (i.e.  $V_{\rm in}$ ,  $V_{\rm dc}$ ,  $v_{\rm ac}$  and  $i_{\rm ac}$ ). (b) The CMV, inverter output terminal voltages  $v_{\rm AN}$  and  $v_{\rm BN}$ , and the leakage current  $i_{\rm leak}$

output voltage  $V_{\rm dc}$ , the grid voltage  $v_{\rm ac}$  and the grid current  $i_{ac}$  are shown in Figures 11(a) and 12(a). The input and output voltages of Figure 11(a) are  $V_{\rm in} = 140$  V,  $V_{\rm dc} = 160$  V and  $v_{\rm ac} = 78 \text{ V}/50 \text{ Hz}$  (RMS), and the DC load  $R_{\rm DC}$  is 25.6  $\Omega$ . While those parameters in Figure 12(a) are  $V_{\rm in} = 180$  V,  $V_{\rm dc} = 260 \, \text{V}, v_{\rm ac} = 110 \, \text{V} / 50 \, \text{Hz}$  (RMS) and  $R_{\rm DC} = 140 \, \Omega$ . Due to the inherent pulsation power of the HERIC, there are certain ripples in the output voltage  $V_{\rm dc}$ . Nevertheless, the results in Figures 11(a) and 12(a) demonstrate the multi-output feature of the proposed converter. Additionally, Figures 11(b) and 12(b) show the CMV, the inverter output terminal voltages, and the leakage currents. Observations in Figures 11(b) and 12(b) indicate that the leakage current  $i_{leak}$  is well suppressed below the limit (300 mA). Moreover, both experimental results illustrate that  $v_{\rm dm}$  of the proposed converter at the AC output has the same performance as the single HERIC with the unipolar PWM (i.e. changing between  $+V_{dc} = -V_{dc}$  and 0) at the switching frequency). Therefore, with the proposed modulation method in Figure 3, the proposed converter can achieve good power quality, low losses and low leakage currents and multiple outputs.

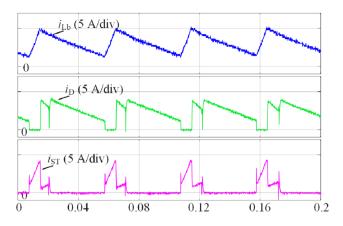

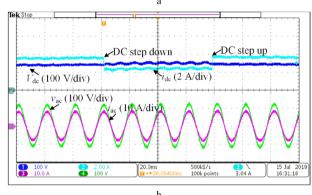

Moreover, the key current waveforms (i.e.  $i_{\rm Lb}$ ,  $i_{\rm D}$  and  $i_{\rm ST}$ ) during switching are shown in Figure 13. It should be noted that the experimental data of these variables are obtained through the oscilloscope and then replotted in MATLAB due to the lack of current probes. It can be observed in Figure 13 that the key

**FIGURE 13** Experimental results of key current waveforms during switching, i.e. the boost current  $i_{\text{Lb}}$ , the diode current  $i_{\text{D}}$  and the input current of the VSI  $i_{\text{ST}}$  (time: 40 ms/div)

**FIGURE 14** Experimental results of the proposed converter at non-unity power factors (time: 20 ms/div). (a)  $i_{ac}$  lagging  $v_{ac}$ ,  $\cos \varphi = +0.866$ . (b)  $i_{ac}$  leading  $v_{ac}$ ,  $\cos \varphi = -0.866$

waveforms agree well with the analysis in Figure 4(c). Notably, the spikes of the HERIC input current  $i_{ST}$  are normal, which are due to the nonidealities of power devices. It thus confirms the effectiveness of the modulation method for the proposed converter.

To further verify the reactive power injection capability, the experimental tests of the proposed converter have been performed under non-unity power factors (i.e. the power factor  $\cos\varphi = +0.866$  and -0.866). The experimental results are shown in Figure 14, in which Figure 14(a) corresponds to the case of  $i_{\rm ac}$

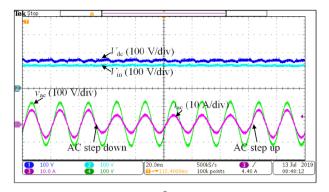

FIGURE 15 Experimental results of the proposed converter under load changes (time: 20 ms/div). (a) AC load change. (b) DC load change

lagging  $v_{\rm ac}$ ,  $\cos \varphi = +0.866$ , and Figure 14(b) presents the case of  $i_{\rm ac}$  leading  $v_{\rm ac}$ ,  $\cos \varphi = -0.866$ . As can be seen in Figure 14, the proposed converter can provide and absorb reactive power upon demands.

The proposed converter is then tested under load changes, and the experimental results are presented in Figure 15. Here, the grid current amplitude (RMS) was changed to 2.5 A and then back to 5 A, as the AC load changes. For the DC load changes, the current was changed to 2.4 A and then restored to 4.8 A. Observations in Figure 15 indicate that the proposed converter can operate stably under dynamic loading changes. That is as long as the proposed converter satisfied the limitation in Equations (15) and (17), the current quality of the inverter will not be affected by the loading changes due to the separated control in Figure 5.

Additionally, Figure 16 shows the experimental efficiency comparison between the traditional two-stage inverter (i.e. a boost converter and an HERIC) and the proposed converter, where different AC and DC power ratios  $P_{\rm ac}$ :  $P_{\rm dc}$  are considered with the total power being 1.4 kW. The conversion efficiencies are calculated by measuring the three input and output voltages and currents. In that case, the measured efficiencies in Figure 16 consider the losses of the power devices as well as the boost and AC filters. The result shown in Figure 16 agrees well with that in Figure 9(c), which indicates that the proposed converter can obtain a higher efficiency than the traditional two-stage inverter. It is valuable to mention that when the AC output power accounts for more, the efficiency benefit of the HERIC will become significant.

**FIGURE 16** Measured efficiency of the traditional two-stage inverter and the proposed converter under different  $P_{ac}$ : $P_{dc}$  and  $P_{T} = 1.4 \text{ kW}$

As a summary, the above simulation and experimental tests have validated the effectiveness of the proposed hybrid transformerless converter in terms of low leakage currents, simultaneous DC and AC outputs and flexible reactive power capability for grid-friendly hybrid PV systems. In addition, with the corresponding modulation scheme, the proposed converter can maintain good power quality and high efficiency. Therefore, the proposed converter can be a promising and cost-effective solution for future smart PV systems.

#### 6 | CONCLUSION

This paper has proposed a type of hybrid transformerless converters, which can achieve simultaneous DC and AC outputs, low leakage currents, and inherent shoot-through capability. The configuration principle for this type of converter has been presented, i.e. 1) a symmetrical boost inductor should be employed to ensure a constant CMV when operating as a boost converter and 2) a transformerless inverter should be adopted as the switch to maintain a constant CMV when acting as a VSI. This has been demonstrated on a converter with the HERIC as the VSI, and the corresponding modulation method, CMV analysis and losses comparison are detailed to illustrate the performance in reactive power injection, low leakage currents and high efficiency. Simulations and experimental results have then verified the effectiveness of the proposed converter in terms of multiple outputs, low leakage currents, flexible reactive power capability, high efficiency and high reliability. Notably, other transformerless topologies can be constructed based on the configuration methodology.

#### **ACKNOWLEDGEMENTS**

This work was supported by the Novo Nordisk Fonden through the Interdisciplinary Synergy Programme under Award NNF18OC0034952.

#### **ORCID**

Zhongting Tang https://orcid.org/0000-0003-2447-2320

Yongheng Yang https://orcid.org/0000-0002-1488-4762

#### REFERENCES

- Blaabjerg, F., et al.: Distributed power generation systems and protection. Proc. IEEE. 105(105), 1311–1331 (2017)

- Boroyevich, D., et al.: Future electronic power distribution systems a contemplative view. Proc. 12th Int. Conf. OPTIM Elect. Electron. Equip. 1369–1380 (May 2010)

- Braun, M., et al.: Is the distribution grid ready to accept large-scale photovoltaic deployment? State of the art, progress, and future prospects: Distribution grid and largescale PV deployment. Prog. Photovolt: Res. Appl. 20(20), 681–697 (2012)

- Lv, Z., et al.: Adjustable inertia implemented by bidirectional power converter in hybrid AC/DC microgrid. IET Gener. Transm. Distrib. 14(14), 3594–3603 (2020)

- Adda, R., et al.: Synchronous-reference-frame-based control of switched boost inverter for standalone DC nanogrid applications. IEEE Trans. Power Electron. 28(28), 1219–1233 (2013)

- Tseng, K.-C., Huang, C.-C.: High step-up high-efficiency interleaved converter with voltage multiplier module for renewable energy system. IEEE Trans. Ind. Electron. 61(61), 1311–1319 (2014)

- Blaabjerg, F., Ionel, D.M.: Renewable Energy Devices and Systems with Simulations in MATLAB® and ANSYS®. 1st ed. Boca Raton, FL:CRC Press. (2017)

- Schirone, L., et al.: Predictive dead time controller for GaN-based boost converters. IET Power Electron. 10(10), 421–428 (2017)

- Tang, T., et al.: Modulation for the AVC-HERIC inverter to compensate for deadtime and minimum pulsewidth limitation distortions. IEEE Trans. Power Electron. 35(35), 2571–2584 (2020)

- Ray, O., Mishra, S.: Boost-derived hybrid converter with simultaneous DC and AC outputs. IEEE Trans. Ind. Appl. 50(50), 1082–1093 (2014)

- Lee, S.S., Heng, Y.E.: Improved single-phase split-source inverter with hybrid quasi-sinusoidal and constant PWM. IEEE Trans. Ind. Electron. 64(64), 2024–2031 (2017)

- Lee, S.S., et al.: Single-phase simplified split-source inverter (S3I) for boost DC–AC power conversion. IEEE Trans. Ind. Appl. 10(66), 7643–7652 (2019)

- Automatic Disconnection Device Between A Generator and the Public Low-Voltage Grid. German Standard DIN VDE 0126, (2010)

- IEEE Standard for Interconnecting and Interoperability of Distributed Resources With Associated Electric Power Systems Interfaces, IEEE Standard 1547.2. (2018)

- Dey, S., et al.: Transformerless hybrid converter with AC and DC outputs and reduced leakage current. IEEE J. Emerg. Sel. Top. Power Electron. 7(7), 1329–1341 (2019)

- Yang, F., et al.: A family of dual-buck inverters with an extended low-voltage DC-input port for efficiency improvement based on dual-input pulsating voltagesource cells. IEEE Trans. Power Electron. 33(33), 3115

3128 (2018)

- Li, W., et al.: Topology review and derivation methodology of single-phase transformerless photovoltaic inverters for leakage current suppression. IEEE Trans. Power Electron. 7(62), 4537–4551 (2015)

- Wu, T., et al.: Combined unipolar and bipolar PWM for current distortion improvement during power compensation. IEEE Trans. Power Electron. 29(29), 1702–1709 (2014)

- Victor, S.B.M., et al.: Method of converting a direct current voltage from a source of direct current voltage, more specifically from a photovoltaic source of direct current voltage, into an alternating current voltage. U.S. Patent 7,411,802 B2, (2008)

- Xiao, H., et al.: Optimised full-bridge transformerless photovoltaic gridconnected inverter with low conduction loss and low leakage current. IET Power Electron. 7(7), 1008–1015 (2014)

- Yu, W., et al.: High-efficiency MOSFET inverter with H6-type configuration for photovoltaic nonisolated AC module applications. IEEE Trans. Power Electron. 26(26), 1253–1260 (2011)

- Islam, M., Mekhilef, S.: H6-type transformerless singlephase inverter for grid-tied photovoltaic system. IET Power Electron. 8(8), 636– 644 (2015)

- 23. Heribert, S., et al.: Inverter for transforming a DC voltage into an AC current or an AC voltage. Europe Patent 1,369,985 (A2), (2003)

- Zhou, L., et al.: A family of neutral-pointclamped circuits of single-phase PV inverters: Generalized principle and implementation. IEEE Trans. Power Electron. 32(32), 4307–4319 (2017)

- Freddy, T.K.S., et al.: Modulation technique for single-phase transformerless photovoltaic inverters with reactive power capability. IEEE Trans. Ind. Electron. 64(64), 6989–6999 (2017)

- Tang, Z., et al.: A symmetrical transformerless hybrid converter with leakage current suppression. Proc. IEEE Energy Convers. Congress Expo. 6680–6685 (Sep. 2019)

- Gubía, E., et al.: Ground currents in single-phase transformerless photovoltaic systems. Prog. Photovolt. Res. Appl. 15(15), 629–650 (2007)

- 28. Erickson, R.W., Maksimovic, D., Fundamentals of Power Electronics. 2nd ed. Norwell, MA: Kluwer. pp. 22–27 (2001)

- Ciobotaru, M., et al.: Control of single stage single-phase PV inverter. Proc. Eur. Conf. Power Electron. Appl. P.1–P.10. (Sep. 2005)

- Li, K., et al.: A transformerless single-phase symmetrical Z-source HERIC inverter with reduced leakage currents for PV systems. Proc. IEEE Appl. Power Electron. Conf. Expo. 356–361 (Mar. 2018)

- Maniktala, S.: Switching Power Supplies A–Z 2nd ed. Amsterdam, The Netherlands: Elsevier. pp. 72–74. (2012)

- Shadmand, M.B., et al.: Constrained decoupled power predictive controller for a single-phase grid-tied inverter. IET Renew. Power. Gener. 11(11), 659–668 (2017)

- Graovac, D.D., Purschel, M.: IGBT Power Losses Calculation Using the Data-Sheet Parameters. Neubiberg, Germany: Infineon. pp. 1–17. (2009)

- Araneo, R., et al.: EMC issues in high-power grid-connected photovoltaic plants. IEEE Trans. Electromagn. Compat. 51(51), 639–648 (2009)

**How to cite this article:** Tang Z, Yang Y, Wan J, Blaabjerg F. Hybrid transformerless PV converters with low leakage currents: Analysis and configuration. *IET Renewable Power Generation*. 2020;1–14. https://doi.org/10.1049/rpg2.12029