## **Aalborg Universitet**

### On Inherent Redundancy of MMC-Based STATCOMs in the Overmodulation Region

Cupertino, Allan Fagner; Pereira, Heverton Augusto; Seleme, Seleme Isaac; Teodorescu, Remus

Published in:

IEEE Transactions on Power Delivery

DOI (link to publication from Publisher): 10.1109/TPWRD.2019.2936784

Creative Commons License CC BY 4.0

Publication date: 2020

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Cupertino, A. F., Pereira, H. A., Seleme, S. I., & Teodorescu, R. (2020). On Inherent Redundancy of MMC-Based STATCOMs in the Overmodulation Region. *IEEE Transactions on Power Delivery*, *35*(3), 1169-1179. Article 8809215. https://doi.org/10.1109/TPWRD.2019.2936784

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

# On Inherent Redundancy of MMC based STATCOMs in the Overmodulation Region

Allan Fagner Cupertino, *Member, IEEE*, Heverton Augusto Pereira, *Member, IEEE*, Seleme Isaac Seleme Junior, Remus Teodorescu, *Fellow, IEEE*

Abstract-Modular multilevel converters (MMCs) are frequently featured to their modular structure, which results in fault-tolerant operation and easy redundancy realization. Nevertheless, in order to reach a given redundancy factor, more cells must be included in the converter, which directly affects the costs. This paper discusses the inherent redundancy of a modular multilevel converter (MMC) based static synchronous compensator (STATCOM) operating in the overmodulation region. Analytical expressions for the limits of the converter linear region were developed in order to define the minimum required dc-link voltage. Moreover, sensitivity analyses were implemented in order to show the effects of grid voltage variations, different output impedances, power factor and injected currents. The results indicated that the operation in overmodulation region has significant inherent redundancy. For a MMC based STATCOM with 26 cells, the converter can ride through 4 failures per arm without significantly increasing the output THD or reducing the injected current into the grid.

Index Terms—Modular Multilevel Converter; Redundancy; Fault tolerance; Overmodulation.

#### I. Introduction

THE modular multilevel converter (MMC) has been strongly studied in recent years. This topology is based on the concept of cascaded connection of low voltage converters (frequently referred as cells) in order to obtain medium or high voltage converters [1]. MMC has proved to be a suitable solution for high voltage direct current (HVDC) systems and static synchronous compensators (STATCOMs) [2], [3].

Once the MMC can be composed of hundreds or thousands of components, some redundancy must be inserted in the converter structure [4]. Under such conditions, if one failure occurs, the faulty cell can be replaced by a redundant cell and the converter remains operating [5], [6]. A redundancy factor is generally considered at the converter design stage.

This study was supported by the Coordenação de Aperfeiçoamento de Pessoal de Nível Superior - Brasil (CAPES) - Finance Code 001, by CNPq and by FAPEMIG.

- A. F. Cupertino and S. I. Seleme Junior are with the Graduate Program in Electrical Engineering, Federal University of Minas Gerais, Belo Horizonte, MG, 31270-901 Brazil. A. F. Cupertino is also with the Department of Materials Engineering, Federal Center for Technological Education of Minas Gerais, Belo Horizonte, MG, 30421-169 Brazil (e-mails: afcupertino@ieee.org; seleme@cpdee.ufmg.br).

- H. A. Pereira are with the Department of Electrical Engineering, Universidade Federal de Viçosa, Viçosa, MG, 36570-900 Brazil (e-mail: heverton.pereira@ufv.br).

- R. Teodorescu is with the Department of Energy Technology, Aalborg University 9220 Aalborg, Denmark (e-mail: ret@et.aau.dk).

Manuscript received December XX, XX; revised December XX, XX.

This redundancy factor defines how many redundant cells are included per arm [7].

The redundancy strategies have been strongly discussed in the literature. Reference [8] proposes the classification in hot and cold redundancy schemes. References [4] and [9] showed results increasing the voltage of the healthy cells after failure events. Nevertheless, the redundancy factor of this strategy is strongly dependent on the voltage margins adopted in the design, as discussed in [7]. Reference [7] presented a comparison of different redundancy strategies in terms of dynamic behavior and power losses. Finally, references [10] and [11] presented a reliability analysis of the MMC converter in order to predict the maintenance interval and the required redundancy factor for a given application.

Nevertheless, there is gap in the technical literature when the number of failures in a given arm exceeds the number of redundant cells. Under such conditions, the required voltage can be higher than the available sum of the capacitor voltages. Strategies which guarantee the operation after all redundancy cells were employed are refereed in this paper as *inherent* redundancy strategies.

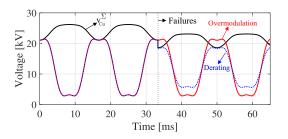

In order to exemplify the problem, Fig. 1 illustrates the reference voltages synthesized by one converter arm and the available sum of capacitor voltages for a MMC STATCOM operating at rated inductive reactive power. At the time 33 ms, some failures occur. Under such conditions, two approaches can be implemented. The first one is the reduction of the reactive power reference in order to reduce the reference voltage, as indicated in the dashed line. Thus, the converter will continue to operate in the linear region. Nevertheless, in the context of a STATCOM application, this derating will limit the voltage regulation capability of the device, which might be detrimental to the transmission system operator (TSO).

Other solution (frequently avoided in the literature) is operating the MMC in the overmodulation region. When this approach is considered, first of all, the extra voltage capability implies in an inherent redundancy factor that can be explored if a high number of failures occur. Secondly, the design of the converter can be implemented with the minimum number of cells. During transients or variation in grid voltage or impedance, the operation in the overmodulation region is considered. This results in cost effective design of the converter. Moreover, in the start of the overmodulation region, the increase in the harmonic distortion might not be an issue if the MMC is already modulated by the nearest-level control or other stair-case modulation scheme.

Reference [12] proposes a space vector modulator for a

Fig. 1. Inherent redundancy strategies for a MMC based STATCOM.

MMC HVDC system in the overmodulation region during voltage transients. Reference [13] discusses the operation in the overmodulation region during the failures for a MMC HVDC system with carrier based modulation. These approaches are limited by the modulator complexity for a high number of cells. Furthermore, these references do not discuss the boundaries between linear and nonlinear regions. Actually, the potential of overmodulation as a fault tolerant solution for MMC has not been discussed in the technical literature.

Therefore, an analysis of the inherent redundancy of modular multilevel converters in the overmodulation region is needed in the technical literature. The present work aims to fill this void, by providing the following contributions:

- Analytical expression of the linear region boundary for a double star chopper cell MMC;

- Sensitivity analysis of the limits with respect to the cell capacitance, grid impedance, grid voltage power factor and injected current;

- Discussion on the potential for fault tolerance in the overmodulation region.

All the analyses are evaluated based on a 17 MVA MMC STATCOM case study. The paper is outlined as follows. Section II presents the MMC characteristics. Section III discusses the control strategy. Section IV derives the linear region limits for MMC and presents some sensitivity analysis, while section V discuss the overmodulation as a fault tolerant solution. The results are shown in Section VI. Finally, the conclusions are stated in Section VII.

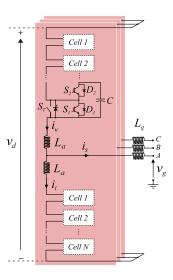

#### II. MMC BASED STATCOM

The MMC STATCOM topology is presented in Fig. 2. The connection between the arms of the same phase are performed through the arm inductors. When industrial IGBT modules are employed, a thyristor and a contactor are used to bypass the faulty cells. The MMC contains N cells per arm. The output and circulating currents can be computed according to the arm currents, as follows [14]:

$$i_s = i_u - i_l, \tag{1}$$

$$i_z = \frac{i_u + i_l}{2}. (2$$

The inserted voltages in upper and lower arms can be approximated by [15]:

Fig. 2. Schematic of the MMC based STATCOM.

$$v_u = v_z^* - v_s^*, \tag{3}$$

$$v_l = v_z^* + v_s^*. (4)$$

where  $v_s^*$  is the output voltage reference (which drives  $i_s$ ) and  $v_z^*$  is the internal voltage (which drives  $i_z$ ). The inserted voltages must be normalized in order to result in the insertion indexes of the converter. As mentioned in [14], the normalization strategy affects significantly the stability of the closed loop system. The normalization performed in reference [15] consists of the division of the reference signals by the measured sum of the capacitor voltages, once the sum of the capacitor voltages is the available voltage. Nevertheless, this strategy results in instabilities, and additional control loops must be employed [15], [16].

When the voltages are normalized by the effective dc-link voltage  $v_d$ , errors are observed between the reference and synthesized voltages. Generally, these errors can be compensated by the current loops, however it will affect the definition of the overmodulation limits, since the reference voltage and the voltage at the converter output will not be the same. Therefore, this work uses the approach proposed in [17], where the reference voltages are normalized by the estimation of the sum of capacitor voltages, here denoted by  $\tilde{v}_{Cu}^{\Sigma}$  and  $\tilde{v}_{Cl}^{\Sigma}$ . Accordingly:

$$n_u = \frac{v_z^* - v_s^*}{\tilde{v}_{Cu}^\Sigma}.$$

(5)

$$n_l = \frac{v_z^* + v_s^*}{\tilde{v}_{Cl}^2}. (6)$$

By neglecting the harmonics in the circulating current,  $v_z \approx v_d/2$  and the insertion indexes in steady-state can be approximated by:

$$n_u \approx \frac{\frac{v_d}{2} - v_s^*}{\tilde{v}_{Cu}^{\Sigma}},\tag{7}$$

Fig. 3. Steady-state reference waveforms for the symmetrical and unsymmetrical operation of MMC STATCOM.

$$n_l \approx \frac{\frac{v_d}{2} - v_s^*}{\tilde{v}_{Cl}^{\Sigma}}.$$

(8)

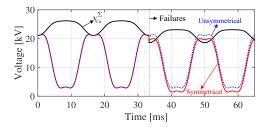

In the linear region of the modulator, it is expected that  $0 \le n_u \le 1$  and  $0 \le n_l \le 1$ . This means that the inserted voltages are lower than the sum of capacitor voltages for all operating conditions. Supposing now that some failures occur in one of the MMC arms, the faulty arm will operate in the overmodulation region. Under such conditions, two strategies can be considered:

- Unsymmetrical operation: Only the faulty cells are bypassed;

- Symmetrical operation: Cells in all arms are bypassed in order to maintain an equal number of cells per arm.

The theoretical waveforms after the failure for each strategy are illustrated in Fig. 3. For the unsymmetrical operation, the dc-link voltage value is maintained. Under such conditions, the faulty arm must handle the dc-link voltage and synthesize the same output voltage. For the symmetrical operation, the dc-link voltage is reduced proportionally to the number of failures, since the arms always operate with the same number of cells. Therefore, the converter operates less in the overmodulation region, which benefits the control. For this reason, the symmetrical operation is approached in this paper.

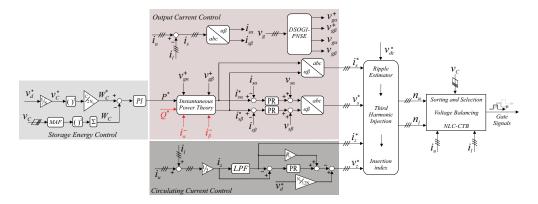

#### III. CONTROL STRATEGY

The control strategy of a MMC STATCOM is presented in Fig. 4. This implementation is based on the storage energy controller, output current control, circulating current control and capacitor voltage balancing. The energy storage controller computes the active power reference  $P^*$ , as follows:

$$P^* = \left(k_{pw} + \frac{k_{iw}}{s}\right) \left(\underbrace{\frac{1}{2}CN_o\left(\frac{v_d}{N}\right)^2}_{W_C^*} - \underbrace{\frac{1}{2}C\sum_{i=1}^{N_o}v_{C,i}^2}_{W_C}\right), (9)$$

where  $k_{pw}$  and  $k_{iw}$  are the proportional and integral gains of the energy controller.  $W_C$  is the total energy storage in the converter while  $W_C^*$  is the desired energy storage.  $\bar{v}_{C,i}$  is the i-th cell voltage of the MMC.  $N_o = 6(N-F)$ , where F is the number of failures in the arm with the lowest voltage capability. The storage energy control indirectly reduces the

dc-link voltage during failures and limits the operation to the most affected arm.

The reactive power and negative sequence current references  $(Q^*, i_{s\alpha}^- \text{ and } i_{s\beta}^-)$  depend on the type of service performed by the STATCOM (reactive power compensation, voltage regulation, etc). Based on these references, the current references can be computed through instantaneous power theory as follows [7]:

$$\begin{bmatrix} i_{s\alpha}^* \\ i_{s\beta}^* \end{bmatrix} = \frac{1}{(v_{g\alpha}^+)^2 + (v_{g\beta}^+)^2} \begin{bmatrix} v_{g\alpha}^+ & v_{g\beta}^+ \\ v_{g\beta}^+ & -v_{g\alpha}^+ \end{bmatrix} \begin{bmatrix} P^* \\ Q^* \end{bmatrix} + \begin{bmatrix} i_{s\alpha}^- \\ i_{s\beta}^- \end{bmatrix}, \tag{10}$$

where  $v_{g\alpha}^+$  and  $v_{g\beta}^+$  are the positive sequence components of grid voltage in stationary reference frame. These components are obtained through a positive and negative sequence extractor based on the double second-order generalized integrator (DSOGI-PNSE), proposed by [18]. Since the current references are sinusoidal waves, the output current is control is implemented in stationary through resonant controllers [7].

The circulating current control is responsible for insert damping in the converter internal dynamics and suppress the second harmonic, which is typical of the circulating current [19]. A proportional resonant controller tuned to the second harmonic is employed per phase.

As previously mentioned, the modulation signals are then normalized by the sum of the capacitor voltages estimation, which can be obtained by [17]:

$$\tilde{v}_{Cu}^{\Sigma} = \sqrt{\left(\frac{N-F}{N}\right)^2 v_d^2 + \frac{N-F}{C} \left(\widetilde{\Delta W}_{\Sigma} + \widetilde{\Delta W}_{\Delta}\right)} \quad (11)$$

$$\tilde{v}_{Cl}^{\Sigma} = \sqrt{\left(\frac{N-F}{N}\right)^2 v_d^2 + \frac{N-F}{C} \left(\widetilde{\Delta W}_{\Sigma} - \widetilde{\Delta W}_{\Delta}\right)} \quad (12)$$

where:

$$\widetilde{\Delta W}_{\Sigma} = 2 \int BPF \left[ v_z^* i_z^* - v_s^* i_s^*; 2\omega_n \right] dt \qquad (13)$$

$$\widetilde{\Delta W}_{\Delta} = \int BPF \left[ v_z^* i_s^* - 2v_s^* i_z^*; \omega_n \right] dt$$

(14)

where  $\omega_n$  is the line frequency.  $BPF[...;\omega_n]$  denotes a band pass filtering tuned in the frequency  $\omega_n$ .

The normalized signals are computed and used by the modulator. Firstly, 1/6 of the third harmonic is injected in the reference voltages to extend the modulator linear region. This work uses the nearest level control (NLC) modulation strategy. The cells of each arm are balanced through the cell tolerance band algorithm (CTB), described in [20]. Basically, the capacitor voltages are sorted in a list in terms of capacitor voltages. When the current is positive, the cells with lower voltage are inserted and when the current is negative the cells with higher voltage are inserted. When some of the voltages reaches the limit of the tolerance band, an exchange is performed and the list is updated. This means that the switching events happen only when is necessary. Therefore, the switching frequency is strongly reduced although it is not

constant [20]. Therefore, NLC-CTB results in a considerable reduction in the MMC power semiconductor losses.

The same control strategy is employed during overmodulation. When a fault happens, the insertion indexes are saturated, which generates an error in the synthesized output and internal voltages. Consequently, this saturation will increase the error in the output and circulating currents. Under such conditions, the current feedback will work to correct this error, increasing the reference voltage dynamically.

The parameters of the MMC STATCOM studied in this paper are presented in Tab. I.

TABLE I

PARAMETERS OF THE MMC STATCOM STUDIED IN THIS WORK.

| Parameter                         | Value                                    |

|-----------------------------------|------------------------------------------|

| Line to line grid voltage $(V_q)$ | 13.8 kV                                  |

| Line frequency $(f_n)$            | 60 Hz                                    |

| Effective dc voltage $(v_d)$      | 25 kV                                    |

| Rated power $(S_n)$               | 17 MVA                                   |

| Transformer X/R ratio             | 18                                       |

| Arm inductances $(L_a)$           | $3 \text{ mH } (\approx 0.1 \text{ pu})$ |

| Arm inductor X/R ratio            | 17                                       |

| Cell capacitance $(C)$            | 6.8 mF                                   |

| Nominal cell voltages $(v_C^*)$   | 962 V                                    |

| Number of cells per arm $N$       | 26                                       |

| Sampling Frequency $f_s$          | 10.92 kHz                                |

# IV. BOUNDARY BETWEEN LINEAR AND NON-LINEAR REGION FOR MMC

The linear region boundary for traditional 2-level converters modulated with carrier based methods is usually defined in terms of the modulation index. The modulation index can be defined as [21]:

$$m = \frac{2\hat{V_s}}{v_d} \tag{15}$$

where  $\hat{V_s}$  is the fundamental component magnitude of line to neutral inverter voltage. The modulation index at the boundary between linear and non-linear region is denoted as  $m_{max}$ . The boundary is usually interpreted as the value of output voltage which leads to equal amplitudes in the reference and carrier signals. For example, if sinusoidal modulation is employed,  $m_{max}=1$  while  $m_{max}\approx 1.15$  when 1/6 of third harmonic injection is considered in the reference voltage.

When compared with traditional 2-level converters, staircase modulated MMC (e.g. NLC-CTB) has specific characteristics which affects considerably the boundary between linear and nonlinear region. In such conditions, the nonlinear (overmodulation) region starts when the insertion indexes (7) and (8) are greater than 1, i.e. the inserted voltages are higher than the sum of capacitor voltages.

The output voltage depends directly of the sum of capacitor voltages in each arm, which is the available voltage. The sum of capacitor voltages presents a non-negligible ripple (typically in the range between 5 and 15 % at rated conditions) and

the ripple waveform is strongly dependent of the operation conditions. Therefore, the computation of the modulation index in the boundary of linear region is not straightforward.

The limits of the linear region are important to guarantee a proper and cost effective converter design. This section aims to study analytically this phenomenon.

#### A. Maximum Output Voltage

Due to symmetry, only the lower arm is analyzed. It is assumed that the error in the sum of capacitor voltages estimation is negligible. Therefore, the insertion index is given by:

$$n_l = \frac{v_z^* + v_s^*}{v_{cl}^{\Sigma}}. (16)$$

The converter output voltage (per phase) and output current are given by:

$$v_s = \widehat{V}_s \cos(\omega_n t), \tag{17}$$

$$i_s = \widehat{V}_s \cos(\omega_n t - \phi). \tag{18}$$

By neglecting the harmonics in circulating current and considering the control strategy discussed in the last section, the following equation can be derived for the insertion indexes:

$$n_l = \frac{\frac{N-F}{N} \frac{v_d}{2} + \widehat{V}_s \cos(\omega_n t) - \frac{1}{6} \widehat{V}_s \cos(3\omega_n t)}{v_d \left(\frac{N-F}{N}\right) + \Delta v_{cl}^{\Sigma}}.$$

(19)

Using a similar development of [17], the sum of capacitor voltage ripples in the lower arm can be estimated by:

$$\Delta v_{cl}^{\Sigma} = \frac{N}{2Cv_{A}} \left( \Delta W_{\Sigma} - \Delta W_{\Delta} \right), \tag{20}$$

where:

$$\Delta W_{\Sigma} = -\frac{\widehat{V}_{s}\widehat{I}_{s}}{4\omega_{n}}\sin\left(2\omega_{n}t - \phi\right) + \frac{\widehat{V}_{s}\widehat{I}_{s}}{24\omega_{n}}\sin\left(2\omega_{n}t + \phi\right) + \frac{\widehat{V}_{s}\widehat{I}_{s}}{48\omega_{n}}\sin\left(4\omega_{n}t - \phi\right),$$

(21)

$$\Delta W_{\Delta} = \frac{N - F}{N} \frac{v_d \hat{I}_s}{\omega_n} \sin(\omega_n t - \phi) - \frac{\hat{V}_s i_z}{\omega_n} \sin(\omega_n t) + \frac{\hat{V}_s i_z}{9\omega_n} \sin(3\omega_n t).$$

(22)

Assuming a sufficiently high switching frequency, the circulating current  $i_z$  in relation (22) can be replaced by its dc value, which can be approximated by:

$$i_z \approx \frac{N}{N-F} \frac{\widehat{V}_s \widehat{I}_s}{2v_s} \cos(\phi).$$

(23)

In the limit of the modulator linear region,  $0 \le n_l \le 1$ . The first part of this inequality results in (see Appendix A for more details):

Fig. 4. Control strategy of a MMC based STATCOM

$$0 < \frac{v_d}{2} + v_s^* \Leftrightarrow \widehat{V}_{s0} \le \frac{N - F}{N} \frac{v_d}{\sqrt{3}}.$$

(24)

If F=0, relation (24) leads to the same result obtained for 2-level converters [22]. Nevertheless, when the second inequality is taken into account, the shape of the capacitor voltage imposes a limit for the maximum output voltage. The maximum insertion index  $(n_l=1)$  is obtained when  $v_s^*$  reaches the maximum value, which means  $\omega_n t = \pi/6$ . By replacing  $\omega_n t = \pi/6$  and (20) in (19), the maximum output voltage can be computed by (see Appendix B for more details):

$$\hat{V}_{s1} = max \left( \frac{-b + \sqrt{b^2 - 4ac}}{2a}; \frac{-b - \sqrt{b^2 - 4ac}}{2a} \right), \quad (25)$$

where

$$a = \frac{2N^2 \hat{I}_s}{9(N-F)\omega_n C v_d^2} \cos(\phi), \tag{26}$$

$$b = \frac{N\widehat{I}_s}{4\omega_n C} \left[ -\frac{1}{2v_d} \sin\left(\frac{\pi}{3} - \phi\right) + \frac{1}{12v_d} \sin\left(\frac{\pi}{3} + \phi\right) + \frac{1}{24v_d} \sin\left(\frac{2\pi}{3} - \phi\right) \right] - \frac{\sqrt{3}}{2}, \tag{27}$$

$$c = \frac{N - F}{N} \frac{v_d}{2} - \frac{(N - F)\widehat{I}_s}{4\omega_n C} \sin\left(\frac{\pi}{6} - \phi\right). \tag{28}$$

Finally, the maximum output voltage can be computed by:

$$\widehat{V}_{s,max} = min(V_{s0}; V_{s1}). \tag{29}$$

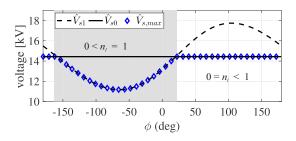

Figure 5 shows the behavior of the MMC maximum output voltage as function of the current angle. The parameters of Table I were employed and operation at rated current is assumed. As observed, the maximum output voltage depends on the operating power factor. For the inductive power factor, the output voltage is limited by the sum of capacitor voltages. For the capacitive power factors, the output voltage presents the same value obtained for 2 level converters.

Fig. 5. Minimum required output voltage as function of the operating power factor.

#### B. Minimum dc-link voltage

The minimum output voltage required for grid connected applications when the converter inject rated current (1 pu) can be computed by:

$$\hat{V}_s = \hat{V}_g \sqrt{[(1 + \Delta V_g) + x_{eq} \sin(\phi)]^2 + [x_{eq} \cos(\phi)]^2},$$

(30)

where  $\Delta V_g$  refers to the perceptual variations in the grid voltage.  $\hat{V}_g$  is the peak of grid voltage (per phase).  $x_{eq}$  refers to the per unit output reactance of the converter, given by:

$$x_{eq} = \left(\frac{x_a}{2} + x_g\right),\tag{31}$$

where  $x_a$  and  $x_g$  are the arm and the output reactance in per unit values, respectively.

In the region where  $n_l$  is limited by the zero voltage, the MMC behavior is similar to that of 2 level converters, and the minimum dc-link is given by:

$$v_{d0} = \sqrt{3}\widehat{V}_s. \tag{32}$$

Nevertheless, in the region where  $n_l$  is limited by the sum of capacitor voltages ripple the relation is more complicated. By replacing (30) in (19) and considering  $v_d$  as an independent variable, a 3rd order polynomial equation is obtained, as follows (see Appendix B for more details):

$$dv_{d1}^3 + ev_{d1}^2 + fv_{d1} + g = 0. (33)$$

where d, e, f and g are shown below:

Fig. 6. Minimum required dc-link voltage as function of the operating power factor.

$$d = -\frac{N - F}{2N},\tag{34}$$

$$e = \frac{(N-F)\widehat{I}_s}{4\omega_n C} \sin\left(\frac{\pi}{6} - \phi\right) + \widehat{V}_s \frac{\sqrt{3}}{2},\tag{35}$$

$$f = -\frac{N\widehat{V}_s\widehat{I}_s}{4\omega_n C} \left[ -\frac{1}{2}\sin\left(\frac{\pi}{3} - \phi\right) + \frac{1}{12}\sin\left(\frac{\pi}{3} + \phi\right) + \frac{1}{24}\sin\left(\frac{2\pi}{3} - \phi\right) \right],$$

(36)

$$g = -\frac{2N\hat{V}_s^2\hat{I}_s}{9\omega_n C} \frac{N}{N - F}\cos(\phi). \tag{37}$$

The highest real positive root of (33) is the minimum required dc-link voltage  $v_{d1}$  at the linear operation range. Therefore, the minimum dc-link voltage for operation in the linear region is given by:

$$v_{d,min} = min(v_{d0}; v_{d1}).$$

(38)

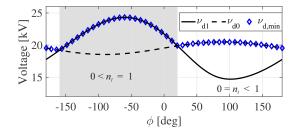

Figure 6 presents the minimum dc-link voltage required for each operating power factor at rated current, based on the parameters of Table I. As observed, in the capacitive region, the modulator gain is described by the same equations that describes 2 level converters, and the required dc-link voltage depends on the output impedance characteristics and grid voltage. On the other hand, in the inductive operation, the required dc-link is limited by the voltage ripple.

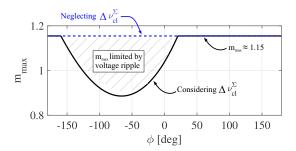

The modulation index at the boundary of linear region can be computed using (30) and (38). Accordingly:

$$m_{max} = \frac{2\hat{V}_s}{v_{d min}}. (39)$$

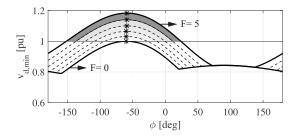

Figure 7 shows the modulation index as function of the current angle, based on the parameters of Tab. I. Operation at rated current is assumed. As observed, for the capacitive operation the voltage ripple does not limit the converter operation and  $m_{max} \approx 1.15$  is obtained (the same for 2-level converters). However, for inductive operation, the voltage ripple significantly affects the converter operation. For the considered parameters, the minimum obtained value is  $m_{max} \approx 0.9$ , which is a significant loss in the voltage synthesis capability.

Fig. 7. Modulation index at the modulator linear region boundary.

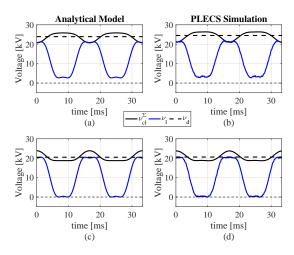

The developed analytical model is validated through simulations of a MMC based STATCOM implemented in PLECS environment. The parameters shown in Tab.I are considered. Five operation conditions are considered, as presented in Tab. II. The dc-link voltage was slowly reduced in the simulation until reach the limit of linear region. As observed, the maximum error obtained in the dc-link voltage estimation was lower than 3.4 %. In the inductive region, the accuracy of the model is affected by both estimations of reference signal and capacitor voltage ripple. In capacitive region, the accuracy is more affected by reference signal estimation, since the overmodulation is observed in the lower limit (zero voltage). Therefore, the errors obtained in inductive operation are higher.

Figure 8 presents the waveforms for inserted voltages and sum of capacitor voltages, considering the minimum dc-link provided by equation (38), for inductive (a) and capacitive (c) operation. Figures 8 (b) and (d) present the inserted voltages and sum of capacitor voltages, obtained by the simulation model, for inductive and capacitive (c) operation, respectively. For the inductive operation, it is observed that the inserted voltage is limited by the sum of capacitor voltages, while for the capacitive operation, the inserted voltage is limited by the zero voltage. Moreover, the analytical and simulation results are very similar. The small differences observed are due to the contribution of  $v_z^*$ .

It must be pointed out that the analytical model presented in this section did not consider the amount of voltage necessary to cancel out the second harmonic in circulating currents. This voltage can contribute with up to 5 % in the maximum voltage for reasonable cell capacitance values, according to the reference [23]. Furthermore, the minimum pulse and dead-time effects were not included. Therefore, the required dc-link voltage will be higher (e.g., 5 %) than the values computed by relation (38).

#### C. Sensitivity Analysis

This section analyzes the effect of parameter variation in the minimum required dc-link voltage, which is an important step for a cost-effective design. For a MMC-STATCOM, the variations in grid voltage and in the output impedance are common phenomena, since a power system is a very complex structure with time varying parameters and configurations. The effects of the cell capacitance and current amplitude are also analyzed in this section.

TABLE II

MINIMUM DC-LINK VOLTAGE FOR OPERATION IN LINEAR REGION OF THE MODULATOR.

| <b>Operation Condition</b>             | Analytical | Simulation | Relative error |

|----------------------------------------|------------|------------|----------------|

| $\widehat{I_s} = 1pu; \phi = \pi/2$    | 20.5 kV    | 20.6 kV    | -0.5 %         |

| $\widehat{I}_s = 1pu; \phi = -\pi/2$   | 23.7 kV    | 24.5 kV    | -3.4 %         |

| $\widehat{I}_s = 0.5 pu; \phi = \pi/2$ | 20 kV      | 20.1 kV    | -0.5 %         |

| $\widehat{I}_s = 0.5pu; \phi = -\pi/2$ | 21.7 kV    | 22 kV      | -1.4 %         |

| $\widehat{I}_s = 0pu$                  | 19.5 kV    | 19.7 kV    | -1 %           |

Fig. 8. Inserted voltage and sum of capacitor voltages for a MMC STATCOM in the limit of the modulator linear region: (a) Analytical result for  $\phi = -\pi/2$ ; (b) Simulation result for  $\phi = -\pi/2$ ; (c) Analytical result for  $\phi = \pi/2$ ; (d) Simulation result for  $\phi = \pi/2$ ;

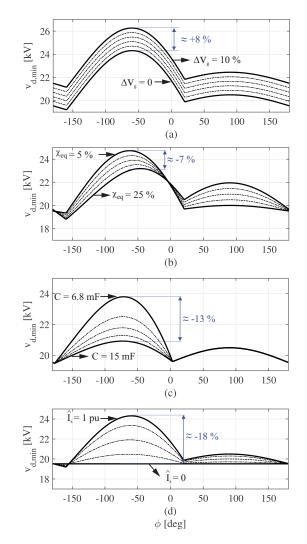

The effect of grid voltage variation is presented in Fig. 9 (a). Variations in the grid voltage up to 10 % were assumed. As observed, the minimum dc-link voltage increases for all operating power factors. A maximum variation of 8 % is observed. The variation in grid voltage affects the required voltage for both inductive and capacitive conditions. Therefore, the inductive region requires the maximum voltage and can be adopted in the converter design.

The effect of the equivalent output impedance is presented in Fig. 9 (b). These variations can be related to the higher arm inductance or variations in the grid impedance. Variations ranging from 5 % to 25 % were considered. As observed, for the capacitive operation, the higher the impedance, the higher the required voltage. Nevertheless, an opposite behavior is observed in the inductive operation. This factor can be justified by relation (30). Basically, due to the arm inductance, when the power factor changes, the inductance voltage drop can be displaced by 0 or 180 degrees from the grid voltage. Interestingly, the inductive region remains as the critical in terms of the required dc-link voltage for all adopted parameters range.

The effect of the cell capacitance is illustrated in Fig. 9 (c). As observed, when the capacitance increases, the required dc-link voltage decreases. This fact is justified by the voltage ripple, which reduces when the capacitance increases. In fact, if an infinite capacitance value is considered, the required

Fig. 9. Minimum required output voltage as function of the operating power factor.

voltage is equal to  $v_{d0}$ . The capacitive region is not affected, since the dc-link requirement for this region does not depend on the voltage ripple.

Finally, the effect of the output current amplitude is presented in Fig. 9 (d). As observed, when the current is reduced, the required dc-link decreases. This is related with the magnitudes of the voltage ripple and required output voltage, which are strongly dependent of the output current.

At this point, the following conclusions can be stated:

- The non-negligible ripple in the capacitor voltages reduces the linear region of the converter in some operation conditions (mainly in the inductive region);

- For 2-level converters the boundary between linear and non-linear region is usually defined in terms of modulation index. In case of MMC, the modulation index can be interpreted as the minimum sum of capacitor voltages for given grid voltage conditions. Therefore, the value of the dc voltage indicated in Fig. 6 is an alternative interpretation of the boundary between linear and nonlinear region;

- The definition of the boundary in terms of minimum

Fig. 10. Effect of failures in the minimum required dc-link voltage.

sum of capacitor voltages is interesting from the design point of view. Design the converter in the boundary conditions will result in the minimum number of cells. The sensitivity of the boundary with respect to the converter and grid parameters was evaluated in order to indicate what are the acceptable converter design margins.

Since the MMC based STATCOM must be able to operate at rated power for both inductive and capacitive conditions, the dc-link voltage is defined by the inductive operation. For the adopted parameters,  $v_d \approx 23.7~\rm kV$  at rated inductive reactive power. In order to deal with the variation of the grid voltage and circulating current control, 5 % of voltage margin is included. Therefore, the rated dc-link voltage is  $v_d \approx 25~\rm kV$ . Under such conditions, for N = 26, the voltage per cell is  $v_C^* \approx 962~\rm V$  and 1.7 kV power switches can be employed.

#### V. EFFECT OF FAILURES

Normally, some redundant cells are included in the converter structure in order to increase the MMC fault tolerance [5], [6]. However, redundant cells mean an increase in the converter cost. Therefore, this paper propose to use the operation in the overmodulation region as a fault tolerance strategy. Thereby, when some cells fail, the sum of capacitor voltages in the converter arm reduces and overmodulation is expected.

Figure 10 presents the per unit minimum required dc-link voltage as function of the number of failures. Here, the parameters of Tab. I and rated current are considered. The base value is the required dc-link voltage when the converter is in normal operation, i.e., F = 0. As observed, when failures occur, the minimum required dc-link increases, because a lower number of cells are available. Therefore, the voltage of each cell must be increased to guarantee the operation in the linear region.

Nevertheless, a cost effective MMC design will not consider large margins to increase the capacitor voltages. Therefore, when failures occur, the converter will overmodulate. The hatched areas indicate the power factors where the converter operates in the overmodulation. Considering the operation as STATCOM, this phenomenon occurs only for inductive operation.

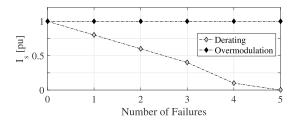

Figure 11 compares the per unit current injected in the grid when the overmodulation and the derating strategy mentioned in Section I are employed. After 3 failures, the converter controlled in derating mode is not able to inject 50 % of the initial power. This reduction will limit the capacity of the STATCOM to provide services to the utility. On the other hand,

Fig. 11. Comparison of the injected current for derating and overmodulation strategies.

Fig. 12. Effect of the failures in the MMC operation: (a) Instantaneous active and reactive power; (b) Circulating currents.

theoretically, the operation in the overmodulation region can ride through faults without resulting in lost of power capability.

#### VI. RESULTS

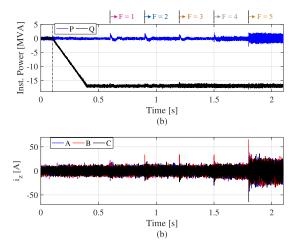

In order to show the operation of a MMC STATCOM in the overmodulation region, simulations were implemented in the PLECS environment. Initially, the converter is connected to the grid without any power transfer. At the time 0.1 seconds, the reactive power increases in ramp up to the rated value. When the converter reaches steady-state, five consecutive failures are simulated in order to exemplify the converter operation in the overmodulation region.

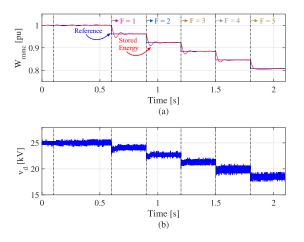

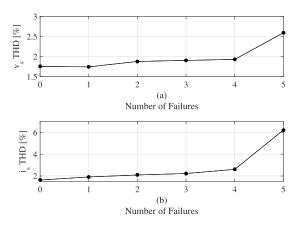

Figure 12 (a) illustrates the instantaneous active and reactive power delivered to the grid. Since the converter is working in inductive power factor, the reactive power is negative. As observed, even after the failures, the converter is able to deliver the rated power to the grid. Figure 12 (b) shows the circulating current dynamics. The average value of the circulating current is zero, since no active power is transferred from the dc-link to the grid. Up to the failure number 4, it can be observed a slightly increased ripple in instantaneous power and circulating current. Nevertheless, when F= 5, the ripple increases significantly, due to the increased low order harmonics synthesized by the converter.

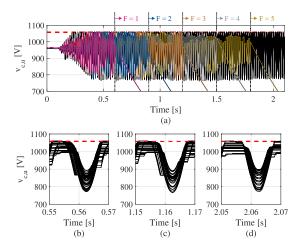

The cell capacitor voltages are illustrated in Fig. 13. Due to symmetry, only phase A is shown. The zoomed views in Fig. 13 (b)-(d) shows that the average capacitor voltages are well controlled and balanced, even in the overmodulation region.

Fig. 13. Effect of the failures in the MMC operation: (a) Upper arm of phase A; (b) Zoomed view for F = 0; (b) Zoomed view for F = 2; (b) Zoomed view for F = 5.

Fig. 14. Effect of the failures in the MMC operation: (a) Total MMC storage energy; (b) Dc-link voltage.

The tolerance band control guarantees that the capacitor voltages are within the upper limit (defined as 110 % of the rated voltage). The voltage of the faulty cells decreases due to the bleeder resistors connected in parallel with the cell capacitors.

Figure 14 (a) illustrates the MMC storage energy  $W_C$  after failures in per unit values. As observed, when the failures occur, the energy is reduced since less converter cells are operating. Once the converter is controlled in the balanced mode, this effect is also observed in the dc-link voltage, as shown in Fig. 14 (b).

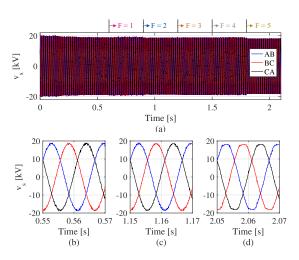

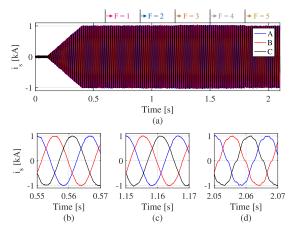

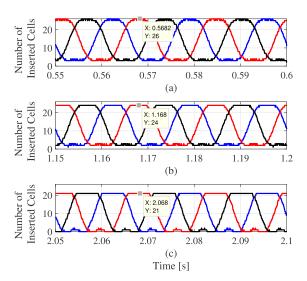

The line to line voltage and the current at the converter output is showed in Figs. 15 and 16, respectively. As observed, the converter is able to deliver rated current to the grid. At normal conditions, the waveforms are almost sinusoidal, since the converter presents 53 levels (2N+1) in the output voltage. Figure 17 presents the total harmonic distortion of line-to-line voltage and output current. As observed, for the first failures (start of the overmodulation region), the harmonic content increases slightly. This can be also noted in the waveforms

Fig. 15. Effect of the failures in the MMC operation: (a) Converter line-to-line voltage; (b) Zoomed view for F = 0; (b) Zoomed view for F = 2; (b) Zoomed view for F = 5.

Fig. 16. Effect of the failures in the MMC operation: (a) Grid current; (b) Zoomed view for F = 0; (b) Zoomed view for F = 2; (b) Zoomed view for F = 2; (c) Zoomed view for F = 2; (d) Zoomed view for F = 2; (e) Zoomed view for F = 2; (f) Zoomed view for F = 2; (e) Zoomed view for F = 2; (f) Zoomed view for F = 2; (h) Zoomed view for F = 2; (

presented in Figs. 15 (c) and 16 (c). Nevertheless, when F = 5, the output THD increases fast and exceeds 6 %.

The behavior of the output THD can be justified by the number of inserted cells, which are presented in Fig. 18. When the MMC operates properly (F=0), the insertion index varies in a staircase, as illustrated in Fig. 18 (a). When failures occur, the insertion index saturates in the upper limit (limited by the capacitor voltage ripples), as shown in Fig. 18 (b). This effect slightly increases the THD when more failures occur. Finally, when the number of failures increases even more, the insertion indexes are saturated in the upper and lower limits. Therefore, the output THD increases significantly in this region.

#### VII. CONCLUSIONS

This work discussed the inherent redundancy of modular multilevel converters in the overmodulation region. Initially, analytical expressions for the limits of the converter linear region were developed in order to define the minimum required dc-link voltage. Since the ripple voltages in MMC are not negligible, the interface between linear and overmodulation regions is strongly dependent on the cell capacitance.

Fig. 17. Total harmonic distortion (THD) as function of the number of failures: (a) Line-to-line voltage; (b) Grid current.

Fig. 18. Insertion number in steady-state for the lower arm: (a) F = 0; (b) F = 2; (c) F = 5.

Sensitivity analyses were implemented in order to show the effects of grid voltage variations, different output impedances, power factors and injected currents. The dc-link voltage value was selected based on these analyses. Afterwards, the effect of failures were evaluated.

The results indicated that the operation in overmodulation region has a significant inherent redundancy. For a modular multilevel converter with 26 cells per arm, the converter can ride through 4 failures without significantly increasing the output THD or applying some derating strategy in the converter. Furthermore, the fault-tolerance was reached without increase the converter cost. The authors believe this strategy can be interesting to improve the cost effectiveness of redundancy in MMC STATCOMs.

#### VIII. APPENDIX

#### A. Derivation of (24)

In linear region the insertion index must be higher than zero. From (19), it is possible to write:

$$0 < \frac{N - F}{N} \frac{v_d}{2} + \widehat{V}_s \cos(\omega_n t) - \frac{1}{6} \widehat{V}_s \cos(3\omega_n t). \tag{40}$$

The peak of the reference voltage  $v_s^*$  is obtained by doing  $\omega_n t = \pi/6$  [1]. Replacing  $\omega_n t = \pi/6$  in (40) leads to:

$$0 < \frac{N - F}{N} \frac{v_d}{2} - \widehat{V}_s \frac{\sqrt{3}}{2}. \tag{41}$$

Solving (41) to  $\hat{V}_s$ :

$$\widehat{V}_s < \frac{N - F}{N} \frac{v_d}{\sqrt{3}}.\tag{42}$$

This solution is denoted by  $\widehat{V}_{s0}$ .

#### B. Derivation of (25) and (31)

In the linear region, the insertion index must be lower than 1. The maximum insertion index is expected when the reference voltage is maximum, which means  $\omega_n t = \pi/6$  [1]. Substituting (20) in (19) yields:

$$n_l = \frac{\frac{N-F}{N}\frac{v_d}{2} + \hat{V}_s\cos(\omega_n t) - \frac{1}{6}\hat{V}_s\cos(3\omega_n t)}{v_d\left(\frac{N-F}{N}\right) + \frac{N}{2C_{1d}}\left(\Delta W_{\Sigma} - \Delta W_{\Delta}\right)} < 1. \quad (43)$$

Substituting (21) and (22) in (43) and replacing  $\omega_n t = \pi/6$  yields:

$$\frac{N-F}{N}\frac{v_d}{2} + \hat{V}_s \frac{\sqrt{3}}{2} < \frac{N-F}{N}v_d + \frac{N\hat{I}_s}{4\omega_n C} [f_1(\phi) + f_2(\phi)], \tag{44}$$

where

$$f_1(\phi) = -\frac{\hat{V}_s}{2v_d} \sin\left(\frac{\pi}{3} - \phi\right) + \frac{\hat{V}_s}{12v_d} \sin\left(\frac{\pi}{3} + \phi\right) + \frac{\hat{V}_s}{24v_d} \sin\left(\frac{2\pi}{3} - \phi\right), \tag{45}$$

$$f_2(\phi) = -\frac{N-F}{N} \sin\left(\frac{\pi}{6} - \phi\right) + \frac{8}{9} \frac{N}{N-F} \frac{\hat{V}_s^2}{v_d^2} \cos(\phi).$$

(46)

Relation (25) is obtained solving (44) to  $\hat{V}_s$ . On the other hand, relation (33) is obtained solving (44) to  $v_d$ .

#### REFERENCES

- K. Sharifabadi, L. Harnefors, H. Nee, S. Norrga, and R. Teodorescu, Design, Control and Application of Modular Multilevel Converters for HVDC Transmission Systems. John Wiley & Sons, 2016, ch. 2, pp. 121–125.

- [2] M. Kurtoğlu, F. Eroğlu, A. O. Arslan, and A. M. Vural, "Recent contributions and future prospects of the modular multilevel converters: A comprehensive review," *International Transactions on Electrical Energy Systems*, vol. 0, no. 0, p. e2763, 2018.

- [3] F. Shahnia, S. Rajakaruna, and A. Ghosh, Static compensators (STATCOMs) in power systems. Springer, 2015.

- [4] G. Liu, Z. Xu, Y. Xue, and G. Tang, "Optimized control strategy based on dynamic redundancy for the modular multilevel converter," *IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 339–348, Jan 2015.

- [5] Y. Chen, Z. Li, S. Zhao, X. Wei, and Y. Kang, "Design and implementation of a modular multilevel converter with hierarchical redundancy ability for electric ship mvdc system," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 5, no. 1, pp. 189–202, March 2017.

- [6] J. Guo, X. Wang, J. Liang, H. Pang, and J. Gonçalves, "Reliability modeling and evaluation of mmcs under different redundancy schemes," *IEEE Transactions on Power Delivery*, vol. 33, no. 5, pp. 2087–2096, Oct 2018.

- [7] J. V. M. Farias, A. F. Cupertino, H. A. Pereira, S. I. S. Junior, and R. Teodorescu, "On the redundancy strategies of modular multilevel converters," *IEEE Transactions on Power Delivery*, vol. 33, no. 2, pp. 851–860, April 2018.

- [8] B. Li, Y. Zhang, R. Yang, R. Xu, D. Xu, and W. Wang, "Seamless transition control for modular multilevel converters when inserting a cold-reserve redundant submodule," *IEEE Transactions on Power Electronics*, vol. 30, no. 8, pp. 4052–4057, Aug 2015.

- [9] N. Ahmed, L. Ängquist, A. Antonopoulos, L. Harnefors, S. Norrga, and H. Nee, "Performance of the modular multilevel converter with redundant submodules," in *IECON 2015 - 41st Annual Conference of the IEEE Industrial Electronics Society*, Nov 2015, pp. 003 922–003 927.

- [10] C. Kim and S. Lee, "Redundancy determination of hvdc mmc modules," *Electronics*, vol. 4, no. 3, pp. 526–537, 2015. [Online]. Available: http://www.mdpi.com/2079-9292/4/3/526

- [11] J. Xu, H. Jing, and C. Zhao, "Reliability modeling of mmcs considering correlations of the requisite and redundant submodules," *IEEE Transactions on Power Delivery*, vol. 33, no. 3, pp. 1213–1222, June 2018.

- [12] P. Briff, F. Moreno, and J. Chivite-Zabalza, "Extended controllability of hvdc converters in the vector space," *IEEE Transactions on Power Delivery*, vol. 32, no. 3, pp. 1505–1515, June 2017.

- [13] M. López, F. Briz, A. Zapico, D. Diaz-Reigosa, and J. M. Guerrero, "Operation of modular multilevel converters under voltage constraints," in 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Sept 2015, pp. 3550–3556.

- [14] L. Harnefors, A. Antonopoulos, S. Norrga, L. Angquist, and H. Nee, "Dynamic analysis of modular multilevel converters," *IEEE Transactions on Industrial Electronics*, vol. 60, no. 7, pp. 2526–2537, July 2013.

- [15] M. Hagiwara, R. Maeda, and H. Akagi, "Control and analysis of the modular multilevel cascade converter based on double-star chopper-cells (mmcc-dscc)," *IEEE Transactions on Power Electronics*, vol. 26, no. 6, pp. 1649–1658, June 2011.

- [16] A. Antonopoulos, L. Angquist, and H. Nee, "On dynamics and voltage control of the modular multilevel converter," in 2009 13th European Conference on Power Electronics and Applications, Sept 2009, pp. 1–10.

- [17] L. Angquist, A. Antonopoulos, D. Siemaszko, K. Ilves, M. Vasiladiotis, and H. Nee, "Open-loop control of modular multilevel converters using estimation of stored energy," *IEEE Transactions on Industry Applications*, vol. 47, no. 6, pp. 2516–2524, Nov 2011.

- [18] P. Rodríguez, R. Teodorescu, I. Candela, A. V. Timbus, M. Liserre, and F. Blaabjerg, "New positive-sequence voltage detector for grid synchronization of power converters under faulty grid conditions," in 2006 37th IEEE Power Electronics Specialists Conference, June 2006, pp. 1–7.

- [19] Y. Yue, F. Ma, A. Luo, Q. Xu, and L. Xie, "A circulating current suppressing method of mmc based statcom for negative-sequence compensation," in 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), May 2016, pp. 3566–3572.

- [20] A. Hassanpoor, L. Ängquist, S. Norrga, K. Ilves, and H. Nee, "Tolerance band modulation methods for modular multilevel converters," *IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 311–326, Jan 2015

- [21] K. Ilves, S. Norrga, L. Harnefors, and H. Nee, "On energy storage requirements in modular multilevel converters," *IEEE Transactions on Power Electronics*, vol. 29, no. 1, pp. 77–88, Jan 2014.

- [22] A. M. Hava, R. J. Kerkman, and T. A. Lipo, "Carrier-based pwm-vsi overmodulation strategies: analysis, comparison, and design," *IEEE Transactions on Power Electronics*, vol. 13, no. 4, pp. 674–689, July 1998.

- [23] B. Li, Z. Xu, S. Shi, D. Xu, and W. Wang, "Comparative study of the active and passive circulating current suppression methods for modular multilevel converters," *IEEE Transactions on Power Electronics*, vol. 33, no. 3, pp. 1878–1883, March 2018.

Allan Fagner Cupertino (M' 15) received the B.S. degree in electrical engineering from the Federal University of Viçosa (UFV) in 2013. and the M.S. degree in Electrical Engineering from the Federal University of Minas Gerais (UFMG). Currently, he is working toward the Ph.D. project about the use of modular multilevel converters in STATCOM applications.

Since 2014 he has been with the Materials Engineering Department at the Federal Center of Technological Education of Minas Gerais (CEFET),

teaching in the area of electric machines. His main research interests include renewable power generation systems, multifunctional inverters, modular multilevel converters and reliability of power electronic converters.

Prof. Cupertino was a recipient of the President Bernardes Silver Medal in 2013.

Heverton Augusto Pereira (M' 12) received the B.S. degree in electrical engineering from the Federal University of Viçosa in 2007, the M.Sc. degree in electrical engineering from the University of Campinas in 2009 and the Ph.D. degree from the Federal University of Minas Gerais in 2015. He was a guest Ph.D. from the Department of Energy Technology, Aalborg University, Denmark in 2014. He has been Adjunct Professor with the Electric Engineering Department, UFV, since 2009. His main research interests includes: grid-connected

converters for photovoltaic and wind power systems, and high-voltage dc/flexible ac transmission systems based on MMC.

Seleme Isaac Seleme Junior received the B.S. degree in electrical engineering from the Escola Politecnica (USP), São Paulo, Brazil, in 1977, the M.S. degree in electrical engineering from the Federal University of Santa Catarina, Florianópolis, Brazil, in 1985, and the Ph.D. degree in control and automation from the Institut National Polytechnique de Grenoble (INPG), Grenoble, France, in 1994. He spent a sabatical leave with the Power Electronics Group, Univesity of California, Berkeley, in 2002. In 2015, he spent a sabatical leave with the Institut

National Polytechnique de Toulouse, INP, France where he developed researches about decentralized control and capacitor voltage estimation techniques for modular multilevel converters.

He is currently Full Professor with the Department of Electronic Engineering, Federal University of Minas Gerais, Belo Horizonte, Brazil. His main research interests include renewable energy systems, modular multilevel converters and nonlinear control applied in power converters.

Remus Teodorescu (F' 12) received the Dipl.Ing. degree in electrical engineering from the Polytechnical University of Bucharest, Bucharest, Romania, in 1989, and the Ph.D. degree in power electronics from the University of Galati, Romania, in 1994. In 1998, he joined the Power Electronics Section, Department of Energy Technology, Aalborg University, Aalborg, Denmark, where he is currently a Full Professor. Since 2013, he has been a Visiting Professor with Chalmers University. His research interests include design and control

of grid-connected converters for photovoltaic and wind power systems, HVDC/FACTS based on modular multilevel converters (MMC) and storage systems based on Li-ion battery technology including modular converters and active BMS.