# **Aalborg Universitet**

# A Bridgeless Buck-flyback PFC Converter with High PF and Dead Angles Eliminated

Chen, Zhengge; Davari, Pooya; Wang, Huai

Published in:

Proceedings of 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019 - ECCE

Publication date: 2019

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Chen, Z., Davari, P., & Wang, H. (2019). A Bridgeless Buck-flyback PFC Converter with High PF and Dead Angles Eliminated. In *Proceedings of 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019 - ECCE Asia)* (pp. 1420-1427). Article 8797303 IEEE Press. https://ieeexplore.ieee.org/document/8797303

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

# A Bridgeless Buck-flyback PFC Converter with High PF and Dead Angles Eliminated

Zhengge Chen, Pooya Davari, and Huai Wang Department of Energy Technology, Aalborg University, Denmark

Abstract-- The inherent dead angles of the input line current in buck power factor correction (PFC) converter deteriorate the power factor (PF) and commonly extra switches with high control complexity are required to eliminate these dead angles. Alternatively, this paper proposed a topological solution using a simple single voltage loop control. The proposed switch integrated bridgeless buck-flyback PFC converter operates in buck-flyback mode and can automatically change to flyback mode when the dead angles occur. Bridgeless operation modes of the proposed converter are achieved by dual converter cells and the corresponding PF expression is derived. Besides, the inductors and transformers ratio is analyzed to ensure the high PF (>0.99) and the satisfactory input current harmonics (meet the IEC 61000-3-2 Class D limits) in the 100~240 Vac input voltage range. The 100 W prototypes of the conventional buck and the proposed converters are built for experimental tests, which confirm the effectiveness of the proposed topology.

Index Terms—dead angles eliminated, switches integrated, bridgeless Buck-flyback, high PF.

#### I. INTRODUCTION

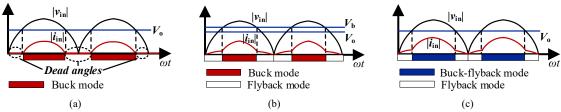

Compared to commonly employed boost power factor correction (PFC) converter, buck PFC converter has advantages of lower voltage stress across switch and higher efficiency at low line voltage, which is suitable for low power applications, such as laptop adaptors and low power AC power supply units [1], [2]. However, the inherent dead angles of the input line current have limited its applications, as there is no input line current flowing through the converter during these dead angles. Inevitably, this phenomenon deteriorates the power factor (PF) and increases the total harmonic distortions of the input line current (THDi). Consequently, to meet the IEC61000-3-2 requirement, the buck PFC converter with careful design has to limit its output voltage (e.g., set 80 Vdc output in the 100~240 Vac input voltage range) to minimize these dead angles [2]. Nonetheless, even though the buck PFC converter with limited output voltage can satisfy required PF and THDi to some extent, higher current conduction losses for a given power load and larger capacitors for a given hold-up time requirement are still problems to handle with in the design process [3], [4].

To tackle these dead angle issues, a variable on-time control is proposed to maximize the output voltage, but the dead angles still exist [3]. Others integrate buck-boost (or flyback, an isolated version of buck-boost) and buck topologies to obtain double switches-based buck PFC

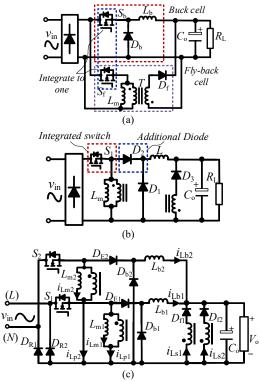

Fig. 1. The topology deriving process: (a) input-parallel-output-parallel buck-flyback PFC topology [6]; (b) switches integrated buck-flyback PFC topology; (c) the proposed switches integrated bridgeless buck-flyback PFC topology using dual buck and flyback cells.

converter, which will switch to buck-boost or flyback mode before the dead angles occurrence. Although the dead angles are eliminated, these solutions impose an additional required switch and the control circuit complexity [4]-[7]. For example, input-parallel-output-parallel buck-flyback converters are proposed in [6], as shown in Fig. 1(a), which mainly operate in buck mode and switched into flyback mode once control circuit detects the upcoming dead angles. Notably, besides the additional circuits required, a boundary output voltage should be set to guarantee the smooth mode change [6].

In order to simplify the control circuit and eliminate the use of additional sensor, using switch integration method in [8], a switch integrated buck-flyback PFC converter is shown in Fig. 1(b). However, for this topology, although dead angles can be eliminated without extra control complexity, there is an additional diode in the current path and part of energy transferred to the load is through the flyback transformer, which will degrade the converter efficiency. On the other hand, bridgeless PFC converters

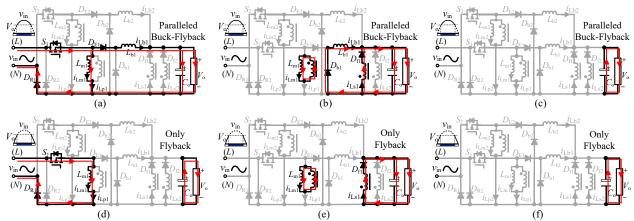

Fig. 2. Operation modes of the proposed converter in the positive input voltage. Buck and Flyback combination operation mode: when  $v_{in} > Vo$ , as shown in (a), (b), and (c). Flyback only operation mode: when  $v_{in} < Vo$ , as shown in (d), (e), and (f).

are becoming attractive due to their minimized conduction losses by eliminating the diode rectifier bridge [9], [10]. Among them, using the dual converter cells to obtain the bridgeless configurations is a popular solution and usually the obtained topologies possesses the merits of original PFC converters, e.g., dual buck, buck-boost, Cuk and Sepic [1], [9], [10].

Thus, to obtain a reasonable efficiency, the topology in Fig. 1(b) is further modified to the bridgeless buck-flyback converter, as shown in Fig. 1(c). Although the component count is doubled, the proposed bridgeless buck-flyback topology still inherits the merits of the topology in Fig. 1(b). It can adopt conventional simple control without sensing the line voltage and can eliminate dead angles by an automatic change from buck-flyback to flyback mode. Besides, theoretically the proposed converter does not have to limit its output voltage below 80V to meet the IEC 61000-3-2 requirement, which is an advantage when there is a hold-up time requirement. Moreover, the minimized conduction losses can maintain the efficiency of the proposed converter at a reasonable level compared with the conventional buck PFC converter.

This paper is organized as follows. Section II will introduce operation modes, derive the PF expression, and provides the inductor and transformer sizing to ensure that PF > 0.99 and the input current harmonics meet the IEC 61000-3-2 Class D limits in the 100~240 Vac input voltage range. Furthermore, discontinuous conduction mode (DCM) operation of the converter in order to nullify the reverse recovery losses of diodes while employ a single voltage loop control including guidelines on components selection are explained. Section III will demonstrate the experimental results of the proposed and the conventional buck PFC converters to verify the merits of the proposed converter. Finally, Section IV summarizes this study.

#### II. ANALYSIS OF THE Proposed CONVERTER

Fig. 1(c) has shown the proposed switch-integrated bridgeless buck-flyback PFC converter. Note that buck inductors  $L_{b1}$ ,  $L_{b2}$ , and diodes  $D_{b1}$ ,  $D_{b2}$  are from buck cells; magnetizing inductors  $L_{m1}$ ,  $L_{m2}$ , and diodes  $D_{f1}$ ,  $D_{f2}$ , are from flyback cells; switches  $S_1$ ,  $S_2$ , are the commonly used

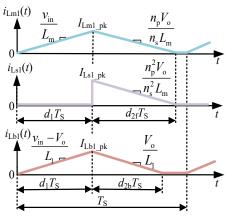

Fig. 3. Waveforms of the magnetizing inductor current  $i_{\rm Lm1}$ , secondary winding current  $i_{\rm Ls1}$ , and the buck cell inductor current  $i_{\rm Lb1}$ .  $n_{\rm p}$  and  $n_{\rm s}$  the primary and secondary winding turns of transformer.

components;  $D_{\rm E1}$  and  $D_{\rm E2}$  are the required extra diodes. In the positive half line cycle,  $L_{\rm b1}$ ,  $D_{\rm b1}$ ,  $L_{\rm m1}$ ,  $D_{\rm f1}$ ,  $D_{\rm E1}$ , and  $S_{\rm 1}$  operate to transfer the energy and in the negative half line cycle,  $L_{\rm b2}$ ,  $D_{\rm b2}$ ,  $L_{\rm m2}$ ,  $D_{\rm f2}$ ,  $D_{\rm E2}$ , and  $S_{\rm 2}$  operate. In this way, the traditional rectifier bridge can be cancelled and the conduction losses are spared.

Assumptions are given as: (i) All the components are ideal. (ii) Switching frequency  $f_{SW}$  is much higher than the line frequency  $f_L$  and the input line voltage  $v_{in}$  can be seen as constant within one switching cycle  $T_S$ . (iii) Capacitor  $C_0$  is large enough so that output voltage  $V_0$  can be seen as constant in one switching cycle. (iv)  $v_{in}$  is ideal input line voltage with  $V_M$  as its peak value and  $V_{in}$  as the RMS value.

### A. Operation modes

Due to the similar operation modes in the positive and negative half line cycle, this paper only gives analysis in the positive half line cycle. Fig. 2 gives the operation modes of the proposed converter and Fig. 3 shows the magnetizing inductor current  $i_{\rm Lm1}$ , the secondary winding current  $i_{\rm Ls1}$ , and the buck cell inductor current  $i_{\rm Lb1}$  waveforms. There are two types of operation modes, buckflyback combination operation mode and flyback only operation mode.

Fig. 4. Input voltage and current waveforms of converters: (a) conventional buck PFC converter with dead angles [2], (b) double switches-based buck PFC converter with requirement of detecting the boundary voltage  $V_b$  to switch between buck and flyback modes [4], [5], [7], (c) the proposed converter with two operation modes.

Fig. 5. Based on (3), the normalized input line current with (a) a as variable, and (b) m as variable.

For buck-flyback combination operation mode, as shown in Fig. 2(a), (b), (c), when  $v_{in} > V_o$ , both buck and flyback cells are in operation to transfer power.

In Fig. 2(a), when switch  $S_1$  is turned on, for buck cell, the input line current  $i_{\rm in}$  flows through the switch  $S_1$ , diode  $D_{\rm E1}$ , and rectifier diode  $D_{\rm R1}$  to charge  $L_{\rm b1}$  and feed the load. For flyback cell,  $i_{\rm in}$  flow through  $S_1$  and  $D_{\rm R1}$  to charge the magnetizing inductor  $L_{\rm m1}$  of the transformer. During this on-time switching period, both the buck inductor current  $i_{\rm Lb1}$  and magnetizing current  $i_{\rm Lm1}$  increase linearly.

In Fig. 2(b), when  $S_1$  is turned off,  $i_{Lb1}$  flow through  $D_{b1}$  to charge load, and the stored energy in the magnetizing inductor  $L_{\rm m}$  is discharged to the load through the ideal transformer and diode  $D_{\rm f1}$ . During this period, both  $i_{\rm Lb1}$  and  $i_{\rm Lm1}$  decrease linearly.

In Fig. 2(c), both current  $i_{Lb1}$  and  $i_{Lm1}$  have become zero, and only the output capacitor  $C_0$  feeds the load.

For flyback only operation mode, as shown in Fig. 2(d), (e), (f), when  $v_{\rm in} < V_{\rm o}$ , no current flows through the buck cell, same as in the conventional buck PFC converter. However, the flyback cell continues to work so that the dead angles of the input line current can be eliminated, as there is still current flowing through the flyback cell.

In Fig. 2(d), when  $S_1$  is turned on,  $i_{\rm in}$  flows through  $L_{\rm m1}$  and  $D_{\rm R1}$ , meanwhile,  $C_{\rm o}$  feeds the load. During the on time switching period, the magnetizing current  $i_{\rm Lm1}$  increases linearly.

In Fig. 2(e), the energy stored in  $L_{\rm ml}$  is discharged to load through transformer and diode  $D_{\rm fl}$ . During this period,  $i_{\rm Lml}$  reduces linearly.

In Fig. 2(f),  $i_{Lm1}$  has become zero and only the output capacitor  $C_0$  feeds the load.

## B. PF and input current harmonics

Fig. 4 shows the different type converters' input line current waveforms. Seen from Fig. 4, the proposed converter has the paralleled buck and flyback cells both working in the whole line cycle and when the dead angles come, the buck cell itself stops the operation. Then there is still flyback cell maintaining the input current. Hence, the input line current  $i_{\rm in}$  is the sum of the input currents  $i_{\rm in\_b}$  and  $i_{\rm in\_fly}$  from buck and flyback cells, expressed as:

$$i_{\text{in}}(t) = i_{\text{S1\_ave}}(t) = i_{\text{in\_b}}(t) + i_{\text{in\_fly}}(t)$$

(1)

For buck and flyback cells,  $i_{in\_b}$  and  $i_{in\_fly}$  have been given in [11] and [12]. Thus, (1) can be re-written as

$$i_{\text{in}}(t) = \begin{cases} \frac{V_{\text{M}}d_{1}^{2}}{2L_{\text{ml}}f_{\text{SW}}} \left(\frac{L_{\text{ml}}}{L_{\text{bl}}} \mid \sin \omega t \mid -\frac{V_{\text{o}}L_{\text{ml}}}{V_{\text{M}}L_{\text{bl}}} + \mid \sin \omega t \mid \right) & t \in \left[\frac{\theta}{\omega}, \frac{\pi - \theta}{\omega}\right] \\ \frac{V_{\text{M}}d_{1}^{2} \mid \sin \omega t \mid}{2L_{\text{ml}}f_{\text{SW}}} & t \in \left[0, \frac{\theta}{\omega}\right) \cup \hat{\frac{\pi}{\omega}} \frac{\pi}{\omega} \end{cases}$$

$$(2)$$

where  $\omega$  is the line angular frequency,  $d_1$  is the duty cycle of switch  $S_1$ , and  $\theta$  is equal to  $\sin^{-1}(V_o/V_M)$ .

Seen from (2),  $i_{\rm in}$  relates to the ratio of  $L_{\rm ml}/L_{\rm bl}$  and  $V_{\rm o}/V_{\rm M}$ . Hence, let  $L_{\rm ml}/L_{\rm bl}=a$  and  $V_{\rm o}/V_{\rm M}=m$ . (2) can be normalized as  $\odot$ :

$$i_{\text{in(Norm)}}(t) = \begin{cases} \frac{\alpha |\sin \omega t| - \alpha m + |\sin \omega t|}{a - \alpha m + 1} & t \in \left[\frac{\theta}{\omega}, \frac{\pi - \theta}{\omega}\right] \\ \frac{|\sin \omega t|}{a - \alpha m + 1} & t \in \left[0, \frac{\theta}{\omega}\right) \bigcup \left[\frac{\pi}{\omega}, \frac{\pi}{\omega}\right] \end{cases}$$

(3)

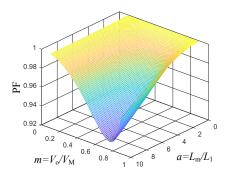

Based on (3), Fig. 5 is obtained. Seen from Fig. 5(a), when m is constant, by setting smaller a, the line current becomes more close to sinusoidal. On the other hand, when a is constant, the smaller m leads to more sinusoidal line current. In a half line cycle, the duty cycle  $d_1$  can be considered as a time-invariant value if the converter uses a single voltage loop control, also referred as constant duty cycle control in [13]. Then the average input power  $P_{\text{in\_b}}$  of buck and  $P_{\text{in\_f}}$  of flyback cells can be derived as:

①-The normalized equation can be obtained by:

$$f(t)_{\text{Norm}} = \frac{f(t) - f(t)_{\text{min}}}{f(t)_{\text{max}} - f(t)_{\text{min}}}$$

Note that 'am' is added in (3) in both numerator and denominator on the purpose of finding out the impact of 'm' on  $i_{\text{in(norm)}}$ .

Fig. 6. Based on (6), PF surface with m and a as variables. When  $a \in (0, 1.5]$ , then PF>0.99 in a wide input voltage range is guaranteed.

$$P_{\text{in\_b}} = \frac{V_{\text{M}}^2 d_1^2}{4L_{\text{bl}} f_{\text{SW}}} \left[1 - \frac{2}{\pi} \sin^{-1} \left(\frac{V_{\text{o}}}{V_{\text{M}}}\right) - \frac{2V_{\text{o}} \sqrt{V_{\text{M}}^2 - V_{\text{o}}^2}}{\pi V_{\text{M}}^2}\right]$$

(4)

$$P_{\text{in}_{_{1}}} = \frac{V_{\text{M}}^{2} d_{1}^{2}}{4L_{_{m}} f_{\text{sw}}}$$

(5)

The average input power  $P_{in}$  is the sum of  $P_{in\_b}$  and  $P_{in\_f}$ . Then, PF is derived as: PF =

$$\frac{\sqrt{\frac{\pi}{2}}\left[1+a-\frac{2}{\pi}a\theta-\frac{2}{\pi}am\sqrt{1-m^2}\right]}{\sqrt{\theta-m\sqrt{1-m^2}}+\int_{\theta}^{\pi-\theta}\left[a\mid\sin\omega t\mid-am+\mid\sin\omega t\mid\right]^2d(\omega t)}$$

(6)

Based on (6), Fig. 6 gives the PF surface with m and a as variables. Seen from Fig. 6, to ensure a high PF (> 0.99) in a wide input voltage range, which means that m changes widely, a should be in the range of (0, 1.5]. Furthermore, generally buck cell has better efficiency than flyback cell as there is no transformer in the buck cell. Hence, the ratio a should be chosen to ensure that buck cell processes more power than flyback cell. Assume  $\beta$  is the ratio between  $P_{\text{in } b}$  and  $P_{\text{in } f}$ . Then, based on (4) and (5), it results in

$$\beta = \frac{P_{\text{in\_b}}}{P_{\text{in\_f}}} = a(1 - \frac{2}{\pi}\theta - \frac{2}{\pi}m\sqrt{1 - m^2}). \tag{7}$$

Based on (7), Fig. 7 shows the power relationship between buck and flyback cells with a and m as variables. Seen from Fig. 7, when m is in a wide range, a should be as large as possible to allow buck cell process more power ( $\beta$  should be as large as possible). So in the range of (0, 1.5], a is determined to be 1.5.

In order to conduct the FFT analysis of the input current, firstly,  $i_{in}$  given in (2) needs to be simplified. Based on (4) and (5), assuming that the converter in this paper are all lossless systems (eff.  $\eta$ =1), then the constant duty cycle  $d_1$  can be obtained from (4) and (5) as:

$$d_{1} = \sqrt{\frac{4L_{\rm b1}f_{\rm sw}\pi P_{\rm in\_b}}{\eta V_{\rm M}^{2}(\pi - 2\sin^{-1}m - 2m\sqrt{1 - m^{2}})}}$$

(8)

$$d_{1} = \sqrt{\frac{4L_{\rm ml}f_{\rm sw}P_{\rm in_{-}f}}{\eta V_{\rm M}^{2}}} \tag{9}$$

where  $P_{\text{in\_b}} = P_o \cdot \beta / (\beta + 1)$  and  $P_{\text{in\_f}} = P_o / (\beta + 1)$ . Substitute  $d_1$  in (2) with (8) and (9), then it results in:

Fig. 7. Based on (7), power relationship between buck and flyback cells with *a* and *m* as variables. Seen from the curve, to get higher converter efficiency, *a* should be as large as possible.

$$i_{\text{in}}(t) = \begin{cases} \frac{2\pi P_{\text{in\_b}}(|\sin\omega t| - m)}{V_{\text{M}}(\pi - 2\sin^{-1}m - 2m\sqrt{1 - m^2})} + \frac{2P_{\text{in\_f}}|\sin\omega t|}{V_{\text{M}}} & t \in \left[\frac{\theta}{\omega}, \frac{\pi - \theta}{\omega}\right] \\ \frac{2P_{\text{in\_f}}|\sin\omega t|}{V_{\text{M}}} & t \in \left[0, \frac{\theta}{\omega}\right) \cup \left[\frac{\pi}{\omega}\right] \end{cases}$$

$$(10)$$

Seen from (10) and (7), the input line current  $i_{\rm in}$  of the proposed converter actually relates to  $V_{\rm M}$ , m,  $P_{\rm o}$ , and a (determined as 1.5). Similarly, the input current  $i_{\rm in\_b}$  of the conventional buck PFC converter can be obtained as:

$$i_{\text{in\_b}}(t) = \begin{cases} \frac{2\pi P_{\text{in\_b}}(|\sin \omega t| - m)}{V_{\text{M}}(\pi - 2\sin^{-1} m - 2m\sqrt{1 - m^2})} & t \in \left[\frac{\theta}{\omega}, \frac{\pi - \theta}{\omega}\right] \\ 0 & t \in \left[0, \frac{\theta}{\omega}\right) \cup \frac{\pi}{\omega} \end{cases}$$

(11)

which involves to only  $V_{\rm M}$ , m, and  $P_{\rm o}$ .

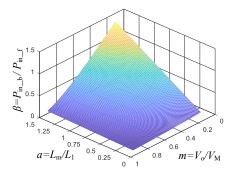

Therefore, based on (10) and (11), set  $P_o = 100 \text{ W}$ ,  $V_o = 80 \text{ V}$ , and  $V_M = \sqrt{2} \times (100 \sim 240) \text{ Vac}$ , the input current harmonic spectrums of the proposed and the conventional converter can be obtained in Fig. 8 with the RMS input voltage  $V_{\text{in}}$  as variable.

Seen from Figs. 8(a) and 8(b), when  $V_{\rm in}=100$  Vac, the  $3^{\rm rd}$  order input current harmonics of the conventional buck PFC converter exceeds the corresponding  $3^{\rm rd}$  order standard in the IEC 61000-3-2 Class D limits. In fact, the conventional buck PFC converter with a simple voltage loop control needs to further limit its input line current to pass the limit. Thus, according to (11), its  $P_{\rm o}$  (=  $P_{\rm in_b}$ ) or  $V_{\rm o}$  (involves to m) need to be reduced. On the other hand, as shown in Figs. 8(c) and 8(d), the input current harmonics of the proposed converter has satisfied the limits with margins. Hence, compared to the conventional buck PFC converter, the proposed converter has better performances in terms of PF and the input current harmonics.

## C. Component parameter determined

For the proposed converter operating in DCM, a simple voltage loop control is applied to regulate the output voltage and achieve the high PF. However, to ensure the DCM operation, the inductor limitation should be determined.

Referring to Fig. 3, the turning-off duty cycle  $d_{2b}$  and  $d_{2f}$  of buck and flyback cells can be expressed as:

Fig. 8. Based on (10) and (11), the input current harmonic spectrums of the conventional buck and the proposed converters with  $V_o = 80 \text{ V}$ ,  $P_o = 100 \text{ W}$ , and  $V_{\text{in}}$  as variable. (a) and (b) show the  $3^{\text{rd}} \sim 13^{\text{th}}$  order input current harmonics of the buck converter; (c) and (d) show corresponding current harmonics of the proposed converter.

$$d_{2b} = \frac{d_1(V_{\rm M}|\sin\omega t| - V_{\rm o})}{V_{\rm o}}$$

(12)

$$d_{2f} = \frac{V_{\rm M} \left| \sin \omega t \right| n_{\rm s} d_1}{V_{\rm o} n_{\rm p}} \tag{13}$$

As converters operate in the DCM,  $d_1+d_{2b} \le 1$  and  $d_1+d_{2f} \le 1$ , then there are:

$$\frac{V_o^2 \eta(\pi - 2\sin^{-1} m - 2m\sqrt{1 - m^2})}{4f_{sw}P_{in_b}} \ge L_{b1}$$

(14)

$$\frac{V_{\rm M}^2 \eta}{4 f_{\rm sw} P_{\rm in f}} \left( \frac{V_{\rm o} n_{\rm p} / n_{\rm s}}{V_{\rm M} + V_{\rm o} n_{\rm p} / n_{\rm s}} \right)^2 \ge L_{\rm ml}$$

(15)

Eq. (14) and (15) consider the limited inductance of each converter cell operating in DCM only, it should be

further revised by considering  $a = L_{\rm MI}/L_{\rm b1} = 1.5$  to ensure high PF. Moreover, the transformer turns ratio  $n_{\rm p}/n_{\rm s}$  in (15) can be determined by referring to [14], which has given the specific flyback design procedure. Basically, it uses the pre-set peak current limit and the maximum allowed turning-on duty cycle to derive the required parameters.

For the output capacitors, the capacitance is mainly determined by output ripple voltage and hold-up time requirements. In a steady operation, the output ripple voltage of a PFC converter is dominated by the second-order line frequency component, caused by the corresponding output ripple current. Thus, by assuming the second-order line frequency output current  $I_{\text{O rip}}$  as:

$$I_{\text{o rip}} = I_{\text{o}} \sin(2\omega t + \varphi) \tag{16}$$

where  $\varphi$  is the angle difference between the grid. Then, the output ripple voltage  $\Delta V_{\text{o\_rip}}$  can be expressed as:

$$\Delta V_{\text{o_rip}} = \frac{1}{C_{\text{o_r}}} \int_0^t I_{\text{o}} \sin(2\omega t + \varphi) d(t)$$

$$= \frac{I_{\text{o}} \cos(\varphi) - I_{\text{o}} \cos(2\omega t + \varphi)}{2\omega C_{\text{o r}}}$$

(17)

Based on (17), considering the worst case of  $\Delta V_{o_{\text{rip}}}$ , then the required capacitance  $C_{o_{\text{r}}}$  is:

$$C_{\text{o_r}} = \frac{P_{\text{o}}}{2 \cdot \pi \cdot f_{\text{L}} \cdot V_{\text{o}} \cdot \Delta V_{\text{o rip}}}$$

(18)

where  $P_o/V_o = I_o$  and  $2 \cdot \pi \cdot f_L = \omega$ . Note that (18) is applicable to most PFC converters [14], [15]. However, for the PFC converters with high output voltage ripple requirement, (18) considers the worst scenario of output ripple may cause too much over design of capacitance selection. Specially, for the buck cell,  $P_o$  in (18) should be further revised as  $P_o[1-2\sin^{-1}(m)/\pi]$ , due to the dead angles.

The hold-up time  $t_{\text{hold\_up}}$  actually involves the energy storage of the output capacitors. Accordingly, the minimum required capacitance  $C_{\text{o t}}$  is:

$$C_{o_{-t}} = \frac{2P_{o}t_{\text{hold\_up}}}{V_{o}^{2} - V_{o,\text{min}}^{2}}$$

(19)

where  $V_{o\_min}$  is the minimum output voltage. The final capacitance  $C_o$  should be the maximum value of  $C_{o\_r}$  and  $C_{o\_t}$ . In this paper, the hold-up time is not considered as the  $V_{o\_min}$ , mainly depending on the lowest input voltage of the post DC-DC converter, is not specified here.

For semiconductors, empirically, the maximum peak or the average conduction currents determine the selection. Furthermore, a de-rated factor, e.g. 0.8 or 0.85, is used to guarantee the selected devices are capable to handle the conduction current. More delicately, others have used the power loss models of each devices in different topologies to find out the best cost-effective or the lowest power losses devices by design iterations [17]. However, it needs to build the components' database and the corresponding precise models to ensure the accurate results.

This paper only adopts the empirical way to determine the semiconductors, as the purpose of this paper is to offer a new topology solution for solving dead angles not yet to optimize it. The peak current expressions of main components switch  $S_1$ , rectifier diode  $D_{R1}$ , and diodes  $D_{b1}$ ,  $D_{E1}$ ,  $D_{f1}$  can be expressed as:

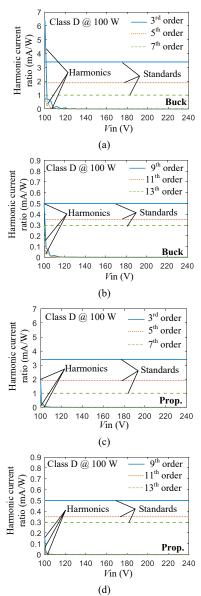

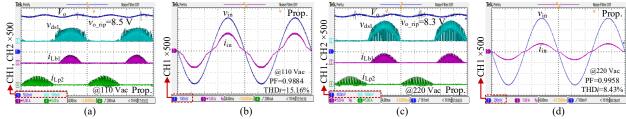

Fig. 9. The conventional buck PFC converter experimental waveforms with (a), (b) in 110 Vac and (c), (d) in 220 Vac input voltage. In (a) and (c), output voltage  $V_o$  [25 V/div], reversed voltage across switch  $v_{ds}$  [250 V/div], inductor current  $i_L$  [5 A/div], voltage across diode rectifier bridge  $V_d$  [250 V/div], and time [4 ms/div]. In (b) and (d), input voltage  $v_{in}$  [50 V/div], input current  $i_{in}$  [1 A/div] and time [4 ms/div].

Fig. 10. The proposed bridgeless buck-flyback PFC converter experimental waveforms with (a), (b) in 110 Vac and (c), (d) in 220 Vac input voltage. In (a) and (c), output voltage  $V_o$  [25 V/div], reversed voltage across switch  $v_{ds1}$  [250 V/div], the buck cell inductor current  $i_{Lb1}$  [5 A/div], the flyback cell primary winding current in the transformer  $i_{Lp2}$  [5 A/div], and time [4 ms/div]. In (b) and (d), input voltage  $v_{in}$  [50 V/div], input current  $i_{in}$  [1 A/div] and time [4 ms/div].

$$I_{\rm S1\_pk} = I_{\rm DR1\_pk} = (\frac{V_{\rm M} \left| \sin \omega t \right| - V_{\rm o}}{L_{\rm b1}} + \frac{V_{\rm M} \left| \sin \omega t \right|}{L_{\rm m1}}) d_1 T_{\rm S} \quad (20)$$

$$I_{\text{Db1\_pk}} = I_{\text{DE1\_pk}} = I_{\text{Lb1\_pk}} = \frac{V_{\text{M}} |\sin \omega t| - V_{\text{o}}}{L_{\text{b1}}} d_1 T_{\text{S}}$$

(21)

$$I_{\text{Dfl\_pk}} = I_{\text{Lsl\_pk}} = \frac{n_{\text{p}}^2 V_{\text{o}}}{n_{\text{s}}^2 L_{\text{ml}}} d_{2\text{f}} T_{\text{S}}$$

(22)

$d_1$  in (20) and (21) can be referred to (8) and  $d_{2f}$  referred to (13). Note that (20), (21), and (22) are only the peak current expressions in each switching cycle. The peak values in a half line cycle can be obtained when  $|\sin \omega t|$ =1.

## III. EXPERIMENTAL VALIDATIONS

For the proposed converter, using (14) and (15) with the specifications given in Table I, the limited  $L_{\rm m}$  and  $L_{\rm b}$  are obtained for DCM operation. Similarly, the DCM limited L is obtained for the conventional buck PFC converter. Considering margins, the final used  $L_{\rm m}$ ,  $L_{\rm b}$ , and L are  $0.9\times$  calculated limited values to guarantee the DCM operations. Output capacitors and semiconductors are selected based on (18) and (20)~(22), respectively. Final devices are shown in the Table II. The conventional buck and the proposed buck-flyback prototypes with single voltage loop control are built for experimental validations. The control is implemented by DSP28335 and the switch driving IC chip is ADUM3223. Fig. 9 and Fig. 10 show the experimental waveforms of the conventional buck and the proposed bridgeless buck-flyback converters.

Seen from Figs. 10(a) and 10(c), in one line cycle,  $S_1$ ,  $L_{\rm ml}$ , and  $L_{\rm b1}$  only operate in the half line cycle and in the complementary half line cycle,  $S_2$ ,  $L_{\rm m2}$ , and  $L_2$  operate. These waveforms have proved that the proposed converter is operating under the 'dual bridgeless' configuration, as each converter cell operates in only positive or negative line cycle to avoid the use of diode rectifier bridge.

TABLE I Parameters of Converters

| Rey I diameters of Converters |                             |               |  |

|-------------------------------|-----------------------------|---------------|--|

| Specifications                | The proposed                | Conv. buck    |  |

| f <sub>SW</sub>               | 50 kHz                      | 50 kHz        |  |

| $f_{ m L}$                    | 50 Hz                       | 50 Hz         |  |

| $V_{ m in}$                   | 100~240 Vac                 | 100~240 Vac   |  |

| $V_{o}$                       | 80 Vdc                      | 80 Vdc        |  |

| $P_{\mathrm{o}}$              | 100 W                       | 100 W         |  |

| $d_{1\max}$                   | 30%                         | 30%           |  |

| $\Delta V_{ m o\_rip}$        | ≤10 V                       | ≤10 V         |  |

| η                             | ≈91%                        | ≈93%          |  |

| DCM Limited L                 | -                           | ≤153 μH, cal. |  |

| DCM Limited Lm                | $\leq$ 390 µH, cal. by (15) | -             |  |

| DCM Limited L <sub>b</sub>    | ≤260 µH, cal. by (14)       | -             |  |

| a = Lm/L                      | 1.5                         | -             |  |

TABLE II Component Selections of Converters

| Comp.                                            | The proposed               | Comp.            | Conv. buck                 |

|--------------------------------------------------|----------------------------|------------------|----------------------------|

| $L_{b1}, L_{b2}$                                 | 240 μH (Toroidal:          | L (0.9 ×         | 138 μH (Toroidal:          |

| $(0.9 \times limited L_b)$                       | CH571060)                  | limited L)       | CH571060)                  |

| $L_{\rm m1},L_{\rm m2}$                          | 360 μH (E core:            |                  |                            |

| (0.9×limited L <sub>m</sub> )                    | B66366)                    | -                | -                          |

| Turns ratio                                      | 41:31                      | -                | -                          |

| $D_{R1}, D_{R2}, D_{f1}, D_{62}$                 | STTH12R06D                 | Rectifier        | GBU8J                      |

| $D_{\rm E1}, D_{\rm E2}, D_{\rm b1}, D_{\rm b2}$ | STTH5R06D                  | D                | STTH5R06D                  |

| $S_1, S_2$                                       | IXFH12N65X2                | S                | IXFH12N65X2                |

| $C_{o}$                                          | $330~\mu F/100~V~\times 3$ | $C_{\mathrm{o}}$ | $330~\mu F/100~V~\times 3$ |

In Figs. 9(b) and 9(d), it is clear that the dead angles exist in the input line current of the conventional buck PFC converter. Consequently, the corresponding PF and THDi are 0.94 and 37% with 110 Vac input voltage, 0.99 and 17% with 220 Vac input voltage. By contrast, in Figs. 7(b) and 7(d), the proposed converter eliminates the dead angles and the corresponding PF and THDi are 0.99 and 15% with 110 Vac input voltage, 0.99 and 8% with 220 Vac input voltage. The performance improvements are obvious in terms of PF and THDi, especially in the low input line voltage. Besides, by comparing  $V_{o_{\rm rip}}$  in Figs. 9 and 10, it can be seen that the proposed converter has relatively smaller output voltage ripple than the conventional buck PFC converter.

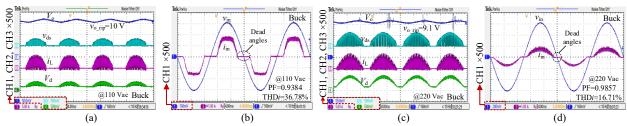

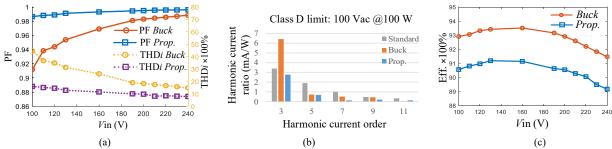

Fig. 11. Measured experimental data in the 100~240 Vac input voltage range, (a) PF and THDi, (b) harmonic current ratio, (c) efficiency (full load).

Furthermore, in the 100~240 Vac input voltage range, the measured experimental data are shown in the Fig. 11. Seen from Fig. 11(a), the PF of the proposed converter is near unity and the measured THD*i* is below 15%, better than the performances of the conventional buck PFC converter. Moreover, as shown in Fig. 11(b), the proposed converter can satisfy the IEC61000-3-2 Class D limits. By contrast, the conventional buck converter cannot meet the limits. These experimental results are in agreement with the corresponding input current harmonics analysis presented in Fig. 8.

Nevertheless, seen from Fig. 11(c), the efficiency of the proposed converter is worse than that of the conventional buck PFC converter, almost 2% less in average. This is due to the more component count and the used transformers in the proposed converter.

#### IV. CONCLUSIONS

To eliminate the dead angles of the input line current in the conventional buck PFC converter, many literatures use additional switch and control circuit to switch between the buck and flyback modes, which are effective but at cost of high control complexity.

Alternatively, in order to maintain the simple control meanwhile eliminate the dead angles, this paper integrates switches to allow the proposed converter automatically changing between the buck-flyback mode and the buck mode. Although the proposed converter decreases the efficiency due to the more component count, however, the dual bridgeless configuration can maintain the efficiency at an acceptable level. Consequently, in the 100~240 Vac input voltage range, compared to the conventional buck PFC converter, the proposed converter, in compliance with IEC 61000-3-2 Class D limits, has better PF, THD*i*, and smaller output voltage ripple, but at cost of around 2% decreased efficiency in the 100 W prototype.

#### REFERENCES

- [1] Y. Jang, and M. M. Jovanovic, "Bridgeless High-Power-Factor Buck Converter," *IEEE Trans. Ind. Electron.*, vol. 26, no. 2, pp. 602–611, Feb. 2011.

- [2] L. Huber, L. Gang, and M. M. Jovanović, "Design-oriented analysis and performance evaluation of buck PFC front end," *IEEE Trans. Power Electron.*, vol. 25, no. 1, pp. 85– 94, Jan. 2010.

- [3] X. Wu, J. Yang, J. Zhang, and Z. Qian, "Variable on-time (VOT)-controlled critical conduction mode buck PFC converter for high-input AC/DC HB-LED lighting

- applications," *IEEE Trans. Power Electron.*, vol. 27, no. 11, pp. 4530–4539, Nov. 2012.

- [4] X. Xie, C. Zhao, Q. Lu, and S. Liu, "A novel integrated buck-flyback nonisolated PFC converter with high power factor," *IEEE Trans. Ind. Electron.*, vol. 60, no. 12, pp. 5603–5612, Dec. 2013.

- [5] J. Zhang, C. Zhao, S. Zhao, and X. Wu, "A family of single-phase hybrid step-down PFC converters," *IEEE Trans. Power Electron.*, vol. 32, no. 7, pp. 5271–5281, Jul. 2017.

- [6] G. Spiazzi and S. Buso, "Power factor preregulators based on combined buck-flyback topologies," *IEEE Trans. Power Electron.*, vol. 15, no. 2, pp. 197–204, Mar. 2000.

- [7] X. Lin and F. Wang, "New bridgeless buck PFC Converter with improved input current and power factor," *IEEE Trans. Ind. Electron.*, vol. 65, no. 10, pp. 7730–7740, Oct. 2018.

[8] T. F. Wu and Y. K. Chen, "A systematic and unified

- [8] T. F. Wu and Y. K. Chen, "A systematic and unified approach to modeling PWM DC/DC converters based on the graft scheme," *IEEE Trans. Ind. Electron.*, vol. 45, no. 1, pp. 88–98, Feb. 1998.

[9] V. Bist and B. Singh, "An adjustable-speed PFC bridgeless

- [9] V. Bist and B. Singh, "An adjustable-speed PFC bridgeless buck-boost converter-fed BLDC motor drive," *IEEE Trans. Ind. Electron.*, vol. 61, no. 6, pp. 2665–2677, Jun. 2014.

- [10] A. J. Sabzali, E. H. Ismail, M. A. Al-Saffar, and A. A. Fardoun, "New Bridgeless DCM Sepic and Cuk PFC Rectifiers With Low Conduction and Switching Losses," *IEEE Trans. Ind. Appl.*, vol. 47, no. 2, pp. 873-881, Mar./April 2011.

- [11] H. Endo, T. Yamashita, and T. Sugiura, "A high power factor buck converter," in *Proc. Power Electron. Specialist Conf.* (PESC), 1992, pp. 1071–1076.

- [12] R. Erickson, M. Madigan, and S. Singer, "Design of a simple high-power-factor rectifier based on the flyback converter," in *Proc. Appl. Power Electron. Conf. Expo.* (APEC), 1990, pp. 792–801.

- [13] Z. Chen, P. Yang, G. Zhou, J. Xu, and Z. Chen, "Variable Duty Cycle Control for Quadratic Boost PFC Converter," *IEEE Trans. Ind. Electron.*, vol. 63, no. 7, pp. 4222–4232, Jul. 2016.

- [14] Infineon Appl. Note, "55 W flyback converter design using the IRS2982S controller IRXLED04," Infineon Tech., Munich, Germany, 2017. [Online].

- [15] TI Literature No: SLUP264, "Power Factor Correction Using the Buck Topology-Efficiency Benefits and Practical Design Considerations," Texas Instruments Incorporated, Texas, US, 2010. [Online]

- [16] R. M. Burkart and J. W. Kolar, "Comparative Life Cycle Cost Analysis of Si and SiC PV Converter Systems Based on Advanced η-ρ-σ Multi-objective Optimization Techniques," *IEEE Trans. Power Electron.*, vol. 32, no. 6, pp. 4344–4358, Jun. 2017.

- [17] D. Pan, X. Ruan, C. Bao, W. Li, and X. Wang, "Magnetic integration of the LCL filter in grid-connected inverters," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 1573–1578, Apr. 2014.