# **Aalborg Universitet**

# Implementation of Designed PV Integrated Controlled Converter System

De, Saptarshi; Swathika, O. V. Gnana; Tewari, Nilanjan; Venkatesan, Anantha Krishnan; Subramaniam, Umashankar; Bhaskar, Mahajan Sagar; Padmanaban, Sanjeevikumar; Leonowicz, Zbigniew; Mitolo, Massimo

Published in: **IEEE Access**

DOI (link to publication from Publisher): 10.1109/ACCESS.2020.2997405

Creative Commons License CC BY 4.0

Publication date: 2020

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

De, S., Swathika, O. V. G., Tewari, N., Venkatesan, A. K., Subramaniam, U., Bhaskar, M. S., Padmanaban, S., Leonowicz, Z., & Mitolo, M. (2020). Implementation of Designed PV Integrated Controlled Converter System. IEEE Access, 8, 100905-100915. https://doi.org/10.1109/ACCESS.2020.2997405

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

Received May 1, 2020, accepted May 17, 2020, date of publication May 25, 2020, date of current version June 9, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.2997405

# Implementation of Designed PV Integrated **Controlled Converter System**

SAPTARSHI DE<sup>1</sup>, O. V. GNANA SWATHIKA<sup>10</sup>, (Member, IEEE), NILANJAN TEWARI<sup>1</sup>, (Member, IEEE), ANANTHA KRISHNAN VENKATESAN<sup>®</sup><sup>1</sup>, UMASHANKAR SUBRAMANIAM<sup>©2</sup>, (Senior Member, IEEE), MAHAJAN SAGAR BHASKAR<sup>®</sup>2, (Member, IEEE), SANJEEVIKUMAR PADMANABAN<sup>®</sup>3, (Senior Member, IEEE), ZBIGNIEW LEONOWICZ<sup>04</sup>, (Senior Member, IEEE), AND MASSIMO MITOLO<sup>5</sup>, (Fellow, IEEE)

<sup>1</sup>School of Electrical Engineering, Vellore Institute of Technology (VIT), Chennai 600127, India

Corresponding authors: O. V. Gnana Swathika (gnanaswathika.ov@vit.ac.in) and Sanjeevikumar Padmanaban (san@et.aau.dk)

**ABSTRACT** Photovoltaic (PV) energy has increased drastically at an average annual rate of 60% in the last few years. It quickly became an integral part of the power system networks. This increase, in turn, has triggered the evolution of PV power converters with more efficiency and reliability. In this paper, a prototype of the PV integrated controlled converter system is designed, which is applicable in water pumping for irrigation. Main components of this system are floating dual boost converter (FDBC), three-phase voltage source inverter (VSI) and three-phase squirrel cage induction motor (pump). For address the issue of PV voltage fluctuations, a voltage mode controller is designed for the FDBC which regulates the output voltage of the FDBC to a fixed value irrespective of any voltage fluctuations at the PV side.

**INDEX TERMS** Floating dual boost converter, photovoltaic system, power converter.

# **NOMENCLATURE**

| $v_{in}/v_{o}$             | The input voltage of FDBC/ Average output voltage of FDBC   |

|----------------------------|-------------------------------------------------------------|

| $v_{\rm C1}/v_{\rm C2}$    | The voltage across $C_1$ /Voltage across $C_2$              |

| $i_{\rm in}/i_{\rm o}$     | The input current of FDBC/ Average load current of FDBC     |

| $i_{L1}/i_{L2}$            | Inductor $(L_1)$ current/Inductor $(L_2)$ current           |

| $\Delta v_c  / \Delta i_L$ | Capacitor ripple voltage of FDBC /Inductor                  |

|                            | ripple current                                              |

| $\Delta v_0/\Delta i$      | Output voltage ripple of FDBC /Input current ripple of FDBC |

| R                          | Resistive load of FDBC                                      |

| d                          | The duty cycle of FDBC                                      |

| $f_s$                      | Switching frequency                                         |

The associate editor coordinating the review of this manuscript and approving it for publication was Pierluigi Siano.

# I. INTRODUCTION

In today's world, the most important downside faced in the field of the power sector is the incrementing power demand and is probably to rise to 76% by 2030. In overpopulated countries, like India, there is a dearth of power-generating resources, and as a result, many cities and towns are facing constant load shedding and black-outs. Another concern is that the power generating stations and distribution locations are far from each other resulting in insufficient power supply to the rural areas. Renewable energy sources (RES) in conjunction with power electronics is one of the potential solutions to tackle the problems of power demand and lack of flexibility in power distribution. Solar energy is considered to be one of the most important renewable energy sources (RES) because it is free of cost, abundantly available and pollution-free. The technology of converting solar energy into electricity is called photovoltaic (PV) and is done using semiconductor that exhibits photovoltaic. Solar energy-based applications are being widely used in many islands and rural

<sup>&</sup>lt;sup>2</sup>Renewable Energy Lab (REL), Department of Communication and Networks, College of Engineering, Prince Sultan University (PSU), Riyadh 11586, Saudi

<sup>&</sup>lt;sup>3</sup>Department of Energy Technology, Aalborg University, 6700 Esbjerg, Denmark

<sup>&</sup>lt;sup>4</sup>Faculty of Electrical Engineering, Wroclaw University of Science and Technology, 50-370 Wroclaw, Poland

<sup>&</sup>lt;sup>5</sup>School of Integrated Design, Engineering, and Automation, Irvine Valley College, Irvine, CA 92618, USA

areas where the distribution networks do not reach. One of the most promising applications is solar water pumping for irrigation.

Agriculture is the backbone of India. Statistically, 64% of the cultivated land depends on monsoon. Therefore it is essential to provide and improve irrigation methodology in India. However, due to lack of generation and distribution of electric energy in agricultural areas of India, it is difficult to implement an effective and efficient irrigation system. PV water pumping irrigation system is one of the feasible solutions to this problem. PV systems for water pumping applications are extensively used around the world as they are highly reliable systems that inherently require low maintenance. Use of solar energy for irrigation is suggested in [1]. In [2] authors proposed a solar-powered automatic irrigation system. Solarpowered drip irrigation scheme is presented in [3]. Optimal design of the solar-powered fuzzy control irrigation system is proposed in [4]. However, high initial cost and low energy conversion efficiency result in high expense [5]. Therefore, there is scope and need for research in this domain.

Though there are various techniques for solar-based irrigation, the basic system includes a PV system, a converter module and a motor (pump) as load. PV fed DC motor for water pumping is available in the literature. However, they have limited applications due to the high cost and maintenance problems of DC motors for being commutators type machines [6]. On the contrary, the induction motor is free from brushes and commutators and maintenance is almost negligible. Thus DC motors are now replaced by induction motors for solar pumping.

The output of PV is low-level DC voltage and needs to be boosted to a higher level for any potential application [7]. The converter module does this. A transformer in many applications is used to provide increased voltage gain [8]. However, for large power conversion the size as well as the cost of the transformer increases. Thus making the system bulky and expensive. As a result, transformer-less power electronic converter systems are now becoming popular [9]. Transformer-less power electronic converter systems consist of a DC-DC boost converter and also an inverter if the load is AC. The voltage gain is controlled by the duty cycle of the DC-DC boost converter. The conventional boost converter topology cannot be used for high voltage conversion [10]. Some potential topologies of DC-DC converter with high gain are presented in [11], [12]. However, the concept of high current ripples is a drawback. The technique of interleaving reduces high ripple current. However, the voltage gain is the same as that of the conventional boost converter. Some of the interleaved topologies with high voltage gain are presented in [13], [14]. Other high gain topologies are proposed in [15]–[21]. The converter topology implemented in this paper was proposed in [22]. It comprised of two conventional boost modules connected in parallel at the input, namely the non-floating topology and the floating topology. Parallel connection of the two modules at the input side and the phaseshifted control signals between the two switches ensures interleaving. This topology is known as floating dual boost converter (FDBC). Another issue that has to be tackled is the problem of PV voltage fluctuation. As it is evident that the PV voltage is a function of irradiance which varies with time, thus the PV output voltage is not constant throughout when driving a constant load. This problem of voltage fluctuations needs to be addressed [23]–[34].

The objective of this work is to design a prototype of a PV integrated controlled converter system applicable to water pumping for irrigation. Main components of this system are an FDBC, a three-phase voltage source inverter (VSI) and a three-phase squirrel cage induction motor (pump). For address the issue of PV voltage fluctuations, a voltage mode controller is designed for the FDBC which regulates the output voltage of the FDBC to a fixed value irrespective of any voltage fluctuations at the PV side.

#### **II. PROPOSED SYSTEM DESCRIPTION**

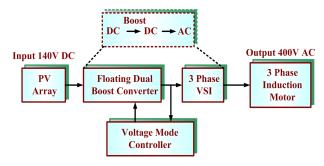

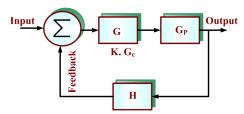

Block diagram of the proposed system shown in Fig. 1. This system is basically a PV fed converter module driving an induction motor. The input to the system is from a series of connected PV panels. Each PV panel is rated for 35 V, 8 amps. Four such panels are connected in series to obtain a PV array of rating 140 V, 8 amps. The PV array is the input to the floating dual boost converter (FDBC). The PV voltage is boosted to 485 V by the FDBC to drive the induction motor. The DC output of the FDBC is fed to a conventional three-phase voltage source inverter (VSI) for conversion from DC to AC and then connected to the three-phase induction motor. The three-phase VSI is operated in 180 degrees conduction mode. The motor is rated for 400 V (rms), 1.8 amps. A voltage mode controller is incorporated using DSPIC30F4011 for the FDBC. The voltage mode controller ensures that the input voltage to the VSI is maintained constant irrespective of voltage fluctuations in the PV output voltage.

FIGURE 1. Block diagram of PV integrated controlled converter system.

#### III. MODELLING OF FDBC

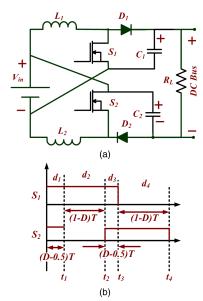

The floating dual boost converter, also known as a twophase interleaved double dual boost converter, consists of two modules. Module 1 comprises of  $L_1$ ,  $S_1$  and  $C_1$  and module 2 comprises of  $L_2$ ,  $S_2$ , and  $C_2$ . The steady-state operating point is chosen at duty cycle > 50%. Fig. 2(a) shows a circuit diagram and Fig. 2(b) shows the switching sequence of FDBC.

FIGURE 2. Circuit diagram and switching sequence of FDBC, (a) circuit diagram of FDBC, (b) switching sequence for d > 0.5 of FDBC.

The output voltage, output current, input current and voltage stress across the switches and diodes is given by,

$$v_o = v_{C1} + v_{C2} - v_{in} \tag{1}$$

$$i_o = v_o/R \tag{2}$$

$$i_{in} = i_{L1} + i_{L2} - i_o (3)$$

$$v_s = v_{C1} + v_{C2} = v_o - v_{in} \tag{4}$$

#### A. LARGE SIGNAL MODEL

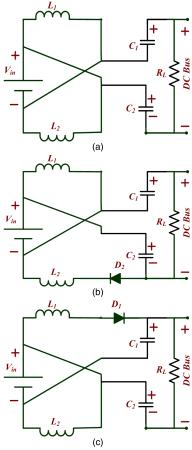

Mode 1 (0 to  $t_1$ ): When  $S_1$  and  $S_2$  are turned ON. Fig. 3(a) shows the circuit during mode 1.  $L_1$  and  $L_2$  are charging, and  $C_1$  and  $C_2$  are discharging. State-space representation of mode 1 is represented by,

$$\dot{x} = A_{m1}x + B_{m1}u \Rightarrow \begin{bmatrix} \dot{i}_{L1} \\ \dot{v}_{C1} \\ \dot{i}_{L2} \\ \dot{v}_{C2} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & \frac{-1}{RC_1} & 0 & \frac{-1}{RC_1} \\ 0 & 0 & 0 & 0 \\ 0 & \frac{-1}{RC_2} & 0 & \frac{-1}{RC_2} \end{bmatrix}$$

$$\times \begin{bmatrix} i_{L1} \\ v_{C1} \\ i_{L2} \\ v_{C2} \end{bmatrix} + \begin{bmatrix} \frac{1}{L_1} \\ \frac{1}{RC_1} \\ \frac{1}{L_2} \\ \frac{1}{RC_2} \end{bmatrix} v_{in}$$

(5)

$$\begin{bmatrix}

\overline{RC_2} \\

y = C_{m1}x + D_{m1}u \Rightarrow [V_o] = \begin{bmatrix} 0 & 1 & 0 & 1 \end{bmatrix} \begin{bmatrix} i_{L1} \\ v_{C1} \\ i_{L2} \\ v_{C2} \end{bmatrix} \qquad y = C_{m2}x + D_{m2}u \Rightarrow [V_o] = \begin{bmatrix} 0 & 1 & 0 & 1 \end{bmatrix} \begin{bmatrix} i_{L1} \\ v_{C1} \\ i_{L2} \\ v_{C2} \end{bmatrix} \\

+ [-1]V_{in} \qquad (6) \qquad \text{Fig. 3(c) shows the circuit during mode 3. Learn C. as}$$

Mode 2 ( $t_1$  to  $t_2$ ): When  $S_1$  is turned ON, and  $S_2$  is turned OFF. Fig. 3(b) shows the circuit during mode 2.  $L_1$  and  $C_2$

FIGURE 3. FDBC equivalent circuit (a) mode 1, (b) mode (2), (c) mode 3.

are charging while  $L_2$  and  $C_1$  are discharging. State-space representation of mode 2 is represented by (7) and (8).

and

$$C_1$$

and  $C_2$  are discharging. State-space representation of mode 1 is represented by,

$$\dot{x} = A_{m1}x + B_{m1}u \Rightarrow \begin{bmatrix} \dot{i}_{L1} \\ \dot{v}_{C1} \\ \dot{i}_{L2} \\ \dot{v}_{C2} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & \frac{-1}{RC_1} & 0 & \frac{-1}{RC_1} \\ 0 & 0 & 0 & 0 \\ 0 & \frac{-1}{RC_2} & 0 & \frac{-1}{RC_2} \end{bmatrix} \qquad \dot{x} = A_{m2}x + B_{m2}u \Rightarrow \begin{bmatrix} \dot{i}_{L1} \\ \dot{v}_{C1} \\ \dot{i}_{L2} \\ \dot{v}_{C2} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & \frac{-1}{RC_1} & 0 & \frac{-1}{RC_1} \\ 0 & 0 & 0 & \frac{-1}{L_2} \\ 0 & \frac{-1}{RC_2} & \frac{-1}{RC_2} \end{bmatrix}$$

$$\times \begin{bmatrix} i_{L1} \\ v_{C1} \\ i_{L2} \\ v_{C2} \end{bmatrix} + \begin{bmatrix} \frac{1}{L_1} \\ \frac{1}{RC_1} \\ \frac{1}{L_2} \\ \frac{1}{RC_2} \end{bmatrix} v_{in}$$

(7)

$$y = C_{m2}x + D_{m2}u \Rightarrow [V_o] = \begin{bmatrix} 0 & 1 & 0 & 1 \end{bmatrix} \begin{bmatrix} i_{L1} \\ v_{C1} \\ i_{L2} \\ v_{C2} \end{bmatrix} + [-1]V_{in}$$

(8)

Fig. 3(c) shows the circuit during mode 3.  $L_2$  and  $C_1$  are charging while  $L_1$  and  $C_2$  are discharging. State representation of mode 3 is also likewise obtained. The averaged

large-signal model is obtained using the circuit averaging method in [35]. In FDBC  $L_1 = L_2 = L \& C_1 = C_2 = C$ , Therefore the averaged large-signal model of floating dual boost converter is,

$$\dot{x} = A_{ave}x + B_{ave}u \Rightarrow \begin{bmatrix} \dot{i}_{L1} \\ \dot{v}_{C1} \\ \dot{i}_{L2} \\ \dot{v}_{C2} \end{bmatrix} = \begin{bmatrix} 0 & -\overline{d}_1 & 0 & 0 \\ \overline{d}_1 & -2 & 0 & 0 \\ 0 & 0 & 0 & -\overline{d}_2 \\ 0 & 0 & \overline{d}_2 & -2 \\ 0 & 0 & \overline{d}_2 & -2 \end{bmatrix} \qquad \dot{x} = A\hat{x} + B\hat{y} = 0 \text{ and } (1/) \text{ in } (15) \text{ and } (16) \hat{x} \\ \dot{i}_{L1} \\ \dot{v}_{C1} \\ \dot{i}_{L2} \\ \dot{v}_{C1} \end{bmatrix} = A \begin{bmatrix} \hat{i}_{L1} \\ \hat{v}_{C1} \\ \hat{i}_{L2} \\ \hat{v}_{C1} \end{bmatrix}$$

$$\begin{bmatrix} i_{L1} \\ v_{C1} \\ i_{L2} \\ v^2 \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ \frac{1}{RC} \\ \frac{1}{L} \\ \frac{1}{RC} \end{bmatrix} v_{in}$$

(9)

$$y = C_{ave}x + D_{ave}u \Rightarrow [v_o] = \begin{bmatrix} 0 & 1 & 0 & 1 \end{bmatrix} \begin{bmatrix} i_{L1} \\ v_{C1} \\ i_{L2} \\ v_{C2} \end{bmatrix} + [-1]v_{in}$$

(10)

#### B. STEADY STATE VOLTAGE GAIN

Averaged large-signal model = Steady-state model + Small-signal model

$$x = X + \hat{x} \tag{11}$$

$$y = Y + \widehat{y} \tag{12}$$

where X and Y are the steady-state model  $\hat{x}$  and  $\hat{y}$  is a small signal model.

$$v_{in} = V_{in} + \widehat{v}_{in}; v_o = V_o + \widehat{v}_o; i_{L1} = I_{L1} + \widehat{i}_{L1}$$

$$i_{L2} = I_{L1} + \widehat{i}_{L1}; v_{C1} = V_{C1} + \widehat{v}_{C1}; v_{C2} = V_{C2} + \widehat{v}_{C2}$$

$$d_1 = D_1 + \widehat{d}_1; d_2 = D_2 + \widehat{d}_2$$

(13)

During steady-state x = X, y = Y and  $\dot{X} = AX +$ BY = 0, therefore the voltage gain is given as,

$$\Rightarrow \frac{V_o}{V_{in}} = \frac{1}{1 - D_1} + \frac{1}{1 - D_2} - 1 = \frac{1 + D}{1 - D}$$

(Where  $D_1 = D_2 = D$ ) (14)

The voltage gain of FDBC is given by (14).

## C. LINEARIZED SMALL SIGNAL MODEL

The small-signal model is obtained by substituting (13) in the averaged large-signal model ((9) and (10)).

$$\begin{bmatrix} \hat{i}_{L1} + I_{L1} \\ \hat{v}_{C1} + V_{C1} \\ \hat{i}_{L2} + I_{L2} \\ \hat{v}_{C2} + V_{C2} \end{bmatrix} = P \begin{bmatrix} \hat{i}_{L1} + I_{L1} \\ \hat{v}_{C1} + V_{C1} \\ \hat{i}_{L2} + I_{L1} \\ \hat{v}_{C2} + V_{C2} \end{bmatrix} + \begin{bmatrix} \frac{1}{L} \\ \frac{1}{RC} \\ \frac{1}{L} \\ \frac{1}{RC} \end{bmatrix} (\hat{v}_{in} + V_{in}) \quad (15)$$

where, (16) as shown at the bottom of the next page.

The multiplication of two small signals yields a minimal value, thus

$$\widehat{x}.\widehat{x} \text{ or } \widehat{y}.\widehat{y} \text{ or } \widehat{x}.\widehat{y} = 0$$

(17)

Using  $\dot{X} = AX + BY = 0$  and (17) in (15) and (16) results

$$\hat{x} = A\hat{x} + B_{1}\hat{u}_{1} + B_{2}\hat{u}_{2} \Rightarrow \begin{bmatrix} \dot{i}_{L1} \\ \dot{i}_{L1} \\ \dot{\hat{v}}_{C1} \\ \dot{i}_{L2} \\ \dot{\hat{v}}_{C1} \end{bmatrix} = A \begin{bmatrix} \hat{i}_{L1} \\ \hat{v}_{C1} \\ \dot{i}_{L2} \\ \dot{\hat{v}}_{C1} \end{bmatrix}$$

$$+ \begin{bmatrix} \frac{1}{L} \\ \frac{1}{RC} \\ \frac{1}{L} \\ \frac{1}{RC} \end{bmatrix} \hat{v}_{in} + \begin{bmatrix} \frac{V_{C1}}{L} \\ \frac{I_{L1}}{C} \\ \frac{V_{C2}}{L} \\ \frac{I_{L2}}{L} \end{bmatrix} \hat{d} \qquad (18)$$

$$\hat{y} = C\hat{x} + D_{1}\hat{u}_{1} + D_{2}\hat{u}_{2} \Rightarrow \hat{v}_{o} = \begin{bmatrix} 0 & 1 & 0 & 1 \end{bmatrix}$$

$$\times \begin{bmatrix} \hat{i}_{L1} \\ \hat{v}_{C1} \\ \hat{i}_{L2} \end{bmatrix} + [-1]\hat{v}_{in} + [0]\hat{d} \qquad (19)$$

The linearized small-signal model of FDBC is represented by (18) and (19). The voltage mode controller for the FDBC is designed based on this small-signal model of the FDBC.

**TABLE 1.** Components constraint of FDBC.

| Components | Iaverage             | $V_{max}$            |

|------------|----------------------|----------------------|

| Transistor | $(i_{in}$ - $i_o)/2$ | $v_{out}$ - $v_{in}$ |

| Diode      | $i_o$                | $v_{out}$ - $v_{in}$ |

| Inductor   | $(i_{in}$ - $i_o)/2$ |                      |

| Capacitor  | 0                    | $v_{out}$ - $v_{in}$ |

# D. PARAMETER DESIGN

In this topology, the switches have to handle lower current and voltage rating while the size of the input inductances and output capacitances decreases due to the interleaving concept. Table 1 shows the components constraint [35]. The inductor value is calculated using (20) [35],

$$L = \frac{2v_{in}}{\Delta i_{in} f_s} (D - 0.5) \tag{20}$$

The capacitor value is calculated using (21) [35],

$$C = \frac{2i_o}{\Delta v_o f_s} (D - 0.5) \tag{21}$$

#### E. TRANSFER FUNCTION

It is essential to derive the small-signal transfer function of the converter in order to design a controller for the same. The generalized transfer function equation is given as,

$$Y(s) = C(sI - A)^{-1}BU(s) + DU(S) \Rightarrow \frac{Y(s)}{U(s)}$$

$$= C(sI - A)^{-1}B + D \tag{22}$$

The transfer functions of FDBC are given as,

$$\frac{\widehat{v}_o(s)}{\widehat{v}_{in}(s)} = C(sI - A)^{-1}B_1 + D_1@\widehat{d} = 0$$

(23)

$$\frac{\widehat{v}_{o}(s)}{\widehat{v}_{in}(s)} = C(sI - A)^{-1}B_{1} + D_{1}@\widehat{d} = 0$$

$$\frac{\widehat{v}_{o}(s)}{\widehat{d}(s)} = C(sI - A)^{-1}B_{2} + D_{2}@\widehat{v}_{in} = 0$$

(23)

The input to output transfer function is represented by (23), and the control to output transfer function is represented by (24). Substituting the value of A,  $B_2$ , C,  $D_2$  from (18) and (19) in (24),

$$\frac{\widehat{v}_o(s)}{\widehat{d}(s)} = \frac{-3.467e^5s^3 + 4.469e^9s^2 + 2.433e^{11}s + 1.28e^{16}}{s^4 + 533.3s^3 + 5.685e^6s^2 + 1.497e^9s + 7.87e^{12}}$$

(25)

The control to output transfer function for the designed FDBC is represented by (25).

#### IV. CONTROLLER DESIGN

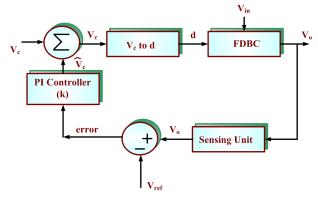

Proportional integral derivative (PID) controller is one of the most common control loop mechanism present and is extremely mainstream in industrial control systems. Generally, PI type controllers are used for the DC-DC converter. When incorporated with a DC-DC converter as a voltage controller, a PID controller attempts to reduce the error between the sensed output voltage and the reference voltage by outputting a control voltage that can adjust the duty cycle accordingly. PI controller is linear. However, DC-DC converters are non-linear. Therefore the design of a PI controller for a DC-DC converter is realized using a linearized small-signal model of the converter. Fig. 4 shows a closed-loop structure for the designed FDBC. In Fig. 4,  $V_{ref}$  is the steady-state output voltage;  $v_c$  is the control voltage that can adjust the duty cycle (d). It is evident from the figure that the PI controller addresses the small-signal disturbances arising at the output side and reduces it to zero by controlling the duty cycle.

Design of PI controller involves the calculation  $K_p$  and  $K_i$ . The most incorporated method to tune a PI controller is the Ziegler-Nichol's method as it does not involves complex modelling of the plant and also handles problems like

FIGURE 4. Closed loop system of FDBC.

FIGURE 5. Block diagram of a closed loop plant.

uncertainty, modelled dynamics, etc. The drawback of this method is that it is tedious and time-consuming as it is a trial and error method. Other techniques like bode plot and root locus techniques are also popular but require the mathematical modelling of the system. In the case of FDBC, the small-signal transfer function has a zero on the right-hand side of the S plane, making it a minimum phase system. Bode plot will work for non-minimum phase systems only, therefore, cannot be used to design a PI controller for FDBC.

Root locus technique was not very popular before the advent of powerful mathematical tools like MATLAB, Octave etc. The reason being, this method is very computationally intensive and requires complex mathematical calculations which increase the room for error. To understand this technique, let us take a general block diagram of a closed-loop plant, as shown in Fig. 5. Where  $G_p$  is a plant

$$P = \begin{bmatrix} \frac{0}{-(D_1 + \hat{d}_1)} & 0 & 0 \\ \frac{-(D_1 + \hat{d}_1)}{C} & \frac{-2}{RC} & 0 & 0 \\ 0 & 0 & \frac{0}{-(D_2 + \hat{d}_2)} & \frac{-2}{L} \\ 0 & 0 & \frac{-(D_2 + \hat{d}_2)}{L} \end{bmatrix}$$

$$\begin{bmatrix} \hat{v}_o + V_0 \end{bmatrix} = \begin{bmatrix} 0 & 1 & 0 & 1 \end{bmatrix} \begin{bmatrix} \hat{i}_{L1} + I_{L1} \\ \hat{v}_{C1} + V_{C1} \\ \hat{i}_{L2} + I_{L1} \\ \hat{v}_{C2} + V_{C2} \end{bmatrix} + [-1](\hat{v}_{in} + V_{in})$$

(16)

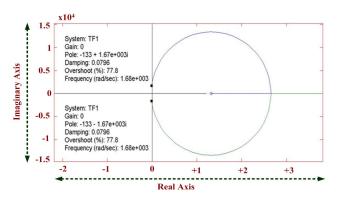

FIGURE 6. Root locus of the plant (FDBC).

transfer function, G is controller transfer function  $(KG_c)$ , K is controller gain,  $G_c$  is the pole-zero structure of the controller, H is the feedback transfer function.

$$TF_c = \frac{n_c}{d_c} = \frac{KG_cG_p}{1 + KG_cG_pH} \tag{26}$$

where  $TF_c$  is the closed-loop transfer function of the plant.  $G_c$  is given by,

$$G_c = \frac{(s+a)}{s}$$

$$a = \frac{K_i}{K_p}$$

$$K_p = K$$

(27)

(28)

$$a = \frac{K_i}{K_n} \tag{28}$$

$$K_p = K \tag{29}$$

$$K_i = aK (30)$$

Now to obtain the location of the pole of  $TF_c$ ,  $d_c$  has to be equated to zero,

$$1 + KG_cG_pH = 0 (31)$$

Now for a given value of  $G_c$ ,  $G_p$ , H, if we vary K from then the location of the poles of  $TF_c$  will vary accordingly. Values of  $K_p$  and  $K_i$  for the voltage controller of FDBC is obtained using the root locus technique. Followings are the steps to design the controller for FDBC using root locus technique.

The plant is the FDBC, and the transfer function of the plant from the control point of view will be the control voltage gain as in (25). The transfer function of the plant is, (32), as shown at the bottom of the next page.

Fig. 6 shows the root locus of  $G_p$ . Each pole location, shown and consists of two poles. The close loop transfer function  $(TF_c)$  is calculated using (23).  $G_p$  is the plant transfer function. Since unity feedback is considered in this case, therefore H is taken as unity. As the designer has the liberty to choose the pole location, the value of K and  $G_c$  are obtained accordingly. The closed-loop transfer function of FDBC for the chosen pole location is given as, (33) shown at the bottom of the next page.

The root locus of  $TF_c$  is shown in Fig. 7(a). The two poles marked in the figure are the poles which will be varied to obtain a desirable step response. It is seen that a fifth pole in introduced in  $TF_c$  when compared to the open-loop transfer function, this pole is added due to the integrator. It is also seen

FIGURE 7. Root locus and response (a) root locus of  $T_{C}$ , (b) step response of  $T_{C}$ , (c) root locus for the new  $T_{C}$ , (d) step response of the new  $TF_c$ .

FIGURE 8. Experimental setup of proposed work.

**TABLE 2.** Hardware specifications.

| FDBC Specifications                     |                               |  |  |  |

|-----------------------------------------|-------------------------------|--|--|--|

| Input Supply (PV array)                 | 140 Volts, 8 Amps (DC).       |  |  |  |

| Required Output (Max)                   | 495 Volts, 1.5 Amps (DC)      |  |  |  |

| Steady state duty cycle=56%             | 56%                           |  |  |  |

| Switch part number                      | IPA60R199CP (Mosfet)          |  |  |  |

| Diode part number                       | STTH806                       |  |  |  |

| Inductor rating/Inductor part number    | 560 μH/PCV-2-564-08L          |  |  |  |

| Capacitor rating                        | 120μF, 600V                   |  |  |  |

| VSI Specifications                      |                               |  |  |  |

| Input Supply(FDBC)                      | 495 Volts, 1.5 Amps (DC).     |  |  |  |

| Required Output (Max)                   | 400 Volts (rms), 1 Amps (rms) |  |  |  |

|                                         | (AC)                          |  |  |  |

| DC-Link Capacitor rating                | 1000uF, 500 Volts             |  |  |  |

| Switch part number                      | FGA25N120ANTD (IGBT)          |  |  |  |

| 3-phase Induction Motor (Squirrel Cage) |                               |  |  |  |

| Ratings                                 | 400 Volts, 1.8 Amps, 0.72 kW  |  |  |  |

| Frequency                               | 50 Hz                         |  |  |  |

| RPM                                     | 1415                          |  |  |  |

| PF                                      | 0.8                           |  |  |  |

in the root locus of  $TF_c$ . The step response of  $TF_c$  is obtained to validate the performance of the controller with the desired performance requirement. Fig. 7(b) shows the step response of  $TF_c$ .

Obtain new poles- From the step response, it can be inferred that the settling time of the controller is high. Thus we to move the poles from its initial position to a new position along the root locus. However, the pole position should be selected such that it is on the left-hand side of the s-plane. After multiple iterations, the desirable step response was obtained for FDBC.

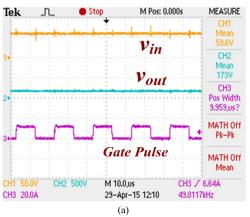

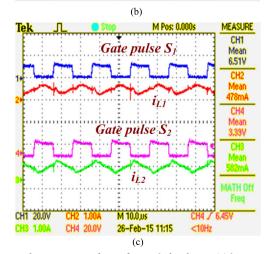

FIGURE 9. The output waveform of FDBC in hardware, (a) input voltage, output voltage and duty cycle, (b) input voltage, output voltage and voltage stress across switches, (c) inductor current.

The new closed-loop transfer function (TF<sub>C</sub>) is expressed as, (34) shown at the bottom of this page.

$$G_p = \frac{\widehat{v}_o(s)}{\widehat{d}(s)} = \frac{-3.467 \times 10^5 s^3 + 4.469 \times 10^9 s^2 + 2.433 \times 10^{11} s + 1.28 \times 10^{16}}{s^4 + 533.3s^3 + 5.685 \times 10^6 s^2 + 1.497 \times 10^9 s + 7.87 \times 10^{12}}$$

(32)

$$TF_c = \frac{-1.761s^4 + 2.252 \times 10^4 s^3 + 3.506 \times 10^6 s^2 + 6.5141 \times 10^{10}s + 6.501 \times 10^{12}}{s^5 + 531.4s^4 + 5.709 \times 10^6 s^3 + 1.501 \times 10^9 s^2 + 7.939 \times 10^{12}s + 6.501 \times 10^{12}}$$

$$TF_c = \frac{-14.59s^4 + 1.866 \times 10^5 s^3 + 2.905 \times 10^7 s^2 + 5.397 \times 10^{11}s + 5.387 \times 10^{13}}{s^5 + 518.7s^4 + 5.872 \times 10^6 s^3 + 1.526 \times 10^9 s^2 + 8.41 \times 10^{12}s + 5.3871 \times 10^{13}}$$

(34)

$$TF_c = \frac{-14.59s^4 + 1.866 \times 10^3 s^3 + 2.905 \times 10^7 s^2 + 5.397 \times 10^{11} s + 5.387 \times 10^{13}}{s^5 + 518.7s^4 + 5.872 \times 10^6 s^3 + 1.526 \times 10^9 s^2 + 8.41 \times 10^{12} s + 5.3871 \times 10^{13}}$$

(34)

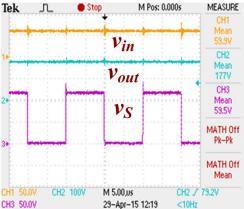

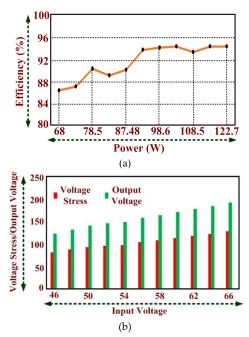

FIGURE 10. Performance graph of FDBC, (a) power VS efficiency curve, (b) bar graph representing output voltage and voltage stress of switches.

FIGURE 11. Output waveform of the entire system (a) output waveform of the PV voltage, FDBC voltage, VSI voltage and current, (b) motor output waveform.

Fig. 7(c) shows the root locus for the new  $TF_c$ . The new pole locations are highlighted in the root locus. Fig. 7(d)

FIGURE 12. Closed-loop output waveform of FDBC in hardware.

shows the step response of the new  $TF_c$ . It can interfere that the settling time of the system has reduced from 4.74 sec to 0.548 sec. Thus, the pole position can be varied accordingly to obtain the desired response. For the selected pole location, the value of K is obtained, and  $K_p$  (1.2) and  $K_i$  (0.25) are calculated using (29) and (30) for the voltage controller of FDBC. Realizing the above steps requires complex and long mathematical computation; thus, these steps are computed using MATLAB.

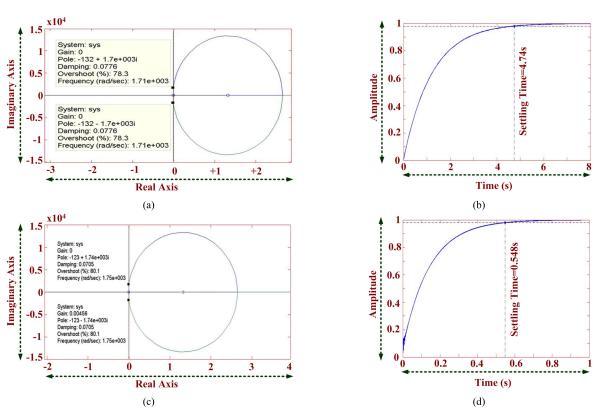

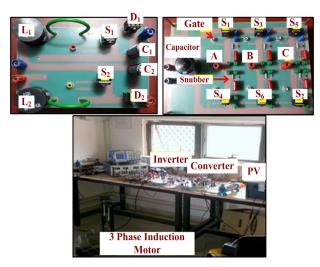

#### **V. HARDWARE SPECIFICATIONS**

The specifications of the setup are given in Table. 2, the Experimental setup is shown in Fig. 8. Fig. 9(a) shows the input voltage, output voltage and duty cycle and Fig. 9(b) shows the input voltage, output voltage and voltage stress across the switch of the FDBC in hardware. Fig. 9(c) highlights the inductor current for both the modules of FDBC. Fig. 10(a) shows the plot for input power VS efficiency for the fabricated FDBC. Fig. 10(b) shows the bar graph of output voltage and voltage stress across the switches for a specific input voltage. It is inferred from the plot that this topology offers low voltage stress across its switches.

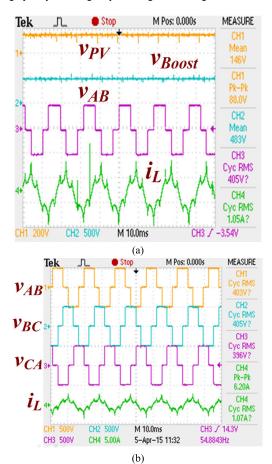

The output waveform of the entire system is shown in Fig. 11(a). It highlights the PV voltage, the output voltage of the FDBC, motor phase to phase voltage and motor phase current. Fig. 11(b) shows all the three-phase to phase voltages and the phase current of the motor. It is observed that  $V(line)_{rms} = 0.81V_{in}$ ,  $V_{in} = 483 \ V$ ,  $V(line)_{rms} = 483^{\circ}0.81 = 396 \ V$  for the  $180^{\circ}$  mode three-phase inverter used.

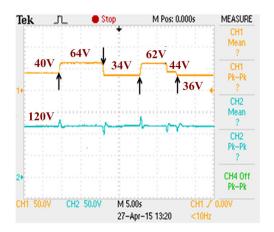

As discussed earlier, the PV output voltage as functions of time or instead function of irradiance, which is a function of time. The output voltage of the PV fed FDBC when driving a constant load has to be maintained constant despite the variations in PV voltage. The voltage mode controller is designed for this purpose. The hardware results of the closed-loop operation of FDBC are shown in Fig.12. The reference voltage is set at  $120V(V_{ref})$ . From Fig. 12 it is observed that the output is maintained constant at the reference value.

### VI. CONCLUSION

A PV based system using floating dual boost converter (FDBC), a three-phase voltage source inverter (VSI) and a three-phase squirrel cage induction motor (pump) are designed and implemented. It has been observed that the DC-link voltage obtained from the DC-DC converter varies with solar input voltage variation. So, it is essential to control either the DC-link voltage of the inverter or the output voltage of the inverter to obtain better performance. Hence, a voltage mode controller has been designed and implemented to keep the output of the DC-DC converter constant. The DC-DC converter is tested in closed-loop for different input voltage, and the performance of the voltage mode controller has been verified.

#### **REFERENCES**

- Z. A. Mahbub, M. Shahriar, M. Hossain, M. Islam, and M. Rahman, "Solar energy utilizing irrigation system for the rural areas of Bangladesh," *Global J. Research. Engg. Elect. Electron. Engg.*, vol. 13, no. 5, pp. 1–7, 2013.

- [2] M. Dursun and S. Ozden, "Application of solar powered automatic water pumping in turkey," *Int. J. Comput. Electr. Eng.*, vol. 4, no. 2, pp. 161–164, 2012.

- [3] J. Burney, L. Woltering, M. Burke, R. Naylor, and D. Pasternak, "Solar-powered drip irrigation enhances food security in the Sudano– Sahel," *Proc. Nat. Acad. Sci. USA*, vol. 107, no. 5, pp. 1848–1853, Feb. 2010

- [4] S. N. Singh, R. Jha, and M. K. Nandwana, "Optimal design of solar powered fuzzy control irrigation system for cultivation of green vegetable plants in rural India," in *Proc. 1st Int. Conf. Recent Adv. Inf. Technol.* (RAIT), Mar. 2012, pp. 877–882.

- [5] M. J. Case and E. E. Denny, "A novel approach to photovoltaic powered water pumping design," in *Proc. 13th Int. Power Electron. Motion Control Conf.*, Warsaw, Poland, Sep. 2008, pp. 1821–1825.

- [6] R. Sivapriyan, S. Umashankar, and P. Sanjeevikumar, "Direct-coupled permanent magnet DC motor-driven solar photovoltaic water pumping system—A literature review," in *Advances in Smart Grid and Renewable Energy* (Lecture Notes in Electrical Engineering), vol. 435. Singapore: Springer, 2018, pp. 307–314.

- [7] F. Blaabjerg, Z. Chen, and S. B. Kjaer, "Power electronics as efficient interface in dispersed power generation systems," *IEEE Trans. Power Electron.*, vol. 19, no. 5, pp. 1184–1194, Sep. 2004.

- [8] Y. Xue, L. Chang, S. B. Kjaer, J. Bordonau, and T. Shimizu, "Topologies of single-phase inverters for small distributed power generators: An overview," *IEEE Trans. Power Electron.*, vol. 19, no. 5, pp. 1305–1314, Sep. 2004.

- [9] R. Gonzalez, J. Lopez, P. Sanchis, and L. Parroyo, "Transformerless inverter for single-phase photovoltaic systems," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 693–697, Mar. 2007.

- [10] J. L. Duran-Gomez, E. Garcia-Cervantes, D. R. Lopez-Flores, P. N. Enjeti, and L. Palma, "Analysis and evaluation of a series-combined connected boost and buck-boost DC-DC converter for photovoltaic application," in *Proc. 21st Annu. IEEE Appl. Power Electron. Conf. Exposit. (APEC)*, Mar. 2006, pp. 979–985.

- [11] O. Abutbul, A. Gherlitz, Y. Berkovich, and A. Ioinovici, "Step-up switching-mode converter with high voltage gain using a switchedcapacitor circuit," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 50, no. 8, pp. 1098–1102, Aug. 2003.

- [12] L. Palma, M. H. Todorovic, and P. Enjeti, "A high gain transformer-less DC-DC converter for fuel-cell applications," in *Proc. IEEE PESC*, Jun. 2005, pp. 2514–2520.

- [13] R. Gules, L. L. Pfitscher, and L. C. Franco, "An interleaved boost DC-DC converter with large conversion ratio," in *Proc. IEEE Int. Symp. Ind. Electron.*, Jun. 2003, pp. 411–416.

- [14] L. C. Franco, L. L. Pfitscher, and R. Gules, "A new high static gain nonisolated DC-DC converter," in *Proc. IEEE* 34th Annu. Conf. Power Electron. Spec. (PESC), Jun. 2003, pp. 1367–1372.

- [15] A. Bhinge, N. Mohan, R. Giri, and R. Ayyanar, "Series-parallel connection of DC-DC converter modules with active sharing of input voltage and load current," in *Proc. APEC. 17th Annu. IEEE Appl. Power Electron. Conf. Exposit.*, Mar. 2002, pp. 648–653.

- [16] L.-H. Chen, J.-C. Hwang, S.-N. Yeh, and G.-C. Yu, "Analysis and design of four-leg fuel cell boost converter," in *Proc. 32nd Annu. Conf. IEEE Ind. Electron. (IECON)*, Nov. 2006, pp. 4285–4290.

- [17] K. C. Tseng and T. J. Liang, "Novel high-efficiency step-up converter," Inst. Elect. Eng. Proc.-Electr. Power Appl., vol. 151, no. 2, pp. 182–190, Mar. 2004.

- [18] C. Park, J. Yang, S. Choi, and S. Nam, "A transformer-less boost converter with high gain and low current ripple for fuel cell applications," in *Proc. Korean Inst. Power Electron. Conf.*, Jun. 2006, pp. 348–351.

- [19] C. Qiao and K. M. Smedley, "A general three-phase PFC controller for rectifiers with a parallel-connected dual boost topology," *IEEE Trans. Power Electron.*, vol. 17, no. 6, pp. 925–934, Nov. 2002.

- [20] B. Huang, I. Sadli, J.-P. Martin, and B. Davat, "Design of a high power, high step-up non-isolated DC-DC converter for fuel cell applications," in *Proc. IEEE Vehicle Power Propuls. Conf.*, Sep. 2006, pp. 1–6.

- [21] D. Bang Viet, Y. Lembeye, J. P. Ferrieux, J. Barbaroux, and Y. Avenas, "New high power-high ratio non isolated DC-DC boost converter for fuel cell applications," in *Proc. 37th IEEE Power Electron. Specialists Conf.*, 2006, pp. 1–7.

- [22] S. Choi, V. G. Agelidis, J. Yang, D. Coutellier, and P. Marabeas, "Analysis, design and experimental results of a floating-output interleaved-input boost-derived DC-DC high-gain transformer-less converter," *IET Power Electron.*, vol. 4, no. 1, pp. 168–180, Jan. 2011.

- [23] Y. Yang, H. Li, A. Aichhorn, J. Zheng, and M. Greenleaf, "Sizing strategy of distributed battery storage system with high penetration of photovoltaic for voltage regulation and peak load shaving," *IEEE Trans. Smart Grid*, vol. 5, no. 2, pp. 982–991, Mar. 2014.

- [24] S. Umashankar, V. Sridhar, P. Sanjeevikumar, F. Blaabjerg, J. B. Holm-Nielsen, and A. Dhafer, "A hybrid PV-battery system for ON-grid and OFF-grid applications-controller-in-loop simulation validation," *Energies J.*, vol. 13, no. 755, pp. 1–19, Feb. 2020.

- [25] G. Swaminathan, P. Sanjeevikumar, R. Varadarajan, U. Subramaniam, and L. Mihet-Popa, "Study and analysis of an intelligent microgrid energy management solution with distributed energy sources," *Energies*, vol. 10, no. 9, p. 1419, 2017.

- [26] J. V. M. Caracas, G. De Carvalho Farias, L. F. M. Teixeira, and L. A. de Souza Ribeiro, "Implementation of a high-efficiency, highlifetime, and low-cost converter for an autonomous photovoltaic water pumping system," *IEEE Trans. Ind. Appl.*, vol. 50, no. 1, pp. 631–641, Jan./Feb. 2014.

- [27] M. Kasper, D. Bortis, and J. W. Kolar, "Classification and comparative evaluation of PV panel-integrated DC–DC converter concepts," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2511–2526, May 2014.

- [28] L. Liu, H. Li, Y. Xue, and W. Liu, "Decoupled active and reactive power control for large-scale grid-connected photovoltaic systems using cascaded modular multilevel converters," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 176–187, Jan. 2015.

- [29] R. Zaitu, "Voltage mode boost converter small signal control loop analysis using the TPS61030," Texas Instrum., Dallas, TX, USA, Appl. Rep. SLVA274A, Jan. 2009. [Online]. Available: http://www.ti.com/ lit/an/slva274a/slva274a.pdf?ts=1590521419203

- [30] A. de la Villa Jaén, A. García-Santana, and D. E. Montoya-Andrade, "Maximizing output power of linear generators for wave energy conversion," *Int. Trans. Electr. Energy Syst.*, vol. 24, no. 6, pp. 875–890, Jun. 2014.

- [31] C. Muscas, "Assessment of electric power quality: Indices for identifying disturbing loads," Eur. Trans. Electr. Power, vol. 8, no. 4, pp. 287–292, Jul./Aug. 1998.

- [32] T. Lambert, P. Gilman, and P. Lilienthal, "Micropower system modeling with HOMER," in *Integration of Alternative Sources of Energy*, F. A. Farret and M. G. Simoes, Eds. Hoboken, NJ, USA: Wiley, 2006, pp. 379–418. [Online]. Available: https://www.homerenergy.com/documents/MicropowerSystemModelingWithHOMER.pdf

- [33] J. Abushnaf, A. Rassau, and W. Górnisiewicz, "Impact on electricity use of introducing time-of-use pricing to a multi-user home energy management system," *Int. Trans. Electr. Energy Syst.*, vol. 26, no. 5, pp. 993–1005, May 2016.

VOLUME 8, 2020 100913

- [34] H. Haghighat, "Energy loss reduction by optimal distributed generation allocation in distribution systems," *Int. Trans. Electr. Energy Syst.*, vol. 25, no. 9, pp. 1673–1684, Sep. 2015.

- [35] F. S. Garcia, J. A. Pomilio, and G. Spiazzi, "Modeling and control design of the interleaved double dual boost converter," *IEEE Trans. Ind. Electron.*, vol. 60, no. 8, pp. 3283–3290, Aug. 2013.

**SAPTARSHI DE** received the B.Tech. degree in electrical and electronics from the Vellore Institute of Technology (VIT), Vellore, and the M.Tech. degree in power electronics and drives from VIT, Chennai. He has extensively worked on drive controls, interleaved converters, and system design using real-time simulators. His research interests include controller design, machine learning, and artificial intelligence.

**O. V. GNANA SWATHIKA** (Member, IEEE) received the B.E. degree in electrical and electronics engineering from the University of Madras, Chennai, India, in 2000, the M.S. degree in electrical engineering from Wayne State University, Detroit, MI, USA, in 2004, and the Ph.D. degree in electrical engineering from Vellore Institute of Technology (VIT), Chennai, in 2017. She has also completed her postdoctoral research at the University of Moratuwa, Sri Lanka. Her current research

interests include microgrid protection and energy management systems.

UMASHANKAR SUBRAMANIAM (Senior Member, IEEE) is with the Renewable Energy Lab, College of Engineering, Prince Sultan University, Saudi Arabia, and has more than 15 years of teaching, research, and industrial Research and Development experience. Previously, he worked as an Associate Professor, the Head, and a Senior Research and Development and Senior Application Engineer in the fields of power electronics, renewable energy, and electrical drives with

the Vellore Institute of Technology (VIT), Vellore. Under his guidance, 24 master's degree students and more than 25 bachelor's degree students completed the senior design project work. Also, six Ph.D. scholars completed the doctoral thesis as a research associate. He has published more than 250 research articles in national and international journals and conferences. He is also involved in collaborative research projects with various international and national level organizations and research institutions. He has also authored/coauthored/contributed 12 books/chapters and 12 technical articles on power electronics applications in renewable energy and allied areas. He is a member of the IACSIT, IDES, and ISTE. He has taken charge as the Vice-Chair of the IEEE Madras Section and the Chair of IEEE student activities, from 2018 to 2019. He was an Executive Member, from 2014 to 2016, and the Vice-Chair of the IEEE MAS Young Professional, IEEE Madras Section, from 2017 to 2019. He received the Danfoss Innovator Award-Mentor, from 2014 to 2015 and from 2017 to 2018, and the Research Award from VIT, from 2013 to 2018. He received the INAE Summer Research Fellowship, in 2014. He is an Editor of *Heliyon* (Elsevier)

NILANJAN TEWARI (Member, IEEE) received the B.Tech. degree in electrical engineering from the West Bengal University of Technology, in 2009, and the M.Tech. degree in electrical engineering from the National Institute of Technology, Durgapur, in 2011. He is currently working as an Assistant Professor with the School of Electrical Engineering, Vellore Institute of Technology (VIT), Chennai, India. He is currently associated with the Smart Grid Laboratory, VIT. He has more

than eight years of teaching and research experience. His current research interests include dc-dc converters, renewable energy, and microgrids and smart grids applications. He is a member of the IEEE Power Electronics Society and the IEEE Smart Grid Community.

ANANTHA KRISHNAN VENKATESAN received the B.E. degree in electrical and electronics engineering from the University of Madras, India, in 2001, and the M.E. degree in power systems engineering from the College of Engineering, Anna University, Chennai, India, in 2006. He has more than 15 years of teaching and research experience. He is working as an Assistant Professor with the School of Electrical Engineering, Vellore Institute of Technology, Chennai. His current

research interests include microgrids, stability analysis in microgrids, neural networks, and fuzzy logic controller applications.

MAHAJAN SAGAR BHASKAR (Member, IEEE) received the bachelor's degree in electronics and telecommunication engineering from the University of Mumbai, Mumbai, India, in 2011, the master's degree in power electronics and drives from the Vellore Institute of Technology (VIT), India, in 2014, and the Ph.D. degree in electrical and electronics engineering from the University of Johannesburg, South Africa, in 2019. He worked as a Research Assistant with the Department of

Electrical Engineering, Qatar University, Doha, Qatar, from 2018 to 2019. He worked as a Research Student with the Power Quality Research Group, Department of Electrical Power Engineering, Universiti Tenaga Nasional (UNITEN), Private University, Kajang, Malaysia, from August to September 2017. He is currently with the Renewable Energy Lab, Department of Communications and Networks Engineering, College of Engineering, Prince Sultan University, Riyadh, Saudi Arabia. He has authored 100 plus scientific articles in particular reference to X-Y converter family, multilevel dc/dc and dc/ac converters, and high-gain converter, and received the Best Paper Research Paper Awards from the IEEE ICCPCT 2014, ETAEERE 2016 for a sponsored Lecture Notes in Electrical Engineering (Springer) book, IET CEAT 2016, and the IEEE CENCON 2019. He is a member of the IEEE Industrial Electronics, Power Electronics, Industrial Applications, and Power and Energy, Robotics and Automation, Vehicular Technology Societies, Young Professionals, and various IEEE Councils and Technical Communities. He received IEEE Access Award Reviewer of Month in Jan 2019 for a quick turnaround on reviews. He is a Reviewer Member of various international journals and conferences, including the IEEE and IET.

SANJEEVIKUMAR PADMANABAN (Senior Member, IEEE) received the bachelor's degree in electrical engineering from the University of Madras, Chennai, India, in 2002, the master's degree (Hons.) in electrical engineering from Pondicherry University, Puducherry, India, in 2006, and the Ph.D. degree in electrical engineering from the University of Bologna, Bologna, Italy, in 2012.

He was an Associate Professor with the Vellore Institute of Technology (VIT), from 2012 to 2013. In 2013, he joined the National Institute of Technology, India, as a Faculty Member. In 2014, he was invited as a Visiting Researcher at the Department of Electrical Engineering, Qatar University, Doha, Qatar, funded by the Qatar National Research Foundation (Government of Qatar). He continued his research activities with the Dublin Institute of Technology, Dublin, Ireland, in 2014. He was an Associate Professor with the Department of Electrical and Electronics Engineering, University of Johannesburg, Johannesburg, South Africa, from 2016 to 2018. Since 2018, he has been a Faculty Member of the Department of Energy Technology, Aalborg University, Esbjerg, Denmark. He has authored more than 300 scientific articles. He is a Fellow of the Institution of Engineers, India, the Institution of Electronics and Telecommunication Engineers, India, and the Institution of Engineering and Technology, U.K. He was the recipient of the Best Paper cum Most Excellence Research Paper Award from IET SEISCON 2013, IET CEAT 2016, the IEEE EECSI 2019, and the IEEE CENCON 2019, and five Best Paper Awards from ETAEERE 2016 for a sponsored Lecture Notes in Electrical Engineering book (Springer). He is an Editor/Associate Editor/Editorial Board Member of refereed journals, in particular the IEEE Systems Journal, the IEEE TRANSACTION ON INDUSTRY APPLICATIONS, IEEE ACCESS, IET Power Electronics, and the International Transactions on Electrical Energy Systems journal (Wiley), and the Subject Editor of the IET Renewable Power Generation, IET Generation, Transmission, and Distribution, and FACTS journal (Canada).

**ZBIGNIEW LEONOWICZ** (Senior Member, IEEE) received the M.Sc. and Ph.D. degrees in electrical engineering from the Wroclaw University of Science and Technology, Wroclaw, Poland, in 1997 and 2001, respectively, and the Habilitation degree from the Bialystok University of Technology, Bialystok, Poland, in 2012. In 2019, he received Professor titles in Poland and in Czech Republic. Since 1997, he has been with the Department of Electrical Engineering, Wroclaw University

sity of Science and Technology, where he is currently a Full Professor and the Head of the Chair of Electrical Engineering Fundamentals. He has authored over 180 research articles and received numerous recognitions for his activity as a Reviewer. His current research interests include power quality, control, and protection of power systems, renewables, industrial ecology, and the applications of advanced signal processing methods in power systems.

**MASSIMO MITOLO** (Fellow, IEEE) received the Ph.D. degree in electrical engineering from the University of Napoli "Federico II," Italy.

He is currently a Full Professor of electrical engineering with the Irvine Valley College, Irvine, CA, USA, and also a Senior Consultant in the matter of failure analysis and electrical safety with Engineering Systems Inc., ESi. He has authored over 140 journal papers and books, including the "Electrical Safety of Low-Voltage Systems"

(McGraw-Hill), the "Laboratory Manual for Introduction to Electronics: A Basic Approach" (Pearson), and the "Analysis of Grounding and Bonding Systems" (CRC Press). His research interests include the analysis and grounding of power systems and electrical safety engineering.

Dr. Mitolo is a Fellow of the IEEE in recognition "for contributions to the electrical safety of low-voltage systems," and a Fellow of the Institution of Engineering and Technology (IET) of London. He is a registered Professional Engineer in the state of California and in Italy. He is active within the Industrial and Commercial Power Systems Department of the IEEE Industry Applications Society (IAS) in numerous committees and working groups. He is a recipient of the James E. Ballinger Engineer of the Year 2013 Award from the Orange County Engineering Council. He has received numerous recognitions and best paper awards, among which are the IEEE "Ralph H. Lee I&CPS Department Prize Paper Award," the IEEE "I&CPS 2015 Department Achievement Award," and the IEEE Region 6 "2015 Outstanding Engineer Award." He currently serves both as an Associate Editor and a Guest Editor for the IEEE IAS TRANSACTIONS. He is currently the Deputy Editor-in-Chief of the IEEE TRANSACTIONS on Industry Applications.

0 0 0

VOLUME 8, 2020 100915