# **Aalborg Universitet**

# Effect of short-circuit degradation on the remaining useful lifetime of SiC MOSFETs and its failure analysis

Du, He; Letz, Sebastian; Baker, Nick; Goetz, Thomas; Iannuzzo, Francesco; Schletz, **Andreas**

Published in: Microelectronics Reliability

DOI (link to publication from Publisher): 10.1016/j.microrel.2020.113784

Creative Commons License CC BY-NC-ND 4.0

Publication date: 2020

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Du, H., Letz, S., Baker, N., Goetz, T., Iannuzzo, F., & Schletz, A. (2020). Effect of short-circuit degradation on the remaining useful lifetime of SiC MOSFETs and its failure analysis. *Microelectronics Reliability*, 114, 1-5. Article 113784. https://doi.org/10.1016/j.microrel.2020.113784

# **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

# Effect of short-circuit degradation on the remaining useful lifetime of SiC MOSFETs and its failure analysis

H. Du <sup>a,\*</sup>, S. Letz <sup>b</sup>, N. Baker <sup>a</sup>, T. Goetz <sup>b</sup>, F. Iannuzzo <sup>a</sup>, A. Schletz <sup>b</sup>

<sup>a</sup> Department of Energy Technology, Aalborg University, Denmark <sup>b</sup> Fraunhofer Institute for Integrated Systems and Device Technology, Erlangen, Germany

Abstract — When the SiC MOSFET works in the normal operating conditions, its remaining useful lifetime used to be estimated based on the monitored parameters and the lifetime model derived from accelerated tests. In this case, the degradation caused by abnormal events has not been considered. Therefore, it makes sense to investigate the effect of short-circuit degradation on the remaining useful lifetime of SiC MOSFETs. A different number of repetitive short-circuit events have been introduced into the accelerated power cycling tests to assess the impact. The experimental results indicate a gate degradation with the increasing number of short-circuit repetitions, which leads to higher conduction loss and earlier failure. Further failure analysis is achieved by performing lock-in thermography, scanning electron microscopy, and focused ion beam.

# 1. Introduction

Silicon Carbide (SiC) MOSFETs have widely emerged in the market, offering higher efficiency and power density [1]. To meet the safety requirements, the short-circuit reliability of SiC MOSFETs is becoming a critical concern as it endures a high voltage, high current, and high transient junction temperature at the same time [2]. Many efforts have been devoted to short-circuit robustness, revealing a shorter short-circuit withstand time [3]. To avoid device destruction induced by short-circuit events, faster desaturation fault detection and short circuit protection has been proposed, which allows the SiC MOSFET to withstand many times of low-energy non-destructive short-circuit events during its whole lifetime [4].

Through different accelerated ageing tests (such as power cycling, temperature cycling), the lifetime models of SiC MOSFETs can be obtained. Then, together with condition monitoring parameters (for example, on-state drain-source voltage, junction-case thermal impedance), the Remaining Useful Lifetime (RUL) of the devices can be estimated under normal operating conditions [5]. However, it is worth noting that the impact of short-circuit events on the RUL was neglected before. By taking into account this aspect, it will be possible to achieve a more accurate RUL estimation.

This paper aims to investigate the effect of short-circuit degradation on the RUL in power cycling tests by introducing a different number of short-circuit events. In Section 2, the test approach and platforms are described. The experimental results are presented in Section 3. Then Section 4 presents failure analysis and further discussion. Finally, concluding remarks are given.

# 2. Mixed power cycling tests with short-circuit stress

Power cycling test tends to detect the bond wires lift-off, which is a common failure mode at the packaging level and it is caused by the Coefficient of Thermal Expansion (CTE) mismatch between the bond wire and SiC material. In order to identify the ageing process in the tests, the on-state drain-source voltage ( $V_{\rm DS,on}$ ), consists of the chip and package-related voltage, is used as an ageing indicator [6]. Hence, the power

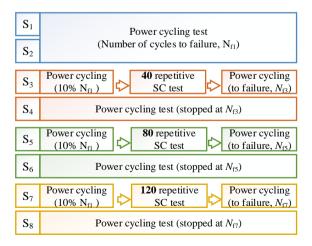

cycling tests combined with a different number of repetitive short-circuit tests are performed to assess the short-circuit degradation effect on the  $V_{\rm DS,on}$  and the number of cycles to failure ( $N_{\rm f}$ ). The Device Under Test (DUT) is a commercial 1000-V/ 22-A SiC MOSFET with 3<sup>rd</sup> planar technology from Wolfspeed. The experimental approach can be seen in Fig. 1.

First of all, fresh devices with matched static characteristics are chose and named from  $S_1$  to  $S_8$ . A power cycling test without any short-circuit stress is performed for device S<sub>1</sub> and S<sub>2</sub> to understand its end of the lifetime. The number of cycles to failure  $(N_{f1})$  is recorded when either device first shows an extremely high  $V_{\rm DS,on}$  or open circuit failure mode to mitigate the impact of the deviation. Then the number of cycles equal to  $10\% \cdot N_{\rm fl}$  is selected as the point to introduce short-circuit events since the devices remain consistent characteristics at the early of the test and the impact of power cycling ageing on the shortcircuit performance is negligible [7]. Thereafter, another three sets of power cycling tests are run. For the device  $S_3$ ,  $S_5$ , and  $S_7$ , a different number of repetitive short circuits (40, 80, and 120) are applied at the selected point  $(10\% \cdot N_{\rm fl})$ , respectively. To ensure the power cycling tests keep the same setting conditions after  $10\% \cdot N_{f1}$ , the device  $S_4$ ,  $S_6$  and  $S_8$  are run without short

Fig. 1. Experimental approach of the power cycling test combined with different numbers of short-circuit repetitions.

circuit stress as a reference.

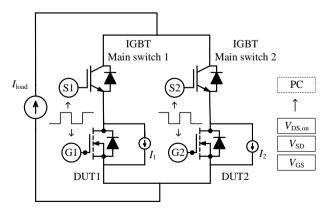

During DC-based power cycling tests, the devices are heated periodically by conduction power loss ( $P_{con}$ ) and cooled down when the devices turn off. Their junction temperature conditions are controlled by adjusting turn-on and turn-off time duration  $(t_{\rm on}/t_{\rm off})$ , constant load current  $(I_{\rm load})$ , together with controllable heater and forced air cooling system. The schematic of the power cycling test is shown in Fig. 2. A DC source supply (DELTA SM 70-45 D) provides the required  $I_{load}$  and two main switches (1200-V 85-A IGBTs from IXYS) operate in a complementary mode with 0.5 ms overlap during the test. Each DUT, in series with one of the main switches, has the same control signal and separated gate driver (CREE CRD-001) with adjustable output voltage. The ARM microcontroller development board (MBED-LPC1768) generates control signals and streams real-time test data to PC. The gate-source voltage  $(V_{\rm GS})$  is monitored with the oscilloscope during the whole test.

During the conduction period of the DUT, its  $V_{\rm DS,on}$  is recorded as an ageing indicator. When the DUT turns off, the body diode's voltage drop  $(V_{\rm SD})$  is measured by injecting a small current  $(I_1 = I_2 = 20 \text{ mA})$ , which makes the impact of package-related ageing on the  $V_{\rm SD}$  negligible. Since the relationship between the  $V_{\rm SD}$  and junction temperature  $(T_{\rm j})$  does not change over ageing, the  $V_{\rm SD}$  can be used to estimate the  $T_{\rm j}$  [8]. It should be noted that the  $V_{\rm SD}$  is affected by the off-state  $V_{\rm GS}$  value as the MOS-channel still conducts current at zero gate bias or small negative bias [9]. Thus, a negative  $V_{\rm GS}$  of -4 V is applied at the initial calibration stage to enable an accurate estimation.

The power cycling test condition is selected as below. By adjusting the  $I_{\rm load}$  and cooling system, the initial maximum junction temperature ( $T_{\rm j\_max}$ ) and minimum junction temperature ( $T_{\rm j\_min}$ ) are set to 130 °C and 70 °C, respectively. Then the  $I_{\rm load}$  and the case temperature controlled by the cooling system are kept constant during the test. The  $t_{\rm on}/t_{\rm off}$  is 2 s/2 s and the gate resistance is equal to 20  $\Omega$ . The  $V_{\rm GS}$  of the device  $S_1$ ,  $S_3$ ,  $S_5$ , and  $S_7$  is set to +15 V/-4 V. For the other devices (i.e.  $S_2$ ,  $S_4$ ,  $S_6$ , and  $S_8$ ), a slight lower  $V_{\rm GS}$  is used to ensure the same junction temperature condition.

The repetitive short circuit events are performed with a Non-Destructive Tester, which has been described in [10]. To prevent thermal runaway failure, the applied short-circuit energy must be lower than the critical energy of the device ( $E_{\rm SCmax}$ ). Therefore, the short-circuit condition at 25 °C case temperature is selected based on previous work in [11], whose  $E_{\rm SCmax}$  is 0.15

Fig. 2. Schematic of DC-based power cycling test.

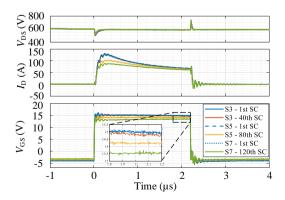

J. The short-circuit pulse time duration ( $t_{SC}$ ) is set to 2.2  $\mu$ s since its maximum short-circuit withstanding time ( $t_{SC\_max}$ ) is 4  $\mu$ s (i.e.  $t_{SC}/t_{SC\_max} = 0.55$ ). The drain-source voltage ( $V_{DS}$ ) is 600 V and the  $V_{GS}$  keeps +15 V/ -4 V with 20  $\Omega$  external gate resistance. The case temperature is 25 °C. During each short circuit repetition, the waveform of drain current waveform ( $I_D$ ),  $V_{DS}$  and  $V_{GS}$  are measured with the oscilloscope.

## 3. Experimental results

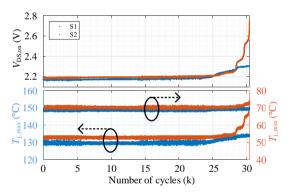

Fig. 3 shows the evolution of the on-state voltage ( $V_{\rm DS,on}$ ),  $T_{\rm j\_max}$  and  $T_{\rm j\_min}$  with the number of cycles for the device S<sub>1</sub> and S<sub>2</sub>. The  $V_{\rm DS,on}$  of both devices have similar increasing trend till 28 k cycles and the device S<sub>2</sub> failed after 30.4 k cycles, which is regarded as the number of cycles to failure without short circuit stress ( $N_{\rm f1}$ ). Therefore, the power cycling tests for the device S<sub>3</sub>, S<sub>5</sub>, and S<sub>7</sub> stop after 3 k cycles ( $10\% \cdot N_{\rm f1}$ ) and at that point, different number of short-circuit repetitions (40, 80 and 120 times) are performed, respectively.

Fig. 4 presents the first and last time short circuit waveforms of the device  $S_3$ ,  $S_5$ , and  $S_7$ , including  $V_{DS}$ ,  $I_D$  and  $V_{GS}$ . Comparing to the same results at the first short-circuit repetition, the last repetition shows an obvious difference, reflecting on the lower  $V_{GS}$  and peak  $I_D$ .

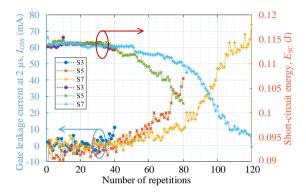

The  $V_{\rm GS}$  at end of the short-circuit time duration, i.e. t=2  $\mu s$ , can be used as an indicator to evaluate the short-circuit degradation process [11]. Then the gate leakage current at 2  $\mu s$  ( $I_{\rm GSS}$ ) during the short-circuit test can be estimated by the voltage drop on the external gate resistor (20  $\Omega$ ). The left axis of Fig. 5

Fig. 3. Power cycling test for device  $S_1$  and  $S_2$  without short circuit stress.

Fig. 4. First and the last repetition short circuit waveform ( $V_{DS}$ ,  $I_{D}$  and  $V_{GS}$ ) of the device  $S_3$ ,  $S_5$  and  $S_7$ .

shows the increasing  $I_{\rm GSS}$  with the number of repetitions. The short-circuit energy  $(E_{\rm SC})$  of each repetition is also calculated and shown in the right axis of Fig. 5. All devices keep nearly the same  $E_{\rm SC}$  (0.114 J) at the beginning, which is below the critical energy (i.e.  $E_{\rm SC}/E_{\rm SCmax}=0.76$ ). It shows that the different degrees of degradation is mainly affected by the number of repetitions rather than the first time or initial  $E_{\rm SC}$ . These results can be explained by gate degradation, which includes the damages in gate oxide or SiO<sub>2</sub> dielectric [12].

After short-circuit events, the relationship between  $V_{\rm SD}$  and  $T_{\rm j}$  is calibrated again. Among them, the devices without short circuit stress (i.e. S<sub>4</sub>, S<sub>6</sub> and S<sub>8</sub>) keep the same values as before. Because of the increased  $I_{\rm GSS}$ , the device after short circuit stress

Fig. 5. Estimated gate leakage current at 2  $\mu$ s ( $I_{GSS}$ ) increases and short-circuit energy ( $E_{SC}$ ) decreases with the number of short-circuit repetitions.

Fig. 6. On-state drain-source voltage ( $V_{DS,on}$ ) variation with the number of cycles for the devices from  $S_3$  to  $S_8$ .

Fig. 7. Junction temperature swing  $(\Delta T_j)$  variation with the number of cycles for the devices from S<sub>3</sub> to S<sub>8</sub>.

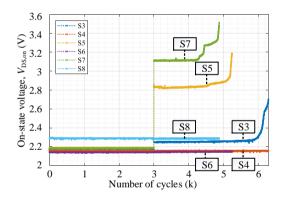

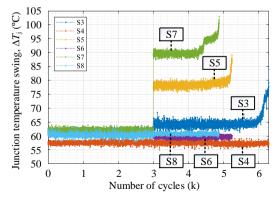

(i.e.  $S_3$ ,  $S_5$  and  $S_7$ ) is set to -4 V  $V_{GS}$  again and a clear variation appears. Thereafter, the power cycling tests continue to run until failure as mentioned above in Section 2. Fig. 6 shows the  $V_{DS,on}$  evolution of the device  $S_3$  -  $S_8$ . All three reference devices without short circuit stress remain the same  $V_{DS,on}$  as before while the other three devices with short-circuit stress show increased value. Due to the non-negligible  $I_{GSS}$ , the oscilloscopemeasured  $V_{GS}$  of the device  $S_3$ ,  $S_5$  and  $S_7$  drop from 15 V to 14.2 V, 11.8 V and 11.1 V, respectively even though the positive output voltage of their gate drivers still keep 15 V. This factor mainly contributes to the higher  $V_{DS,on}$  and higher conduction loss, which results in a higher junction temperature swing further as shown in Fig. 7. This implication of short-circuit stress on the power cycling condition has been explained in [13].

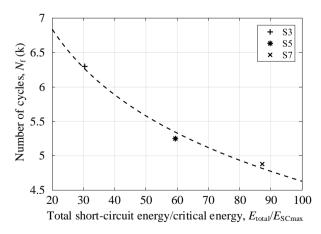

With the higher junction temperature swing ( $\Delta T_j$ ), the device S<sub>3</sub>, S<sub>5</sub> and S<sub>7</sub> fail after 6.3 k, 5.25 k and 4.88 k cycles, separately while the other three reference devices show stable  $V_{\rm DS,on}$  and  $\Delta T_j$  until the tests are stopped. This result indicates that the number of cycles to failure is affected by the number of short-circuit repetitions (i.e. the degree of gate degradation). Fig. 8 presents the relationship between the number of cycles to failure and the quotient of total short-circuit energy and critical energy ( $E_{\rm total}/E_{\rm SCmax}$ ), and it can be fitted as the dotted line. Therefore, if several times of non-destructive short circuits happen in the applications, a revised RUL estimation based on the short-circuit energy and updated  $T_i$  might be needed.

### 4. Failure analysis and discussion

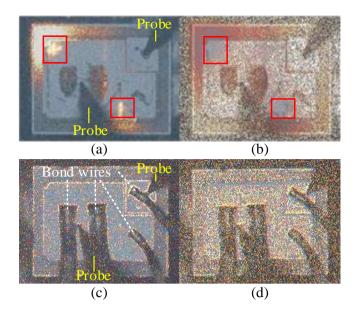

To obtain further insight into the effect of short-circuit degradation, deeper failure analysis is achieved for the devices  $S_5$  and  $S_6$ . First, the devices are de-capsulated by laser ablation and high-temperature acid etching to remove the moulded material and then the ultrasonic cleaning is used for both devices. The bonding wires of the device  $S_5$  are found to have been removed from the top side of the chip, as shown in Fig. 9 (a) and (b). However, the Al wires of the device  $S_6$  remain bonded on the chip surface in Fig. 9 (c) and (d). A likely explanation may be that the bonding wires of the device  $S_5$  has already lifted off before de-capsulation, which agrees with its open circuit failure mode. On the other hand, the  $V_{DS}$  of the

Fig. 8. Relationship between the number of cycles to failure ( $N_f$ ) and the quotient of total short-circuit energy and its critical energy ( $E_{\text{total}}/E_{\text{SCmax}}$ ).

Fig. 9. Lock-in thermography with applied gate-source voltages: (a) amplitude and (b) phase image of the device  $S_5$ ; (c) amplitude and device  $S_6$  keeps stable, indicating well connection and negligible impact of de-capsulation process and ultrasonic cleaning on the bonding wires.

After that, the lock-in thermography measurements are performed to locate the damaged areas. The high-resolution lock-in thermography system from DCG Systems is equipped with a high-performance InSb 320 M infrared camera, which makes it possible to detect low power dissipation. A periodical square-pulse voltage is applied on the gate pad through probe while the drain and source are short connected to the ground. To avoid introducing artificial damage, the gate leakage current limitation is set.

With respect to the device  $S_5$ , the measured gate leakage current achieves at 1 mA when the  $V_{\rm GS}$  is equal to 0.84 V and two degraded regions have been observed as shown in Fig. 9 (a) and (b); the reason why these two regions are located in the periphery needs to be further studied. In contrast, the device  $S_6$  shows negligible gate leakage current ( $I_{\rm GSS}=0.17$  nA) when the  $V_{\rm GS}$  is applied to 15 V, which indicates no gate damage as shown in Fig. 9 (c) and (d).

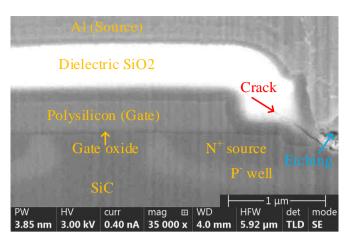

Thereafter, a Focused Ion Beam (FIB) at the degraded locations of the device  $S_5$  is performed by the ThermoScientific Helios G4 PFIB UXe system to obtain the vertical cross-section. Fig. 10 shows the magnified Scanning Electron Microscopy (SEM) image and a dielectric  $SiO_2$  crack exists in one of the cells. This crack may be caused by an etching artefact close to it. On the other hand, whether there is a damage in the gate oxide between the polysilicon and the SiC substrate, whose thickness is around 50 nm, cannot be seen, unfortunately, since the FIB limits SEM resolution.

However, this dielectric  $SiO_2$  crack might have reached the polysilicon gate along with the direction vertical to the figure. This kind of crack is also found in [12] [14] and well supported in [15] with the Energy-Dispersive Spectroscopy (EDS) results, which indicates that the thermal stress on  $SiO_2$  dielectric causes the crack. Then, a conductive path between the polysilicon gate and the Al source can be built and leads to a significant  $I_{QSS}$ .

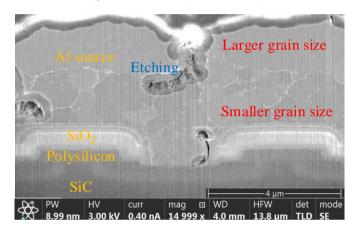

Besides, a large difference in the Al grains size between the top and bottom locations is observed in Fig. 11. This

Fig. 10. Magnified cross-sectional SEM image of the damaged cell from the device S<sub>5</sub>. The red arrow identifies the crack.

inhomogeneity of Al grains size is similar to the Al metallization reconstruction in [16] and it might come from the vertical temperature gradient, which in turn induces microstructural evolution along the temperature gradient. Further research is needed to investigate whether it comes from short-circuit stress or power cycling stress. The degradation of Al metallization, which is characterized by the grain size reduction, can be explained by the dislocation-based plasticity in [17]. Then the multiplication of grain boundaries and even the appearance of intergranular cracks may cause an increase of Al metallization resistance.

### 5. Conclusions

This paper investigates the effect of short-circuit degradation on the RUL of the 1000-V 22-A SiC MOSFETs with  $3^{\rm rd}$  planar technology from Wolfspeed. The experimental results of mixed power cycling tests show that a larger number of short-circuit repetitions induce higher  $I_{\rm GSS}$ , which leads to the higher  $V_{\rm DS,on}$  and  $P_{\rm con}$ . Owing to the higher  $\Delta T_{\rm j}$ , the device fails much earlier and further failure analysis still demonstrates the bonding wires lift-off, which is in agreement with the opencircuit failure mode. After the FIB, a dielectric SiO<sub>2</sub> crack is observed with SEM. This may form a conductive path between the gate and source, which results in the higher  $I_{\rm GSS}$ . The inhomogeneity of Al grains size might be caused by a strong vertical temperature gradient during the tests and attributed to the dislocation-based plasticity.

# Acknowledgements

This work is funded by the Advanced Power Electronic Technology and Tools (APETT) project from the Innovation Fund Denmark.

#### References

- [1] X. She, A. Q. Huang, B. Ozpineci, Review of silicon carbide power devices and their applications, IEEE Trans. Ind. Electron., vol. 64, no. 10, pp. 8193–8205, 2017.

- [2] Z. Wang, X. Shi, L. M. Tolbert, F. Wang, Z. Liang, D. Costinett, B. J. Blalock, Temperature-dependent short-circuit capability of silicon carbide power MOSFETs, IEEE Trans. Power Electron., vol. 31, no. 2, pp. 1555–1566, 2016.

- [3] J. Sun, J. Wei, Z. Zheng, Y. Wang, K. J. Chen, Short circuit capability and short circuit induced Vth instability of a 1.2kV SiC power MOSFET, IEEE J. Emerg. Sel. Top. Power Electron., vol. 7, no. 3, pp. 1539–1546, 2019.

- [4] D. P. Sadik, J. Colmenares, G. Tolstoy, D. Peftitsis, M. Bakowski, J. Rabkowski, H. P. Nee, Short-circuit protection circuits for silicon-carbide power transistors, IEEE Trans. Ind. Electron., vol. 63, no. 4, pp. 1995–2004, 2016.

- [5] Z. Ni, X. Lyu, O. P. Yadav, B. N. Singh, S. Zheng, D. Cao, Overview of real-time lifetime prediction and extension for SiC power converters, IEEE Trans. Power Electron., vol. 35, no. 8, pp. 7765–7794, 2019.

- [6] P. Nayak, S. K. Pramanick, K. Rajashekara, A high-temperature gate driver for silicon carbide MOSFETs, IEEE Trans. Ind. Electron., vol. 65, no. 3, pp. 1955–1964, 2018.

- [7] P. Diaz Reigosa, H. Luo, F. Iannuzzo, Implications of ageing through power cycling on the short circuit robustness of 1.2-kV SiC MOSFETs, IEEE Trans. Power Electron., vol. 34, no. 11, pp. 11182–11190, 2019.

- [8] F. Yang, E. Ugur, B. Akin, G. Wang, Design methodology of DC power cycling test setup for SiC MOSFETs, IEEE J. Emerg. Sel. Top. Power Electron., 2019.

- [9] J. A. O. Gonzalez, O. Alatise, A novel non-intrusive technique for BTI characterization in SiC MOSFETs, IEEE Trans. Power Electron., vol. 34, no. 6, pp. 5737–5747, 2019.

- [10] P. D. Reigosa, F. Iannuzzo, H. Luo, F. Blaabjerg, A short-circuit safe operation area identification criterion for SiC MOSFET power modules, IEEE Trans. Ind. Appl., vol. 53, no. 3, pp. 2880–2887, 2017.

- [11] H. Du, P. D. Reigosa, L. Ceccarelli, F. Iannuzzo, Impact of repetitive short-circuit tests on the normal operation of SiC MOSFETs considering case temperature influence, IEEE J. Emerg. Sel. Top. Power Electron., vol. 8, no. 1, pp. 195–205, 2020.

- [12] F. Boige, F. Richardeau, D. Trémouilles, S. Lefebvre, G. Guibaud, Investigation on damaged planar-oxide of 1200 V SiC power MOSFETs in non-destructive short-circuit operation, Microelectron. Reliab., vol. 76–77, pp. 500–506, 2017.

- [13] H. Du, L. Ceccarelli, F. Iannuzzo, P. D. Reigosa, Implications of short-circuit events on power cycling of 1.2-kV/20-A SiC MOSFET power modules, Microelectron. Reliab., vol. 100– 101, pp. 113373, 2019.

- [14] J. Liu, G. Zhang, B. Wang, W. Li, J. Wang, Gate failure physics of SiC MOSFETs under short-circuit stress, IEEE Electron Device Lett., vol. 41, no. 1, pp. 103–106, 2020.

- [15] P. D. Reigosa, F. Iannuzzo, L. Ceccarelli, Effect of short-circuit stress on the degradation of the SiO2 dielectric in SiC power MOSFETs, Microelectron. Reliab., vol. 88–90, pp. 577–583, 2018.

- [16] R. Ruffilli, M. Berkani, P. Dupuy, S. Lefebvre, Y. Weber, M. Legros, In-depth investigation of metallization aging in power MOSFETs, Microelectron. Reliab., vol. 55, no. 9–10, pp. 1966–1970, 2015.

- [17] D. Martineau, T. Mazeaud, M. Legros, P. Dupuy, C. Levade, Characterization of alterations on power MOSFET devices under extreme electro-thermal fatigue, Microelectron. Reliab., vol. 50, no. 9–11, pp. 1768–1772, 2010.