# **Aalborg Universitet**

# A Simple Multilevel Space Vector Modulation Technique and MATLAB System Generator Built FPGA Implementation for Three-Level Neutral-Point Clamped Inverter

Madasamy, P.; Pongiannan, R. K.; Ravichandran, Sekar; Padmanaban, Sanjeevikumar; Chokkalingam, Bharatiraja; Hossain, Eklas; Adedayo, Yusuff

Published in: **Energies**

DOI (link to publication from Publisher): 10.3390/en12224332

Creative Commons License CC BY 4.0

Publication date: 2019

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Madasamy, P., Pongiannan, R. K., Ravichandran, S., Padmanaban, S., Chokkalingam, B., Hossain, E., & Adedayo, Y. (2019). A Simple Multilevel Space Vector Modulation Technique and MATLAB System Generator Built FPGA Implementation for Three-Level Neutral-Point Clamped Inverter. Energies, 12(22). https://doi.org/10.3390/en12224332

### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

Article

# A Simple Multilevel Space Vector Modulation Technique and MATLAB System Generator Built FPGA Implementation for Three-Level Neutral-Point Clamped Inverter

P. Madasamy <sup>1</sup>, R. K. Pongiannan <sup>2</sup>, Sekar Ravichandran <sup>3</sup>,\*, Sanjeevikumar Padmanaban <sup>4</sup>, Bharatiraja Chokkalingam <sup>2,5</sup>,\*, Eklas Hossain <sup>6</sup> and Yusuff Adedayo <sup>5</sup>

- Department of Electrical and Electronics Engineering, Alagappa Chettiar college of Engineering and Technology, Karaikudi 630003, India; mjasmitha0612@gmail.com

- Department of Electrical and Electronics Engineering, SRM Institute of Science and Technology, Chennai 603203, India; rkp.annan@gmail.com

- Department of Electrical and Electronics Engineering, Sreenidhi Institute of Science and Technology, Hyderabad, Telangana 501301, India

- Department of Energy Technology, Aalborg University, 6700 Esbjerg, Denmark; san@et.aau.dk

- Department of Electrical Engineering, University of South Africa, Pretoria 1709, South Africa; yusufaa@unisa.ac.za

- Oregon Renewable Energy Center (OREC), Department of Electrical Engineering & Renewable Energy, Oregon Tech, Klamath Falls, OR 97601, USA; eklas.hossain@oit.edu

- \* Correspondence: csstravichandr@gmail.com (S.R.); bharatiraja@gmail.com (B.C.); Tel.: +82-2220-4349 (B.C.)

Received: 29 June 2019; Accepted: 4 November 2019; Published: 14 November 2019

**Abstract:** The pulse width modulation (PWM) is an important segment in power electronic inverters and multilevel inverters (MLIs) design. The space vector modulation (SVM) methods own distinct advantages over other PWM methods. However, MLI SVM has involved more mathematics in their executions. Hence, the digital signal processors (DSPs) or field programmable gate arrays (FPGAs) based digital implementations are highly preferred for MLI SVM realizations, which require exceptional properties. The conventional MLI SVMs use complex mathematical functions to solve their internal functions to identify the space vector diagram (SVD) sub-triangle and over modulation boundary switching on-times. Particularly these are the changes in the position of reference vector with respect to their sub-triangle positions involving higher mathematical functions. This paper proposes a simplified three-level MLI SVM that reduces the sub-triangle and over modulation switching on-time calculations with reduced mathematical functions. The proposed MLI SVM is derived based on two-level SVM without changing the reference vector position, unlike the traditional approaches. This helps in extending the SVM for any n-level inverter with additional LUTs. The detailed theoretical study, MATLAB-Simulink system generator simulations and Xilinx FPGA family SPARTAN-III-3A based experimental implementations are done with three-level neutral point MLI fed induction motor drive. The theoretical design, analysis, and experimentation results validate the advantages of the proposed PWM design and its implementation. In addition, the proposed implementation is executed from the MATLAB Xilinx system generator directly into target FPGA, which makes it faithful, efficient and minimizes the time spent.

**Keywords:** pulse width modulation (PWM); multilevel inverter (MLI); space vector modulation (SVM); field programmable gate array (FPGA)

Energies **2019**, 12, 4332 2 of 24

#### 1. Introduction

The involvement of modern power electronics converters in the emerging technology is essential for the electrical system in the current era. Very particularly, in the overall power electronics segment, the voltage source two-level inverters are very popular and demanding, due to their application encroachment in industrial, commercial and non-conventional energy conversion systems [1]. Compared with two-level inverters, multilevel inverters (MLIs) have substantial rewards, which are intensive in the enhancement of the voltage and current waveform quality, reduction of harmonic contents, and increment of power handling capability. Nabae et al. invented the first MLI based on two-level inverter structure called neutral-point clamped (NPC) topology in 1981 [2] which was followed by the development of cascaded H-bridge (CHB), flying capacitor (FC), and hybrid MLIs in later years. Even though these MLIs are capable of producing the multi-stepped output voltages with reduced dv/dt and harmonics for improved power qualities. But, considering the DC-link capacitors balancing and common mode voltage (CMV) reduction, the MLIs are widely still investigated with different modulation strategies [3] for compensation methods. Among them, space vector modulation (SVM) offers better-quality voltage and current output with higher DC-link utilization. In addition, SVM provides a switching state selection opportunity to improve the performance of the MLI [4–15]. Particularly, the SVM contributions in NPC-MLI are widely researched and applied in the various fields of drives and renewable energy integration applications [5]. The switching selections in the multilevel SVM are mainly associated with the space vector diagram (SVD) synthesization and switching states on-time calculation. The multilevel SVM using two-level concepts are widely explored than the other MLI SVM methods [4,9,12–16]. However, these methods include complex mathematics to calculate the target reference voltage vector and recognize inner sub-triangle etc. The Zhang et al. has introduced a method for finding switching states on-time using direct two-level SVM approach. In this method, the three-level SVD has fragmented to a six, equal, two-level SVD, and its location of the centre of six virtual hexagons originated through segregation of the SVD [17]. Similar to this method, in the literature, many papers have been reported in which shifting the origin to one of the six centres, and  $\alpha\beta$ -axes are rotated by 60° to use two-level on-time calculations [12–16,18–21]. Even though these methods are calculating the individual switch on-times from segregated two-level SVM, while extending to higher levels that need complex mathematical functions to calculate the sub-triangle. Seo et al. [18] proposed a scheme for an MLI SVM for three-level NPC similar to Zhang et al. where the origin is shifted to 60° which sorts six sub-hexagons to compute on-times, thereby involving additional computations. The three-level SVD based two-level SVD with reduced math function is proposed and implemented for NPC-MLI [9]. The similar idea is extended to linear modulation (LM) and over modulation (OVM) region with field programmable gate array (FPGA) implementation for NPC-MLI [19–23].

In [19], the multilevel SVD is divided into six equal two-level SVDs and switching vector ontime calculations are made through direct transformations from three neighboring switching vectors. However, the estimation of the on-time calculation is done by extending a set of matrix transformations, which includes complex computations. Extending the inverter modulation index more than 0.907 is called as OVM. It requires non-linear mathematical functions to synthesis their reference vector outside SVD hexagon [24–26]. The industrial drives, such as direct torque and field-oriented controller need OVM region operations, since linear modulation range operation restricts the inverter modulation index, and hence, the drives produce limited constant torque as it utilizes only 90% of input DC-link voltage. Hence, the inverter drive covering OVM is beneficial by means of entire exploitation of the installed input source capacity, which results in the increased cumulative speed-torque characteristics, as well as the operating boundary of the traction drives. However, OVM leads to complexities in hardware implementations, due to non-linearity switching equations [20]. Due to this complexity in the OVM region synthesization and on-time calculations, many studies are not preferred to include OVM region operation. Very few implementations have performed in the OVM region operation [21–31]. These implementations are using complex mathematical functions to realize the OVM non-linear region and on-time calculations. To realize the OVM region, the non-linear trigonometric functions are used

Energies **2019**, 12, 4332 3 of 24

to find the modified on-times. These methods are relatively complex to implement [24,25]. Most of the OVM region studies in MLI SVM have been done by charging the reference vector position [23,24,26–30]. The on-time switching calculations of OVM using virtual vectors were recognized by using modifying hexagonal trajectory. However, in these methods, there would be portions of the line cycle, where the preferred reference vector could not be synthesized [28], [30]. Few algorithms were developed which use additional switching time derived from the outside hexagonal boundary projection [26,29]. However, these methods are introducing lower frequency harmonics, which are affecting the output waveform quality.

The rapid developments in high-performance microcontrollers, DSPs and FPGAs, have encouraged the research of work on digital PWM for rapid prototyping. Due to the development of ASIC technology, the FPGA based implementations have become popular, since it has an ability to implement custom hardware solutions and reprogramming flexibility. The SVM implementations on FPGA are showing a higher interest in the current era [6,12,14,32–44]. These implementations are mainly done through Altera and Xilinx Spartan family. The first successful single chip FPGA implementation of SVM has been presented by Tzou et al. [33], and followed by a variety of single chip FPGA IP core three-level SVM implementation and reported the validation [34–36,40]. These implementations have been done through Altera Vertex and Spartan with large device utilization and computational time. These direct VHDL code based implementations have suffered from the drawbacks of computational burden (writing VHDL/Verilog coding), high device utilization, and higher time taken. Particularly at high modulation ranges, due to the higher mathematical burden, the processing time is being increased [23,29,42]. These methods are very effective for implementation in terms of calculating the switching vectors and dwell times by means of simple addition and comparison operators without using any angles, trigonometric function and LUTs. However, the extension to OVM in n-level needed high mathematical operations and high hardware resources. The low complexity and fewer computation approaches make the SVM implementations very suitable for real-time application drive systems. The FPGA Spartan processors are developed on a VHDL code to carry out the implementation into FPGA. By the use of Xilinx system generator ISE tools, the SVM implementations have focused on increasing the processing speed, reduce the device utilization and the reconfiguration (partial and full) implementations [37,40]. In any implementation, the resource (FFs, LUTs) utilization is a major factor. Wang et al. [45] deployed three-level SVM in Spartan-3 FPGA with the consumption of 3,584 slices. Few more attempts were made with the same FPGA, which were also found to have higher resource utilization [14,23,40]. As an alternative, the same can be achieved using MATLAB/Simulink-Xilinx System generator tools with foundation ISE tools [46].

From the wide range of literature in the MLI SVM design and FPGA implementations, the existing methods involve higher computational complications for finding reference vector location and the on-time calculations of switching states. Hence, the existing FPGA implementations occupy higher device utilization and processing time. The reference vector positions in the multilevel SVD sub-triangle and over modulation boundary on-time calculations need to be rethought. Subsequently, the FPGA digital implementations era facilitates the exploitation of control degree of freedom in both LM and OVM region. Therefore, in this paper, a reduced mathematical approach is developed for identifying the sub-triangles and over modulation boundary area for calculating switching on-times. The proposed SVM has a direct way for calculating the LM and OVM switching times using two-level SVM. The proposed SVM is simulated using MATLAB-Simulink ISE system generator and validated directly in Xilinx family SPARTAN-III-3A XC3SD1800A-FG676 DSP-FPGA processor board. The implementation is verified through a three-level NPC-MLI fed induction motor drive laboratory prototype, and the test is performed over a wide range of operating conditions. The proposed SVM and their FPGA implementations are compared with the other reported methods. The theoretical design, analysis, and experimentation results validate the advantages of the proposed PWM design and its implementation.

Energies **2019**, 12, 4332 4 of 24

The organization of the paper is deliberate as follows: Section 2 explains the space vector PWM theory for two-level and multilevel. Section 3 deals with the proposed simplified MLI SVM, including both linear and over modulations. Section 4 accomplishes the MATLAB-Simulink implementation, and Section 5 discusses the FPGA collaborated experimentation setup of three-level MLI. Sections 6 and 7 deal with the distributed implementation of MLI SVM in FPGA MATLAB XSG-ISE and experimental results. In conclusion, the rewards of the proposed MLI SVM and its implementation are presented in Section 8. The list of abbreviations and references are given in the end.

#### 2. State of Art of Space Vector PWM Theory for Two-Level and Multilevel

#### 2.1. Two-Level Space Vector Modulation

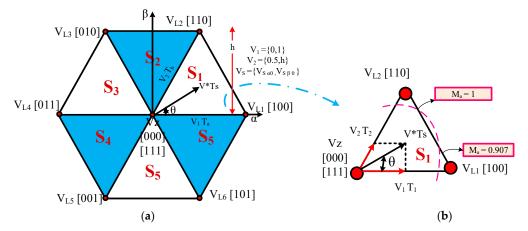

Figure 1a shows the SVD of a two-level inverter [37]. Here, every sector (represented as  $S_i$ , where i=1 to 6) is an equilateral symmetrical triangle with the height of  $h = \sqrt{3}/2$ . Here the edge vectors (V1 to V6) are named as non-zero (active vectors) and V0 and V7 are called zero vectors. The on-time calculation of SVM switching in any sector is calculated among three nearest switching vectors (one zero vector and two active vectors). The movement of the reference or target vector V\* positioning inside the sector is synthesizing the switching times. To understand the two-level switching of SVD, the sector-1 is considered here, as shown in Figure 1b. The volts-second of V\* is determined by multiplication of V\* and sampling time ( $T_s$ ). Then the time integral of V\* is estimated through the summation of products of the two of non-zero vectors ( $V_1$  and  $V_2$  by referring sector-1) and their time widths ( $T_1$  and  $T_2$ ).

Figure 1. (a) Space vector diagram (SVD) for two-level inverter, (b) sector-1 for two-level inverter SVD.

The reference voltage V\* volts-sec equation for the sector-1 is calculated as,

$$V^*T_s = T_1V_1 + T_2V_2 + T_0V_0$$

(1)

where  $T_1$  and  $T_2$  represents time(sec) widths of adjacent switching vectors  $V_1$  and  $V_2$  correspondingly, and  $T_0$  represents as time (sec) width of zero vector ( $V_0$ ). This zero vector state can be either [000] or [111] switching state, or else both. The movement of  $V^*$  angle ( $\theta$ ) within the sector is computed by

$$\theta = \tan^{-1} \left( \frac{V_{\alpha}}{V_{\beta}} \right). \tag{2}$$

The  $\theta$  values sample the V\* in different sector (for example, when  $\theta$  is 115°, the V\* approach sector-2, since sector-2 lies in an angle between 61° to 120°).

According to the V\* position, whether inside or outside the hexagonal SVD (see Figure 1), SVD is divided into linear modulation (where  $M_a \le 0.907$ ) and over modulation (where  $M_a > 0.907$ ), respectively.

Energies **2019**, 12, 4332 5 of 24

The total period is  $T_s = T_1 + T_2 + T_0$ .  $T_1$  and  $T_2$  are calculated from projecting  $V^*$  position along  $\alpha$ -axis and  $\beta$ -axis with respect to SVD origin (zero point). Henceforth, the volts-sec equations for  $\alpha$ -axis and  $\beta$ -axis are  $V^s_{\alpha 0}T_s = T_1 + 0.5T_2$  and  $V^s_{\beta 0}T_s = hT_2$ . Thus, the active vector time can be written as,  $T_2 = T_s \ V^s_{\beta 0}/h$  and  $T_1 = T_s \ (V^s_{\alpha 0} - V^s_{\beta 0})/2h$ . From the given switching frequency, the  $T_1$  and  $T_2$  help to find the zero voltage time  $T_0$ .

## 2.2. Multilevel Space Vector Modulation

Realizing SVM for more than two-level inverter (conventional six-switch inverter) is called MLI SVM. Numerous MLI SVM are developed and employed in MLIs for different applications [4,6,12,20]. The difficulty in the multilevel SVM is its complex mathematical needs to locate the V\* and find the individual vectors. The interesting techniques are proposed in the literature to reduce the complexity of implementing the MLI SVM with reasonable inverter performances.

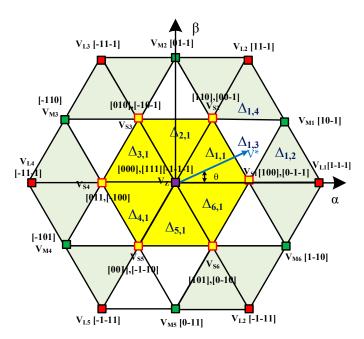

Any of the three-phase n-level SVD can be separated into six sectors  $(S_i)$ , where i=1 to 6. These sectors are further separated into  $(n-1)^2$  sub-triangles  $(\Delta_{i \neq j})$  where j=0 to 3 and i=1 to 6. Hence, the n-level SVD consists of  $n^3$  switching states. For example, considering the three-level MLI SVD, as shown in Figure 2, it has 27-switching states  $(3^3=27)$  and 24-sub-triangles (No. of sub-triangles in each sector is  $(3-1)^2=4$ ; therefore,  $4\times 6=24$ ) [6,9]. The switching vector for any level MLI is categorized into zero vector (ZV), short vector (SV) large vector (LV), and medium vector (MV). Here the ZV, MV and LV lie in the origin and boundary of the SVD, whereas, SV is multiple in numbers and placed in the middle portion of the SVD. Table 1 displays the three-level inverter SVD switching states.

Figure 2. Three-level multilevel inverter (MLI) SVD.

Table 1. Three-level inverter SVD switching states.

| Switching vector name | Switching states                                                                          | Total number of states |

|-----------------------|-------------------------------------------------------------------------------------------|------------------------|

| ZV                    | [000], [111], and [-1-1-1]                                                                | 3                      |

| MV                    | [10-1], [01-1], [-110], [-101], [0-11], [1-10]                                            | 6                      |

| SV                    | [100], [0-1-1], [110], [00-1],<br>[010], [101], [011], [100], [001], [110], [101], [0-10] | 12                     |

| LV                    | [1-1-1], [11-1], [-11-1], [-111], [-1-11], [1-11]                                         | 6                      |

Energies **2019**, 12, 4332 6 of 24

In three-level SVD, the SVs and ZVs have redundancy-switching states that are two for SVs and three for ZVs. When the MLI level is increased, the number of redundancy-switching states for ZVs and SVs are increased.

The switching states and their on-time calculations are calculated based on the rotating reference vector,  $V^*$  position in any one of the four sub-triangles in the particular sector. For example, when  $V^*$  lies in the fouth sub-triangle of first sector ( $\Delta_{1,4}$ ), then the nearest three vectors  $V_{S2}$ ,  $V_{M1}$  and  $V_{L2}$ , switching state are used to synthesize the  $V^*$ . The duty cycle of the above nearest switching vectors  $\delta_{VS2}$ ,  $\delta_{VM2}$  and  $\delta_{VL2}$  can be calculated and applied to the pulse generations.

Fixing the V\* in the sub-triangle is the most difficult task in the SVD realizations. Few mathematical approaches have been developed for finding V\* at sub-triangle, which needed high-end digital controllers to implement them [4,7,8,16]. In addition, considering the over modulation operation in MLI, the complexity is further increased to project the trajectory location in SVD. Once the vector moves outside the hexagonal boundary of the SVD, positioning the vector in the non-linear region (unstructured boundary) is predicted from the available switching vector and its on-times. The MLI SVD over modulation implementations differ from two-level SVD [19,29,30]. In MLI SVD over modulation, the OVM boundary is operating through the crux of MVs and LVs, whereas, in two-level SVD OVM the LVs only play to synthesis the on-time calculation of OVM pulses.

#### 3. Proposed Simplified MLI SVM for Entire Modulation Index

One of the important contributions of this paper is to propose the simple mathematical approach to find out the V\* sub-triangle position of MLI SVM. The proposed MLI SVM is developed based on standard two-level SVM for three-level MLI, and it can be extended for n-level using simple additional equations. In addition to proposed sub-triangle calculation, the reduced mathematical functions for calculating OVM switching on-times is achieved by just adding the compensated on-time gain in over modulation region with LM on-time. Hence, the proposed SVM reduces the implementation burden, since the complex part of MLI SVM calculations of sub-triangle position and OVM on-times are minimized.

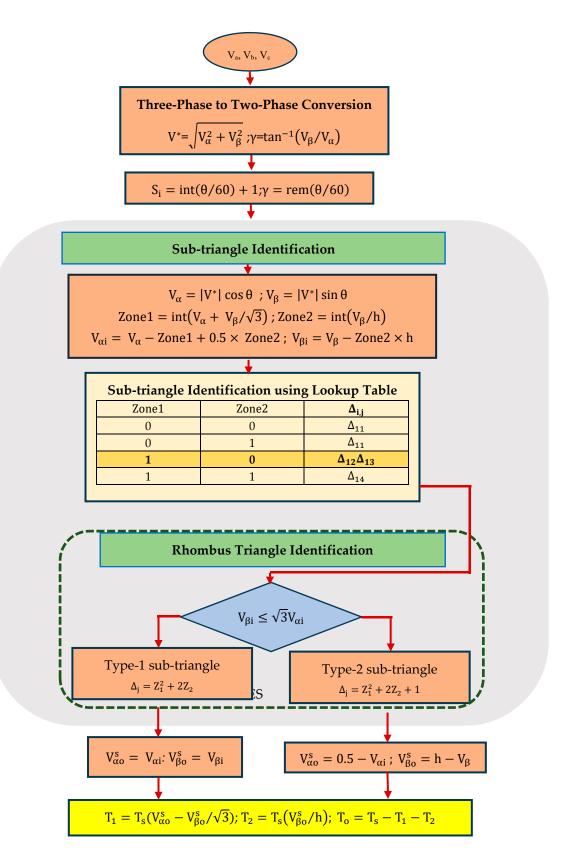

## 3.1. Procedure in Generating MLI SVM in Linear Modulation

Figure 3 shows the three-level MLI SVM generation flowchart. Like two-level SVM, the MLI SVM takes the three-phase signal to calculate two-phase voltage vectors stationary reference frame  $(V_{\alpha}, V_{\beta})$  [20]. Then, the  $V_{\alpha}$ ,  $V_{\beta}$  are converted into reference voltage vector in polar form as  $V^* \angle \theta$ , where  $V^*$  is the voltage magnitude, and  $\theta'$  is the angle of the  $V^*$ .

Using  $V^*$  and  $\theta$ , the reference vector sector position is calculated. Here, based on the  $V^*$  magnitude the SVD operation regions (either LM or OVM) are calculated. In Figure 3, the flow chart is handling only LM MLI SVM, where the proposed sub-triangle calculations are the same for LM and OVM.

The V\* sub-triangle location calculation with-in the sector is calculated through orthogonal time slope mathematical function in  $V_{\alpha}$ ,  $V_{\beta}$  plane. The stationary plane of  $V_{\alpha o}^s$  and  $V_{\beta o}^s$  are calculated for every  $T_s$  and then mapping for the reference vector V\* located in sub-triangle is done by comparing  $V_{\alpha i}^s$  and  $V_{\beta i}^s$ . These logical expressions can be applied for any level for identifying the V\* sub-triangle. The next section explains the proposed sub-triangle calculations.

Energies **2019**, 12, 4332 7 of 24

**Figure 3.** Flow chart for MLI SVM in LM.

Energies **2019**, 12, 4332 8 of 24

#### 3.2. Proposed Sub-Triangle Calculations

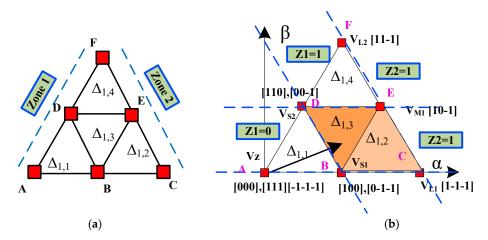

Considering the three-level multilevel SVD, shown in Figure 4, the sub-triangle 1 and 4 (type-1 triangles) can be directly calculated from the V\* magnitude, sector number and its respective sector angle  $(\gamma)$ ,

$$\gamma = \text{rem}(\theta/60). \tag{3}$$

However, this calculation does not support to calculate sub-triangle 2 and 3 (type-2 triangles). Hence, in order to handle type-1 and type-2 triangles searching progress, a simple look-up table and a searching process is developed directly from  $V_{\alpha i}^s$  and  $V_{\beta i}^s$ . Once the V\* sub-triangle is identified, that particular sub-triangle can be considered as a sector and then two-level SVM is applied to calculate the respective sub-triangle switching states on-time calculation. The same procedure is applied to all sectors in the particular  $M_a$  and  $f_s$ . The proposed sub-triangle calculation is explained through sector-1  $(\Delta_{1,j})$  as illustrated in Figure 4.

Figure 4. SVD linear modulation (LM) and over modulation (OVM) boundary.

The calculation of proposed sub-triangle involves two approaches: (1) Type-1 sub-triangles, (2) Type-2 sub-triangles. The V\* position for Type-1 triangles  $\Delta_{1,1}$  and  $\Delta_{1,4}$  can be calculated directly from  $V^s_{\alpha i}$  and  $V^s_{\beta i}$ . However, the calculation of Type-2 triangles  $\Delta_{1,3}$  and  $\Delta_{1,2}$  (orange colored area in Figure 5b) portions are challenging. Figure 5 shows the V\* location identification for Type-1 and Type-2 triangles. According to that, the search process of the triangle of V\* can be narrowed down using the two zones in SVD (Zone-1 and Zone-2). The coordinates ( $V_{\alpha 0}$ ,  $V_{\beta 0}$ ) of these triangles are calculated using two integer calculations of Zone-1 and Zone-2 as follows,

$$Zone1 = int(V_{\alpha} + (V_{\alpha} / \sqrt{3})), \tag{4}$$

$$Zone2 = int(V_{\alpha} + h). \tag{5}$$

In Equation (4), Zone-1 integer denotes the portion of the sector among the two lines joining the vertices divided by distance 'h' and inclined at  $120^{\circ}$  with respect to  $\alpha$ -axis. In Figure 5b, Zone-1 is valued as zero, it indicates that the point V\* is below the line B and C. The Zone-1 appears that the point V\* lies between the points A and B and D and F. The Zone-2 denotes the part of the sector between the two lines joining the vertices separated by distance 'h' and parallel to  $\alpha$ -axis. When the Zone-2 is valued as zero, it indicates that the reference vector tip V\* is positioned between the lines A and D and C and E. When the Zone-2 is valued as integer one, it indicates that the point V\* lies above

Energies **2019**, 12, 4332 9 of 24

the line C and D. Geometrically, the Zone-1 and Zone-2 values are acquired at an intersection of two rectangular regions (rhombus). Here, the V\* may be positioned either in triangle  $\Delta_{1,2}$  or  $\Delta_{1,3}$ .

Figure 5. (a). Sector-1 with Zone, (b) sector-1 with Zone, and Type-1, Type-2 triangles.

Hence, the V\* position in type -1 triangles ( $\Delta_{1,1}$  and  $\Delta_{14}$ ) is directly identified from Zone-1 and Zone-2 integer values. The Zone-1 and Zone-2 receipts zero integer, when the V\* is located in a triangle  $\Delta_{1,1}$ . The Zone-1 and Zone-2 receipts integer one when the V\* is located in triangle  $\Delta_{1,4}$ . However, the other options from the Zone-1 and Zone-2 (integers of Zone-1 is zero and Zone-2 is one or Zone-1 is one and Zone-2 is zero) are not assisting in identifying the  $\Delta_{1,2}$  and  $\Delta_{1/3}$ .

Hence, the Type-2 sub-triangles ( $\Delta_{1,2}$  and  $\Delta_{1,3}$ .) are calculated in rhombus using diagonal slope coordinate comparisons. The V\* co-ordinates point with respect to rhombus point B can be written as,

$$V_{\alpha i} = V_{\alpha} - int(Zone1) + 0.5 int (Zone2)$$

(6)

$$V_{\beta i} = V_{\beta} + 0.5h \tag{7}$$

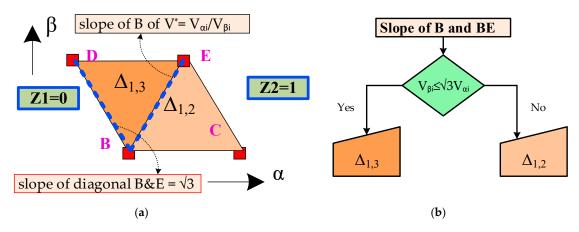

Figure 6a shows the sub-triangle  $\Delta_{1,2}$  and  $\Delta_{1,3}$  rhombus and its slope calculations. The sub-triangle, anywhere in reference vector V\* is situated by relating the slope of B and slope of BE. The slope B and BE can be written as,

$$V_{\beta i} \le \sqrt{3} V_{\alpha i}$$

(8)

Now, comparing the Equation (8) inequality of the Type-2 sub-triangles ( $\Delta_{1,2}$  and  $\Delta_{1,3}$ .) is identified.

Figure 6. (a). Sector-1 rhombus diagonal slope, (b) flow chart for rhombus sub-triangles selection.

Energies 2019, 12, 4332 10 of 24

## 3.3. Sub-Triangle Switching On-time Calculations

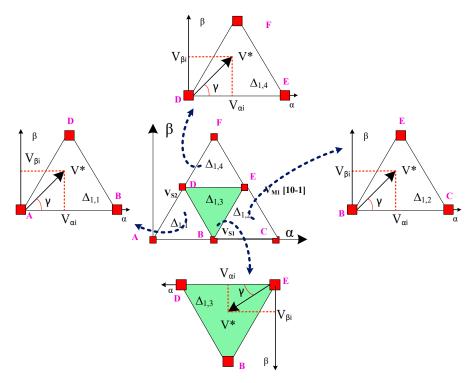

The flowchart (See Figure 3) shows the complete interpretation of the sub-triangle lookup table (LUT) identification for Zone-1 and Zone-2. To simplify the switching on-time calculations, all sub-triangles are further considered into two categories based on their base position either bottom or top. The first category is called as group-1 triangles ( $\Delta_{1,1}$ ,  $\Delta_{1,2}$  and  $\Delta_{1,4}$ ), where it has a base at the bottom. Similarly, group-1 triangle ( $\Delta_{1,3}$ ) is placed in SVD with the base side at the top. Figure 7 shows the group-1 and group-2 triangle for the calculation of switching on-times. For the group-1 and group-2 triangle valuations, the proposed SVM uses simply the calculation by using Zone-1 and Zone-2 triangle positions.

**Figure 7.** Group-1 triangles  $(\Delta_{1,1}, \Delta_{1,2} \text{ and } \Delta_{1,4})$  and Group-2  $(\Delta_{1,4})$  triangle representation for sector-1.

The group-1 triangle is determined by solving the following Equations (9) and (10),

$$int(zone1)^2 + 2 int (zone2)$$

; either  $\Delta_{1,1}$ ,  $\Delta_{1,3}$  and  $\Delta_{1,4}$  (9)

Else,

$$int(zone1)^2 + 2 int (zone2) + 1; either \Delta_{1,2}$$

(10)

Thus the coordinates of group-1 triangle and group-2 triangles can be calculated as  $V_{\alpha i}^s$ ,  $V_{\beta i}^s$  and 0.5  $V_{\alpha i'}^s$  h– $V_{\beta i}^s$ .

From the individual sub-triangle  $\alpha$ ,  $\beta$  coordinates, the switching states on-time of each sub-triangle can be calculated similarly to two-level SVM.

$$T_1 = T_s(V_{\alpha\alpha}^s - V_{\beta\alpha}^s / \sqrt{3}) \tag{11}$$

$$T_2 = T_s(V_{\beta o}^s/h) \tag{12}$$

This calculation can be used for n-level MLI by the accumulation of the group sub-triangles.

Energies **2019**, 12, 4332 11 of 24

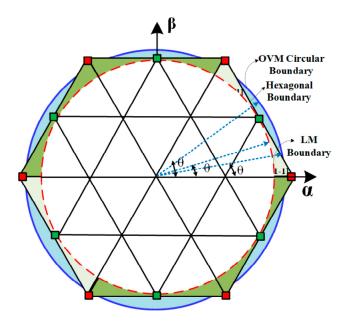

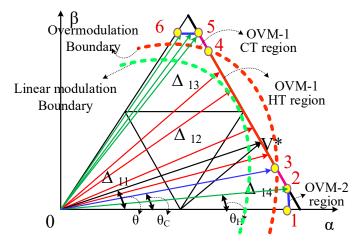

#### 3.4. Extending to Over Modulation

To move the V\* from LM to OVM region, the V\* is moved to outside the hexagonal trajectory. During this circumstance, the  $M_a$  is valued more than 0.9 and the V\* moves outside SVD hexagonal boundary. Thus, the synthetization of V\* in the OVM region is unrealistic (non-linear nature movement). As a result, to achieve the OVM region operation and calculating its switching state on-times, the traditional approach used trigonometric functions to calculate the OVM voltage vector switching state on-times [20,24,30]. These methods consume more mathematical and implementation complexity. In addition, these methods are producing higher low frequency harmonics. The proposed OVM method has a straightforward nature to realize switching on-time from the LM switching time. Hence the non-linearly can be minimized, which helps to avoid the additional lower frequency harmonics. The OVM region is operated in two zones as OVM-1 (V\* is lies from 0.908 to 0.958) and OVM-2 (V\* is lies from 0.958 to one).

In the OVM-1 region, as shown in Figure 8, there would be portions of the OVM line cycle, which are placed partly within the SVD hexagon and partly outside the hexagon. Hence the two relations are derived for calculating the on-time for  $V^*$  circular region and hexagonal region. To differentiate these two boundaries, the crossover angle ( $\theta_C$ ) is calculated from the reference vector  $M_a$ ,

$$\theta_c = 30^{\circ} - \cos^{-1}(\Pi/(2\sqrt{3}M_a)). \tag{13}$$

Now the V\* angle  $\theta$  fulfills the position  $\theta_C \leq \theta < \Pi/3 - \theta_C$ , the V\* remains in hexagonal trajectory, and another portion follows the circular trajectory ( $0 \leq \theta < \theta_C$  to  $\Pi/3 - \theta_C \leq \theta < \Pi/3$ ). Based on the V\* position in SVD, the OVM-1 coordinates ( $V_\alpha$  and  $V_\beta$ ) of V\* can be calculated from  $\theta$  and level (n),

$$V_{\alpha} = (\sqrt{3}(n-1))/(\sqrt{3} + \tan \theta), \tag{14}$$

$$V_{\beta} = (\sqrt{3}(n-1)\tan\theta)/(\sqrt{3} + \tan\theta). \tag{15}$$

From the  $V_{\alpha}$  and  $V_{\beta}$ , the  $V_{\alpha o}^s$  and  $V_{\beta o}^s$  are calculated for deriving modified switching on-time,

$$T_1 = T_s(V_{\alpha o}^s - V_{\beta o}^s / \sqrt{3}); T_o = 0; T_2 = T_s.$$

(16)

To realize the circular trajectory and hexagonal trajectory switching on-times, the gain factor ( $G_t$ ) can be calculated from the OVM-1 maximum boundary and its actual  $M_a$  values. The maximum volt-seconds loss in OVM-1 region is proportional to (0.9535 – 0.907). Hence, the  $G_t$  can be obtained from LM  $M_a$  as,

$$G_{t} = (OVM - 1 - 0.907) / (0.9535 - 0.907). \tag{17}$$

Adding and subtracting the  $G_t$  with  $T_0$ ,  $T_1$  and  $T_2$ , the circular trajectory and hexagonal trajectory switching on-time can be calculated by modifying the  $V^*$ .

Now from Equations (11), (12), and (17), the hexagonal trajectory switching on-time is derived as,

$$T_{1 \text{ OVM-1 HT}} = T_s (V_{\alpha o}^s - V_{\beta o}^s / \sqrt{3}) + 0.5G_t^2 T_o,$$

(18)

$$T_{2 \text{ OVM-1 HT}} = T_s(V_{\beta o}^s/h) + 0.5G_t^2 T_o,$$

(19)

$$T_{o \text{ OVM-1 HT}} = T_s - T_{1 \text{ OVM-1 HT}} - T_{2 \text{ OVM-1 HT}}.$$

(20)

Similarly, the circular trajectory switching on-time is derived as,

$$T_{1 \text{ OVM-1 CT}} = T_s(V_{\alpha o}^s - V_{\beta o}^s / \sqrt{3}) - 0.5G_t^2 T_1,$$

(21)

$$T_{2 \text{ OVM-1 CT}} = T_s(V_{\beta o}^s/h) - 0.5G_t^2 T_2,$$

(22)

Energies **2019**, 12, 4332

$$T_{o \text{ OVM-1 CT}} = T_s - T_{1 \text{ OVM-1 HT}} - T_{2 \text{ OVM-1 HT}}.$$

(23)

When the V\* modulation index  $M_a$  is more than 0.9535, then the V\* is entered into OVM-2 region. During this time the V\* is allowed only in the hexagonal trajectory (beyond the OVM-1 HT), and only six LVs are needed to operate. Hence, the holding angle  $(\theta_h)$  is derived using a similar strategy [9] to keep the V\* at one of the large vectors. The relations  $0 \le \theta < \theta_h$  and  $\Pi/3 - \theta_h \le \theta < \theta_h$  help to find one of the LV in the particular sector with changing V\* position. The on-time equations of OVM-2 are obtained as,

$$0 \le \theta < \theta_h$$

;  $T_1 = T_{s}$ ,  $T_2 = T_0 = 0$ , (24)

$$\Pi/3 - \theta_h \le \theta < \Pi/3 ; T_2 = T_s, T_1 = T_o = 0.$$

(25)

The proposed LM and OVM do not change V\* position. Hence, it allows simple implementations.

Figure 8. OVM boundary for proposed three-level SVM.

#### 4. MATLAB-Simulink Implementation of Three-level SVM

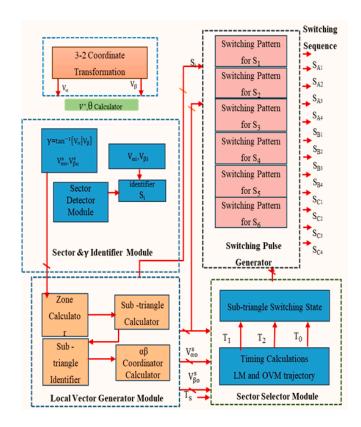

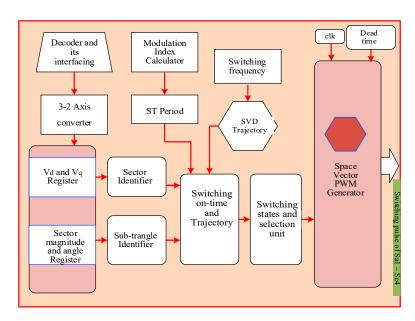

The proposed MLI SVM design is established using MATLAB 13.b Simulink with five subsystems that are connected through In and Out Xilinx SG that helps to implement the MLI SVM directly from MATLAB-Simulink (.mdl) file to target FPGA. Figure 9 illustrates the detailed MATLAB-Simulink design flow of proposed MLI SVM.

- 1) The first block is the "Clarke's transformation", in which the three-phase reference rotating frame are converted into  $V_{\alpha}$ ,  $V_{\beta}$ .

- 2) The 2nd block named 'Sector and  $\gamma$  identifier' block holds four sub-systems namely reference vector  $M_a$ ,  $\theta$ , sector and  $\gamma$ .

- The next block is calculating the local vector reference frame ( $V_{\alpha 0}^{s}$  and  $V_{\beta 0}^{s}$ ) and finding the sub-triangle. Then the switching on-times  $T_1$ ,  $T_2$ , and  $T_0$  are calculated (based on two-level SVM).

- 4) The fouth subsystem is calculating the LM and OVM boundary based on the reference vector  $M_a$ . The subsystem receives the sub-triangles,  $V_{\alpha 0}^s$  and  $V_{\beta 0}^s$  to sample switching pulse period for the  $T_s$ . The switching events of all 27 switching states are stored in LUT.

- 5) Finally, based on the sector number, sub-triangle number, and  $M_a$  boundary, the switching on-times are calculated and mapped into the corresponding switching states.

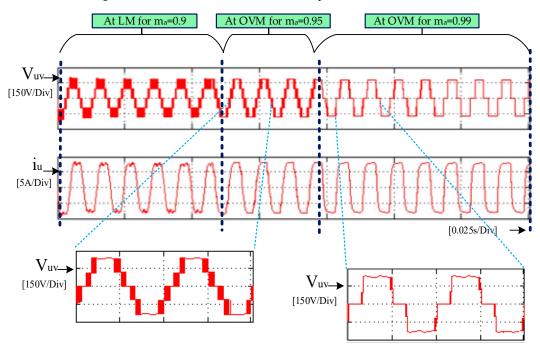

The performance of the MLI SVM for  $0 < M_a \le 0.99$  is simulated on a three-level NPC-MLI drive with 460V DC-link, two 470  $\mu$ F DC-link capacitors, and 10 kHz switching frequency. The 2.45 kW, 1440 rpm, four poles, and 50 Hz induction motor is used as a load. Figure 10 shows the inverter line voltage ( $V_{uv}$ ) waveform for LM, OVM-1 and OVM-2 operations. Initially, the simulation studies are conducted for  $M_a = 0.5$ . Here the line voltage ( $V_{uv}$ ) is measured as a 2-level output, because only

Energies 2019, 12, 4332 13 of 24

the SVs and ZVs have participated in the switching sequence. Hence, the  $V_{uv}$  resulted in 2-level output was 147.8 V with THD value of 13.06 %. Next, the same simulation study is extended for the higher modulation ranges (more than 0.5) and resulting in increased voltage magnitude. When the inverter is operated at maximum LM range of 0.907, the  $V_{uv}$  resulted is 268.4 V, as shown in Figure 10. As expected, the fundamental voltage is increasing linearly by increasing  $M_a$ . Here the line voltage at  $M_a = 0.950$  and  $M_a = 0.990$  is observed as 282 V and 295 V, respectively.

Figure 9. MLI SVM MATLAB-Simulink implementation flow chart.

**Figure 10.** Simulation result for modulation range  $(0.9 < M_a \le 0.99)$ .

Energies **2019**, 12, 4332

# 5. FPGA Collaborated Experimentation Setup of Three-Level MLI

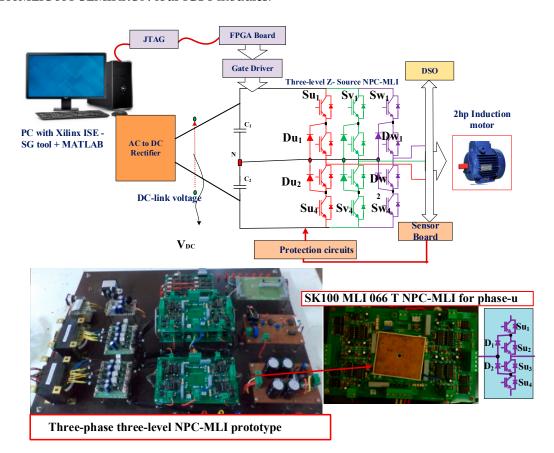

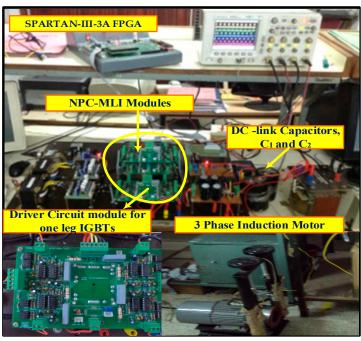

The experimental setup diagram and FPGA are collaborated Three-phase three-level NPC MLI is shown in Figure 11. The NPC-MLI is designed with three integrated surface-mounted SK100MLIO66T-SEMIKRON four IGBT modules.

Figure 11. Three-level MLI experimentation with SPARTAN-III-3A XC3SD1800A-FG676 DSP-FPGA.

Energies **2019**, 12, 4332

Two 100  $\mu$ F, 1000 V rating DC-link capacitors are used for providing DC-link voltage of the MLI. The switching module used HCPL4506 opto-isolator to provide the isolation between the FPGA controller, and IGBT. The Xilinx family SPARTAN-III-3A XC3SD1800A-FG676 DSP-FPGA controller is used to implement and generate the proposed SVM. The 2.45 kW, 1440 r/min, 50 Hz, 4-pole three-phase squirrel-cage induction motor (SCIM) drive is used as a load. The YOKOGAWA spectrum analyzer is used for capturing the experimental results.

#### 6. MATLAB-Simulink built FPGA Habitat for Hardware Implementation

The MATLAB-Simulink support Xilinx ISE project navigator system generator (SG) tool is used for the proposed SVM implementations as it allows the minimization of the time spent for design and cost of implementation.

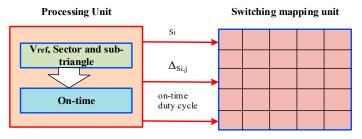

The architecture of the proposed SVM FPGA implementation is shown in Figure 12. The FPGA core contains the two main modules: (1) The processing unit; and (2) switching and its mapping unit, as shown in Figure 13. These modules can perform in parallel that helps to minimize the processing time. The processing unit comprises functional blocks to calculate the V\*, sector, sub-triangle,  $\alpha\beta$  coordinates for LM and OVM trajectory, and logical routes. The mapping unit consists of switching vectors for the corresponding sub-triangles. The switching vector-mapping unit uses memory (LUT). It maps the pre-stored switching sequence for the MLI based on sector, sub-triangle.

Figure 12. Proposed MLI SVM FPGA core structure.

Figure 13. Processing unit and mapping unit sharing.

The core also considers some key design measures for improving computation accuracy and simplifying hardware design and the fixed-point arithmetic unit is adopted for implementing the calculations. The IP core is designed to operate at 20MHz clock frequency, and high switching

Energies **2019**, 12, 4332 16 of 24

frequency, as well as the t<sub>d</sub>, is adjustable. The architecture of the proposed SVM sub-blocks is described, as follows:

- 1. 3/2 axis converter block: It performs the abc to d-q conversion, which generates the V\*and angle  $(\theta)$ .

- 2.  $M_a$  block: Depending upon the V\* requirement, the  $M_a$  value of the inverter can be given through the  $M_a$  block.

- 3. Switching period block: It holds the sampling frequency for the inverter switches.

- 4. Sector identification block: This block finds the  $V^*$  location based on the angle ( $\theta$ ) and  $V^*$  magnitude.

- 5. Triangle identifier block: The block computes V\* sub-triangle location.

- 6. Trajectory identifier block: This block measures the trajectory identifier (LM, OVM boundary) and V\* location based on the  $M_a$  values. It also calculates  $\theta_C$  and  $\theta_H$  angles for OVM operation.

- 7. On-time calculation block: This block calculates the respective switching state on-times based on two-level SVM calculations. This unit uses the LUTs to store the switching states and the switching sequences. Lastly, SVM generator unit generates the pulses to the 3-level NPC-MLI after inserting the dead time  $(t_d)$ .

- 8. Switching state unit: It holds the 27-switching event.

- 9. Dead time register block: Holds the timer to add or reduce the t<sub>d</sub>.

- 10. SVM Generating Unit: This block produces the pulses to the NPC-MLI after inserting the t<sub>d</sub>.

To simplify the interface with the processor, commands to these registers are routed through a decoder and interface circuit. The clock is acting as a base time for PWM generator and is operated at 100MHz. The overflow flag from PWM generator unit indicates the value of PWM counter when it reaches the maximum count, which can be used to trigger events for the inverter.

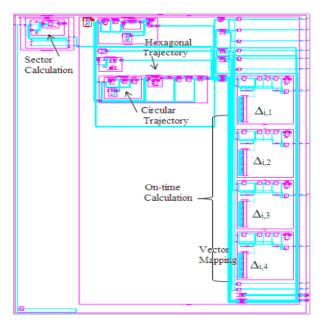

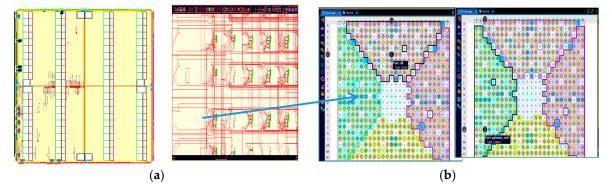

#### 6.1. Implementation of the Proposed MLI SVM Scheme in FPGA

The XSG FPGA environment implementation is divided into five stages as follows: MATLAB code generation through XSG, VHDL code generation and its simulation, register transfer level (RTL) file and bit file generation, synthesis and download into target FPGA. Once the RTL file is generated, the proposed SMV architecture RTL view (shown in Figure 14) and off-line simulation is done to view the generated inverter pulses using ModelSim 5.8e. Figure 15 shows the ModelSim simulation results for the proposed MLI SVM. It ensures the desired pulse pattern, t<sub>d</sub> values. After successful synthesis, the device utilization and power utilization report is generated. It provides the number of logical blocks, LUTs and FFs to be used in architecture. The proposed MLI SVM uses only 3.7% LUT memory space in the FPGA, since it uses simple 2-level SVM, and hence, does not require any additional calculations for calculating the switching on-time. It also minimizes the processing time for LM and OVM operations. Figure 16a shows the internal structure based on the described SVM implementation design. After RTL synthesis, the net list is saved as an NGC file. Afterwards, the JTAG serial mode ("IEEE Standard 1149.1") configuration interface card is used to download the code to the Target FPGA SPARTAN-III-3A XC3SD1800A-FG676. The JTAG configuration is through the independent boundary scan selection. Then the regenerated bit file is generated. Finally, the developed RTL is converted to bit stream format, and then the UCF is written for pin assignment for the mapping process. Mapping is done to fit the design into the available resource of the target FPGA processor. Finally, placing the code in target FPGA is done.

Energies 2019, 12, 4332 17 of 24

Figure 14. Register transfer level (RTL) view proposed MLI SVM core.

**Figure 15.** ModelSim simulation results; 12-pulses  $(S_{1u}-S_{4w})$  of proposed MLI SVM for  $f_s$  = 10 kHz, dead time = 6  $\mu$ s.

Figure 16. (a) Device area utilization, (b) input and output port view for the implemented SVM.

# 6.2. MLI SVM FPGA Implementation Results

There are three types of floor views that are generated for the SVM IC, which are overall floor view of device utilization, input port assign view, and output port assign view. From Figure 16a, it is observed that the proposed code occupies very less resource/area. Figure 16b shows the input and output port of the proposed implementation. The proposed PWM design I/O's are mapped properly using UCF based on reduction of the power losses. The implementation consumes only 0.13 W power utilization for one cyclic operation of pulse generation.

Due to the simplification of sub-triangle calculations and OVM-1 switching mapping, the overall device utilization of the proposed SVM implementation becomes 5.88%, which is less than the earlier

Energies **2019**, 12, 4332 18 of 24

implementations [14,23,40,45]. The simplified calculation to find the rhombus sub-triangles selection and OVM-1 on-time calculations are the primary reasons for the memory reduction (around 0.17%), while considering the implementation reported in [23]. The additional reductions are achieved by way of reducing the LUT usage for operation by repeating switching states.

The processing time of the proposed implementation for LM OVM-1, and OVM-2 are calculated using [37], and the values are 13.017  $\mu$ s, 14.561  $\mu$ s, and 15.532  $\mu$ s, respectively. From the results, it can be understood that the proposed FPGA implementations are taking the same time for all LM values as 13.017  $\mu$ s, since sub-system calculation is same for all the range of LM from 0.5 to 0.907. However, during over modulation operations, the processing time for the proposed implementation is increased. The increase in time is because of  $G_t$  calculation for the new on-times. Nevertheless, when compared to the early implementations, the time taken for OVM is less for the proposed method [23], and it is expected while implementing with other family FPGAs. Similarly, considering the device utilization (memory occupied) on FPGA for the proposed implementations, it is considerably lesser. From the above analysis and results, it is clear that the proposed MLI SVM algorithm and its Sparten-3 FPGA implementation improved in terms of their owning mathematical complexity and implementation. Hence, due to this reduced mathematical burden, less device utilization and processing time, the proposed implementations fit to be considered as an IP core that can be incorporated into a System On-Chip with other IP cores and it can greatly reduce the area of a PCB and improve the immunity to interferences for the power converters design.

#### 7. Experimental Results and Analysis

In order to validate the proposed MLI SVM FPGA implementation, the experimentation study is conducted for 2.3 kW three-phase induction motor supplied from three-phase three-level NPC-MLI. The DC-link voltage of the NPC-MLI is maintained at 560 V through an uncontrolled rectifier. The two 100  $\mu$ F DC-link capacitors  $C_1$  and  $C_2$  are connected with DC-link to clamp the voltage. The switching frequency of 10 kHz and dead time of 6 $\mu$ sec is used between two complementary switches. The experiment study is performed with modulation index value from 0.7 to maximum over modulation range ( $M_a=0.99$ ). During the study, the speed of the motor is recorded using digital tacho-generator.

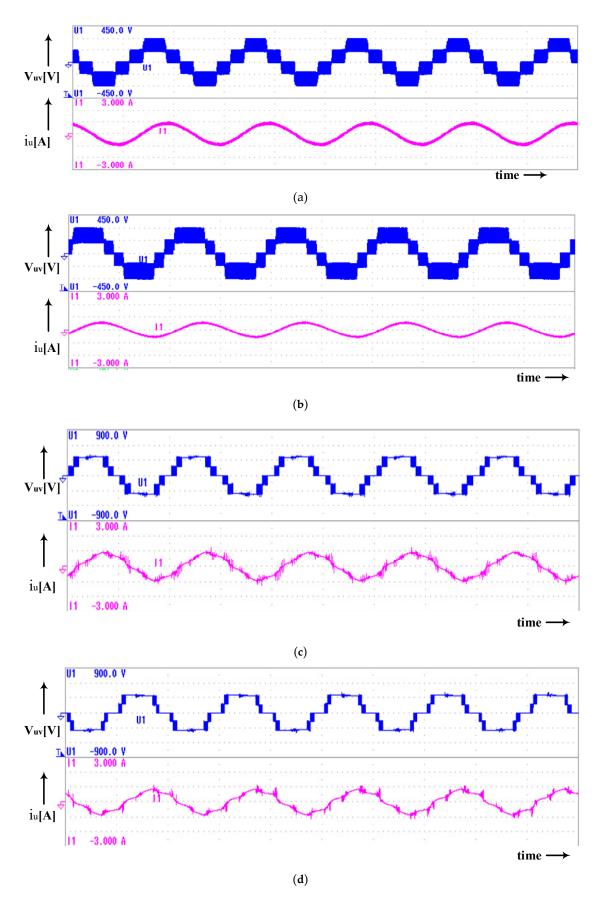

Figure 17a–d depicts the experimental results of MLI line-voltage ( $V_{uv}$ ) and corresponding current ( $I_u$ ) for  $M_a=0.7$ ,  $M_a=0.9$ ,  $M_a=0.95$ , and  $M_a=0.99$ , respectively. In the LM region, the inverter output voltage is obtained as 205.2 V and 262.4 V for  $M_a=0.7$  and  $M_a=0.9$ , respectively. However, while increasing the  $M_a$  from LM to OVM, the fundamental voltage is increased linearly. The  $V_{ab}$  for  $M_a=0.7$  and  $M_a=0.9$  is obtained as 280.3 V and 292.5 V, respectively. From the results, it can be seen that the inverter voltage and current waveforms are changing based on the modulation index value.

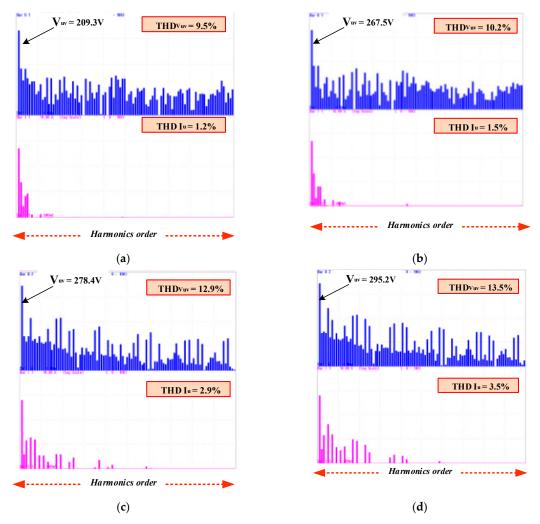

However, the voltage and current waveforms are smooth in all the range of modulation indices. This demonstrates that the proposed SVM is working with full control degree of freedom in the linear and over modulation region. Figure 18a–d shows the voltage and current harmonics spectrum. The voltage and its corresponding current harmonics in the LM are lesser when compared with those in the OVM regions. The line voltage percentage THD is observed as 10.2%, 12.9%, and 13.5% for  $M_a = 0.9$ ,  $M_a = 0.95$  and  $M_a = 0.99$ , respectively. This increase is due to the non-linearity in the switching on-times in the OVM region operation. Similarly, the current percentage THD in OVM is higher than that in LM. When compared with the other multicarrier and selective harmonics elimination PWM methods, the proposed SVM has lower current and voltage THD in both LM and OVM. In addition, while changing the inverter operation from one region to another region, the voltage and current waveforms are smooth, and there are no abrupt changes.

Energies **2019**, 12, 4332

Figure 17. Line voltage  $(V_{uv})$  and Phase current  $(I_u)$  waveform; (a)  $V_{uv}$  for  $M_a=0.7$ , (b)  $V_{uv}$  for  $M_a=0.9$ , (c)  $V_{uv}$  for  $M_a=0.95$ , (d)  $V_{uv}$  for  $M_a=0.99$ .

Energies **2019**, 12, 4332

**Figure 18.** Line voltage harmonics spectrum; (a) at  $M_a = 0.7$ , (b) at  $M_a = 0.9$ , (c) at  $M_a = 0.958$ , (d) at  $M_a = 0.997$ .

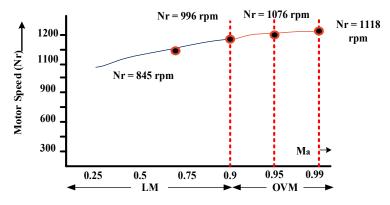

The induction motor speed variations for the modulation index range from  $M_a=0.7$  to  $M_a=0.99$  are measured and plotted in Figure 19. From the results, it can be seen that the motor speed changes in linear with the SVM modulation index. This illustrates that the proposed SVM can be directly employed to open-loop drives. In closed-loop operation, depending on the control requirement, the proposed SVM voltage reference magnitude and frequency can be changed easily without any additional mathematical calculations.

Figure 19. Motor speed response while changing modulation index.

Energies **2019**, 12, 4332 21 of 24

#### 8. Conclusions

In this paper, the detailed theoretical analytical study on MLI SVM and its digital implementation practices are explained. In addition to the previous method of SVM, the paper has also proposed a simplified mathematical approach to find out the MLI SVD sub-triangles, switching on-time calculation in both linear and over modulation. The proposed three-level MLI-SVM is exhibited based on two-level SVM without changing the reference vector position, unlike the traditional approaches. Hence, it can be easily prolonged with additional LUTs for any n-level inverter without any significant increase in computations. The proposed MLI SVM is comprehensively analyzed and validated for implementation in Xilinx family SPARTAN-III-3A XC3SD1800A-FG676 FPGA. The mathematical procedure involved in the proposed MLI SVM is reduced compared to the early attempts; hence, the device utilization and processing time are considerably reduced. The MATLAB–Simulink SG based simulation and SPARTAN-III-3A XC3SD1800A-FG676 FPGA implementation are performed to validate the proposed SVM with 2 kW three-phase three-level NPC MLI fed induction motor drive system. The presented results are confirming the performance of the MLI SVM at different modulation depths of the NPC MLI. The proposed implementation fits to be considered as an IP core that can be incorporated into a System On-Chip with other IP cores.

**Author Contributions:** All authors are involved in developing the concept, simulation and experimental validation and to make the article error free technical outcome for the set investigation work.

Funding: This research received no external funding.

Conflicts of Interest: The authors declare no conflict of interest.

#### Nomenclature

V\* Reference vector

$V_{\alpha}$ ,  $V_{\beta}$  Voltage vectors stationary reference frame

$\begin{array}{lll} \delta_{VS2} & & \text{Duty cycle of SV} \\ \delta_{VM2} & & \text{Duty cycle of MV} \\ \delta_{VL2} & & \text{Duty cycle of LV} \end{array}$

$\begin{array}{ll} \Delta_{i,j} & \text{Sub-triangle within the sectors} \\ \theta & \text{Angle of the reference vector} \end{array}$

γ Sector angleh Vertices height

$V_{\alpha o}^{s}, V_{\beta o}^{s}$  Individual Sub-triangle  $\alpha$ ,  $\beta$  coordinates

$\begin{array}{ll} \theta_C & \quad \text{Crossover angle} \\ \theta_h & \quad \text{Holding angle} \end{array}$

PWM Pulse Width Modulation

MLI Multilevel Inverter

SVM Space Vector Modulation

SVD Space Vector Diagram

LM Linear Modulation

OVM Over Modulation

NPC Neutral-Point Clamped

ZV Zero Vector SV Small Vector MV Medium Vector LV Large Vector

IP Intellectual Property

HT Hexagonal Trajectory

CT Circular Trajectory

THD Total Harmonic Distortion

IGBT Insulated-Gate Bipolar Transistor

SCIM Squirrel-Cage Induction Motor

Energies **2019**, 12, 4332 22 of 24

SG System Generator RTL Register transfer level

LUT Lookup Table

#### References

1. Abu-Rub, H.; Holtz, J.; Rodriguez, J.; Baoming, G. Medium voltage multilevel converter-state of the art, challenges and requirements in industrial applications. *IEEE Trans. Ind. Electron.* **2008**, *57*, 2581–2596. [CrossRef]

- 2. Nabae, A.; Takahashi, I.; Akagi, H. A new neutral-point clamped PWM inverter. *IEEE Trans. Ind. Appl.* **1981**, *IA-17*, 518–523. [CrossRef]

- 3. Bharatiraja, C.; Sanjeevikumar, P.; Blaabjerg, F. Critical Investigation and Comparative Analysis of Advanced PWM Techniques for Three-Phase Three-Level NPC-MLI Drives. *Electr. Power Compon. Syst.* **2018**, *46*, 258–269.

- 4. Ttique, Q.M. A Survey on Space-Vector Pulse Width Modulation for Multilevel Inverters. *CPSS Trans. Power Electron. Appl.* **2017**, 2, 226–236.

- 5. Jiao, Y.; Lee, F.C.; Lu, S. Space vector modulation for three-level NPC converter with neutral point voltage balance and switching loss reduction. *IEEE Trans. Power Electron.* **2014**, *29*, 5579–5591. [CrossRef]

- 6. Bharatiraja, C.; Jeevananthan, S.; Latha, R. FPGA based practical implementation of NPC-MLI with SVPWM for an autonomous operation PV system with capacitor balancing. *Int. J. Electr. Power Energy Syst.* **2014**, 61, 489–509. [CrossRef]

- 7. Choudhury, A.; Pillay, P.; Williamson, S.S. DC-Bus Voltage Balancing Algorithm for Three-Level Neutral-Point-Clamped (NPC) Traction Inverter Drive With Modified Virtual Space Vector. *IEEE Trans. Ind. Appl.* **2016**, *52*, 3958–3967. [CrossRef]

- 8. Bharatiraja, C.; Sanjeevikumar, P.; Iqbal, P. A Investigations of Multi-Carrier Pulse Width Modulation Schemes for Diode Free Neutral Point Clamped Multilevel Inverter. *J. Power Electr.* (*JPE*) **2019**, *19*, 702–713.

- 9. Gupta, A.K.; Khambadkone, A.M. A space vector PWM algorithm for multilevel inverters based on two-level space vector PWM. *IEEE Trans. Ind. Electron.* **2006**, *53*, 163–171. [CrossRef]

- 10. Narendra Babu, A.; Agarwal, P. Nearest and Non-Nearest Three Vector Modulations of NPCI Using Two-Level Space Vector Diagram—A Novel Approach. *IEEE Trans. Ind. Appl.* **2018**, *54*, 2400–2415.

- Sourkounis, C.; Al-Diab, A. A Comprehensive Analysis and Comparison between Multilevel Space-Vector Modulation and Multilevel Carrier-based PWM. In Proceedings of the 13th Power Electronics and Motion Control Conference (PEMC '08), Poznan, Poland, 1–3 September 2008; pp. 1710–1715.

- 12. Madasamy, P.; Suresh Kumar, V.; Sanjeevikumar, P.; Holm-Nielsen, J.B.; Hosain, E.; Bharatiraja, C.A. Three-Phase Transformerless T-Type-NPC-MLI for Grid Connected PV Systems with Common-Mode Leakage Current Mitigation. *Energies* **2019**, *12*, 2434. [CrossRef]

- 13. Selvara, R.; Chelliah, T.R.; Khare, D. A Novel Switching Strategy for DC Link Voltage Balance in Parallel Connected Three-Level Diode Clamped Back-to-Back Converter Systems Serving to Variable Speed Pumped Storage Plant. In Proceedings of the IEEE Transportation Electrification Conference (ITEC-India), Pune, India, 13–15 December 2017. [CrossRef]

- 14. Valan Rajkumar, M.; Manoharan, P.S.; Ravi, A. Simulation and an experimental investigation of SVPWM technique on a multilevel voltage source inverter for photovoltaic systems. *Int. J. Electr. Power Energy Syst.* **2013**, *52*, 116–131. [CrossRef]

- 15. Gui, S.W.; Lin, Z.J.; Huang, S.H. A varied VSVM strategy for balancing the neutral-point voltage of dc-link capacitors in three-level NPC converters. *Energies* **2015**, *8*, 2032–2047. [CrossRef]

- 16. Prats, M.; Franquelo, L.G.; Leon, J.I.; Portillo, R.; Galvan, E.; Carrasco, J.M. A 3-D space vector modulation generalized algorithm for multilevel converters. *IEEE Power Electron. Lett.* **2003**, *1*, 110–114. [CrossRef]

- 17. Zhang, H.; Von Jouanne, A.; Dai, S.; Wallace, A.K.; Wang, F. Multilevel inverter modulation schemes to eliminate common mode voltages. *IEEE Trans. Ind. Appl.* **2000**, *36*, 1645–1653.

- 18. Seo, J.H.; Choi, C.H.; Hyun, D.S. A new simplified space-vector PWM method for three level inverters. *IEEE Trans. Power Electron.* **2001**, *16*, 545–550.

- Bharatiraja, C.; Jeevananthan, S.; Munda, J.L.; Latha, R. Improved SVPWM vector selection approaches in OVM region to reduce common-mode voltage for three-level neutral point clamped inverter. *Int. J. Electr. Power Energy Syst. Elsevier* 2016, 79, 285–297. [CrossRef]

Energies **2019**, 12, 4332 23 of 24

20. Mondal, S.K.; Bose, B.K.; Oleschuk, V.; Pinto, J.O.P. Space vector pulse width modulation of three-level inverter extending operation into over modulation region. *IEEE Trans. Power Electron.* **2003**, *18*, 604–611. [CrossRef]

- 21. Giri, S.K.; Mukherjee, S.; Kundu, S.; Banerjee, S. An Altered PWM Strategy for Over Modulation Operation of Three-Level NPC Inverter with Capacitor Voltage Balancing. In Proceedings of the 2017 IEEE Transportation Electrification Conference (ITEC-India), Pune, India, 13–15 December 2017. [CrossRef]

- 22. Sanbo Pan, A. Shifted SVPWM method to control dc-link resonant inverters and its FPGA realization. *IEEE Trans. Ind. Electron.* **2011**, *59*, 3383–3391. [CrossRef]

- 23. Bharatiraja, C.; Jeevananthan, S.; Munda, J.L. Timing Correction Algorithm for SVPWM Based Diode-Clamped MLI Operated in over modulation Region. *IEEE J. Sel. Top. Power Electron.* **2018**, *6*, 233–245. [CrossRef]

- 24. Dong-Myung, L.; Jin-Woo, J.; Sang-Shin, K. Simple space vector PWM scheme for 3-Level NPC inverters including the OVM region. *J. Power Electron.* **2011**, *11*, 688–696.

- 25. Zhu, R.; Wu, X.; Tang, Y. Duty cycle-based three pulse-width modulation with over modulation and neutral balancing capabilities for three-phase neutral-point clamped inverters. *IET Power Electron.* **2015**, *8*, 1931–1940. [CrossRef]

- 26. Giri, S.K.; Mukherjee, S.; Kundu, S.; Banerjee, S.; Chakraborty, C. An Improved PWM Scheme for Three-Level Inverter Extending Operation into Over modulation Region With Neutral-Point Voltage Balancing for Full Power-Factor Range. *IEEE J. Emerg. Sel. Top. Power Electron.* **2018**, *6*, 1527–1539. [CrossRef]

- 27. Cataliotti, A.; Genduso, F.; Raciti, A.; Galluzzo, G.R. Generalized PWM–VSI Control Algorithm Based on a Universal Duty-Cycle Expression: Theoretical Analysis, Simulation Results, and Experimental Validations. *IEEE Trans. Ind. Electron.* **2007**, *54*, 1569–1580. [CrossRef]

- 28. Mehrizi-Sani, A.; Filizadeh, S. An Optimized Space Vector Modulation Sequence for Improved Harmonic Performance. *IEEE Trans. Ind. Electron.* **2009**, *56*, 2894–2903. [CrossRef]

- Beig, A.R. Synchronized SVPWM Algorithm for the Overmodulation Region of a Low Switching Frequency Medium-Voltage Three-Level VSI. *IEEE Trans. Ind. Electron.* 2012, 59, 4545–4554. [CrossRef]

- Maheshwari, R.; Munk-Nielsen, S.; Busquets, S. Carrier-based based Approach for Overmodulation of Three-level Neutral Inverter with Zero Neutral-point Current. In Proceedings of the IEEE International Conference Energy Conversion Congress and Exposition, Raleigh, NC, USA, 15–20 September 2012; pp. 1767–1773.

- 31. Gupta, A.K.; Khambadkone, A.M. A simple space vector PWM scheme to operate a three-level NPC inverter at high modulation index including over modulation region, with neutral point balancing. *IEEE Trans. Ind. Appl.* **2007**, *43*, 751–760. [CrossRef]

- 32. Dorairaj, N.; Shiflet, E.; Goosman, M. Plan ahead software as a platform for partial reconfiguration. *Xcell J. Xilinx* **2010**, *55*, 68–71.

- 33. Tzou, Y.Y.; Hsu, H.J. FPGA realization of space vector PWM control IC for three phase PWM inverters. *IEEE Trans. Power Electron.* **1997**, *12*, 953–963. [CrossRef]

- 34. Raja, B.; Raghu, S. Comparative Analysis of Different PWM Techniques to Reduce the Common Mode Voltage in Three-Level Neutral-Point-Clamped Inverters for Variable Speed Induction Drives. *Int. J. Power Electr. Drive Syst.* **2013**, *3*, 105–116. [CrossRef]

- 35. Lopez, O.; Alvarez, J.; Doval-Gandoy, J.; Freijedo, F.D.; Nogueiras, A.; Lago, A.; Penalver, C.M. Comparison of the FPGA implementation of two multilevel space vector PWM algorithms. *IEEE Trans. Ind. Electron.* **2008**, *55*, 1537–1547. [CrossRef]

- 36. Zeliang, S.; Jian, T.; Yuhua, G.; Jisan, L. An efficient SVPWM algorithm with low computational overhead for three-phase inverters. *IEEE Trans. Power Electron.* **2007**, 22, 1797–1805.

- 37. Pongiannan, R.K.; Paramasivam, A.; Yadaiah, N. Dynamically reconfigurable PWM controller for three phase voltage source inverters. *IEEE Trans. Power Electron.* **2010**, *26*, 1790–1799. [CrossRef]

- 38. Boujelben, O.; Bahoura, M. Efficient FPGA-based architecture of an automatic wheeze detector using a combination of MFCC and SVM algorithms. *J. Syst. Archit. Elsevier BV* **2018**, *88*, 54–64. [CrossRef]

- 39. Bharatiraja, C.; Prasad, T.B.; Latha, R. Comparative Realization of Different SVPWM Schemes in Linear Modulation using FPGA. In Proceedings of the IEEE Region 8 International Conference on Computational Technologies in Electrical and Electronics Engineering, Novosibirsk, Russia, 21–25 July 2008. [CrossRef]

Energies **2019**, 12, 4332 24 of 24

40. Bharatiraja, C.; Jeevananthan, S.; Latha, R.; Dash, S.S. Simplified Structure—A Mapped Space Vector Pulse width Modulation for Three Level Neutral Point Diode Clamped Multilevel Inverter. In Proceedings of the IET International Conference on Sustainable Energy and Intelligent Systems (SEISCON 2011), Chennai, India, 20–22 July 2011. [CrossRef]

- 41. Chettibi, N.; Mellit, A. FPGA-based real time simulation and control of grid-connected photovoltaic systems. *Sci. Direct Simul. Model. Pract. Theory* **2014**, *43*, 34–53. [CrossRef]

- 42. Fan, B.; Tan, G.; Fan, S. Comparison of three different 2-d space vector PWM algorithms and their FPGA implementations. *J. Power Technol.* **2014**, *94*, 176.

- 43. Ala, G.; Caruso, M.; Miceli, R.; Pellitteri, F.; Schettino, G.; Trapanese, M. Experimental Investigation on the Performances of a Multilevel Inverter Using a Field Programmable Gate Array-Based Control System. *Energies* **2019**, *12*, 1016. [CrossRef]

- 44. Wei, S.; Wu, B.; Wang, Q. An Improved Space Vector PWM Control Algorithm for Multilevel Inverters. In Proceedings of the International Power Electronics Motion Control Conference (IPEMC '04), Xi'an, China, 14–16 August 2004; pp. 1124–1129.

- 45. Yun, W.; Jianguo, J. The Study of FPGA-based Three-level SVM NPC Inverter. In Proceedings of the 6th IEEE International Conference on Power Electronics and Motion Control, Wuhan, China, 17–20 May 2009; pp. 1470–1474.

- 46. MathWorks. MATLAB Statistics Toolbox™ User Guide, R2016a; MathWorks: Natick, MA, USA, 2001.

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).