# **Aalborg Universitet**

### Reliability Analysis of Capacitors in Voltage Regulator Modules with Consecutive Load **Transients**

Zhao, Zhaoyang; Zhou, Dao; Davari, Pooya; Fang, Junlong; Blaabjerg, Frede

Published in:

I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2020.3016902

Publication date: 2021

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Zhao, Z., Zhou, D., Davari, P., Fang, J., & Blaabjerg, F. (2021). Reliability Analysis of Capacitors in Voltage Regulator Modules with Consecutive Load Transients. *I E E Transactions on Power Electronics*, *36*(3), 2481-2487. Article 9167458. https://doi.org/10.1109/TPEL.2020.3016902

### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 04, 2025

# Reliability Analysis of Capacitors in Voltage Regulator Modules with Consecutive Load Transients

Zhaoyang Zhao, Student Member, IEEE, Dao Zhou, Senior Member, IEEE, Pooya Davari, Senior Member, IEEE, Junlong Fang, and Frede Blaabjerg, Fellow, IEEE

Abstract—Capacitors are critical in voltage regulator modules (VRMs) which contribute to store energy and stabilize the output voltage during load transients. Usually, VRMs work with consecutive load transients, which would bring more electrothermal stress to capacitors and affect the reliability of capacitors compared with the steady-state operation. Recently, some efforts have been made to investigate the reliability of capacitors in power electronic converters. Unfortunately, transient processes are commonly ignored, which can impair the accuracy of the lifetime estimation. Regarding this issue, this paper investigates the influence of transients on the damage of capacitors in VRMs. A 150 W VRM is introduced as a case study. Firstly, the electrothermal stresses during steady state and transients are analyzed. Then, the lifetime calculation is considered from a single capacitor to hybrid capacitor banks. In addition, a suitable capacitor configuration of capacitor banks is also provided, in order to maximize its lifetime.

Index Terms—Capacitors, voltage regulator module (VRM), reliability evaluation, load transients.

#### I. Introduction

VOLTAGE regulator modules (VRMs) are widely used as power supplies for modern electronic applications with continuously varying loading conditions, such as digital signal processors, microprocessors, etc. [1]. In order to store energy and stabilize the output voltage during transients, a large capacity filter capacitor bank consisting of Aluminum Electrolytic Capacitors (Al-Caps) and Multi-Layer Ceramic Capacitors (MLC-Caps) is commonly applied at the output side of VRMs. However, capacitors are often considered to be the weakest components in power electronic systems [2]. For reliability reasons, it is important to investigate the lifetime of capacitors to provide a reference for capacitor sizing.

Usually, capacitor manufacturers provide a lifetime calculation model for their products [3]. However, the capacitor lifespan is estimated under a special condition with a given ambient temperature, ripple current, and capacitor voltage. The estimation result can not accurately represent the lifetime of capacitors in the actual operation with varied electro-thermal stress.

To improve the evaluation accuracy, some mission profile based reliability assessment methods have been presented in recent years. In [4], [5], a real mission profile and statistical approaches are used to evaluate the lifetime of capacitors. However, there is a lack of research focusing on the reliability

Manuscript received June 25, 2020; revised August 01, 2020; accepted August 11, 2020. This work was supported by the Application Technology Research and Development of Harbin under Grant 2017RAXXJ075. (Corresponding author: Junlong Fang).

- Z. Zhao is with the Department of Electrical Engineering, Chongqing University, Chongqing 400044, China (e-mail: zhaoyang.z@foxmail.com).

- J. Fang is with the College of Electronic and Information, Northeast Agricultural University, Harbin 150000, China (e-mail: junlongfang@126.com).

D. Zhou, P. Davari and F. Blaabjerg are with the Department of Energy

- D. Zhou, P. Davari and F. Blaabjerg are with the Department of Energy Technology, Aalborg University, Aalborg 9220, Denmark (e-mail: zda@et.aau.dk; pda@et.aau.dk; fbl@et.aau.dk).

- evaluation of capacitors in VRMs, and some limitations exist in applying the above-mentioned methods in VRMs.

- 1) Few research efforts have investigated the lifespan of hybrid capacitor banks consisting of Al-Caps (non-solid or polymer Al-Caps) and MLC-Caps, which are widely used in VRMs.

- 2) Low sampling-rate mission profiles (the sampling rate is usually in the order of minutes, and it is in the order of hours in [4]) cannot represent the actual operation state of VRMs (the loading step frequency is usually larger than 1kHz [6]), which results in some important loading information are ignored.

- 3) The loading profiles in [4], [5] are sampled in steady state, which ignores the transient processes. For VRM applications, the current and voltage stresses of capacitors during transients are usually larger than that for steady state. Ignoring the transient processes would result in inaccurate estimation results.

- 4) There is a lack of a thermal model to describe the temperature dynamic for capacitors. In [4], [5], the hotspot temperature is calculated using the steady-state thermal resistance of capacitors, which is inaccurate for capacitors in VRMs

In order to fill up the gap of reliability analysis of capacitors in VRMs, this paper investigates the lifetime of hybrid capacitor banks in VRMs. The main contributions are given as follows.

- 1) A thermal model is proposed to describe the temperature dynamic of capacitors in VRMs with consecutive load transients.

- 2) The electro-thermal stresses of capacitors during steady-state and transient processes are analyzed. Then the annual damage of different types of capacitors including non-solid Al-Caps, polymer Al-Caps, and MLC-Caps are investigated.

- 3) A reliability-oriented design method is used to investigate the lifetimes of capacitor banks with different configurations, which provides a reference for capacitor sizing.

The rest of this paper is organized as follows: Section II describes the capacitors functions in VRMs. A reliability analysis procedure of capacitors in VRMs is presented in Section III. Finally, conclusions are drawn in Section IV.

### II. CAPACITORS IN VOLTAGE REGULATOR MODULES

#### A. Electrical Stress of Capacitors in VRMs

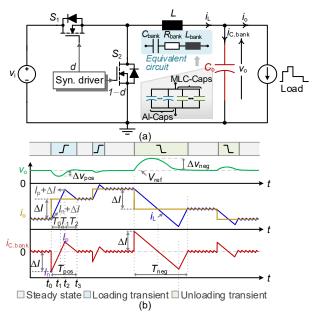

In VRM applications, synchronous buck converters are the most preferred topology, as shown in Fig. 1(a), where the output capacitor bank is composed of Al-Caps and MLC-Caps. The total equivalent series resistance (ESR) of the capacitor bank  $C_{\rm o}$  is defined as  $R_{\rm bank}$ , the total equivalent series inductance (ESL) is  $L_{\rm bank}$ , and its capacitance is defined as  $C_{\rm bank}$ . For VRMs, the amplitude and frequency of loading current ( $i_{\rm o}$ ) step are variable, a typical example of which is shown in Fig. 1(b).

Fig. 1. Topology and key waveforms of a VRM. (a) Topology of a synchronous buck converter. (b) Key waveforms.

In order to achieve an optimal transient performance, some state-of-the-art control techniques including  $V^2$  control [7], time-optimal control [1], [8], etc., have been widely used in VRMs. These control techniques have pushed the transient performance of a VRM close to its physical limit, as shown in Fig. 1(b), where  $v_i$ ,  $v_o$ ,  $i_L$ ,  $i_{C,bank}$  represent the input voltage, output voltage, inductor current, and capacitor current of a capacitor bank, respectively. Before the instant  $t_0$ , the converter works in steady state, the root mean square (RMS) of steady-state capacitor current is calculated as [9],

$$I_{\text{RMS\_steady}} = v_o \left( 1 - d \right) / \left( f_s \sqrt{12} L \right) \tag{1}$$

where  $f_s$ , d, and L denote the switching frequency, duty cycle, and inductance, respectively.

At  $t_0$ , a positive load current step  $\Delta I$  occurs (i.e., a loading transient), which causes a capacitor current step. At  $t_3$ , the output voltage again reaches to the reference voltage  $V_{\rm ref}$ . The RMS value of the capacitor current during the loading transient is calculated as [9]

$$I_{\text{RMS\_pos}} = \sqrt{\frac{I_{\text{n}}^2 + I_{\text{p}}^2 + I_{\text{n}}I_{\text{p}}}{3} \times \frac{T_0 + T_1}{T_{\text{pos}}} + \frac{I_{\text{p}}^2}{3} \times \frac{T_2}{T_{\text{pos}}}}}$$

(2)

where the current peak values  $I_p$ ,  $I_n$  are

$$I_{\rm n} = -\Delta I, \quad I_{\rm p} = (v_{\rm i} - v_{\rm o})(T_0 + T_1)/L - \Delta I$$

(3)

The transient period  $T_{pos}$ , and the durations  $T_0$  ( $t_0$  to  $t_1$ ),  $T_1$  ( $t_1$  to  $t_2$ ),  $T_2$  ( $t_2$  to  $t_3$ ) can be obtained from [1].

Referring to Fig. 1, the RMS value of the capacitor voltage during steady state equals to  $V_{\rm ref}$ . During transients, the voltage trajectory can be approximated to a half-wave sine curve. The RMS value during the loading transient is calculated as

$$V_{\rm RMS,pos} = V_{\rm ref} - \Delta v_{\rm pos} / \sqrt{2}$$

(4)

where,  $\Delta v_{pos}$  represents the voltage undershoot [1], i.e.,

$$\Delta v_{\text{pos}} = \frac{R_{\text{ESR}}^2 C_{\text{bank}}^2 \left( v_i^2 - 2v_i v_o + v_o^2 \right) + \Delta I^2 L^2}{2 \left( v_i - v_o \right) L C_{\text{bank}}}.$$

(5)

Similarly, the RMS values  $I_{RMS\_neg}$  and  $V_{RMS\_neg}$  of capacitor

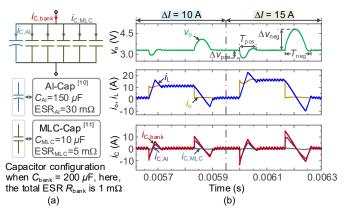

Fig. 2. Simulation results. (a) Capacitor configuration of the capacitor bank when  $C_{\rm bunk}=200~\mu{\rm F}.$  (b) Simulation waveforms of a VRM under different transients.

TABLE I

SIMULATION RESULTS OF THE CAPACITOR CURRENTS

| Operating state            | Total RMS current | RMS value of $i_{C,Al}$ | RMS value of $i_{\rm C,MLC}$ |

|----------------------------|-------------------|-------------------------|------------------------------|

| Steady state               | 0.62 A            | 0.32 A                  | 0.06 A                       |

| $\Delta I = +15 \text{ A}$ | 4.96 A            | 3.68 A                  | 0.26 A                       |

| $\Delta I = -15 \text{ A}$ | 7.89 A            | 5.97 A                  | 0.39 A                       |

current and capacitor voltage during unloading transients can be calculated in the same way.

Considering the current distribution of individual capacitor in capacitor banks, the transient current of k-th capacitor in the bank is calculated as [5]

$$I_{k\_pos} = I_{RMS\_pos} \times C_k / \sum_{i=1}^{n} C_n$$

(6)

where  $C_k$  represents the capacitance of k-th capacitor in the bank, and n is the number of capacitors. Similarly, the current distribution of capacitors during steady state can be calculated using the impedance at the switching frequency.

#### B. Simulation Validation

A 150 W VRM is built in the PSIM simulation environment, the key parameters are given as follows:  $V_i = 12 \text{ V}$ ,  $V_o = 3.3 \text{ V}$ ,  $L = 13 \mu H$ ,  $f_s = 100 \text{ kHz}$ . Taking a 200  $\mu F$  ( $R_{bank} \approx 1 \text{ m}\Omega$ ) capacitor bank as an example, Fig. 2(a) shows the capacitor configuration, where two different types of capacitors are considered. The types of Al-Caps and MLC-Caps are PSLP8075105142006 (150  $\mu$ F/ 6.3 V, ESR<sub>Al</sub> = 30 mΩ [10]) and GRM185R60J106ME15 (10  $\mu$ F/ 6.3 V, ESR<sub>MLC</sub> = 5 m $\Omega$  [11]), respectively. Notice that the capacitor current of these four MLC-Caps  $i_{C,MLC}$  are the same due to the same capacitor parameters, the capacitor current of the Al-Caps is denoted as  $i_{\text{C,Al}}$ . Two different load steps are chosen as examples, i.e.,  $\Delta I =$ 10 A and  $\Delta I = 15$  A, Fig. 2(b) shows the steady-state and transient waveforms of  $v_0$ ,  $i_L$ ,  $i_0$ ,  $i_{C,bank}$ ,  $i_{C,Al}$ , and  $i_{C,MLC}$ . It is found that the voltage deviations  $\Delta v_{pos}$ ,  $\Delta v_{neg}$  and setting time  $T_{\text{pos}}$ ,  $T_{\text{neg}}$  for different transients are different.

To verify the current distribution of the capacitor bank, Table I lists the simulation results of the capacitor current during steady-state and the 15 A load transient, which are approximately equal to the calculation results in (6). Moreover, Fig. 2(b) illustrates that  $i_{C,bank} = i_L - i_o$ , so the total RMS values of capacitor banks can be calculated using  $i_L$  and  $i_o$ .

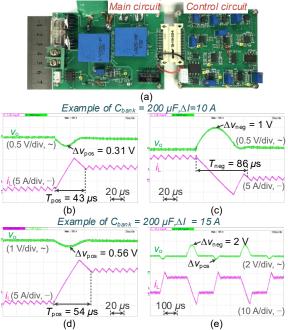

Fig. 3. Experimental results (a) Photo of the built VRM. (b) Loading transient when  $\Delta I = 10$  A. (c) Unloading transient when  $\Delta I = 10$  A. (d) Loading transient when  $\Delta I = 15$  A. (e) Repetitive transient when  $\Delta I = 15$  A.

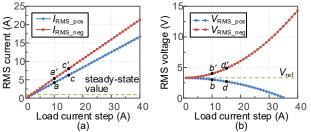

Fig. 4. Capacitor current and capacitor voltage RMS values under different load current steps. (a) Capacitor current RMS values. (b) Capacitor voltage RMS values.

#### C. Experimental Validation

Fig 3(a) shows the built VRM, which uses the same parameters in simulation. Figs. 3(b) and (c) show the experimental results of loading transient and unloading transient when  $\Delta I = 10$  A. Figs. 3(d) and (e) show the experimental results of loading transient and repetitive transient when  $\Delta I = 15$  A [8]. Referring to Figs. 3(b) and (d), it is found

that the voltage undershoots  $\Delta v_{\rm pos}$  and setting time  $T_{\rm pos}$  for different transients are different. Moreover, the calculated RMS values for a 10 A load transient are  $I_{\rm RMS\_pos} = 3.45$  A,  $I_{\rm RMS\_neg} = 4.82$  A,  $V_{\rm RMS\_pos} = 3.1$  V,  $V_{\rm RMS\_neg} = 4.0$  V, which are consistent with the theoretical values in Fig. 4 (i.e., points a, a', b, and b'). The calculated RMS values for a 15 A load transient are  $I_{\rm RMS\_pos} = 5.61$  A,  $I_{\rm RMS\_neg} = 7.51$  A,  $V_{\rm RMS\_pos} = 2.9$  V,  $V_{\rm RMS\_neg} = 4.71$  V, which are also consistent with the theoretical values in Fig. 4 (i.e., points c, c', d, and d'). Based on the calculated  $I_{\rm RMS\_pos}$  and  $I_{\rm RMS\_neg}$ , the RMS current for each individual capacitor can be derived using (6).

Moreover, the theoretical results in Fig. 4 illustrate that the RMS currents during transients are larger than for the steady-state. For capacitor current during transients, the RMS current increases as the load current step increases. For capacitor voltage during transients, RMS voltage during unloading transients increases as the load step  $\Delta I$  increases. And, the RMS voltage during loading transients decreases as  $\Delta I$  increases.

# III. RELIABILITY-ORIENTED DESIGN OF CAPACITORS IN VRMs

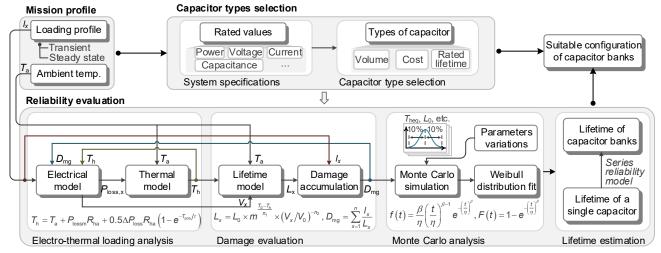

The procedure for designing the capacitor bank of VRMs is shown in Fig. 5, which are detailed discussed in the following.

#### A. Mission Profile and Capacitor Types Selection

VRMs are widely used as power supplies for various node components in data centers. The daily ambient temperature of a data center [12] with a sample rate of one hour is shown in Fig. 6(a). In order to obtain the detailed load transient information, a short time-scale loading profile is considered, as shown in Fig. 6(b) [13], it is found that the load current fluctuates continuously. As the loading step frequency of VRMs is usually larger than 1 kHz [6], here, the sampling frequency  $f_{\text{samp}}$  is defined as 2 kHz.

Referring to Fig. 5, the capacitor types can be selected based on the mission profile and system specifications. In this case study, the output voltage of the VRM is 3.3 V, three different types of capacitors with a rated voltage of 6.3 V are considered. Detailed parameters of capacitors are shown in Table II, where  $R_{\rm ha}$  and  $\tau_{\rm ha}$  represent the thermal resistance and thermal time constant from the hotspot to ambient, respectively.

Assuming the design aim of the VRM is to keep the maximum voltage undershoot (e.g.,  $\Delta I = 15$  A) within 5% of the steady-state reference value.

Fig. 5. Reliability-oriented design of capacitor banks in VRMs

Fig. 6. Mission profile of VRMs in a data center. (a) Daily ambient temperature in a data center. (b) Loading profile of a VRM in a specified period.

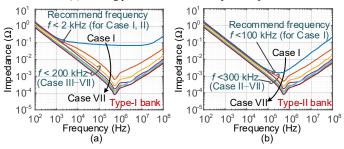

Fig. 7. Impedance characteristics of hybrid capacitor banks. (a) Capacitor banks consisting of non-solid Al-Caps and MLC-Caps. (b) Capacitor banks consisting of polymer Al-Caps and MLC-Caps.

# $\label{thm:table II} \textbf{SPECIFICATIONS} \ \textbf{AND} \ \textbf{PARAMETERS} \ \textbf{OF} \ \textbf{EMPLOYED} \ \textbf{AL-CAPS} \ \textbf{AND} \ \textbf{MLC-CAPS}$

| Parameter                      | Non-solid Al-Cap:<br>WCAP-ASLI | Polymer Al-Cap:<br>WCAP-PSLP   | MLC-Cap: ZRB<br>GRM185R60J106ME15, |  |  |

|--------------------------------|--------------------------------|--------------------------------|------------------------------------|--|--|

|                                | 865060143005<br>[10]           | 875105142006<br>[10]           | GRM21BR60J107ME15<br>[11]          |  |  |

| Dimension                      | 43.6×5.5 mm                    | 28.1×5.5 mm                    | 1.3×0.5 mm<br>2.5×1.25 mm          |  |  |

| Rated capacity                 | 150 μF/6.3V                    | 150 μF/6.3 V                   | 10μF/6.3 V<br>100μF/6.3 V          |  |  |

| Initial ESR                    | 510 mΩ<br>@ 100 kHz, 20 °C     | 30 mΩ<br>@ 100 kHz, 20 °C      | 5 mΩ, 1 mΩ<br>@ 100 kHz, 25 °C     |  |  |

| Rated                          | 2000 h [10]                    | 2000 h [10]                    | 1000 h [14]                        |  |  |

| lifetime  R <sub>ha</sub> [15] | @ +105 °C, 6.3 V<br>55.6 °C/W  | @ +105 °C, 6.3 V<br>133.1 °C/W | @ +85 °C, 12.6 V<br>22.9 °C/W      |  |  |

| τ <sub>ha</sub> [16],[17]      | 40 s                           | 83.9 s                         | 0.14 s                             |  |  |

According to the calculation results in (5), a 1000 µF capacitor bank is required. The possible combinations of capacitor bank are listed in Table III. Notice that the configurations of capacitor banks consider the influence of voltage on the capacitance of MLC-Caps. There exist 7 different configurations, the impedance characteristics of these capacitor banks are shown in Fig. 7, where Fig. 7(a) shows the impedance characteristics for capacitor banks consisting of non-solid Al-Caps and MLC-Caps (i.e., Type I), Fig. 7(b) shows that for capacitor banks consisting of polymer Al-Caps and MLC-Caps (i.e., Type II). It should be noted that the impedance data of MLC-Caps are obtained at 0 V/25 °C [11]. Generally, the recommended operating frequencies f of capacitor banks are at the frequency band in which the impedance is dominated by capacitance, as shown in Fig. 7.

## B. Reliability Analysis of a Single Capacitor

The procedure to assess reliability is shown in the bottom of Fig. 5, which mainly includes four steps. Notice that the feedback loops from the hotspot temperature  $T_{\rm h}$  and the accumulated damage  $D_{\rm mg}$  to the electrical model represent ESR and C degradation. Taking the capacitor bank configuration in Case IV as an example, the reliability evaluation process is given as follows.

### 1) Electro-thermal loading analysis

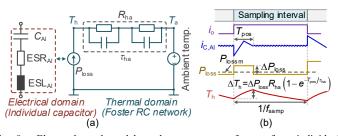

Thermal stress is the critical stressor of capacitors' wear-out

Fig. 8. Electro-thermal models and response waveforms of an individual capacitor under consecutive load transients. (a) Electro-thermal models. (b) Electro-thermal response waveforms.

# TABLE III DIFFERENT CONFIGURATIONS OF CAPACITOR BANKS

| Capacitor types [10], [11]            | Number of capacitors in different configuration cases |      |      |      |      |      |      |

|---------------------------------------|-------------------------------------------------------|------|------|------|------|------|------|

|                                       | Case                                                  | Case | Case | Case | Case | Case | Case |

| [10], [11]                            | I                                                     | II   | III  | IV   | V    | VI   | VII  |

| 150 μF Non-solid or<br>Polymer Al-Cap | 7                                                     | 6    | 5    | 4    | 3    | 2    | 1    |

| 100μF MLC-Cap<br>(35μF @ 3.3V)        | 0                                                     | 3    | 7    | 11   | 15   | 20   | 24   |

| 10μF MLC-Cap II<br>(3.5μF @ 3.3V)     | 0                                                     | 0    | 2    | 5    | 8    | 0    | 3    |

failure, which is mainly caused by the rise of the hotspot temperature of capacitors. Taking an AL-Cap as an example, the electro-thermal model is shown in Fig. 8(a) [4], the hotspot temperature  $T_h$  of capacitors is affected by the ambient temperature  $T_a$  and power loss of capacitors. Taking the loading transient as an example, Fig. 8(b) shows the electro-thermal response waveforms of capacitors.

Based on the Foster RC network model, the hotspot temperature fluctuation caused by step loss  $\Delta P_{\rm loss}$  is calculated as [18]

$$\Delta T_{\rm h} = \Delta P_{\rm loss} R_{\rm ha} \left( 1 - e^{-T_{\rm pos}/\tau_{\rm ha}} \right) \tag{7}$$

According to Fig. 8(b),  $T_h$  during one sampling interval (i.e., one load step period,  $1/f_{samp}$ ) is approximately calculated as

$$T_{\rm h} = T_{\rm a} + P_{\rm lossm} R_{\rm ha} + 0.5 \Delta P_{\rm loss} R_{\rm ha} \left( 1 - e^{-T_{\rm pos}/\tau_{\rm ha}} \right)$$

(8)

where  $P_{\rm lossm}$  represents the mean loss and step loss of capacitors during this sampling interval, which can be calculated based on  $P_{\rm loss}$ . Furthermore,  $P_{\rm loss}$  is calculated as  $P_{\rm loss} = {\rm ESR_{Al}} \cdot I_{\rm RMS,Al}^2$ , where  $I_{\rm RMS,Al}$  represents the RMS current of an individual Al-Cap at different transient modes.  $T_{\rm h}$  can be approximate as  $T_{\rm h} = T_{\rm a} + P_{\rm lossm} \times R_{\rm ha}$  when  $\tau_{\rm ha} >> T_{\rm pos}$ . Here, the mean loss  $P_{\rm lossm}$  can be calculated using the mean value of multiple sampling intervals. Then,  $T_{\rm h}$  represents the hotspot temperature for multiple intervals. Notice that the thermal model is also suitable for other types of capacitors in capacitor banks.

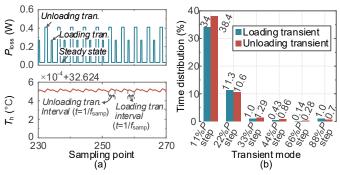

Based on the foregoing analysis, the hotspot temperature of capacitors can be calculated using the sampling interval as unit. Referring to Fig. 6(b), the current during sampling points 230 to 270 are repetitive with  $\pm 10$  A steps. Taking these sampling intervals as an example, Fig. 9(a) shows the power loss (the top part) and temperature profile (the bottom part) of individual Al-Cap in the capacitor bank (i.e., Case IV). Here, the current distribution of different capacitors is considered. Referring to Fig. 9(a),  $P_{\text{lossm}}$  for an unloading transient interval and a loading transient interval are 0.19 W and 0.08 W, respectively. Based on (8),  $T_{\text{h}}$  for these two intervals are 35.56 °C and 29.45 °C, respectively. The mean value of  $T_{\text{h}}$  during these two intervals is 32.5 °C, which is consistent with the simulated  $T_{\text{h}}$  based on the total interval (i.e., sampling point from 230 to 270). The simulation results are consistent with the theoretical results from

Fig. 9. Thermal simulation waveforms and transient mode distribution. (a) Simulation waveforms of the non-solid Al-Cap in the bank (Case IV). (b) Transient mode distribution.

TABLE IV Summary of the Lifetime Model Parameters Used in (9)

| Parameters | Non-solid Al-Cap [4] | Polymer Al-Cap [3] | MLC-Cap [19] |

|------------|----------------------|--------------------|--------------|

| m          | 2                    | 10                 | 2            |

| $n_1$      | 10                   | 20                 | 8            |

| $n_2$      | 0                    | 0                  | 3            |

### (8), which illustrates the feasibility of this thermal model.

In this case study, the power steps are divided into six typical values for the sake of simplicity, i.e., 11%P, 22%P, 33%P, 44%P, 66%P, and 88%P, where P represents the rated power of a VRM. Assuming that the mission profile in Fig. 6(b) is repeated every 0.35 s, the time distribution of different transient models is shown in Fig. 9(b).

#### 2) Accumulated damage evaluation

The widely used lifetime model and accumulated damage model for lifetime evaluation of capacitors are [3], [4], [19]

$$L_{x} = L_{0} \times m^{\frac{T_{0} - T_{h}}{n_{1}}} \times (V_{x} / V_{0})^{-n_{2}}, D_{mg} = \sum_{x=1}^{n} \frac{I_{x}}{L_{x}}$$

(9)

where  $L_0$ ,  $V_0$ , and  $T_0$  denote the rated lifetime, rated voltage, and hotspot temperature under the reference condition,  $l_x$ ,  $L_x$ ,  $V_x$ , and  $T_h$  represent the operation time, calculated lifetime, capacitor voltage, and hotspot temperature under the used conditions. The coefficient m,  $n_1$ , and  $n_2$  denote the temperature coefficient, temperature-dependent constant, and voltage stress exponent respectively, which are summarized in Table IV.

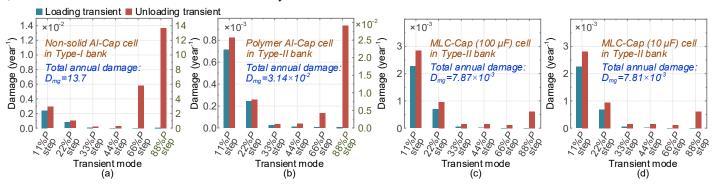

According to the mission profile, the annual damage of each type of capacitor cell can be calculated, as shown in Fig. 10, where Fig. 10(a) shows the result for the non-solid Al-Cap in Type-I bank, Figs. 10(b)–10(d) show the results for the polymer Al-Cap and the MLC-Cap (100  $\mu$ F and 10  $\mu$ F) in Type-II bank. Referring to Fig. 10(a), it can be seen that the damage consumption of the non-solid Al-Cap ( $D_{\rm mg}=13.7$ ) is larger than 1, which illustrates that its lifetime is shorter than 1 year.

From Figs. 10(b)-10(d), it is found that the polymer Al-Cap  $(D_{\rm mg} = 3.14 \times 10^{-2})$  has relatively low annual damage. And the damage for the MLC-Caps ( $D_{\rm mg}$  equals to  $7.87\times10^{-3}$  and 7.81×10<sup>-3</sup>) are the lowest. For Al-Caps, the wear-out failure is mainly caused by the current stress [2]. From Fig. 10, it is easily found that the majority of damage consumption of Al-Caps occurs during the 88%P step period due to the highest current stress [i.e., thermal stress, c.f. (8)] on capacitors in this mode. Different from that, the majority of damage consumption of MLC-Caps mainly occurs during the 11%P step period due to the operation time of this mode is longest. Here, the failure is dominated by voltage stress due to the thermal stress on MLC-Caps is relatively small (as the ESR is very small). Taking 22%P step as an example, it is found that the damage consumption during unloading transient is larger than that during loading transient due to larger voltage and current stresses on capacitors.

#### 3) Monte Carlo analysis and lifetime evaluation

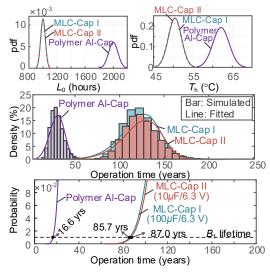

To address the uncertainty in the above mentioned accumulated damage estimation process, a statistical approach based on Monte Carlo simulation is introduced to the estimation process. Assuming that all the variations of parameters obey the normal distribution, 100000 samples are chosen to analyze the time-to-failure of capacitors, as shown in Fig. 11. Here,  $T_{\rm heq}$ ,  $L_0$ , and  $V_0$  (similar to the distribution of  $T_{\rm heq}$  and  $L_0$ , which is not shown in Fig. 11) are considered to have a 10% variation, respectively. Notably  $T_{\rm heq}$  is the equivalent hotspot temperature calculated from  $D_{\rm mg}$ . Usually, the time-to-failure of samples obey with Weibull distribution [4], i.e.,

$$f(t) = (\beta/\eta) \cdot (t/\eta)^{\beta-1} e^{-\left(\frac{t}{\eta}\right)^{\beta}}, F(t) = 1 - e^{-\left(\frac{t}{\eta}\right)^{\beta}}$$

(10)

where,  $\beta$  and  $\eta$  represent the shape parameter and the scale parameter, respectively. Based on this, the histograms of years to failure and failure probability for different types of capacitors are shown in Fig. 11. It is found that the  $B_1$  lifetimes of polymer Al-Caps and MLC-Caps are approximately equaled to 16.6 and

Al-Caps and MLC-Caps are approximately equaled to 16.6 and 85.7 (or 87) years, respectively.

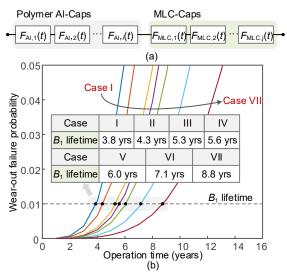

## 4) Reliability analysis of hybrid capacitor banks

Table V lists the total volumes and costs for each capacitor bank configuration (i.e., Case I to Case VII in Table III), where the non-solid Al-Cap is not considered due to its lifetime is less than 1 year. In Table V, the total volume is approximately calculated as the total base area of capacitors multiply the maximum height.

Based on the series reliability model in Fig. 12(a) [4], the wear-out failure probability curves of capacitor banks are shown in Fig. 12(b). It is found that the lifetime of the capacitor bank

Fig. 10. Annual damage for different types of capacitor cells. (a) Annual damage of non-solid Al-Cap cell in Type-II bank. (b) Annual damage of polymer Al-Cap cell in Type-II bank. (c) Annual damage of MLC-Cap (100  $\mu$ F) cell in Type-II bank. (d) Annual damage of MLC-Cap (100  $\mu$ F) cell in Type-II bank.

Fig. 11. Monte Carlo simulation results for capacitors in a bank (Case IV).

Fig. 12. Wear-out probability curves of different capacitor bank configurations. (a) Series reliability model. (b) Wear-out probability curves.

TABLE V

COMPARISON OF THE TOTAL VOLUMES AND COSTS FOR EACH CASE

| COMPARISON OF THE TOTAL VOLUMES AND COSTSTOR EACH CASE |           |            |             |            |           |            |             |

|--------------------------------------------------------|-----------|------------|-------------|------------|-----------|------------|-------------|

| Capacitor types                                        | Case<br>I | Case<br>II | Case<br>III | Case<br>IV | Case<br>V | Case<br>VI | Case<br>VII |

| Total volume (base                                     | 196.7     | 176.1      | 160.1       | 146.3      | 132.1     | 106.2      | 91.9        |

| area × height, mm)                                     | × 5.5     | × 5.5      | × 5.5       | × 5.5      | × 5.5     | × 5.5      | × 5.5       |

| Cost (USD)                                             | 3.57      | 3.69       | 6.25        | 8.89       | 11.53     | 13.96      | 16.6        |

increases as the number of employed polymer Al-Caps decreases. For Case I, the  $B_1$  lifetime is 3.8 years, which is significantly shorter than 8.8 years for Case VII. Moreover, the total volume of Case VII is smaller than that for Case I. However, the total cost of Case VII is higher than that for Case I. From the perspective of reliability, it is recommended to reduce the number of polymer Al-Caps to improve the reliability of the capacitor bank.

#### IV. CONCLUSION

This paper investigates the lifetime of capacitors in VRMs with consecutive load transients. Based on a case study (a 150 W VRM), the electro-thermal stresses, annual damage, estimated lifetime of capacitors are analyzed. The main conclusions are as follows:

1) The damage consumption of Al-Caps mainly occurs during the transient with higher current stress. The majority of damage consumption of MLC-Caps occurs during the transient with longer operation time.

- 2) The lifetime of non-solid Al-Cap in VRMs is less than 1 year, which illustrates that it is not suitable for VRMs.

- 3) For hybrid capacitor banks consisting of polymer Al-Caps and MLC-Caps, reduction of the number of polymer Al-Caps can improve the reliability of capacitor banks while reducing the total volume of capacitors. However, the total cost of capacitor banks is increased.

- 4) For VRMs consisting of multiphase buck converters with different types of capacitors and different rated power, the evaluation method of lifetime for capacitors is the same.

#### REFERENCES

- [1] E. Meyer, Z. Zhang, and Y.-F. Liu, "An optimal control method for buck converters using a practical capacitor charge balance technique," *IEEE Trans. Power Electron.*, vol. 23, no. 4, pp. 1802–1812, Jul. 2008.

- [2] H. Wang and F. Blaabjerg, "Reliability of capacitors for dc-link applications in power electronic converters-an overview," *IEEE Trans. Ind. Appl.*, vol. 50, no. 5, pp. 3569–3578, Sep. 2014.

- [3] Nichicon, Corp., Kyoto, Japan, "Estimated life calculator for capacitors," 2020.[Online]Available:https://www.nichicon.co.jp/english/products/lifetim e/solid01.html?sr=PCF

- [4] D. Zhou, H. Wang, and F. Blaabjerg, "Mission profile based system-level reliability analysis of DC/DC converters for a backup power application," *IEEE Trans. on Power Electronics*, vol. 33, no. 9, pp. 8030-8039, Sept. 2018.

- [5] H. Wang and H. Wang, "Capacitive dc links in power electronic systemsreliability and circuit design," *Chinese Journal of Electrical Engineering*, vol. 4, pp. 29–36, Sep. 2018.

- [6] Voltage regulator module (VRM) and Enterprise Voltage Regulator-Down (EVRD) 11.0, Intel Corp., Hillsboro, OR, USA, Sep. 2009.

- [7] Y. Yan, F.C. Lee, S. Tian, and P. Liu, "Modeling and design optimization of capacitor current ramp compensated constant on-time V<sup>2</sup> control," *IEEE Trans. Power Electron.*, vol. 33, no. 8, pp. 7288–7296, Aug. 2018.

- [8] Z. Zhao, W. G. Lu, W. Chen, X. Du and H. H. Iu, "Multi-Period Frame Transient Switching Control for Low-Voltage High-Current Buck Converter with a Controlled Coupled Inductor," *IEEE Trans. Power Electron.*, vol. 34, no. 10, pp. 9743-9757, Oct. 2019.

- [9] S. Maniktala, Switching Power Supplies A to Z. Newnes, London-UK, Jun. 22, 2006.

- [10] Wurth Electronics Group, Germany, "Aluminum electrolytic/Aluminum polymer capacitors," 2020. [Online]. Available: https://redexpert.weonline.com/redexpert/#/module/20/productdata/=861140783006

- [11] muRata, Nagaokakyo, Japan, "Multilayer ceramic capacitor," 2020.

[Online]. Available: https://ds.murata.co.jp/simsurfing/mlcc.html?lcid=en-

- [12] Jimil M. Shah, "Reliability challenges in airside economization and oil immersion cooling", The University of Texas at Arlington, May 2016.

- [13] M. Rashti, G. Sabin and B. Norris, "Power and energy analysis and modeling of high performance computing systems using WattProf," in *Proc.* 2015 NAECON, Dayton, OH, 2015, pp. 367-373.

- [14] KEMET, Fort Lauderdale, USA, "Surface mount multilayer ceramic chip capacitors," 2020. [Online]. Available: https://content.kemet.com/datasheets/KEM\_C1005\_Y5V\_SMD.pdf

- [15] Murata Manufacturing Co., Ltd., Kyoto, Japan, "Polymer capacitor basics," 2015. [Online]. Available: https://article.murata.com/en-eu/article/polymer-capacitor-basics-part-2

- [16] T. Furukawa, D. Senzai and T. Yoshida, "Electrolytic capacitor thermal model and life study for forklift motor drive application," in *Proc.* 2013 EVS27, Barcelona, 2013, pp. 1-6.

- [17] Z. Sarkany, M. Rencz, "A Way for Measuring the Temperature Transients of Capacitors", Adv. Sci. Technol. Eng. Syst. J., vol. 2, no. 3, pp. 1381-1389, 2017

- [18] Toshiba, Tokyo, Japan, "Power mosfet thermal design and attachment of a thermal fin," 2020. [Online]. Available: https://toshiba.semiconstorage.com/info/docget.jsp?did=13417

- [19] muRata, Nagaokakyo, Japan, "Ceramic capacitors FAQ," 2020. [Online]. Available: http://www.murata.com/support/faqs/products/capacitor/mlcc/qlty/0010