#### **Aalborg Universitet**

#### Modeling and Reducing the Parasitic Capacitance in Medium-Voltage Inductors

Zhao, Hongbo

DOI (link to publication from Publisher): 10.54337/aau443223351

Publication date: 2021

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Zhao, H. (2021). Modeling and Reducing the Parasitic Capacitance in Medium-Voltage Inductors. Aalborg Universitetsforlag.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

## MODELING AND REDUCING THE PARASITIC CAPACITANCES IN MEDIUM-VOLTAGE INDUCTORS

#### BY HONGBO ZHAO

**DISSERTATION SUBMITTED 2021**

# MODELING AND REDUCING THE PARASITIC CAPACITANCES IN MEDIUM-VOLTAGE INDUCTORS

by

Hongbo Zhao

Dissertation submitted June 2021

Dissertation submitted: June 2021

PhD supervisor: Prof. Stig Munk-Nielsen

Aalborg Universitet

PhD co-supervisors: Prof. Xiongfei Wang

Aalborg Universitet

Dr. Asger Bjørn Jørgensen

Aalborg Universitet

PhD committee: Associate Professor Florin Iov (chairman)

Aalborg University

Associate Professor Ziwei Ouyang Technical University of Denmark

Professor Jürgen Biela

High Power Electronics, ETH Zürich

PhD Series: Faculty of Engineering and Science, Aalborg University

Department: Department of Energy Technology

ISSN (online): 2446-1636

ISBN (online): 978-87-7210-954-1

Published by:

**Aalborg University Press**

Kroghstræde 3

DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Hongbo Zhao

Printed in Denmark by Rosendahls, 2021

"I think, therefore I am"

— Rene Descartes

#### **ENGLISH SUMMARY**

With the recent advancements of medium-voltage (MV) Silicon Carbide (SiC) metal-oxide-semiconductor field-effect transistor (MOSFET) technology, the MV converters are benefited from simpler circuit topologies, lower switching energy dissipation, and higher switching frequency than conventional Silicon devices. However, the fast switching behaviors (high dv/dt) introduced by MV SiC MOSFETs pose several challenges to the MV inductors, which can introduce significant capacitive current into the system due to the parasitic capacitance of MV inductors. To deal with this challenge holistically, this Ph.D. thesis focuses on developing physics-based and behavior-based modeling methods to characterize the capacitive couplings as well as approaches to reduce the parasitic capacitance of inductors.

The equivalent parasitic capacitance of inductors is frequency-dependent. The physics-based modeling method can predict the equivalent parasitic capacitance of inductors according to the geometrical structure and material parameters before the first resonant frequency. The improper assumptions for physically modeling the equivalent capacitance of inductors at the first resonant frequency is critiqued firstly. Then, a physics-based modeling method for calculating the parasitic capacitance of inductors considering the grounding effects is developed, which uses a three-terminal equivalent circuit to characterize the capacitive couplings of inductors instead of the conventional two-terminal equivalent circuit. Furthermore, the modeling methods of parasitic capacitance considering the fringe electrical field in copper-foiled MV inductors are presented.

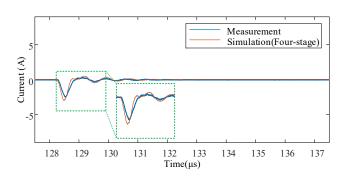

In addition to the physics-based modeling, the behavior-based modeling method can represent the actual couplings by using the time-domain or frequency domain response of the inductors, where the valid frequency range is limited by the bandwidth of the devices that measure the time-domain or frequency-domain signals. A behavioral model of MV inductors is developed. It is firstly obtained from the impedance of the inductor measured by an impedance analyzer. Then, the capacitive coupling between terminal and core of inductors is characterized by using a multistage RLC circuit, the parameters of which are analytically calculated according to the measured impedance. The derived behavior-based model of inductors is finally used to build a digital twin of a double-pulse-test setup, where the simulated ground current shows good agreement with the measurements.

The approaches of reducing parasitic capacitance in MV inductors with multiple windings are further proposed. The physics-based modeling indicates that parasitic capacitance can be reduced by changing the geometrical structures, electrical connections, and winding layout. According to analytical calculations, several prototypes of inductors are manufactured, whose parasitic capacitance is reduced

significantly by using the proposed technologies. However, some of the technologies will sacrifice the power density of winding and may increase the manufacturing cost.

Finally, the remained challenges of modeling the parasitic capacitance of mediumvoltage inductors are summarized. Conclusions and future research are given at the end of this thesis.

The thesis is in a paper-collection type, which is basically combined by five journal papers, two conference papers, and one filed patent by Danish Patent and Trademark Office.

#### **DANSK RESUME**

Grundet de seneste forbedringer i teknologien bag mellemspændings siliciumkarbid (SiC) metal-oxide-semiconductor field-effect transistor (MOSFET), har mellemspændings strømforsyninger set forbedringer i form af simplere kredsløbstopologier, lavere skiftetab og operation ved højere frekvenser, sammenlignet med mellemspændings-systemer baseret på traditionelle silicium komponenter. Men de høje spændingshældninger under tænd/sluk (høj dv/dt), der kan opnås med nye mellemspændings SiC MOSFETs, skaber adskillige udfordringer for mellemspændings-spoler og filtre, da det via spolens kapacitive koblinger kan skabe høje jordstrømme i de effektelektroniske systemer. For at undersøge og klarlægge denne udfordring, fokuserer PhD-afhandlingen på udvikling af både fysik-baserede og system dynamiske modelleringsmetoder, for at kunne karakterisere og løse udfordringerne med kapacitive koblinger i mellemspændings-spoler.

Den ækvivalente kapacitive kobling af en spole er frekvensafhængig. Den fysik-baserede modelleringsmetode kan estimere den ækvivalente kapacitive kobling med udgangspunkt i den geometriske struktur og materiale-parametre gældende op til den første resonansfrekvens. En række unøjagtige antagelser om den fysik-baserede model op til første resonansfrekvens adresseres. Dernæst præsenteres en fysik-baseret modelleringsmetode til at udregne den kapacitive kobling i spoler, inklusiv dets effekter ved jording. Metoden bruger et tre-terminals ækvivalentkredsløb til at karakterisere de kapacitive koblinger, i stedet for det konventionelle to-terminals ækvivalentkredsløb for en spole. Herefter præsenteres en modelleringsmetode af den kapacitive kobling, som også tager højde for kant-effekter i de elektriske felter i kobberfolie mellemspændingsspoler.

I tillæg til den fysik-baserede model, kan system-dynamikken af de faktiske koblinger modelleres ved brug af tids- og frekvens-responset af spolen. Modellens nøjagtighed er begrænset af båndbredden af det udstyr der måler tids- eller frekvens-responset. En model af mellemspændings-spolens dynamik præsenteres, udregnet fra den målte frekvensafhængige impedans. Dernæst er den kapacitive kobling mellem spolens terminaler og kerne karakteriseret, ved brug af et stigenetværk af RLC-kredsløb, hvor dets parametre er analytisk udregnet fra det målte impedans-respons. Den udviklede model af spolen benyttes slutteligt, til at opbygge en digital tvilling af en double-pulsetest opstilling, hvor den simulerede strøm i spolens jordforbindelse viser god overensstemmelse med de eksperimentielle målinger.

Herefter præsenteres teknikker til at reducere de kapacitive koblinger i mellemspændings-spoler med flere viklinger. Den fysik-baserede modelleringsmetode indikerer at den kapacitive kobling kan reduceres ved at ændre den geometriske struktur, de elektriske forbindelser og viklings-layout. Med udgangspunkt i analytiske udregninger, og ved brug af de præsenterede teknikker,

fremstilles adskillige prototyper af spoler, hvis kapacitive koblinger er reduceret markant. Men nogle af de fremsatte teknikker sker på bekostning af nedsat effektdensitet af vindingerne eller en forøgelse af fremstillingsomkostningerne.

Til slut er de tilbageværende udfordringer ved modellering af kapacitive koblinger i mellemspændingsspoler opsummeret. Konklusioner og fremtidig forskning er givet sidst i afhandlingen.

Afhandlingen er opbygget på baggrund af en samling af videnskabelige artikler, herunder: fem tidsskrift-bidrag, to konference-artikler og et ansøgt patent indsendt til Patent- og Varemærkestyrelsen i Danmark.

#### **ACKNOWLEDGEMENTS**

At the final milestone of my formal education, it is significant to reflect on the individuals and organizations who have contributed to my development. However, it is impossible to completely list every technical, emotional, and financial support that I have received during the three-year Ph.D. study in such a small space.

My greatest gratitude goes to my Ph.D. supervisor, Prof. Stig Munk-Nielsen. I appreciate his trust in enrolling me as a Ph.D. student in 2018. I benefit a lot from his enthusiasm, expertise, and industry knowledge, which inspire me to explore more research questions. Without his encouragement, support, and continuous optimism to my Ph.D. project, it would have been hardly completed.

I gratefully acknowledge the contributions of my co-supervisor, Prof. Xiongfei Wang. He has worked with me many late nights, helping me develop critical and structural thinking, suggesting perspective and interesting research topics, and examining some technical details. I also appreciate another co-supervisor Dr. Asger Bjørn Jørgensen, for his guidelines in helping me understand power modules. His rich knowledge in finite-element methods has inspired me a lot during the research.

It is a great pleasure to work with Prof. Alex Hanson, who is the host supervisor of my virtual study-abroad project at the University of Texas at Austin. I am impressed by his insightful and construable suggestions to my research as well as his rigorous attitude for research.

My office mates and friends, Mr. Dipen Narendra Dalal, Mr. Thore Stig Aunsborg, and Mr. Jannick Kjær Jørgensen, have spent numerous hours in argument and debate about every topic in power electronics, and every other topic as well. Dipen and I have spent countless hours drinking coffee and tea, debugging prototypes, and even investigating the difference between Chinese and Indian philosophy. Jannick taught me in FEM simulations with his professional background as a physicist. I enjoyed the stay with Thore at Lisbon in 2019, where we have measured the size of Lisbon with our feet. It is doubtful that I would have survived my Ph.D. project without the special brand of humor from my office mates.

I am thankful to Dr. Bjørn Rannestad with KK wind solutions for his suggestions and organizations, who is the leader of my work packages in both MVBASIC and MVOLT project. I benefited a lot from the weekly project coordinating meeting managed by him. I want to acknowledge Prof. Christian Uhrenfeldt, Prof. Szymon Michal Beczkowski, Prof. Michael Møller Bech, and Prof. Christian Vasile Lascu, for the beneficial intern discussions about magnetic modeling and system integration.

I am forever thankful to my colleagues and friends, Dr. Zhan Shen, Mr. Faheem Ahmad, Mr. Jonas Jacobsen, Dr. Prasun Mishra, Dr. Sung-young Song, Dr. Songda Wang, Dr. Yingzhou Peng, Mr. Rui Wang, Mr. Shaokang Luan, Miss. Yuan Gao, Dr.

Shuhan Zhou, Mr. Guihua Mao, Miss. Xinrong Huang, Dr. Wenjie Liu, Prof. Haoran Wang, Prof. Qian Wang, Dr. Chao Wu, Mr. Jinkui He, Dr. Zhizhao Huang, Dr. Zhaoyang Zhao, Dr. Heng Wu, Dr. Hong Gong, Mr. Mengfan Zhang, Dr. Zheming Jin, Dr. Teng Liu, Dr. Fangzhou Zhao, Dr. Bo Fan, Dr. Yi Zhang, Miss Yunfeng Li, Dr. Mengxin Chen, Dr. Zhongting Tang, Mr. Wenbin Yuan, Mr. Jiahui Wu and so on. I enjoyed every second of discussions and chatting with them, and thanks for creating a dynamic and open working environment together.

I would like to acknowledge Prof. Francesco Iannuzzo and Prof. Pooya Davari with Aalborg University and Prof. Eckart Hoene with Fraunhofer IZM, where I enjoyed and learned a lot about power electronics from the Ph.D. courses lectured by them. I appreciated a lot since they have spent many hours discussing my questions after class. Beyond all doubts, the knowledge will benefit my entire life career. I also want to show my thanks to Dr. Yang Yang, from Simpson Querrey Institute at Northwestern University, for sharing his rich insights into the dielectric material and circuit theory with me.

I would like to thank my Ph.D. assessment committee members, Prof. Florin Iov of Aalborg University, Prof. Jürgen Biela from the Swiss Federal Institute of Technology in Zurich, Prof. Ziwei Ouyang from the Technical University of Denmark, and all the anonymous reviewers and editors of my papers, for their critical comments and constructive suggestions on my research.

Financial support has been received from two resources. The first two-year of my Ph.D. project is supported by Medium Voltage Converters based on SiC (MVBASIC), which is funded by the Department of Energy Technology, Aalborg University. The last year of my Ph.D. project was supported by Medium Voltage Power Electronics for Wind Systems (MVOLT), which is co-funded by Innovation Fund Denmark, Aalborg University, Siemens Gamesa Renewable Energy, Vestas Wind System, and KK Wind Solutions. I am indebted to all the related staff in the Department of Energy Technology for their excellent administrative works and all experts in MVBASIC and MVOLT project for their professional suggestions.

Finally, my deep and sincere gratitude to my parents for their continuous and unparalleled love, help and support. My wife, Dr. Yicheng Liao sat through many soliloquies on modeling of power converters and components, machine learning, complex network theory and never batted an eye. Of course, we have significant improvements in culinary skills after the three-year stay in Denmark. This journey would not have been possible if not for her, and I dedicate this milestone to her.

Hongbo Zhao

#### **TABLE OF CONTENTS**

| Chapter 1. Introduction                                                     | 17   |

|-----------------------------------------------------------------------------|------|

| 1.1 Background and motivation                                               | . 17 |

| 1.2 State of the art                                                        | . 18 |

| 1.2.1 Physics-based modeling methods                                        | . 18 |

| 1.2.2 Behavior-based modeling methods                                       | . 21 |

| 1.2.3 Methods for reducing parasitic capacitance                            | . 22 |

| 1.3 Reminded challenges                                                     | . 22 |

| 1.4 Objectives                                                              | . 23 |

| 1.5 Hypothesis and methodology                                              | . 24 |

| 1.6 Thesis outline and contributions                                        | . 24 |

| 1.7 Related publications and patents                                        | . 26 |

| Chapter 2. Physics-Based Modeling Method                                    | 29   |

| 2.1 Proper and improper assumptions                                         | . 29 |

| 2.1.1 The original equivalent circuit                                       | . 29 |

| 2.1.2 Contradiction.                                                        | . 31 |

| 2.1.3 Evaluation of model assumptions                                       | . 32 |

| 2.1.4 Summary                                                               | . 36 |

| 2.2 Physics-based modeling methods with considering ground effects          | . 37 |

| 2.2.1 Capacitive couplings in a typical Medium Voltage inductor             | . 37 |

| 2.2.2 Static and dynamic capacitance                                        | . 39 |

| 2.2.3 Experimental verifications                                            | . 42 |

| 2.2.4 Summary                                                               | . 45 |

| 2.3 Physics-based modeling methods with considering electrical fringe field | . 45 |

| 2.3.1 An medium-voltage copper-foiled inductor                              | . 45 |

| 2.3.2 The electrical Fringe field                                           | . 47 |

| 2.3.3 Static and dynamic capacitance contributed by electrical Fringe field | . 48 |

| 2.3.4 Experimental verification                                             | . 53 |

| 2.3.5 Summary                                                               | 55   |

| 2.4 Physics-based modeling methods without using floating voltage potential 55 |

|--------------------------------------------------------------------------------|

| 2.4.1 Improved physics-based modeling method                                   |

| 2.4.2 Experimental verifications                                               |

| 2.4.3 Summary                                                                  |

| Chapter 3. Behavior-Based Modeling Method61                                    |

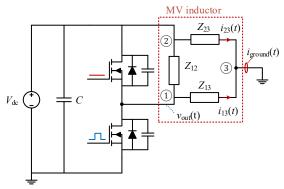

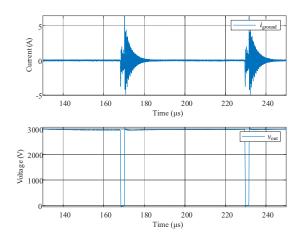

| 3.1 Measurement of common-mode impedance by using double-pulse-test setup      |

| 3.1.1 Double-pulse-test setup                                                  |

| 3.1.2 Principle of the impedance measurement                                   |

| 3.1.3 Experimental verifications                                               |

| 3.1.4 Summary                                                                  |

| 3.2 Behavior-based modeling method using transfer functions                    |

| 3.2.1 Basic Principle                                                          |

| 3.2.2 Simulations and experimental verifications                               |

| 3.2.3 Summary                                                                  |

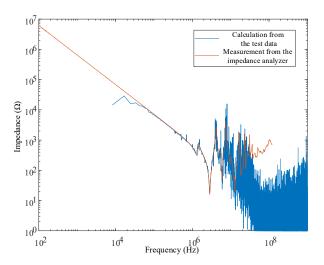

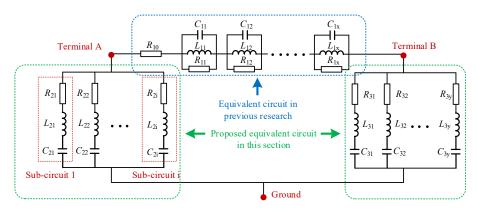

| 3.3 Behavior-based modeling method using equivalent circuit                    |

| 3.3.1 Derivation of the proposed equivalent circuit                            |

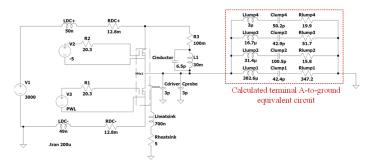

| 3.3.2 Digital-twin simulations and experimental verifications                  |

| 3.3.3 Summary                                                                  |

| Chapter 4 Reducing Parasitic Capacitance in MV Inductors                       |

| 4.1 Case studies                                                               |

| 4.1.1 Conventional design                                                      |

| 4.1.2 Improved design                                                          |

| 4.1.3 Calculations and verification                                            |

| 4.2 Design-oriented guidelines                                                 |

| 4.3 Summary                                                                    |

| Chapter 5. Conclusions and Prospects                                           |

| 5.1 Conclusions 89                                                             |

| 5.2 Prospects                                                                  |

| Bibliography93                                                                 |

| Appended Publications103                                                       |

#### **TABLE OF FIGURES**

| Fig. 1-1 3-dimension CAD model of a toroid inductor                                       |

|-------------------------------------------------------------------------------------------|

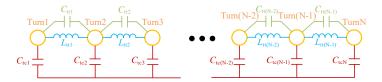

| Fig. 1-2 Simplified equivalent circuit using the lumped-capacitor-network-based           |

| method                                                                                    |

| Fig. 1-3 Simplified equivalent circuit using the energy-conservation based method20       |

| Fig. 2-1 Equivalent circuit of a single-layer inductor                                    |

| Fig. 2-2 Simplified equivalent circuit using the lumped-capacitor-network-based           |

| method                                                                                    |

| Fig. 2-3 Simplified equivalent circuit using the energy-conservation-based method         |

| Fig. 2-4 Comparison of simulated impedance using LTSpice and calculated                   |

| impedance using the energy-conservation-based method and lumped-capacitor-                |

| network method (N = 10 is used in this case)                                              |

| Fig. 2-5 Simulated voltage potential distribution of Turn 1-10 in LTSpice 34              |

| Fig. 2-6 Comparison of the calculated and simulated capacitance of the equivalent         |

| circuit with different number of turns                                                    |

| Fig. 2-7 Inductor with adjustable number of turns                                         |

| Fig. 2-8 Comparison of theoretically calculated capacitance and measured capacitance      |

|                                                                                           |

| Fig. 2-9 Schematics for deriving geometrical parameters of the MV inductor. (a) CAD       |

| model and capacitive couplings. (b) Cross section A (horizontal cross section) . (c)      |

| Cross section B (vertical cross section)                                                  |

| Fig. 2-10 Schematic of the inner layer and core with different configurations. a) Case    |

| 1: core is floating; b) Case 2: core is clamped to the hot terminal; c) core is clamped   |

| to the cold terminal                                                                      |

| Fig. 2-11 Derivation of the three-terminal equivalent circuit schematic. (a) is the       |

| schematic. (b), (c) and (d) are the representation of three cases with different terminal |

| connections                                                                               |

| Fig. 2-12 Pictures of the researched MV inductor 43                                       |

| Fig. 2-13 Schematic of the medium-voltage copper-foiled inductor. (a) Front view.           |

|---------------------------------------------------------------------------------------------|

| (b) Cross-sectional view                                                                    |

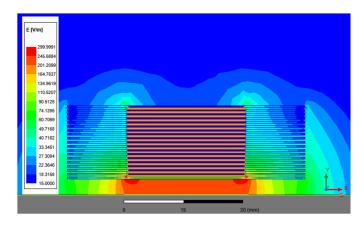

| Fig. 2-14 Electrical field simulation of the 2-dimension copper-foil inductor 48            |

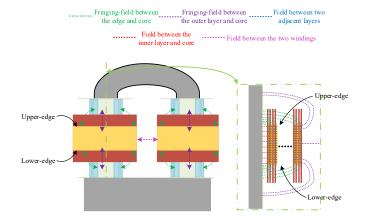

| Fig. 2-15 Identify the capacitive couplings in copper-foiled MV inductors                   |

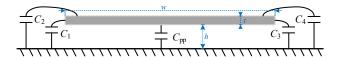

| Fig. 2-16 Schematic of a chip and ground in VLSI applications                               |

| Fig. 2-17 Elementary capacitances contributed by the fringe field. (a) elementary           |

| capacitance between the sidewall and core; (b) elementary capacitance between the           |

| top-surface and core                                                                        |

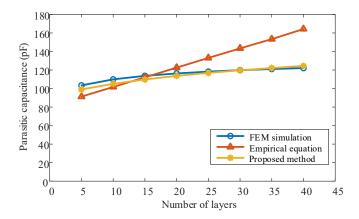

| Fig. 2-18 Comparison of the static capacitances obtained using the FEM simulation,          |

| the empirical equations, and the proposed modeling method                                   |

| Fig. 2-19 Schematic of the copper-foiled inductor with different configurations. a)         |

| Case 1: core is floating; b) Case 2: core is clamped to the hot terminal; c) core is        |

| clamped to the cold terminal                                                                |

| Fig. 2-20 Pictures of the manufactured copper-foiled MV filter inductor 54                  |

| Fig. 2-21 Schematics for the three configurations of the improved modeling method.          |

| a) Configuration 1; b) Configuration 2; c) Configuration 3                                  |

| Fig. 2-22 Converting the three-terminal equivalent circuit of an inductor into two-         |

| terminal equivalent circuit when the core/frame is floating                                 |

| Fig. 3-1 A DPT setup enabled by 10 kV SiC MOSFETs. a) Picture. b) Schematic. $62$           |

| Fig. 3-2 Measured voltage and currents from the DPT at 3 kV/12 A $63$                       |

| Fig. 3-3 Schematic of the DPT setup with inductor represented by a three-terminal           |

| equivalent circuit                                                                          |

| Fig. 3-4 Measured voltage and ground current in DPT setup with triple pulse and $t_{\rm w}$ |

| $=120\mu s65$                                                                               |

| Fig. 3-5 Comparsion between the calculated impedance using DPT setup and                    |

| measured impedance using impedance analyzer                                                 |

| Fig. 3-6 Equivalent circuit representation of an inductor. (a) Schematic of the inductor    |

| with ground connection. (b) General three-terminal equivalent circuit                       |

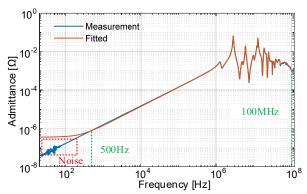

| Fig. 3-7 Comparison between the measured and fitted admittance                              |

| Fig. 3-8 Comparison between the simulation and experiments using the actual          |

|--------------------------------------------------------------------------------------|

| measured voltage as the excitation. a) First turn-off transition. b) Second turn-on  |

| transition                                                                           |

| Fig. 3-9 Comparison between the simulation and experiments using a ramp signal as    |

| the excitation. a) First turn-off transition. b) Second turn-on transition 69        |

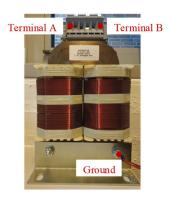

| Fig. 3-10 The exampled medium-inductor with labeling terminals and ground $70$       |

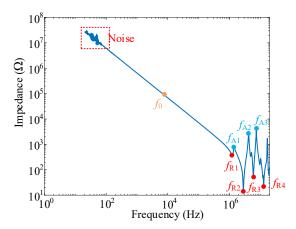

| Fig. 3-11 Measured impedance of the capacitive coupling between Terminal A and       |

| Ground in the exampled medium-voltage inductor with selected frequencies 70          |

| Fig. 3-12 High-frequency RLC-based equivalent circuit of a medium-voltage inductor   |

| 71                                                                                   |

| Fig. 3-13 A comparison between the fitted impedance by using the derived equivalent  |

| circuits and measurement                                                             |

| Fig. 3-14 Image of digital-twin of the double-pulse-test in LTSpice                  |

| Fig. 3-15 Measured and simulated ground current according to digital-twin simulation |

| in LTSpice. a) during the first turn-off transition. b) during the second turn-on    |

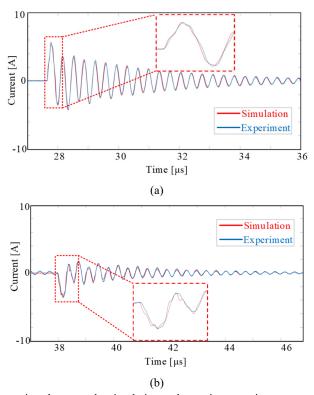

| transition                                                                           |

| Fig. 3-16 Measured and simulated ground current from the digital-twin simulation in  |

| LTSpice using a damping resistance                                                   |

| Fig. 3-17 Measured and simulated ground current from the digital-twin simulation in  |

| LTSpice swapping the connections of the medium-voltage inductor                      |

| Fig. 4-1 Schematic of Case 1                                                         |

| Fig. 4-2 Complete schematic of Case 1                                                |

| Fig. 4-3 Schematic of Case 2                                                         |

| Fig. 4-4 Schematic of Case 3                                                         |

| Fig. 4-5 Schematic of Case 4                                                         |

| Fig. 4-6 Schematic of Case 5                                                         |

| Fig. 4-7 Schematic of Case 6                                                         |

| Fig. 4-8 Schematic of Case 7                                                         |

| Fig. 4-9 Schematic of Case 8                                                         |

| Fig. 4-10 Schematic of Case 9                                                        |

| Fig. 4-11 Schematic of Case 10                                                       |

#### **CHAPTER 1. INTRODUCTION**

"A human is a reed, the weakest thing in nature, but it is a thinking reed."

— Blaise Pascal

#### 1.1 BACKGROUND AND MOTIVATION

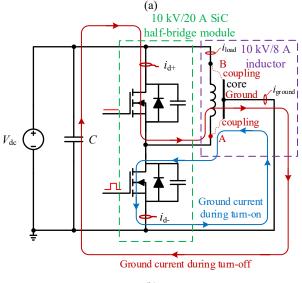

In the past few years, researchers and engineers have witnessed the exponential growth of applying wide-band-gap (WBG) devices in power electronics converters. The WBG semiconductor material of devices can enable the converters to operate at the higher switching frequency, higher blocking voltage, higher ambient temperature, and less switching losses [1]-[8]. As one of the novel wide-band-gap devices, the 10 kV SiC MOSFETs show promising features, e.g. simpler topology of converters in high voltage applications, reduced complexities of system, and higher efficiency [9]-[13], and show potentials in applying in power generation system [14], power distribution system [15], data centers [16], railway applications [17], and etc.

However, the fast switching speed with high dv/dt value of medium-voltage SiC MOSFETs (up to 250 V/ns [18]) poses several challenges to the components in the system [19]. The parasitic capacitive couplings of power components can introduce large capacitive current under the high dv/dt switching transition, e.g. the commonmode current in gate drivers [20], the ground current in heatsink [21], the capacitive current in power modules [22], transformers and inductors [23]-[26]. Especially for medium-voltage inductors, it is reported that the value of parasitic capacitance is usually larger due to the high inductance value and extra insulation compared to low-voltage inductors [25]. The capacitive current contributed by the parasitic capacitive couplings in medium-voltage inductors will circulate in the power converter, which can cause electro-magnetic interference issues [27], and extra losses on transistors as well as degradation of the transistors [28]. The parasitic capacitance of medium-voltage inductors can limit the expected performance of the medium-voltage SiC MOSFETs.

In order to research the parasitic capacitance of inductors (or transformers), both physics-based and behavior-based modeling methods have been reported in previous research. The physics-based modeling method can be used to obtain the equivalent parasitic capacitance of inductors using the geometrical and material parameters [23],

[29]-[31]. Therefore, the physics-based modeling method can predict the value of the parasitic capacitance prior to manufacturing [32], which provides possibilities reiterate the design of inductors for reducing the parasitic capacitance during the design process. The behavior-based modeling method is usually derived by using the measured frequency-domain or time-domain response of long cables [33]-[36], but further extended to characterize the inductors [37]-[39]. The behavior-based modeling method cannot predict the performance of inductors before manufacturing, but it can simulate the actual response of inductors with circuit simulation tools [40].

The motivations of this PhD thesis are listed as below:

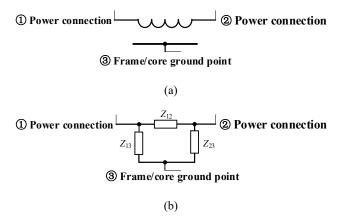

Firstly, there is a typical difference between medium voltage and low voltage applications. In medium-voltage applications, the core and frame of magnetics are required to be grounded due to the safety considerations [41], while in low-voltage applications, the frame and core can be floated if sufficient insulation is applied. When, the core and frame of the inductor is grounded in introduces the third terminal to the system. Therefore, it is not clear that if the previous modeling methods are still applicable in the inductors when their core and frame are grounded.

Secondly, the digital twin of the converter is desired for investigating the system-level performance. The behavior-based models of inductors can be integrated with the behavior-based models of other power components, and the digital twin of the system can be built in circuit simulators. The digital twin simulations can significantly reduce the lab work and accelerate the design and development phase.

Lastly, the methods for reducing the parasitic capacitance in medium-voltage inductors are gaining attention. Although some methods for reducing the parasitic capacitance of inductors have been reported in low-voltage low-power inductors, it is still questionable if the conventional methods are scalable and applicable in the case of medium-voltage inductors.

#### 1.2 STATE OF THE ART

The modeling of capacitive couplings in inductors has been studied in the following three aspects: a) how to develop the physics-based models for inductors; b) how to develop the behavior-based models for inductors; c) how to reduce the capacitive couplings in inductors.

#### 1.2.1 PHYSICS-BASED MODELING METHODS

The physics-based modeling methods of parasitic capacitance in inductors have been researched for almost half a century. The parasitic capacitance of inductors can be

modeled by using the finite-element-method (FEM) [42]-[46], which should be accurate with precise geometrical and material parameters and proper configurations and clear definitions of the physics. However, the FEM-based simulations cannot provide the explicit expression of parasitic capacitance, and the factors influencing the magnitude of the parasitic capacitance are difficult to be identified.

In order to obtain the explicit expressions of parasitic capacitance, two modeling methods: a) lumped-capacitor-network-based method [31], [47]-[49] and b) energy-conservation-based method [23], [29], [52]-[58], are derived in previous research. Both methods can be regarded as a simplification of the FEM-based methods, where more assumptions are applied to reduce the complexity and computation of the physics-based models.

#### 1.2.1.1 LUMPED-CAPACITOR-NETWORK-BASED METHOD

A single-layer inductor with a ferrite core is taken as an example in this section. Fig. 1-1 shows the 3-dimension CAD model of the inductor.

Fig. 1-1 3-dimension CAD model of a toroid inductor

Accurately, there are infinite elementary capacitive couplings within the inductor. By using FEM analysis, the infinite elementary capacitive couplings are simplified into finite couplings based on the mesh theory, and acceptable errors are introduced. In the lumped-capacitor-network method, the capacitive couplings within the inductor are further reduced [31], [47]-[49]. The simplified equivalent circuit of the illustrated single-layer inductor using this method is shown in Fig. 1-2. The capacitive couplings between non-adjacent turns are not considered since these couplings have limited impacts in most situations.

Fig. 1-2 Simplified equivalent circuit using the lumped-capacitor-network-based method

In the lumped-capacitor-network method, the capacitive coupling between two neighbor turns is simplified as a single capacitor  $C_{tt}(N)$ , the capacitive coupling between turn and core is simplified as a single capacitor  $C_{tc}(N)$ , where the equivalent inductance and resistance of each turn is neglected.  $C_{tt}(N)$  and  $C_{tc}(N)$  can be derived using the geometrical and material parameters. Thus, the complex capacitive couplings of the illustrated inductor are simplified into a pure capacitor network, where the total equivalent capacitance can be calculated and explicitly solved using delta-star transformation [31], [47]-[49]. However, this method is limited in inductors with simple geometrical structures, e.g., single-layer inductor or air-coiled inductor. For inductors or transformers with more complex structure, e.g., multi-layer inductor or transformers, the equivalent capacitance can be solved by Spice simulators according to the equivalent circuit representation [50]. The core and frame of inductors are assumed to be floating in lumped-capacitor-network modeling methods [31], [47]-[49], whose applications are limited to two-terminal components.

#### 1.2.1.2 ENERGY-CONSERVATION-BASED METHOD

Taking a single-layer inductor as an example, the energy-conservation-based method is also started with an equivalent circuit representation of the single-layer inductor, as shown in Fig. 1-3.

Fig. 1-3 Simplified equivalent circuit using the energy-conservation based method

The energy-conservation-based method tries to solve the equivalent capacitance of the circuit by calculating the total energy stored in the electrical field [23] [29], [51]-[57]. It assumes that the voltage potential is linearly distributed in the winding [58], [59], and is contributed by the elementary inductance  $L_{tt}$  between two turns. Therefore, the equivalent capacitance calculated by this method is only valid before the first resonant frequency [29]. Since  $C_{tt}(N)$  and  $C_{tc}(N)$  are known according to the geometrical and material parameters, the equivalent capacitance of the simplified circuit at the first resonant frequency can be explicitly solved.

The energy-conservation-based modeling method has been applied in inductors or transformers with complex structures [52]-[59], which means this method can be applied into multi-terminal components, e.g., four-terminal transformers [23], [59],

[60]. The six individual capacitances of a four-terminal transformer are analytically calculated using the method based on energy-conservation [60].

In high frequency applications, the skin-effects and proximity effects on the parasitic capacitance in inductors are considered using energy-conservation-based method [61]. For high-voltage and high-power applications, the core and frame are grounded [62], according to safety considerations and standards[41]. In [60], the parasitic capacitances of a transformer with grounded core/frame are calculated. However, one terminal of the transformer is assumed to be grounded with core/frame during the modeling process [60], where the equivalent capacitance between terminals and core/frame cannot be characterized.

#### 1.2.2 BEHAVIOR-BASED MODELING METHODS

According to the introduction in previous sections, the physics-based modeling methods can only predict a single equivalent capacitor (lumped-capacitor-network-based method) or the equivalent capacitor at the first resonant frequency (energy-conservation-based method).

In practice, there are multiple resonances and anti-resonances according to the measured impedance of inductors and transformers [63], which means the capacitance predicted by physics-based modeling methods cannot reveal the complete behaviors of inductors and transformers at the wide frequency range. Besides, the actual behaviors of inductors and transformers are ruled by not only parasitic capacitance but also resistance and inductance at each frequency.

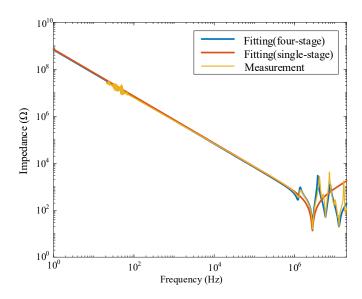

The behavioral model represented by transfer functions are widely used in the modeling of the long cable [33]-[35], where the time-domain or frequency-domain response of the cable is measured first. The behavioral model can also be represented by a circuit, which is more intuitive in comparison to its presentation transfer functions in Spice-based simulators [64]. In [65]-[67], the behavioral models represented by equivalent circuits of chokes are imported into Spice-based simulators, where the common-mode and differential-mode current are simulated. The common-mode and differential-mode impedance of chokes are inductive before the first resonant frequency, where the impedance keeps increasing with the increase of frequency [37], [38]. In [40], the impedance of a common-mode choke is measured first, and a multistage RLC circuit is proposed for fitting the measured impedance. The parameters of the multi-stage RLC circuit can be analytically calculated by identifying the frequency and magnitude of resonances and anti-resonances [40]. [37]- [40] introduce a scalable solution for behaviorally modeling the impedance with inductive characteristics before the first resonant frequency.

The behavior-based model can be integrated into the circuit simulator with the behavior-based models of other power components, where a digital-twin of the circuit is possible to be implemented for system-level simulations. However, such behavior-based models are dependent on the electrical measurements on the actual components, which requires to manufacture the prototype before modeling.

#### 1.2.3 METHODS FOR REDUCING PARASITIC CAPACITANCE

The inductors with a low value of the parasitic capacitance can reduce the capacitive current within the circuit. The equivalent parasitic capacitance and thereby the capacitive current of the inductor can be reduced by paralleling another inductor with a smaller parasitic capacitance[68], however, it requires extra components and can cause more losses due to the use of damping resistance. Therefore, it is desired to reduce the parasitic capacitance of inductors by improving their designs.

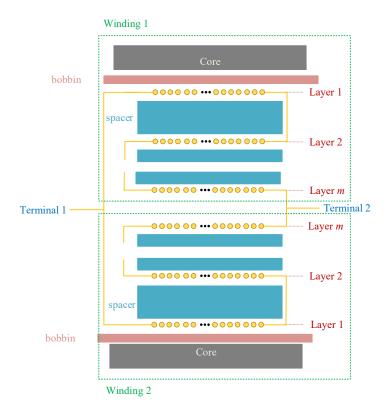

Using a larger distance to weaken the couplings between two adjacent planes is one of the solutions. In [69], spacers are used between two adjacent layers to reduce the parasitic capacitance contributed by the electrical-field energy stored between them. The parasitic capacitance can also be reduced using applying different winding patterns [29], e.g., by changing the original winding layout to flyback winding layout [70]. These methods are developed at the cost of sacrificing the power density of the inductor and increased manufacturing complexity.

#### 1.3 REMINDED CHALLENGES

The previous research mainly focuses on low-power and low-voltage inductors, where the core and frame of inductors are usually floating in these applications. Therefore, the previous modeling methods assume that the inductor is a two-terminal component [71], where there is only one capacitive coupling that needs to be characterized.

However, in high-power or medium-voltage applications, the core and frame of magnetic devices are required to be grounded since the high floating voltage potential can cause safety hazards. Although the ground effects are considered in modeling parasitic capacitance of transformers [60], where the core and frame have the same ground potential as one of the four terminals of transformers, however the equivalent capacitance between terminals and core/frame are not revealed.

Therefore, the medium-voltage inductors should be characterized as the three-terminal passive components instead of the conventional two-terminal components, where the core/frame need to be considered as an individual terminal. Thus, the equivalent capacitance between two terminals of inductors, as well as the equivalent capacitance between terminal and core is possible to be characterized. Therefore, the

first research gap is to develop a physics-based modeling method for characterizing the three parasitic capacitances in inductors considering the core and frame as a separation terminal.

Then, most research analyzes the parasitic capacitance constructed by round-cable and litz wire. However, for high-power applications, the inductors based on copperfoils are more popular due to the low cost and high scalability. Thus, the second gap is to verify whether the physics-based modeling methods developed for inductors with round cables are still valid for copper-foiled inductors.

Besides, the conventional behavior-based modeling method focuses on characterizing the inductive impedance, where the magnitude of impedance keeps increasing with increased frequency before the first resonance. However, according to the experimental measurements, the impedance between the terminal and core(frame) is capacitive, where the impedance drops with increasing the frequency. Therefore, the traditional behavioral modeling methods cannot be directly applied in characterizing the capacitive couplings between terminal and core(frame). Thus, the third research gap is to develop a behavior-based modeling method for characterizing the capacitive impedance.

Finally, the proposed methodologies/approaches to reduce the parasitic capacitance in previous research are only reported in the situations where the core and frame of inductors are floating. Therefore, only the equivalent capacitance between the two terminals of inductors needs to be reduced in previous research. However, this is not sufficient for the inductors with grounded core and frame, since the other two capacitive couplings between each terminal and core needs to consider. Besides, the medium-voltage inductors usually have multiple windings, and the methodologies for reducing inductors with multiple windings are not discussed in previous research. Thus, the fourth research gap is to develop methodologies/approaches of reducing parasitic capacitance in medium-voltage inductors with grounded core and frame.

#### 1.4 OBJECTIVES

Considering the research gaps and unsolved challenges in the modeling and methods of reducing the parasitic capacitance in medium-voltage inductors, this Ph.D. thesis focus on the following specific objectives:

- To develop physics-based modeling methods that can be applied to the inductors with grounded core and frame.

- To develop behavior-based modeling methods that can characterize the capacitive impedance in inductors.

- To propose approaches for reducing parasitic capacitance in medium-voltage inductors with multiple windings and grounded core and frame.

#### 1.5 HYPOTHESIS AND METHODOLOGY

This Ph.D. thesis deals with the modeling methods and approaches for reducing parasitic capacitance in medium-voltage inductors, which is based on the following hypothesis:

- The medium-voltage inductors can be modeled by both physics-based and behavior-based modeling methods. The capacitive couplings between the terminal and core (and frame) can be individually characterized.

- The behavior-based modeling method can develop a circuit-based solution for importing the derived model into circuit simulations.

- By analyzing the developed physics-based and behavior-based model of medium-voltage inductors, several approaches can be proposed for reducing the parasitic capacitance of medium-voltage inductors with multiple windings and grounded core/frame.

Based on the above assumptions, the following methods will be adopted in this thesis:

- The medium-voltage inductors are modeled by an equivalent circuit with finite elementary capacitors and inductors.

- The geometry theory, charge-conservation theory, energy-conservation theory, and multi-terminal circuit theory is applied in calculating the equivalent capacitance between any two terminals of the medium voltage inductors.

- Advanced mathematics is applied to develop the derived models.

- Matlab is used in solving the derived models.

- The FEM simulation, ANSYS, and COMSOL, are used in order to verify the derived models.

- Some prototypes of medium-voltage inductors are designed and manufactured, where the derived model can be experimentally verified by impedance analyzer and double-pulse-test.

#### 1.6 THESIS OUTLINE AND CONTRIBUTIONS

This Ph.D. thesis is divided into five chapters. The main chapters are related to seven publications [J1]-[J5], [C1]-[C2] and one filed patent [P1].

Chapter 1 is the introduction.

Chapter 2 develops the physics-based modeling method for medium-voltage inductors. Chapter 2 is further divided into four subsections:

- Section 2.1 [J1]: Proper and Improper assumptions in modeling parasitic capacitance of inductors

- The proper and improper assumptions for physically modeling the parasitic capacitance in inductors are classified, where the assumptions used in the lumped-capacitor-network method is the improper assumption for modeling the equivalent capacitance at the first resonant frequency. The assumption of linear voltage potential distribution is proper in the energy-conservation-based modeling method, although this assumption can introduce some acceptable errors.

- Section 2.2 [J2]: Physics-based modeling method for medium-voltage inductors with considering the ground effects

This subsection extends the conventional physics-based modeling method of parasitic capacitance for two-terminal inductors (core and frame are floating) to three-terminal inductors (core and frame are grounded), where the three individual capacitance between any two terminals of the three-terminal inductor can be analytically calculated.

- Section 2.3 [J3]: Physics-based modeling method for copper-foiled medium-voltage inductors with considering fringe electrical field

It is found that the energy stored in electrical fringe field is significant for copper-foiled medium-voltage inductors. Thus, the parasitic capacitance contributed by the stored energy in the fringe electrical field of the windings is considered and modeled.

- Section 2.4 [J4]: Improved physics-based modeling method without using the floating core voltage potential

The previous modeling methods require knowing the floating core voltage potential as model input for calculating the parasitic capacitance of inductors with floating or grounding cores. In this section, an improved modeling method is proposed without using the floating core voltage potential. The modeling method can also be extended for the transformers.

Chapter 3 develops the behavior-based modeling method for medium-voltage inductors. Chapter 3 is further divided into three subsections:

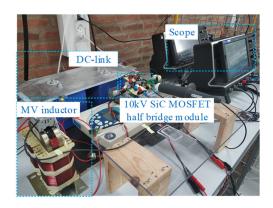

- Section 3.1[C1]: Measurements of the capacitive impedance in medium-voltage inductor with using double-pulse-test setup

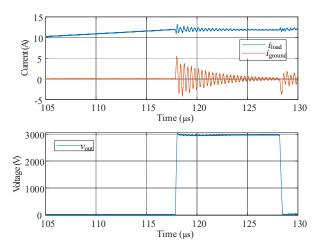

The impedance of the capacitive couplings in medium-voltage inductors is measured using a double-pulse-test setup, which enables the measurement of the impedance under high-voltage and high-current operating conditions. It is found that the impedance of the capacitive couplings is current- and voltage-independent.

- Section 3.2 [C2]: Behavior-based modeling methods of the capacitive impedance in medium-voltage inductors with using transfer functions.

The capacitive coupling in medium-voltage inductors is measured using the impedance analyzer. Then the measured impedance is fitted by a transfer

function using Matlab system identification toolbox. The time-domain simulations of the transfer function-based behavioral model show good agreement with the experimental results.

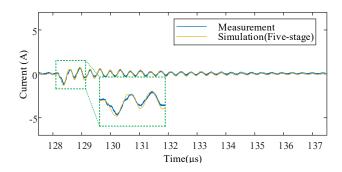

• Section 3.3 [J5]: Behavioral Modeling and Analysis of Ground Current in Medium-Voltage Inductors

The measured impedance of the capacitive couplings in medium-voltage inductors is fitted by using a multi-stage RLC circuit, whose parameters can be analytically calculated according to the measured impedance. The derived RLC circuit is imported into LTSpice, where a digital twin of the double-pulse-test is simulated. The digital twin simulations of the ground current in the medium-voltage inductor show good agreement with the experimental results.

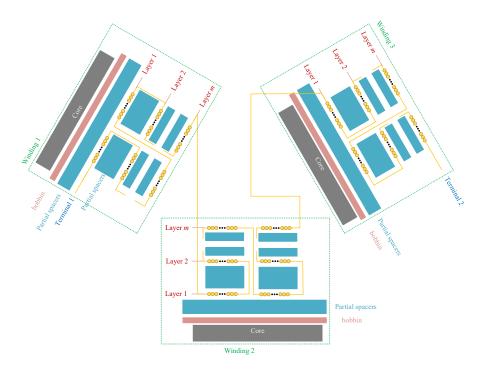

Chapter 4 introduces the approaches for reducing parasitic capacitance for medium-voltage inductors. The multiple winding arrangements, winding layout, and geometrical improvements are discussed in this chapter, where multiple solutions and case studies are presented. This chapter is supported by [P1].

Chapter 5 discusses the conclusions and future work of this thesis.

#### 1.7 RELATED PUBLICATIONS AND PATENTS

The publications related to this Ph.D. thesis are listed as follows:

#### **Journal Publications:**

- [J1] Hongbo Zhao et al., "Proper and Improper Assumptions in Modeling Parasitic Capacitance of Inductors," *IEEE Transactions on Power Electronics*, submitted.

- [J2] Hongbo Zhao et al., "Physics-based Modeling of Parasitic Capacitance in Medium-Voltage Filter Inductors," *IEEE Transactions on Power Electronics*, vol. 36, no. 1, pp. 829 843, Jan. 2021.

- [J3] Hongbo Zhao et al., "Parasitic Capacitance Modeling of Copper-Foiled Medium-Voltage Filter Inductors Considering Fringe Electrical Field," *IEEE Transactions on Power Electronics*, vol. 36, no. 7, pp. 8181 – 8192, Jul. 2021.

- [J4] Hongbo Zhao et al., "Parasitic Capacitance Modeling of Inductors Without Using the Floating Voltage Potential of Core," *IEEE Transactions on Industrial Electronics*, doi: 10.1109/TIE.2021.3068677, early access.

[J5] Hongbo Zhao et al., "Behavioral Modeling and Analysis of Ground Current in Medium-Voltage Inductors," *IEEE Transactions on Power Electronics*, vol. 36, no. 2, pp. 1236 – 1241, Feb. 2021.

#### **Conference Publications:**

- [C1] Hongbo Zhao et.al., "Terminal-to-Core Impedance measurements of the Filter Inductors by Using Double-Pulse-Test", in Proc. 2020 IEEE Workshop on Control and Modeling for Power Electronics, pp. 1-6, 2020.

- [C2] Hongbo Zhao et.al., "Behavioral Modeling of the Ground Current in Filter Inductors for MV SiC-MOSFET-Based Converters", in Proc. 2020 IEEE Applied Power Electronics Conference (APEC), pp. 1972-1978, 2020.

#### Patent:

[P1] Hongbo Zhao et al., "Reducing Parasitic Capacitance in Medium-Voltage Inductors, filed in Danish Patent and Trademark Office, 75792DK01, 2021-03-23.

### CHAPTER 2. PHYSICS-BASED MODELING METHOD

"Thoughts without content are empty, intuitions without concepts are blind.

— Immanuel Kant

This chapter develops the physics-based modeling method for analytically deriving the individual parasitic capacitances in medium-voltage inductors. First, the proper and improper assumptions used in previous research are clarified and verified in Section 2.1. Then, the developed modeling method considering the ground effects is introduced in Section 2.2. The proposed modeling method for copper-foiled inductors considering the electrical fringe field effects is introduced in Section 2.3. Finally, an improved physics-based modeling method without using the floating core voltage potential is introduced in Section 2.4.

#### 2.1 PROPER AND IMPROPER ASSUMPTIONS

Two different modeling methods, the lumped-capacitor-network method, and energy-conservation-based method are reported in previous research for solving the equivalent capacitance of inductors at the first resonant frequency. However, these two methods show a significant contradiction in the conclusions. Therefore, the proper and improper assumptions applied in these two methods are classified in this section.

#### 2.1.1 THE ORIGINAL EQUIVALENT CIRCUIT

The single-layer inductor can be expressed as the equivalent circuit is shown in Fig. 2-1, using the following assumptions.

• Each turn is simplified to a 2D element in Fig. 2. 1. The capacitive coupling between two adjacent turns is simplified as a single capacitor  $C_{tt}$  [72]. The capacitive couplings between each turn and core are simplified as the single capacitor  $C_{tc}$  [72].

- Between two adjacent turns, there is an elementary inductor  $L_{tt}$  [50], [72]. The capacitive couplings between non-adjacent turns are neglected [73]. Losses are also neglected.

- The core is assumed as a perfect conductor [58], as is commonly done. Even high-resistivity cores often have relatively high permittivity [20], [74], which has a similar effect when modeling electric field distributions.

Fig. 2-1 Equivalent circuit of a single-layer inductor

The lumped-capacitor-network modeling method and energy-conservation-based method are original from the equivalent circuit representation of the exampled inductor shown in Fig. 2-1. The lumped circuit assumes that the turn-to-turn inductance  $L_{\rm tt}$  can be assumed as open since the frequency at the first resonant frequency is high enough. Therefore, the equivalent circuit shown in Fig. 2-1 can be simplified as Fig. 2-2, where  $L_{\rm tt}$  is neglected. Therefore, in the lumped-capacitor-network method, the equivalent capacitance of the pure capacitor-network can be solved by using delta-star circuit transformation according to [72].

Fig. 2-2 Simplified equivalent circuit using the lumped-capacitor-network-based method

Although  $L_{tt}$  is not considered directly in the energy-conservation-based modeling method, the voltage potential distribution introduced by  $L_{tt}$  is considered, which is shown as Fig. 2-3. The voltage potential is assumed to be linearly distributed at the first resonant frequency, where the equivalent capacitance of the equivalent circuit can be obtained by calculating the total stored electrical-field energy.

Fig. 2-3 Simplified equivalent circuit using the energy-conservation-based method

#### 2.1.2 CONTRADICTION

By using the lumped-capacitor-network method [72], the total equivalent capacitance  $C_{\text{total}}(N)$  of the inductor with a different number N of turns can be calculated [47], which is given in eq. (2.1).

$$C_{\text{total}}(2) = C_{\text{tt}} + \frac{C_{\text{tc}}}{2}$$

$$C_{\text{total}}(3) = \frac{C_{\text{tt}}}{2} + \frac{C_{\text{tc}}}{2}$$

$$C_{\text{total}}(N) = \frac{C_{\text{total}}(N-2) \times \frac{C_{\text{tt}}}{2}}{C_{\text{total}}(N-2) + \frac{C_{\text{tt}}}{2}} + \frac{C_{\text{tc}}}{2}, \text{ if } N > 3$$

(2.1)

If N > 3,  $C_{total}(N)$  is an iterative sequence. According to [47],  $C_{total}(N)$  is convergent when N is large enough, which is given as the equation presented eq. (2.2).

$$C_{\text{total}}(\infty) = \frac{C_{\text{tt}}}{4} (\alpha + \sqrt{\alpha^2 + 4\alpha}), \ \alpha = \frac{C_{\text{tc}}}{C_{\text{total}}}$$

(2.2)

For example, if  $\alpha = 2$ , the total capacitance between Turn1 and Turn N is convergent to 1.366  $C_{tt}$  when N is larger than 10.

However, using the energy-conservation-based method, the total equivalent capacitance at the first resonant frequency of the circuit shown in Fig. 2. 3 is presented in eq. (2.3).

$$C_{\text{total}}(N) = \sum_{n=1}^{N} \left( \frac{(N-n)V_{\text{total}}}{N-1} - \frac{V_{\text{total}}}{2} \right)^{2} \frac{C_{\text{tc}}}{V_{\text{total}}^{2}} + \sum_{n=1}^{N-1} \left( \frac{V_{\text{total}}}{N-1} \right)^{2} \frac{C_{\text{tt}}}{V_{\text{total}}^{2}}$$

(2.3)

Due to the discrete voltage potential distribution in Fig. 2. 3, the total equivalent capacitance is represented by a sum sequence. If the number of turns is large enough,

the total equivalent capacitance can be approximated as an integral, and then the total capacitance can be represented as eq. (2.4).

$$C_{\text{total}}(N) = \frac{NC_{\text{tc}}}{12} + \frac{C_{\text{tt}}}{N-1}$$

$$C_{\text{total}}(\infty) = \infty$$

(2.4)

Although both methods are aiming to model the total equivalent capacitance at the first resonant frequency, the results and conclusions in (2.2) and (2.4) are quite different. The lumped-capacitor-network method claims that  $C_{\text{total}}(N)$  will be convergent when N is infinite, where the energy-conservation-based methods claims that  $C_{\text{total}}(N)$  is infinite when N is infinite. Therefore, these two methods have a contradiction in the final results, and one or both methods is improper in calculating the total equivalent capacitance at the first resonant frequency of inductors.

#### 2.1.3 EVALUATION OF MODEL ASSUMPTIONS

Since both the lumped-capacitor-network method and the energy-conservation-based method originate from the same equivalent circuit, as the circuit shown in Fig. 2-1 is used as the reference circuit for evaluating the model assumptions.

There is a significant difference between the two modeling methods. In the lumped-capacitor-network method, it assumes that the first resonant frequency is high enough that the elementary inductance between adjacent turns is neglected, where the impacts raised by inductance are completely not considered. However, the energy-conservation-based method assumes the linear voltage distribution within the winding, where the voltage distribution is caused by the elementary inductance between adjacent turns. This section will prove that the lumped-capacitor-network-based method has used the improper assumption due to the overlook of impacts raised by turn-to-turn inductance at the first resonant frequency.

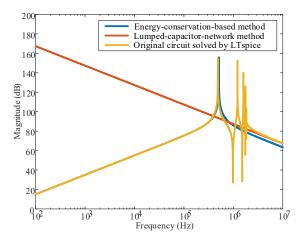

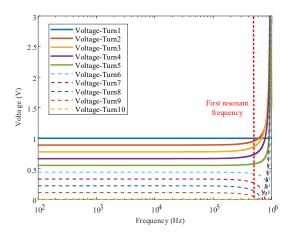

The two different modeling methods are compared in LTSpice, where  $L_{\rm tt}$  = 1 mH,  $C_{\rm tt}$  = 5 pF,  $C_{\rm tc}$  = 10 pF, N = 10. The impedance of the equivalent circuit with calculated capacitance at the first resonant frequency is compared with the measured impedance of the original circuit in LTSpice. The calculated capacitance using the lumped-capacitor-network method is 6.9 pF at the first resonant frequency, where the calculated capacitance using the energy-conservation-based method is 10.8 pF at the first resonant frequency. The measured impedance of the original circuit in LTSpice can be fitted with  $L_{\rm total}$  = 9 mH and  $C_{\rm total}$  = 11.9 pF. Therefore, the calculated capacitance using the lumped-capacitor-network method has a larger error.

In further, the impedances calculated by the lumped-capacitor-network method and energy-conservation-based method are compared with the measured impedance of the original circuit. It can be found that the lumped-capacitor-network-based method actually calculates the total equivalent capacitance after the last resonant frequency. At the first resonant frequency, the turn-to-turn inductance of the original equivalent circuit still has some impacts. Therefore, the turn-to-turn inductance cannot be neglected at the first resonant frequency of inductors.

The voltage potential at Turn  $1 \sim N$  of the original circuit is simulated in LTSpice, which is given in Fig. 2-5. The voltage potential distribution is not absolutely linear at the first resonant frequency, which is however, can introduce some errors to the calculated capacitance at the first resonant frequency compared to the original circuit. Since the variation of voltage potential distribution is relatively small, the assumption claimed by the energy-conservation-based method is more reasonable compared to the assumption claimed by the lumped-capacitor-network method.

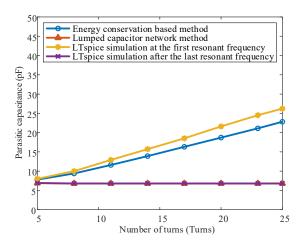

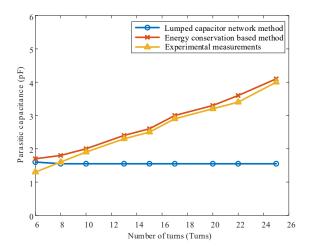

The calculated and simulated capacitance are also compared under a different number of turns, which is shown in Fig. 2-6. The calculated capacitance using lumped-capacitor-network method at the first resonant frequency is constant with the increase of turns, where the measured capacitance at the first resonant frequency of the original circuit keeps increasing. Due to the non-linear voltage distribution at the first resonant frequency, there are some errors between the calculated capacitance using the energy-conservation-based method and the measured capacitance of LTSpice, however, the energy-conservation-based method is much more accurate compared to the calculated capacitance using the lumped-capacitor-network method.

Fig. 2-4 Comparison of simulated impedance using LTSpice and calculated impedance using the energy-conservation-based method and lumped-capacitor-network method (N = 10 is used in this case).

Fig. 2-5 Simulated voltage potential distribution of Turn 1-10 in LTSpice.

Fig. 2-6 Comparison of the calculated and simulated capacitance of the equivalent circuit with different number of turns

The theoretical analysis is also verified by experimental results. An inductor with a different number of turns is taken as an example, where Fig. 2-7 is the picture of the test inductor and Table 2-I lists its geometrical and material parameters.

Fig. 2-7 Inductor with adjustable number of turns

The impedance of the test inductor is measured using Keysight E4990 impedance analyzer [75] and its adapter 16047E [76]. By using the geometrical and material parameters, the calculated capacitance of the test inductor at the first resonant frequency using lumped-capacitor-network method and energy-conservation-based method are calculated, and the measured capacitances of the test inductor at the first resonant frequency using impedance analyzer are compared in Fig. 2-8.

In Fig. 2-8, the measured capacitance of test inductors at the first resonant frequency keeps increasing when the number of turns is increased, which means the lumped-capacitor-network method fails to predict the equivalent capacitance of inductors at the first resonant frequency. The energy-conservation-based method predicts the capacitance with an error that is still within the tolerance of geometrical and material parameters as well as the nonlinear voltage distribution at the first resonant frequency of inductors.

Table 2-I Geometrical and material parameters of the test inductor

| Table 2-1 Geometrical and material parameters of the test inductor |                |  |  |

|--------------------------------------------------------------------|----------------|--|--|

| Core size                                                          | 75mm/40mm/25mm |  |  |

| (Outer diameter/Inner diameter/Height)                             |                |  |  |

| Core material                                                      | MnZn           |  |  |

| Mean length of per turn                                            | 120 mm         |  |  |

| Number of turns                                                    | 6-25           |  |  |

| Average distance of the airgap between the winding and core        | 1.75 mm        |  |  |

| Average distance of the airgap between two adjacent turns          | 0.2 mm         |  |  |

| Diameter of conductor                                              | 0.5mm          |  |  |

| Thickness of the insulation                                        | 0.6mm          |  |  |

| Relative permittivity of the turn coating (PVC [77])               | 3.1            |  |  |

Fig. 2-8 Comparison of theoretically calculated capacitance and measured capacitance

#### **2.1.4 SUMMARY**

This section is supported by [J1]. Two widely used modeling methods for characterizing the equivalent capacitance of inductors at the first resonant frequency are classified:

- The lumped-capacitor-network method assumes that only capacitive impedance is significant. This method predicts the capacitance at a very high frequency, and therefore, is improper to predict the equivalent capacitance at the first resonant frequency.

- The energy-conservation-based method assumes that the voltage distribution between turns is uniform and is shown to be more proper for analytically calculating the parasitic capacitance at the first resonant frequency. However, the voltage potential distribution of winding is shown to be non-uniform at the first resonant frequency according to the LTSpice simulations of the equivalent circuit, though by a relatively small amount, which can introduce errors in predictions.

The two modeling methods are compared by experiments. The lumped-capacitor approach is confirmed to be inappropriate, while the errors of the energy-conservation method are found to be within acceptable tolerance in one example.

# 2.2 PHYSICS-BASED MODELING METHODS WITH CONSIDERING GROUND EFFECTS

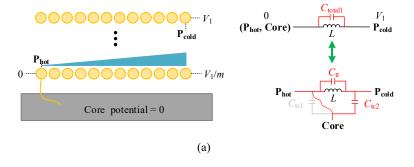

The conventional physics-based modeling methods of parasitic capacitance in inductors usually assume that the inductor is a two-terminal component where the core is floating. However, in medium-voltage and high-power applications, the core and frame of magnetic devices are required to be grounded due to safety considerations. Therefore, three individual capacitances between any two terminals of the three-terminal component need to be characterized, respectively.

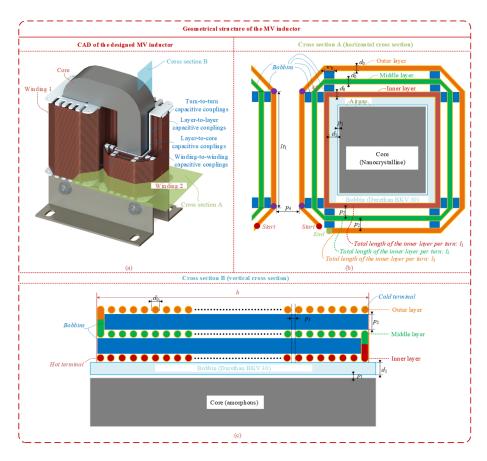

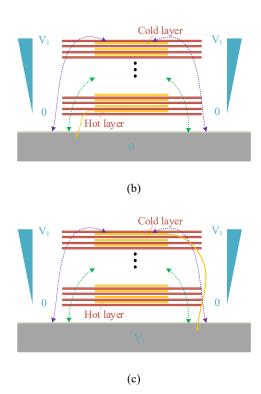

# 2.2.1 CAPACITIVE COUPLINGS IN A TYPICAL MEDIUM VOLTAGE INDUCTOR

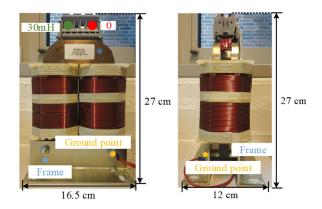

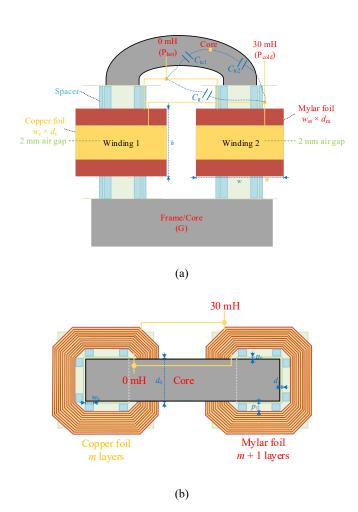

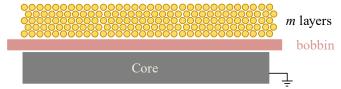

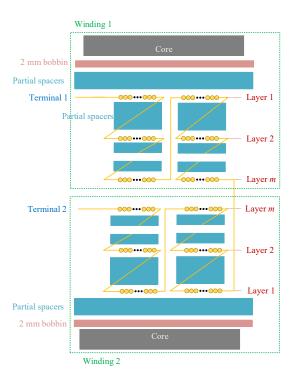

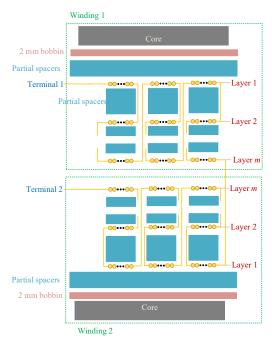

A typical medium-voltage inductor is used as an example in this paper, where the 3-dimension CAD model is shown in Fig. 2-9 (a). The medium-voltage inductor is designed for a five kHz two-level voltage source converter enabled by 10 kV SiC MOSFETs. The medium-voltage inductor is constructed by two U-type amorphous cores[78], with a 2 mm air gap in between. The geometrical structure of the windings is illustrated in Fig. 2-9 (b) and (c). The geometrical and material parameters are listed in Table 2-II and Table 2-III.

Table 2-II. Key parameters of the MV inductor

| Table 2-11. Key parameters of the MV inductor                     |                       |         |  |

|-------------------------------------------------------------------|-----------------------|---------|--|

| Description                                                       | Symbol                | Value   |  |

| Diameter of the cable                                             | $d_0$                 | 1.4 mm  |  |

| Length of the air gap between the bobbin and core                 | $p_1$                 | 0.75 mm |  |

| Thickness of the bobbins between the inner layer and core         | $d_1$                 | 2 mm    |  |

| Length of the air gap between two adjacent layers                 | $p_2$                 | 5.7 mm  |  |

| Average length of the air gap between two turns in the same layer | рз                    | 0.45 mm |  |

| Height of the windings                                            | h                     | 11.9 cm |  |

| Width of the spacers between two adjacent layers                  | Wb                    | 4.8 mm  |  |

| Length of the outer layer per turn                                | $l_1$                 | 24.7 cm |  |

| Length of the middle layer per turn                               | $l_2$                 | 22.2 cm |  |

| Length of the inner layer per turn                                | $l_3$                 | 19.7 cm |  |

| Average length of per turn for three layers                       | l                     | 22.2 cm |  |

| Average length of the air gap between the two windings            | <i>p</i> <sub>4</sub> | 3 mm    |  |

| Number of turns of per layers                                     | n                     | 63      |  |

| Number of layers      | m | 3     |

|-----------------------|---|-------|

| Number of the winding | w | 2     |

| Total inductance      | L | 30 mH |

Fig. 2-9 Schematics for deriving geometrical parameters of the MV inductor. (a) CAD model and capacitive couplings. (b) Cross section A (horizontal cross section) . (c) Cross section B (vertical cross section).

TABLE II. Relative permittivity of the material

| Description                                          | Symbol                     | Value                      |

|------------------------------------------------------|----------------------------|----------------------------|

| The permittivity of the bobbins [79], [80]           | Еъ                         | 4.0                        |

| The permittivity of the coating of cables [81], [82] | $\mathcal{E}_{\mathrm{r}}$ | 3.7 (average value)        |

| The permittivity of vacuum [83]                      | £0                         | 8.82×10 <sup>-12</sup> F/m |

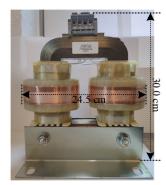

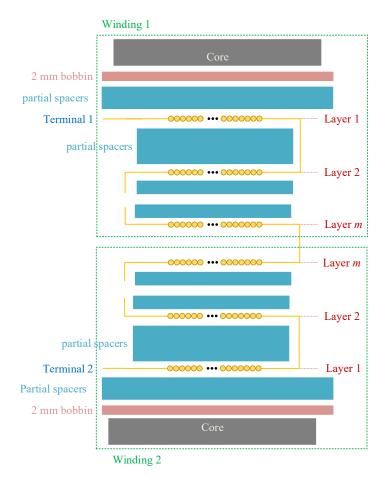

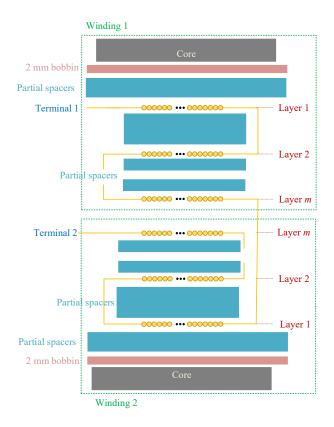

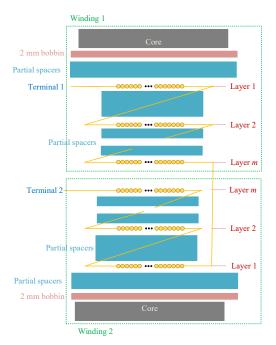

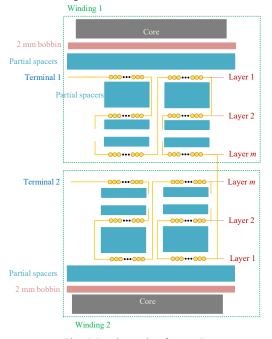

According to Fig. 2-10, four basic capacitive couplings of the researched medium-voltage inductor can be identified as follows [J2]:

- The turn-to-turn capacitive coupling between two adjacent turns at the same layer.

- The layer-to-layer capacitive coupling between two adjacent layers.

- The layer-to-core capacitive coupling between the inner layer and core.

- The winding-to-winding capacitive couplings occurred between the two windings.

Due to the limited impacts, the capacitive couplings between two non-adjacent turns and between two not-adjacent layers are neglected in this thesis.

## 2.2.2 STATIC AND DYNAMIC CAPACITANCE

Two different capacitances, static and dynamic capacitance, need to be defined before modeling. The static capacitance is only dependent on the geometrical and material parameters, e.g.,  $C_{\rm tc}$  and  $C_{\rm tt}$  showed in Fig. 2-1. The dynamic capacitance is the equivalent capacitance of the inductor when the inductor is under normal operations, where the current flows through the winding. The dynamic capacitance is the overall performance of the inductor, which is represented by the actual stored electrical-field energy, e.g.  $C_{\rm total}$  solved in eq. (2.3). Since in the previous section, the thesis has revealed that the lumped-capacitor-network method is the improper solution for calculating the parasitic capacitance of inductors at the first resonant frequency, the dynamic capacitance (total equivalent capacitance of inductor) will be solved using the energy-conservation-based method. Therefore, the dynamic capacitance of the inductor is dependent on both static capacitance and voltage distribution within the winding, which is represented by the total stored electrical field energy of the static capacitance. Thus, the static capacitance and dynamic capacitance need to be solved in sequence.

The derivations of static capacitance for the considered medium-voltage inductor have been elaborated in [J2]. The four static capacitances, corresponding to the four basic capacitive couplings of the exampled medium-voltage inductor,  $C_{\text{sta\_num-to-turn}}$  (static capacitance between two adjacent turns),  $C_{\text{sta\_layer-to-layer}}$  (static capacitance between two adjacent layers),  $C_{\text{sta\_layer-to-core}}$  (static capacitance between inner layer and core),  $C_{\text{sta\_winding-to-winding}}$  (static capacitance between two windings), are derived based on the geometrical and material parameters. The detailed derivations of the four static capacitance are given in [J2]

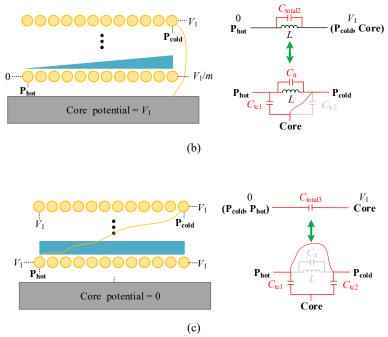

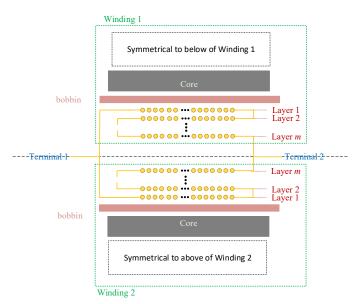

In order to calculate the three individual capacitance of the medium-voltage inductor considering the ground effects, three different configurations are implemented, which are shown in Fig. 2-10. Each configuration is a two-terminal network, where the

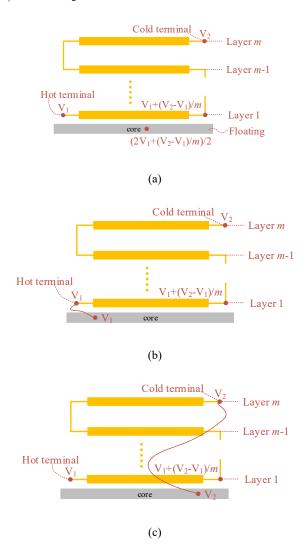

voltage potential on the core is different. The voltage potential on the core is assumed to be equal, where the voltage potential of the winding is assumed to be equal to one of the terminals. The voltage potential on the two terminals is  $V_1$  and  $V_2$ , respectively. In Case 1, the floating voltage potential on the core is  $(2V_1+(V_2-V_1/m))/2$ , which is assumed to be the average voltage potential of Layer 1. The voltage potential on core is  $V_1$  in Case 2, which is  $V_2$  in Case 3.

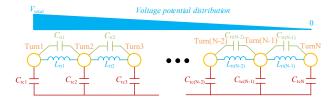

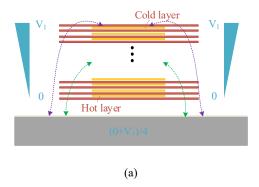

Fig. 2-10 Schematic of the inner layer and core with different configurations. a) Case 1: core is floating; b) Case 2: core is clamped to the hot terminal; c) core is clamped to the cold terminal

In these three configurations, the dynamic capacitance  $C_{\rm dyn\_turn-to-turn}$  between two adjacent turns,  $C_{\rm dyn\_layer-to-layer}$  between two adjacent layers, and  $C_{\rm dyn\_winding-to-winding}$  between two windings are the same since the voltage potential within the winding is the same. The only difference is the dynamic capacitance between the inner layer and core, since the voltage potential difference between the inner layer and core is different in the three configurations [J2].

The three dynamic capacitance  $C_{\text{dyn\_layer-to-core}}$  between the inner layer and core in the three configurations are given in eq. (2.5).

$$C_{\text{dyn\_layer-to-core}1} = 2 \times \frac{1}{12m^2} \times C_{\text{sta\_layer-to-core}}$$

$$C_{\text{dyn\_layer-to-core}2} = 2 \times \frac{1}{3m^2} \times C_{\text{sta\_layer-to-core}}$$

$$C_{\text{dyn\_layer-to-core}3} = 2 \times \frac{3m^2 - 3m + 1}{3m^2} \times C_{\text{sta\_layer-to-core}}$$

(2.5)

It is noted that there is a coefficient of 2 in eq. (2.5), since there are two windings in the researched medium-voltage inductors. The detailed derivations of  $C_{\text{dyn\_turn-to-turn}}$ ,  $C_{\text{dyn\_layer-to-layer}}$ ,  $C_{\text{dyn\_winding-to-winding}}$ , and  $C_{\text{dyn\_layer-to-core}}$  are elaborated in [J2].

The total dynamic capacitance of the researched inductor in three configurations can be obtained as eq. (2.6), based on energy-conservation law.

$$\begin{split} &C_{\rm dyn1} = C_{\rm dyn\_turn-to-turn} + C_{\rm dyn\_layer\_to\_layer} + C_{\rm dyn\_layer\_to\_core1} + C_{\rm dyn\_winding\_to\_winding} \\ &C_{\rm dyn2} = C_{\rm dyn\_turn-to-turn} + C_{\rm dyn\_layer\_to\_layer} + C_{\rm dyn\_layer\_to\_core2} + C_{\rm dyn\_winding\_to\_winding} \\ &C_{\rm dyn3} = C_{\rm dyn\_turn-to-turn} + C_{\rm dyn\_layer\_to\_layer} + C_{\rm dyn\_layer\_to\_core3} + C_{\rm dyn\_winding\_to\_winding} \\ \end{split} \tag{2.6}$$

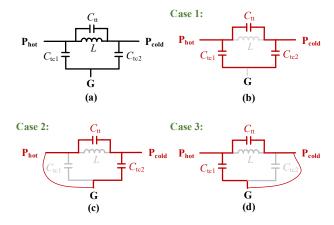

The three configurations of the medium-voltage inductors can also be presented at the circuit-level, as shown in Fig. 2-11. The three configurations are three special cases of the three-terminal inductor, where the three-terminal inductor is reduced to three two-terminal circuits in each configuration.

$C_{\rm tt}$ ,  $C_{\rm tc1}$ , and  $C_{\rm tc2}$  are the three individual capacitances in the three-terminal equivalent circuit. The dynamic capacitance in Case 1-3 can also be represented by the three individual equivalent capacitances based on the series/parallel connection of the capacitances derived using the circuit theory, which is given as eq. (2.7).

$$\begin{cases} C_{\text{dyn1}} = C_{\text{tt}} + \frac{C_{\text{te1}} C_{\text{te2}}}{C_{\text{te1}} + C_{\text{te2}}} \\ C_{\text{dyn2}} = C_{\text{tt}} + C_{\text{te2}} \\ C_{\text{dyn3}} = C_{\text{tt}} + C_{\text{te1}} \end{cases}$$

(2.7)