### **Aalborg Universitet**

#### Parasitic Effect Compensation Method for IGBT ON-State Voltage Measurement in **Traction Inverter Application**

Peng, Yingzhou; Chu, Kaigi; Mu, Shuji; Cao, Hu; Wang, Huai

Published in:

I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2021.3130209

Publication date: 2022

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Peng, Y., Chu, K., Mu, S., Cao, H., & Wang, H. (2022). Parasitic Effect Compensation Method for IGBT ON-State Voltage Measurement in Traction Inverter Application. *I E E E Transactions on Power Electronics*, 37(5), 4937-4941. https://doi.org/10.1109/TPEL.2021.3130209

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: February 07, 2025

# A Parasitic Effect Compensation Method for IGBT On-state Voltage Measurement in Traction Inverter Application

Yingzhou Peng, Member, IEEE, Kaiqi Chu, Shujia Mu, Hu Cao, Huai Wang, Senior Member, IEEE

Abstract—This letter proposes a novel compensation method to eliminate the impact of parasitic inductances on the measurement accuracy of on-state voltage of power semiconductor devices in operating converters. It is an online and non-invasive method by measuring the output current of inverter and on-state voltage of power device only. The impact of parasitic inductances and its compensation are verified experimentally through a traction inverter system.

*Index terms*— Power semiconductor, compensation, parasitic inductance, on-state voltage.

#### I. Introduction

The on-state voltages are closely relative to the health condition and junction temperature of power semiconductor devices [1, 2]. Therefore, their accurate measurement is essential to the realization of predictive maintenance and reliability improvement [1]. Tremendous efforts have been devoted to realizing the online measurement of on-state voltage, consisting of component-level solutions [3–5] and converter-level solutions [6, 7].

Nevertheless, based on our best knowledge, the impact of the parasitic inductances in direct copper bond (DCB) layer and terminals of power semiconductor devices is rarely considered in the literature, and effective compensation method is also not well researched, which can heavily impair the measurement accuracy of on-state voltage in an operating converter. Although higher measurement accuracy of on-state voltage (e.g.,  $\pm 10$ mV and  $\pm 5$  mV) is reported in [5] and [7], they are obtained through static DC input voltage testing, which does not induce voltage drop in the parasitic inductances. In addition, the direct-current (DC) power cycling testing presented in [8] is also independent on the parasitic inductances. However, in real power converter applications, the alternative current (AC) flowing through the DCB and terminals can induce additional voltage and has to be considered. Particularly in motor drive applications, the slope of current is variable due to different operational modes. In addition, for high-power applications, the parasitic inductances of power module might be too large to be neglected. In [3], the deviation of on-state voltage due to

Y. Peng and H. Wang are with the Department of Energy Technology, Aalborg University, Aalborg, Denmark (email: ype@et.aau.dk, hwa@et.aau.dk). K. Chu, S. Mu, and H. Cao are with the CRRC Qingdao Sifang Co., Ltd (Corresponding author: Kaiqi Chu).

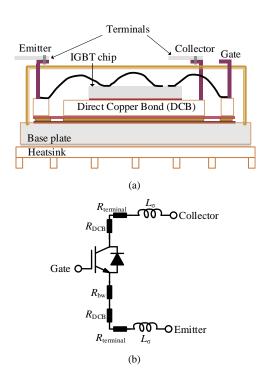

Fig. 1. An example of IGBT module: (a) cross-section; (b) equivalent circuit.

parasitic inductances could be more than 150 mV in a wind turbine power converter and a method is proposed to reduce the impact of parasitic inductances by integrating the measured on-state voltage over one switching-cycle. However, it can only obtain the average of on-state voltage during a switching cycle, instead of the instantaneous on-state voltage, which faces two challenges: (1) during one switching cycle, the change of current could be more than hundreds of amperes, leading to the loss of on-state voltage when power device operates in high-current status; (2) for traction inverter applications, there could be very few switching cycles over one fundamental period, which means very limited on-state voltage information can be obtained over one fundamental period.

In this letter, the impact of parasitic inductances on the measurement of on-state voltage in an operating power electronic converter is investigated and modeled by analyzing its sources and dependencies. Then, a novel compensation strategy is proposed to eliminate the impact of parasitic inductances at any instantaneous current-levels. It utilizes the measured on-

state voltage and phase-current in an operating converter to calculate the parasitic inductances in real-time. As a result, the voltage drop generated in the parasitic inductances can then be compensated without impairing the normal operation of converter. The experimental verification is also conducted through a traction inverter system with high-voltage and high-current.

## II. INVESTIGATION AND COMPENSATION ON PARASITIC INDUCTANCES

In this letter, the analysis and demonstration of the proposed method are conducted based on an IGBT module. It is also applicable to other power devices, such as MOSFET. Fig.1(a) gives an example of a typical wire-bonded IGBT module. The terminals that are made of aluminum alloy provide electrical connection with outside and are soldered on the surface of DCB as like the bond wires inside the power module. Therefore, the physical parasitic elements of those electrical-conduction materials are spatially distributed inside the power module. Fig.1(b) illustrates the equivalent circuit of one IGBT with parasitic resistances and inductances.

Parasitic resistances  $R_{\rm DCB}$  and  $R_{\rm bw}$  are contributed by the tracks on DCB and aluminum bond wires inside the power module, respectively.  $R_{\rm terminal}$  represents the parasitic resistance of the terminals.  $L_{\sigma}$  is the parasitic inductances from collector to emitter. In an operating power converter, the inductive and resistive parasitic elements can lead to the deviation of measured total on-state voltage from the on-state voltage of IGBT chip  $V_{\rm CE,sat,chip}$ , which can be expressed by:

$$\begin{cases} V_{\text{CE,sat}} = V_{\text{CE,sat,chip}} + i_{\text{c}} R_{\text{tot}} + 2L_{\sigma} \frac{di_{\text{c}}}{dt} \\ R_{\text{tot}} = 2R_{\text{DCB}} + R_{\text{bw}} + 2R_{\text{terminal}} \end{cases}$$

(1)

$R_{\rm DCB}$  and  $R_{\rm bw}$  are thermally connected to chip and the voltage drops on them will follow chip temperature linearly for a given current-level [3]. As a result, the sensitivity to temperature change of  $V_{\rm CE,sat}$  is amplified. Moreover,  $R_{\rm DCB}$ and  $R_{\mathrm{bw}}$  have link to the degradation of DCB and bondwire, respectively. Overall, the existence of  $R_{\rm DCB}$  and  $R_{\rm bw}$ can be seen as a benefit for the health condition assessment of power module. The value of  $R_{\text{terminal}}$  is usually in  $\mu\Omega$ level and has negligible impact on  $V_{\rm CE,sat}$  even at different temperatures [3]. It is reported that parasitic inductance usually has a distinct temperature-dependency when frequency is larger than 1 GHz for example [9], which is much higher than that in most power electronic applications. Also, for most cases, the terminal temperature is relatively stable due to its extremely low parasitic resistance and relatively stable temperature inside inverter. Overall, the temperature impact on parasitic inductance can be neglected.

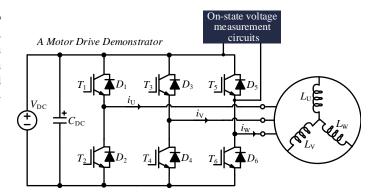

Fig.2 illustrates the topology of a three-phase inverter for motor drive application. According to the modulation strategy

Fig. 2. An example of motor drive system with on-state voltage measurement circuit.

(e.g., SPWM or SVPWM), the operation statues of the inverter can be roughly given by:

$$\begin{cases} L_{x1} \frac{di_{x1}}{dt} - L_{x2} \frac{di_{x2}}{dt} = V_{DC} \\ L_{x1} \frac{di_{x1}}{dt} - L_{x2} \frac{di_{x2}}{dt} = 0 \\ L_{x1} \frac{di_{x1}}{dt} - L_{x2} \frac{di_{x2}}{dt} = -V_{DC} \end{cases}$$

(2)

where x1 and x2 could be any two of U, V, and W, implying that  $L_{\rm x1}$  and  $L_{\rm x2}$  are any two of the three equivalent inductances in the motor  $L_{\rm U}$ ,  $L_{\rm V}$ , and  $L_{\rm W}$ .  $i_{\rm x1}$  and  $i_{\rm x2}$  are any two of the three AC currents  $i_{\rm U}$ ,  $i_{\rm V}$ , and  $i_{\rm W}$ .  $V_{\rm DC}$  is the DC-link voltage. It should be noted that  $i_{\rm U}$ ,  $i_{\rm V}$ , and  $i_{\rm W}$  can be seen as the collector current  $i_{\rm c}$  of the power switch that is in conduction-mode.

Based on (2), over one fundamental period, the derivative of current  $di_c/dt$  is not constant and can be either positive or negative, and changes with variable DC-link voltage. It implies that the measured  $V_{\rm CE,sat}$  has a variable error, which leads to an unacceptable deviation on the evaluation of junction temperature and health condition of device under test (DUT). Especially, the desired switching cycles of DUT in a three-phase inverter are generated by means of pulse width modulation (PWM) method. For example, in an inverter with space-vector pulse width (SVPWM) modulation scheme, there are seven switching vectors during one switching cycle [3], resulting in several changes in  $di_c/dt$  and voltage drops of parasitic inductance.

Therefore, compared to parasitic resistances, the impact of parasitic inductances is more complex due to the variable derivative of current  $(di_c/dt)$  in response to time when the DUT is in conduction-mode, which can affect the accuracy of  $V_{\rm CE,sat}$  and has to be compensated.

For example, when DUT is in conduction-mode, two collector current points with same value but different slopes are selected and indicated as  $I_{\rm c1}$  and  $I_{\rm c2}$  during one switching cycle. Meanwhile, their corresponding on-state voltages are  $V_{\rm CE,sat1}$  and  $V_{\rm CE,sat2}$ , respectively. Based on the measured current data before and after  $I_{\rm c1}$  and  $I_{\rm c2}$ , and data sampling frequency, the current slopes at  $I_{\rm c1}$  and  $I_{\rm c2}$  can be calculated as

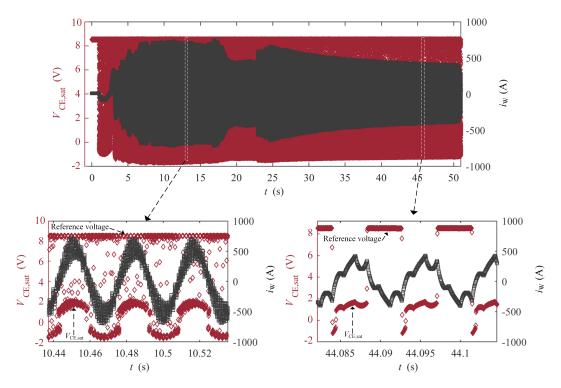

Fig. 3. Measured on-state voltage of  $T_5$  and phase current  $i_W$  while motor drive is in operating (note: when the DUT is in off-state, the voltage across collector to emitter is the DC-link voltage that is blocked and clamped into a reference voltage by the measurement circuit).

$dI_{c1}/dt$  and  $dI_{c2}/dt$ , respectively. Then, the following equations can be obtained:

$$V_{\text{CE,sat1}} = V_{\text{CE,sat,chip1}} + I_{\text{c1}}R_{\text{tot}} + L_{\sigma,\text{tot}}\frac{dI_{\text{c1}}}{dt}$$

(3)

$$V_{\rm CE,sat2} = V_{\rm CE,sat,chip2} + I_{\rm c2}R_{\rm tot} + L_{\sigma,\rm tot}\frac{dI_{\rm c2}}{dt}$$

(4)

where  $L_{\sigma, {

m tot}}$  indicates the total parasitic inductance from the collector to emitter of IGBT.

If  $I_{\rm c1}$  is assumed to be same with  $I_{\rm c2}$ , resulting in that  $V_{\rm CE,sat,chip1} + I_{\rm c1}R_{\rm tot}$  is same with  $V_{\rm CE,sat,chip2} + I_{\rm c2}R_{\rm tot}$ . Then, subtract (4) from (3):

$$L_{\sigma,\text{tot}} = \frac{V_{\text{CE,sat1}} - V_{\text{CE,sat2}}}{dI_{\text{c1}}/dt - dI_{\text{c2}}/dt}$$

(5)

Since  $V_{\rm CE,sat}$  and  $dI_{\rm c}/dt$  are measurable, the parasitic inductance  $L_{\sigma,tot}$  can then be calculated in real-time. Consequently, the inductive term in (1) can be compensated in real-time.

It should be noted that ensuring  $I_{\rm c1}$  is same with  $I_{\rm c2}$  could be a challenge in practice. Therefore, the introduced error due to different  $I_{\rm c}$  should be analyzed. For the module with high power rating (e.g., 3300 V/1500 A),  $R_{\rm tot}$  could be far less than 1 m $\Omega$ . While  $R_{\rm tot}$  is usually couple of m $\Omega$  for the module with low power rating (e.g., 1200 V/50 A). Thus, the former one has more wider tolerance in current difference than the latter module, which corresponds to practical applications since high-current sensor has low resolution than low-current sensor. Actually, the change rate of on-state voltage in response to current  $dV_{\rm CE,sat}/dI_{\rm c}$  can be obtained from the datasheet of

applied IGBT module. Then, the error due to different  $I_{\rm c}$  can be estimated in advance. It is acceptable if this error is less than the absolute value of  $V_{\rm CE,sat1}-V_{\rm CE,sat2}$  by 10%, which will be verified experimentally in next section.

## III. EXPERIMENTAL VERIFICATION WITH A CASE STUDY OF MOTOR DRIVE

The proposed method is verified through a motor drive system with 1800 V DC-link voltage, variable fundamental and switching frequency  $f_{\rm sw}$ . The IGBT in the up-bridge of phase-W (i.e.,  $T_5$  in Fig.2) is taken as the DUT. (the implementation for other power devices can be derived similarly) and an online on-state voltage measurement circuit is used as shown in Fig.2. The applied measurement circuit, originally introduced in [7], is capable of either extracting the on-state voltages of multiply power devices by connecting to the middle-point of each phase-leg, or extracting the on-state voltage of one power device by connecting to the collector-emitter of DUT.

During testing, the motor is set to operate at three different conditions: speed-up, uniform-speed, and speed-down. The measured output phase current  $i_{\rm W}$  and on-state voltage of  $T_5$  over 50 s are presented in Fig.3. The resolution of applied Analog-Digital Converter (ADC) is 12-bits and data sampling frequency  $f_{\rm sm}$  is 25 kHz. In order to get enough details of current and on-state voltage over one switching-cycle and improve the estimation accuracy of  $L_{\sigma,{\rm tot}}$ ,  $f_{\rm sm}$  should be 20-30 times of  $f_{\rm sw}$  according to the experimental results in later this section. The white dash-rectangle parts in the upfigure of Fig.3 are zoomed-in, implying that  $V_{\rm CE,sat}$  and  $i_{\rm W}$  are

Fig. 4. Experimental waveforms: (a) over two fundamental period; (b) over one switching cycle (note: before about 0.4 ms, the DUT is in off-state and the  $di_{\rm W}/dt$  and  $V_{\rm CE,sat}$  are set to zero).

measurable and synchronous, and have variable fundamental and switching frequency at different operation conditions. In practice, considering the phase current sensors are already existed for control or protection purpose in most applications, an additional on-state voltage measurement circuit is required only in terms of hardware. However,  $f_{\rm sm}$  has to be increased, which can be realized by modifying the existing control unit or using an additional data acquisition system with enough  $f_{\rm sm}$  as a condition monitoring unit.

The slope of  $i_{\rm W}$  is simply calculated by using three neighboring points in  $i_{\rm W}$  as:

$$di_{\mathrm{W,k}}/dt = \frac{i_{\mathrm{W,k+1}} - i_{\mathrm{W,k-1}}}{2T_{\mathrm{sample}}}$$

(6)

where  $T_{\text{sample}}$  is the sampling period.

The calculated  $di_{\rm W}/dt$  is shown in Fig.4.  $V_{\rm CE,sat}$  is the measured on-state voltage of DUT. The red rectangle in Fig.4(a) is zoomed-in to show the detail of one switching-cycle as presented in Fig.4(b). The data at upward-track and downward-track, but similar current-level are marked. It can be seen that the on-state voltage at upward-track is higher than the value at downward-track by about 112 mV at this current-level due to the different current slopes and the existence of parasitic inductance. With the marked data in Fig.4(b) and (5), the parasitic inductance can be calculated as:

$$L_{\sigma, \text{tot}} = \frac{1.952 - 1.840}{(1.328 - (-0.577)) \times 10^{-6}} \approx 59nH$$

(7)

To verify the repeatability of (7), another five switching cycles are selected randomly to calculate  $L_{\sigma,\text{tot}}$ , showing 53

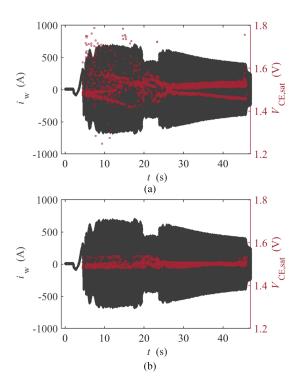

Fig. 5. Extracted on-state voltage when  $i_{\rm W}$  is within (300 - 305) A: (a) before compensation; (b) after compensation.

nH, 56 nH, 69 nH, 62 nH, and 62 nH. This fluctuation is due to the measurement error and can be reduced by calculating the average of these  $L_{\sigma,\text{tot}}$ , which is about 60 nH.

Then, the impact of parasitic inductance can be compensated by substituting this 60 nH into (3) and (4). Five current pairs with similar value are taken from the upward-track and downward-track, and the corresponding on-state voltages are recorded as  $V_{\rm CE,sat1}$  and  $V_{\rm CE,sat2}$ , respectively, as listed in Table I. The  $dV_{\rm CE,sat}/dI_{\rm c}$  of the applied IGBT module is about 1.3 mV/A according to its datasheet. Considering the  $L_{\sigma, {

m tot}}$  caused difference in  $V_{{

m CE, sat}}$  could be 112 mV in this case study, the difference of selected current pairs should be less than 8-9 A. Before compensation, the measured  $V_{\rm CE,sat}$ at upward-track is higher than the value at downward-track by 5.6 % to 6.1 % even at similar selected current-level. However, after compensation, their difference is reduced down to only 0.1 % of the value at upward-track, which proves the effectiveness of the proposed method. Moreover, this deviation is increased from 0.1 % to 0.5 % when the current difference is changed from 0 A to 7 A.

In addition, the on-state voltage when current  $i_{\rm W}$  is within a narrow range (e.g., (300 - 305) A in this case study) is extracted over experimental testing. Then, the proposed compensation strategy is applied to eliminate the impact of parasitic inductances. Fig.5 gives the results before and after compensation. It implies that the obtained on-state voltage after compensation has a much narrower variation and better continuity than the data before compensation.

Overall, with enough data sampling frequency, the proposed

TABLE I

COMPARISON OF MEASURED ON-STATE VOLTAGE BEFORE AND AFTER

COMPENSATION (UNIT: V)

| Up/Down              | 481/476                                                                                                                       | 536/543                                                                                                                                 | 590/590                                                                                                                                                                                                                          | 642/635                                               |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| $V_{\rm CE,sat1}$    | 1.828                                                                                                                         | 1.894                                                                                                                                   | 1.952                                                                                                                                                                                                                            | 2.010                                                 |

| $V_{\rm CE,sat2}$    | 1.716                                                                                                                         | 1.788                                                                                                                                   | 1.840                                                                                                                                                                                                                            | 1.898                                                 |

| Percentage           | 6.1%                                                                                                                          | 5.6%                                                                                                                                    | 5.7%                                                                                                                                                                                                                             | 5.6%                                                  |

| $V_{\text{CE,sat1}}$ | 1.744                                                                                                                         | 1.812                                                                                                                                   | 1.872                                                                                                                                                                                                                            | 1.940                                                 |

|                      | 1.750                                                                                                                         | 1.822                                                                                                                                   | 1.874                                                                                                                                                                                                                            | 1.930                                                 |

| Percentage           | 0.3%                                                                                                                          | 0.4%                                                                                                                                    | 0.1%                                                                                                                                                                                                                             | 0.5%                                                  |

|                      | $V_{\mathrm{CE,sat1}}$ $V_{\mathrm{CE,sat2}}$ Percentage $V_{\mathrm{CE,sat1}}$ $V_{\mathrm{CE,sat1}}$ $V_{\mathrm{CE,sat2}}$ | V <sub>CE,sat1</sub> 1.828<br>V <sub>CE,sat2</sub> 1.716<br>Percentage 6.1%<br>V <sub>CE,sat1</sub> 1.744<br>V <sub>CE,sat2</sub> 1.750 | VCE,sat1         1.828         1.894           VCE,sat2         1.716         1.788           Percentage         6.1%         5.6%           VCE,sat1         1.744         1.812           VCE,sat2         1.750         1.822 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

Note: Up/Down indicate the upward-track and downward-track of current over one switching-cycle, respectively.

method can be implemented in an operating converter by five steps: 1) extract the data over 5-10 switching cycles at the beginning; 2) confirm the current data is in upward-track or downward-track by calculating the change rate of each current data through (6); 3) find the similar currents in upward-track and downward-track, respectively, and corresponding on-state voltages; 4) calculate  $L_{\sigma, \rm tot}$  and its average; 5) compensate  $V_{\rm CE, sat}$  through the calculated average of  $L_{\sigma, \rm tot}$  and measured current.

#### IV. CONCLUSIONS

In this letter, the parasitic elements in the on-state voltage of power semiconductor devices are modeled to explore the impact of inductive parasitic elements. Then, a novel compensation strategy is proposed to reduce the deviation of on-state voltage caused by parasitic inductances. It uses the phase current of inverter and on-state voltage of power semiconductor device only, and can be realized in real time. The experimental verification is conducted through a traction inverter case study. The results imply that the deviation of the on-state voltages measured at similar current-level but with different current slopes could be up to 6.1 % in this case study, which is unacceptable considering the change of on-state voltage due to device degradation is 5 % to 20 %, and its temperature sensitivity is less than 5 mV/°C for most cases. While, after compensation, this deviation is reduced up to 0.5 % under the selected current-levels in this case study.

#### REFERENCES

- A. Avenas, L. Dupont, N. Baker, H. Zara, and F. Barruel, "Condition monitoring: A decade of proposed techniques," *IEEE Transactions on Industrial Electronics*, vol. 9, no. 4, pp. 22–36, Dec. 2015.

- [2] Y. Peng, S. Zhao, and H. Wang, "A digital twin based estimation method for health indicators of dc-dc converters," *IEEE Transactions on Power Electronics*, vol. 36, no. 2, pp. 2105–2118, Feb. 2021.

- [3] B. Rannestad, A. E. Maarbjerg, K. Frederiksen, S. Munk-Nielsen, and K. Gadgaard, "Converter monitoring unit for retrofit of wind power converters," *IEEE Transactions on Power Electronics*, vol. 33, no. 5, pp. 4342–4351, May 2018.

- [4] U. Choi, F. Blaabjerg, S. Jorgensen, S. Munk-Nielsen, and B. Rannestad, "Reliability improvement of power converters by means of condition monitoring of igbt modules," *IEEE Transactions on Power Electronics*, vol. 32, no. 10, pp. 7990–7997, Oct. 2017.

- [5] M. Guacci, D. Bortis, and J. W. Kolar, "On-state voltage measurement of fast switching power semiconductors," CPSS Transactions on Power Electronics and Applications, vol. 3, no. 2, pp. 163–176, Jun. 2018.

- [6] Y. Peng, Y. Shen, and H. Wang, "A converter-level on-state voltage measurement method for power semiconductor devices," *IEEE Transactions on Power Electronics*, vol. 36, no. 2, pp. 1220–1224, Feb. 2021.

[7] Y. Peng and H. Wang, "A simplified on-state voltage measurement circuit for power semiconductor devices," *IEEE Transactions on Power Electronics*, vol. 36., no. 10., pp. 10993–10997, Oct. 2021.

- [8] S. Dusmez, S. H. Ali, M. Heydarzadeh, A. S. Kamath, H. Duran, and B. Akin, "Aging precursor identification and lifetime estimation for thermally aged discrete package silicon power switches," *IEEE Transactions* on *Industry Applications*, vol. 53, no. 1, pp. 251–260, Jan 2017.

- [9] G. E. Ponchak, J. L. Jordan, and M. C. Scardelletti, "Temperature dependence of thin film spiral inductors on alumina over a temperature range of 25 to 475 c," in 2010 Proceedings 60th Electronic Components and Technology Conference (ECTC). IEEE, Jun. 2010, pp. 713–719.