# **Aalborg Universitet**

# Quantitative criteria of considering AC infeed in DC fault assessment of modular multilevel converters

Xu, Yi; Zhang, Yi; Qin, Liang; Liu, Kaipei; Blaabjerg, Frede

Published in: International Journal of Electrical Power & Energy Systems

DOI (link to publication from Publisher): 10.1016/j.ijepes.2021.107874

Publication date: 2022

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Xu, Y., Zhang, Y., Qin, L., Liu, K., & Blaabjerg, F. (2022). Quantitative criteria of considering AC infeed in DC fault assessment of modular multilevel converters. *International Journal of Electrical Power & Energy Systems*, 141, 1-13. Article 107874. https://doi.org/10.1016/j.ijepes.2021.107874

# **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

# Quantitative criteria of considering AC infeed in DC fault assessment of modular multilevel converters

Yi Xu<sup>a</sup>, Yi Zhang<sup>b</sup>, Liang Qin<sup>a</sup>, Kaipei Liu<sup>a</sup>,\*, Frede Blaabjerg<sup>b</sup>

<sup>a</sup>School of Electrical Engineering and Automation, Wuhan University, Wuhan 430072, China <sup>b</sup>AAU Energy, Aalborg University, Aalborg 9220, Denmark

#### Abstract

An accurate and efficient DC fault current assessment of modular multilevel converters (MMCs) is critical for designs and protection. The state-of-the-art often ignores the impact of the AC infeed in the DC fault assessment without MMC blocking. However, whether the AC infeed needs to be considered or not is a controversial problem. This paper proposes quantitative criteria to determine the necessity of considering the AC infeed in the fault current assessment. The method is based on the premise that the MMC blocking has not occurred. Based on the average model of the MMC, the fault current contribution from the AC side is quantified under different control schemes. The criteria are established by a contributing ratio of the AC infeed over the total fault current. The obtained criteria only rely on the system and control parameters, which enable designers to identify the impact by ignoring the AC infeed in the DC fault assessment. The effectiveness of the proposed criteria is validated by two case studies and two different control schemes. The results reveal that the submodule (SM) capacitance and the number of SMs have a large impact on the AC infeed contribution.

© 2017 Elsevier Inc. All rights reserved.

Keywords: AC infeed; DC fault current assessment; modular multilevel converter (MMC); quantitative criteria.

#### 1. Introduction

Half-bridge modular multilevel converter (HB MMC) based high voltage direct current (HVDC) transmission is a promising and flexible solution to integrate a large scale of renewable energy resources [1-5]. However, the HB MMC has no fault current handling capability under DC faults. When a DC fault occurs, the DC network exhibits a fast fault current rise and propagation, which may lead to serious damage to the converters or a complete shutdown of the entire HVDC network [6-8].

Sufficient knowledge of the DC fault current behavior of the MMC is necessary for the sake of hardware design and protection settings. When dealing with the DC fault problems, the HB MMC is conventionally blocked within a few microseconds. However, the method of blocking IGBTs fully disables the controllability of the converter, interrupts the power transmission, and prolongs the outage duration of the HVDC system. Currently, DC circuit breakers (DCCBs) [9-11] have been proposed to deal with DC faults without blocking the MMC, which is beneficial

\* Corresponding author. Tel.: +8613807138258.

*E-mail address:* kpliu@whu.edu.cn http://dx.doi.org/10.1016/j.ijepes.2021.00.000

0142-0615 /© 2021 Elsevier Inc. All rights reserved.

for continuous operation of the HVDC grid. The selection of the DCCB should ensure that the fault current is less than the DCCB capacity. In addition, the power semiconductor devices and other components of the MMC should be able to withstand the maximum fault current. The assessment of the fault current without MMC blocking is thus of great significance for this application.

For the DC fault current assessment without MMC blocking, a simplified equivalent model of MMC is derived as a series RLC circuit [12-15]. Based on the equivalent model, the analytic equations for the MMC fault current calculation are deduced in [14]. The method based on state variable analysis for calculating the pole-to-pole (P2P) DC fault current in HVDC grids is proposed in [15]. Although the simplified RLC model has good performance to estimate the fault current near the fault site, the prediction of the node voltages and currents of far branches has larger deviations [16]. One of the reasons of this under performance is that the RLC model ignores the impact of the AC system.

To consider the AC system in the fault current assessment, an improved fault current estimation method is introduced in [16,17], which involves the dynamics of MMC control. Ref. [17] proposes a general companion circuit-based method to estimate the currents of asymmetric bipolar multi-terminal HVDC grids. The fault calculations based on variable and constant MMC current sources are presented in [18]. The aforementioned papers have contributed to improving the computational accuracy of the fault current. However, by considering the AC infeed, the fault current estimation becomes more complicated and time-consuming. For an efficient assessment of the fault current, whether the AC infeed should be considered or not remains unclear, given that a certain deviation is sometimes allowed in practice.

A quantitative criterion for determining the necessity of considering the AC infeed is important in order to avoid significant deviation in the fault current assessment. On the one hand, some studies suggest that considering the AC infeed is costly in analysis and only leads to slight accuracy improvement in the fault current estimation, which can be totally ignored for simpler analysis. For instance, in the case study of [16], compared with the simulated results, the maximum deviation for the fault current estimation including the AC infeed is 3.15%, while the maximum deviation is 5.94% without considering the AC infeed. On the other hand, ignoring the AC infeed may result in significant deviation between the estimated and the actual results of the fault current. It is found in [17,18] that the computational node voltages without considering the AC infeed significantly deviate from actual values. After a remote DC fault occurs, the simplified model that ignores the AC infeed may cause a capacitor voltage rise of the MMC, which is in contrary to a practical situation. As a result, the fault current, being influenced by the node voltages, may show inaccurate waveforms. With the continuous expansion of the HVDC grid, more potential inaccurate situations are possibly existing if the AC infeed is ignored based on a biased intuition. Moreover, it should be noted that the conclusions of the aforementioned studies are only based on specific parameters. Their conclusions may be completely changed for other parameters. Therefore, it can be seen that whether the AC infeed needs to be considered in the fault current assessment is still a controversial problem. A generic criterion without limitations for specific case studies are of great necessity.

Establishing the criteria of considering the AC infeed in fault assessment has significant challenges. First, the fault transient involving the AC infeed is a nonlinear circuit and influenced by the MMC control schemes. Previous studies [16-18] provide fault current calculation of the multi-terminal HVDC system considering the AC system. However, their studies mainly focus on the numerical solutions of the fault currents in the DC grid. The quantitative analysis of the AC infeed contribution under different control schemes are rarely discussed. Moreover, extensive factors are involved in the DC fault current when considering the AC infeed. The index reflecting the impacts by ignoring the AC infeed is still having theoretical gaps and needs further investigation.

To solve the aforementioned problems, this paper proposes quantitative criteria for determining whether the AC infeed needs to be considered in estimating the DC fault current. The method is based on the premise that the MMC blocking has not occurred. Firstly, the average model of the MMC involving the impacts of AC infeed is established. Then, the analytic equations for fault current contribution from AC infeed under different control modes are deduced. An index to describe the estimation deviation caused by neglecting the AC infeed is introduced. Lastly, the criteria for determining the necessity of considering the AC infeed in fault current assessment are proposed. The main contributions of this paper are summarized as two folds. 1) The AC infeed contribution is quantified under different control modes of the MMC. The index reflecting the impacts by ignoring the AC infeed in the fault assessment is presented. 2) By contrast to the prior arts focusing on specific cases, the proposed criteria are more general, and they are not limited to a specific system parameter or control parameter. The established criteria serve as a tool to help

designers to determine whether the AC infeed should be considered in order to avoid the potential risks of ignoring the AC infeed intuitively.

# 2. DC fault current analysis of MMC considering AC infeed

By contrast to the conventional methods to model the MMC as an RLC circuit only, this paper proposes a combination of an RLC circuit and a current source in order to consider the AC infeed. The current source helps to model the impact of the AC infeed on the DC side. Moreover, two different control modes are also considered in this section.

# 2.1. Equivalent model of MMC under DC faults

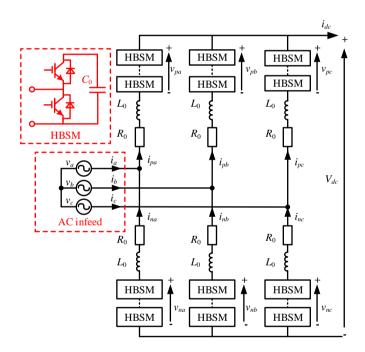

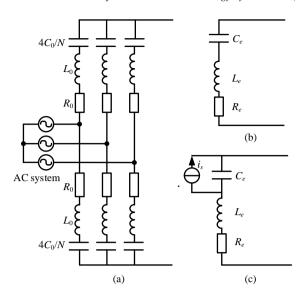

Fig. 1 depicts the configuration of the HB MMC. It consists of six symmetrical arms. Each arm has N submodules (SMs).  $C_0$  is the SM capacitance, and  $L_0$  and  $R_0$  are the arm inductance and resistance, respectively. In 5-10 ms after a DC fault, the equivalent circuit of an MMC is shown in Fig. 2(a). The equivalent capacitor of the SMs  $(4C_0/N)$  is derived by the energy conservation principle. If the AC system is neglected, the model of MMC is equivalent to an RLC series circuit [19], as shown in Fig. 2(b). The parameters are given as follows.

Fig. 1. Configuration of the MMC and its submodule topologies.

$$C_e = \frac{6C_0}{N}, \ L_e = \frac{2L_0}{3}, R_e = \frac{2R_0}{3}$$

(1)

By considering the AC infeed, the improved model of MMC is derived as a series RLC equivalent circuit with a current source [16-18], as shown in Fig. 2(c). The model is established using the principle of power balance [20]. The current source  $i_s$  represents the AC infeed and is obtained as

$$i_s = \frac{P_{ac}}{u_c} \tag{2}$$

Fig. 2. Equivalent circuit of an MMC. (a) detailed model of an MMC. (b) equivalent circuit of the MMC ignoring the AC infeed. (c) equivalent circuit considering the AC infeed.

where  $P_{ac}$  represents the AC active power and  $u_c$  represents the voltage across  $C_e$ , respectively.

Based on the assumption that the q-axis voltage is zero when an ideal PLL is used,  $P_{ac}$  can be represented as [17]

$$P_{ac} = 1.5u_{sd}i_{sd} \tag{3}$$

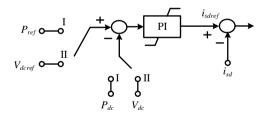

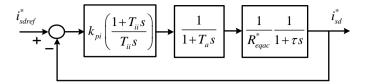

where  $u_{sd}$  and  $i_{sd}$  are the d-axis voltage and current in the control loop, respectively. In this paper, only the controls in the outer active power loop are considered and the other MMC controls are ignored. Specifically, the outer loop controls the active power or the DC voltage and generates the d-axis current reference  $i_{sdref}$  for the inner control loop, as shown in Fig. 3 [21].

Fig. 3. Outer active power control loop of the MMC.

To simplify the analysis, the dynamics of the inner controller and modulation is neglected [22], and  $i_{sd}$  is regarded to be perfectly tracking its reference value, thus identical to  $i_{sdref}$ . Based on per unit values, the active power can be expressed as

$$P_{ac}^* = u_{sd}^* l_{sdref}^* = u_c^* l_s^* \tag{4}$$

If the converter is operated at its voltage rating  $(u_{sd}^*)$  and  $u_c^*$  are 1 p.u.), it can be assumed from (4) that the p.u. values of  $i_s$  and  $i_{sdref}$  are identical. For converters in active power control mode, by converting the parameters from per unit values to actual values,  $i_s$  in terms of complex frequency domain (s-domain) can be obtained as

$$i_{s} = \frac{P_{N}}{V_{deN}^{2}} \left( \frac{P_{ref}}{s} - P_{dc} \right) \left( k_{pp} + \frac{k_{pi}}{s} \right) + \frac{i_{s0}}{s}$$

(5)

where  $P_N$ ,  $V_{dcN}$ ,  $P_{ref}$ ,  $P_{dc}$ ,  $k_{pp}$  and  $k_{pi}$  are the rated active power, the rated DC voltage, the active power reference value, the DC side power, the proportional and integral gain of the active power PI controller, respectively.  $i_{s0}$  represents the prefault value of  $i_s$ . The power transmission between the AC system and the MMC remains controllable in a short period after the fault due to the PI controller [23]. Therefore, when the MMC operates in the power control mode,  $P_{dc}$  is thought to be equal to  $P_{ref}$  in the early fault time [17,24]. As a result,  $i_s$  is almost unchanged and can be solved as

$$i_s \approx i_{s0} = \frac{P_N}{V_{doN}} = i_{dc(0_-)}$$

(6)

where  $i_{dc(0)}$  is the initial DC current when a DC fault occurs.

Similarly, for converters in DC voltage control mode,  $i_s$  can be obtained as

$$i_s = \frac{P_N}{V_{dcN}^2} \left( \frac{V_{dcref}}{s} - V_{dc} \right) \left( k_p + \frac{k_i}{s} \right) + \frac{i_{s0}}{s} \tag{7}$$

where  $V_{dcref}$ ,  $V_{dc}$ ,  $k_p$  and  $k_i$  are the DC voltage reference value, the DC voltage, the proportional and integral gain of DC voltage PI controller, respectively.

### 2.2. Fault current assessment of MMC considering AC infeed

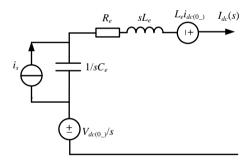

Based on the MMC equivalent circuit in Fig. 2(c), the fault equivalent model in the complex frequency domain is shown in Fig. 4, where  $V_{dc(0)}$  is the initial DC voltage when a fault occurs.

Fig. 4. Equivalent model of the MMC in the complex frequency domain.

1) For MMC in active power control mode: referring to Fig. 4 and (6), the DC fault current in terms of complex frequency domain can be obtained as

$$I_{dc_{-}P}(s) = \frac{sV_{dc(0_{-})} + s^{2}Li_{dc(0_{-})} + i_{dc(0_{-})}/C_{e}}{s(s^{2}L + sR + 1/C_{e})}$$

(8)

$$L = L_e + L_{dc}, \ R = R_e + R_{dc} \tag{9}$$

where  $L_{dc}$  and  $R_{dc}$  are the DC-side inductance and resistance, respectively. By the inverse Laplace transform of (8), the time-domain expression of  $I_{dc\_P}(s)$  can be obtained, which is given in the Appendix of this paper. In addition, when the AC infeed is neglected, the DC fault current is given in the Appendix. Therefore, under the power control mode, the fault current contribution from the AC side can be expressed as

$$\Delta i_{dc_{-P}}(t) = i_{dc_{-P}}(t) - i_{dc}(t) = i_{dc(0_{-})} \left[ 1 - \frac{1}{\sqrt{1 - \xi_{1}^{2}}} e^{-\xi_{1}\omega_{1}t} \sin\left(\omega_{1}\sqrt{1 - \xi_{1}^{2}}t + \varphi_{1}\right) \right]$$

(10)

where  $i_{dc\_P}(t)$  and  $i_{dc}(t)$  represent the fault current with and without considering the AC infeed. The attenuation coefficient of the fault current  $1/\xi_1\omega_1$ , the oscillating current angular frequency  $\omega_1$ , and the initial phase angle  $\varphi_1$  are influenced by the system parameters.

In general,  $R < 2\sqrt{L/C}$ . It can be seen from (10) that the AC infeed contribution presents a second-order underdamped oscillation characteristics. The method that ignores the AC infeed leads to a negative difference in the fault current estimation for sending end converter station, while leads to a positive difference for the receiving end converter station. For the sending end converter, the equivalent SM capacitor discharges slower with the aid of current source  $i_s$ . On the contrary, the equivalent SM capacitor of receiving end converter discharges faster when the AC infeed is considered.

2) For MMC in DC voltage control mode: referring to Fig. 4 and (7), the current source is expressed as

$$i_{s} = \frac{P_{N}}{V_{deN}^{2}} \left( \frac{V_{dcref}}{s} - sLI_{dc}(s) + Li_{dc(0_{-})} \right) \cdot \left( k_{p} + \frac{k_{i}}{s} \right) + \frac{i_{s0}}{s}$$

$$\tag{11}$$

To simplify the analysis, the resistance is neglected in (11). Considering that the value of  $V_{dcref}$  is usually equal to  $V_{dcN}$ , the DC fault current in terms of complex frequency domain is obtained. By the inverse Laplace transform, the time-domain expression of the fault current can be derived. The detailed derivation is given in the Appendix.

For the MMC in the DC voltage control mode, the fault current contribution from the AC side can be expressed as

$$\Delta i_{dc-DC}(t) = i_{dc-DC}(t) - i_{dc}(t) \tag{12}$$

where  $i_{dc\_DC}(t)$  represents the fault current considering the AC infeed. Compared with the active power control mode case, the expression of the AC infeed contribution is relatively complicated. The fault current is influenced by both the system and control parameters under the DC voltage control mode.

# 3. Criteria for determining the necessity of considering AC infeed in fault assessment

The fault current contribution from the AC infeed can be obtained based on the above analysis. In this section, under different control schemes, the quantitative criteria of considering the AC infeed in the fault current assessment are proposed. The criteria can be used to determine whether the influence of the AC infeed is non-negligible in the DC fault current analysis, thus evaluating the fault current level accurately and efficiently.

#### 3.1. MMC in active power control mode

The ratio of the AC infeed contribution to the total fault current is taken as an index to reflect the impact by ignoring the AC infeed in the DC fault assessment, which is expressed as

$$\sigma_1 = \frac{\Delta i_{dc_P}(t)}{i_{dc_P}(t)} \tag{13}$$

Considering that the resistance of a real HVDC system is usually small, and it hardly affects the transient state of the DC current in the first few milliseconds after the fault time [25]. The equivalent resistance R is neglected. Then, the index  $\sigma_1$  can be simplified as

$$\sigma_1 = \frac{1 - \cos \omega_1 t}{1 + K \sin \omega_1 t} \tag{14}$$

where K is defined as

$$K = \frac{V_{dc(0_{-})}}{\omega_1 L i_{dc(0_{-})}} = \frac{V_{dcN}^2}{P_N} \sqrt{\frac{C_e}{L}}$$

(15)

The index  $\sigma_1$  is a function of t. Taking the derivative of  $\sigma_1$  with respect to t, it can be found that  $d\sigma_1/dt \ge 0$  when  $t \in [0, \pi/2\omega_1]$ . Thus, during  $t \in [0, \pi/2\omega_1]$ ,  $\sigma_1$  is an increasing function and reaches the maximum at  $t = \pi/2\omega_1$ . In addition, the DC fault current  $i_{dc\_P}(t)$  increases during this period and peaks at  $t = \pi/2\omega_1$ . Since the rising phase of DC fault current is the main concern, it is important to focus on the fault current during the period of  $t \in [0, \pi/2\omega_1]$ . Considering that the estimation of the peak value is of great significance, and in view of a margin between the estimated and actual values, the maximum value of  $\sigma_1$  at  $t = \pi/2\omega_1$  is taken as the criterion to evaluate the impact of the AC infeed on the fault current. The maximum value of  $\sigma_1$  is obtained as

$$\sigma_1 = \frac{1}{1+K} \tag{16}$$

Comparing  $\sigma_1$  with the maximum allowable deviation of the current estimation, if  $\sigma_1$  is larger, the maximum deviation between the estimated and the actual values exceeds the allowable one when the AC infeed is neglected. Thus, it is necessary to consider the AC infeed in the DC fault current assessment. Otherwise, the AC infeed is negligible. Defining that the maximum allowable deviation of current estimation is  $\sigma_{max}$ , the criterion is concluded to be as

$$\begin{cases}

\sigma_{1} = \frac{1}{1+K} \ge \sigma_{\text{max}}, \text{ AC infeed is non-negligible} \\

\sigma_{1} = \frac{1}{1+K} < \sigma_{\text{max}}, \text{ otherwise}

\end{cases}$$

(17)

Based on (17), the deviation of the fault assessment caused by ignoring the AC infeed depends on K, which is determined by the system parameters. The deviation is proportional to the rated active power, while inversely proportional to the equivalent SM capacitance and the rated DC voltage. Since the equivalent SM capacitance is the ratio of the SM capacitance to the number of SMs, the AC infeed increases with the number of SMs increasing or the SM capacitance decreasing. A larger inductance results in a smaller K, thus resulting in a larger maximum estimation difference. On the other hand, a larger inductance can suppress the fault current below the maximum value for a longer period. That means it takes a longer time for the fault current to reach its peak. As a result, when it mainly focuses on the current in a short period after the fault, the difference may be acceptable even if L is large.

#### 3.2. MMC in DC voltage control mode

Similar to the MMC in active power control mode, the ratio of the AC infeed contribution to the total fault current is taken as the index to reflect the impact of AC infeed, which is expressed as

$$\sigma_2 = \frac{\Delta i_{dc\_DC}(t)}{i_{dc\_DC}(t)} \tag{18}$$

Since the attenuation coefficient and the angular frequency of  $i_{dc\_DC}(t)$  is not equal to that of  $i_{dc}(t)$ , the form of  $\sigma_2$  is complex. To simplify the expression, some assumptions are proposed in this paper. It can be seen from (7) that  $i_s$  is proportional to  $k_p$  and  $k_i$ . It means that the AC infeed contribution is proportional to the parameters of the DC voltage PI controller. If  $k_p$  or  $k_i$  are neglected, the value of the index is smaller than its actual value. When this smaller index exceeds the maximum allowable deviation, the actual current difference certainly exceeds the allowable one. Therefore, the simplified index can be used as a conservative value to determine the estimation deviation caused by ignoring the AC infeed. For simplification of the analysis,  $k_p$  is neglected, and  $i_{dc\_DC}(t)$  is simplified as

$$i_{dc_{-}DC}(t) = i_{dc(0_{-})} + \frac{P_{N}k_{i}}{\omega_{2}^{2}LC_{e}V_{dcN}}t + \frac{V_{dc(0_{-})}C_{e}V_{dcN}^{2} - P_{N}k_{i}V_{dcN}/\omega_{2}^{2}}{LC_{e}V_{dcN}^{2}\omega_{2}}\sin\omega_{2}t$$

(19)

$$\omega_2 = \sqrt{\frac{1}{LC_e} + \frac{P_N k_i}{C_e V_{deN}^2}} \tag{20}$$

If  $k_i$  is also neglected,  $i_{dc\_DC}(t)$  is identical to  $i_{dc\_p}(t)$  and the case of the DC voltage control mode is the same as that of the active power control mode.

1) When  $k_i \ll V_{dcN}^2/(LP_N)$ :  $i_{dc\_DC}(t)$  can be further simplified as

$$i_{dc\_DC}(t) \approx i_{dc(0_{-})} + \frac{P_N k_i}{V_{dcN}} t + \frac{V_{dc(0_{-})}}{\omega_2 L} \sin \omega_2 t - \frac{P_N k_i}{\omega_2 V_{dcN}} \sin \omega_2 t$$

(21)

$$\omega_2 \approx \sqrt{\frac{1}{LC_e}}$$

(22)

According to (21),  $i_{dc\_DC}(t)$  is an increasing function of t during  $t \in [0, \pi/2\omega_2]$ . Similar to the analysis method of the active power control mode case, only the period of  $t \in [0, \pi/2\omega_2]$  is considered. The maximum value of  $\sigma_2$  during this period is taken as the criterion to evaluate the impact of AC infeed. The maximum value of  $\sigma_2$  is obtained as

$$\sigma_2 = \frac{M}{K + M} \tag{23}$$

where M is defined as

$$M = 1 + k_i \sqrt{LC_e} \left( \pi/2 - 1 \right) \tag{24}$$

Defining that the maximum allowable deviation is  $\sigma_{max}$ , the criterion is concluded as

$$\begin{cases} \sigma_2 = \frac{M}{K+M} \ge \sigma_{\text{max}}, \text{ AC infeed is non-negligible} \\ \sigma_2 = \frac{M}{K+M} < \sigma_{\text{max}}, \text{ otherwise} \end{cases}$$

(25)

Based on (25), the deviation caused by ignoring the AC infeed depends on *K* and *M*, which are determined by the overall system and control parameters.

2) When  $k_i \ll V_{deN}^2/(LP_N)$  is invalid: taking the derivative of (19) with respect to t, it can be found that  $i_{de\_DC}(t)$  is an increasing function when  $t \in [0, \pi/2\omega_2]$ . Only the rising phase of the DC fault current during  $t \in [0, \pi/2\omega_2]$  is considered. At  $t = \pi/2\omega_2$ , the value of  $i_{de\_DC}(t)$  is

$$i_{dc_{-}DC}(\frac{\pi}{2\omega_{2}}) = i_{dc(0_{-})} + \frac{V_{dc(0_{-})}}{\omega_{2}L} + \frac{P_{N}k_{i}}{\omega_{2}^{3}LC_{e}V_{deN}} \left(\frac{\pi}{2} - 1\right)$$

(26)

Taking the derivative of  $i_{dc}(t)$  with respect to t results in

$$\frac{di_{dc}(t)}{dt} = \omega_1 \left( K_p \cos \omega_1 t - \sin \omega_1 t \right) \tag{27}$$

According to (27),  $i_{dc}(t)$  reaches the maximum when  $\omega_1 t = \arctan(K)$  and the maximum value is  $\sqrt{1+K^2}$ . Combined with (26), the maximum value of  $\sigma_2$  satisfies

$$\sigma_2 \ge 1 - \frac{\sqrt{1 + K^2}}{O} \tag{28}$$

where Q is defined as

$$Q = 1 + \frac{V_{dcN}^2}{\omega_2 L P_N} + \frac{k_i}{\omega_2^3 L C_e} \left(\frac{\pi}{2} - 1\right)$$

(29)

In view of a margin between the estimated and actual values,  $1-(\sqrt{1+K^2}/Q)$  is used as a conservative index to construct the criterion, which is concluded as

$$\begin{cases} \sigma_2 = 1 - \frac{\sqrt{1 + K^2}}{Q} \ge \sigma_{\text{max}}, \text{ AC infeed is non-negligible} \\ \sigma_2 = 1 - \frac{\sqrt{1 + K^2}}{Q} < \sigma_{\text{max}}, \text{ otherwise} \end{cases}$$

(30)

Similarly, the deviation caused by ignoring the AC infeed depends on K and Q which are determined by the system and the control parameters. Based on (24) and (29), the factors influencing K, M and Q include the rated active power, the rated DC voltage, the equivalent SM capacitance, the equivalent inductance, and the integral gain of the DC voltage PI controller. Although the proportional gain of the DC voltage PI controller is not included in the criterion, the AC side contribution increases with the increase of  $k_p$ . The estimation difference caused by ignoring the AC infeed is proportional to the rated active power, the number of SMs, the integral and proportional gain of the DC voltage PI controller, while inversely proportional to the rated DC voltage and the SM capacitance.

# 3.3. Summary of the proposed criteria

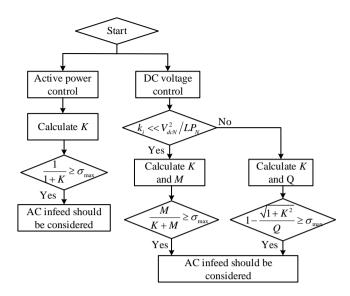

Based on the above detailed analysis, a flowchart of the proposed criteria for determining the necessity of considering AC infeed in the fault assessment is shown in Fig. 5. The concrete processes are described as follows.

Fig. 5. A flowchart for the proposed criteria for determining the necessity of considering AC infeed in the fault current assessment.

- Step 1: Start criterion. If the MMC operates in active power control mode, proceed to Step 2. And if the MMC operates in DC voltage control mode, proceed to Step 3.

- Step 2: Calculate the parameter K and compare 1/(1+K) with defined maximum allowable estimation difference  $\sigma_{\text{max}}$ . If  $1/(1+K) \ge \sigma_{\text{max}}$ , it indicates that the AC infeed should be considered in the fault assessment. Otherwise, the AC infeed can be ignored.

- Step 3: Compare  $k_i$  with  $V_{dcN}^2/LP_N$ . If  $k_i \ll V_{dcN}^2/LP_N$ , proceed to Step 4. Otherwise, proceed to Step 5.

- Step 4: Calculate the parameters K and M, and then compare M/(K+M) with  $\sigma_{\text{max}}$ . If  $M/(K+M) \ge \sigma_{\text{max}}$ , it indicates that the AC infeed should be considered. Otherwise, the AC infeed can be ignored.

- Step 5: Calculate parameters K and Q, and then compare 1-  $(\sqrt{1+K^2}/Q)$  with  $\sigma_{\text{max}}$ . If 1- $(\sqrt{1+K^2}/Q) \ge \sigma_{\text{max}}$ , the AC infeed should be considered. Otherwise, the AC infeed can be ignored.

#### 4. Simulation Verification

This section validates the accuracy and availability of the proposed criteria based on two different test systems. The accuracy of the proposed fault current estimation method considering the AC infeed is verified. The currents are calculated by the proposed method and compared with those obtained by the method which neglects the AC infeed and simulation results. Then, the availability of the proposed criteria is verified under different system parameters and control modes. The criterion is applied to determine the necessity of considering the AC infeed in the fault current estimation. The estimation difference caused by ignoring the AC infeed is provided to verify the availability of the criterion. The sensitivity analysis of the system and control parameters is also carried out to determine the dominant parameters affecting the AC infeed contribution. At last, the impact of the DC current limiting reactor on the proposed method is analyzed.

# 4.1. Test system

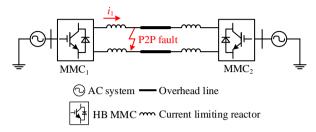

The test systems are based on a two-terminal MMC-HVDC system with different parameters, which is developed in PSCAD/EMTDC. Its schematic diagram is shown in Fig. 6. The MMC parameters of the two test systems are shown in Table 1, in which the second test system is established based on the case study in [26]. The second test system is slightly adapted by equipping the MMC with a current limiting reactor at the outlet.

$\mathsf{MMC}_1$  and  $\mathsf{MMC}_2$  are sending and receiving end converter stations, respectively. The DC fault current contribution from  $\mathsf{MMC}_1$  is  $i_1$ , with a reference direction from the sending end converter to the receiving end converter. The parameters of  $\mathsf{MMC}_1$  and  $\mathsf{MMC}_2$  are the same, while the control modes are different. To study the dynamic performance of the system, there is no additional control and protection action when a fault occurs.

Fig. 6. Two terminal MMC-HVDC system with a fault for analysis.

| Parameters                                             | First test system | Second test system |

|--------------------------------------------------------|-------------------|--------------------|

| Rated DC voltage $V_{dcN}$ (kV)                        | 500               | 420                |

| Rated active power $P_N$ (MW)                          | 1500              | 1250               |

| Number of SMs per arm                                  | 244               | 540                |

| Equivalent SM capacitance $C_e$ (mF)                   | 0.369             | 0.122              |

| Equivalent inductance $L_e$ (mH)                       | 33.3              | 93.3               |

| Equivalent resistance $R_e\left(\Omega\right)$         | 0.14              | 0.05               |

| Current limiting reactor (mH)                          | 225               | 100                |

| Proportionality gain of DC voltage PI controller $k_p$ | 4                 | 3.5                |

| Integration gain of DC voltage PI controller $k_i$     | 430               | 50                 |

Table 1. Parameters of the MMC for analysis.

# 4.2. Validation of the proposed criteria on the first test system

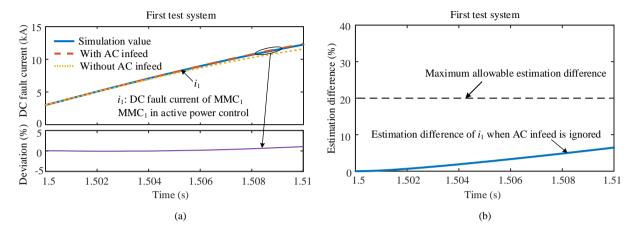

1) Active power control mode: the MMC<sub>1</sub> is in active power control mode while MMC<sub>2</sub> controls the DC voltage. It is assumed that a P2P DC fault with a fault resistance of 0.01  $\Omega$  occurs on the DC line at t=1.50 s. Based on the system parameters, the rate of rise of the fault current is about 1 kA/ms. Thus, in 5-10 ms after the DC fault, the fault current is increased by 5-10 kA, and 20% of it reaches 1 kA. Then the estimation difference reaches the same order of magnitude of the DC fault current. Therefore, the maximal allowable difference of the fault current estimation  $\sigma_{\text{max}}$  is set as 20% in this case. It must be noted that  $\sigma_{\text{max}}$  set in this paper is only used to verify the validity of the method.  $\sigma_{\text{max}}$  can be determined flexibly according to actual needs. According to (15), K is calculated as 4.605. The corresponding 1/(1+K) = 17.8 %, which is smaller than the pre-defined 20% maximum allowable difference. The AC infeed can be neglected.

To validate the presented criterion, the fault current  $i_1$  within 10 ms after the DC fault occurs is computed by the proposed method considering the AC infeed and shown in Fig. 7(a). The estimated value is then compared with those obtained by the method which neglects the AC infeed and the EMT simulation. The deviation between the estimated value considering the AC infeed and the simulated value is also presented at the bottom of Fig. 7(a). It can be seen from Fig. 7(a) that the deviation of  $i_1$  is within 2%, which indicates that the estimated current based on the proposed method is in close agreement with the simulated current. Compared with the method without considering the AC infeed, the proposed method is a little bit more accurate in estimating the fault current. When the requirement of accuracy is not strict, the slight accuracy improvement can be ignored for simpler and more time efficient estimation. Specifically, the estimation difference within 10 ms caused by ignoring the AC infeed does not exceed 10%, as shown in Fig. 7(b). Therefore, the AC infeed can be ignored in the fault current assessment. This conclusion is consistent with the result obtained by the proposed criterion. From Fig. 7(b), the maximum deviation within 10 ms is 6.5%,

which is smaller than 17.8%. This is because the criterion is aimed at the maximum estimation difference in the fault current rising stage. When estimating the peak value of the DC fault current, the estimation difference caused by ignoring the AC infeed is 17.8%. The detailed equation (14) is suitable when the fault assessment focuses on the system response for a fixed period of time and the estimation difference at a specific moment needs to be determined.

Fig. 7. DC fault current results of  $MMC_1$  in the first test system and active power control mode. (a) estimated and simulated values within 10 ms of  $i_1$ . (deviation = (the estimated fault current with considering AC infeed - the EMT simulation)/the EMT simulation); (b) fault current estimation difference of  $i_1$  within 10 ms caused by ignoring the AC infeed.

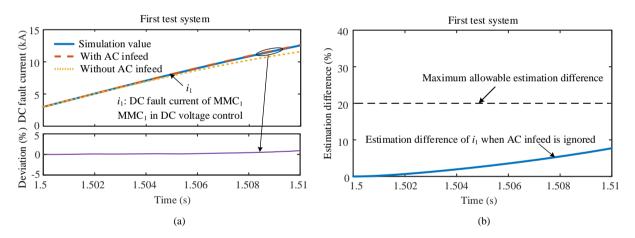

Fig. 8. DC fault current results of MMC<sub>1</sub> (DC voltage control mode) in the first test system. (a) estimated and simulated values of  $i_1$  (the deviation is defined in Fig.7); (b) fault current estimation difference within 10 ms caused by ignoring the AC infeed.

2) DC voltage control mode: MMC<sub>1</sub> is switched to the DC voltage control mode while MMC<sub>2</sub> controls the active power. A P2P fault with a fault resistance of 0.01  $\Omega$  is applied on the DC line at t = 1.50 s. The maximum allowable deviation  $\sigma_{\text{max}}$  is also set to 20%. Since  $V_{dcN}^2/(LP_N) = 345.1$ , which is smaller than  $k_i$ , the second criterion is used to determine the impact of AC infeed. According to (30), 1-  $(\sqrt{1+K^2}/Q)$  is calculated as 6.6%, which is smaller than  $\sigma_{\text{max}}$ . The AC infeed can be neglected.

The estimation results with and without considering the AC infeed and the simulation results are shown in Fig. 8(a). The results show that the proposed method has a similar accuracy with the EMT simulation. Compared with the method without considering the AC infeed, the proposed method provides a slight accuracy improvement, thus the AC infeed can be neglected. In addition, the fault current estimation difference within 10 ms caused by ignoring the

AC infeed is shown in Fig. 8(b). It can be found that the maximum difference does not exceed 10%, which is consistent with the proposed criterion.

As shown in Fig. 7, the DC fault current reaches 12.3 kA in 10 ms after the DC fault. An engineering prototype of 500kV DCCB has been developed, and the experimental verification of  $\pm$  25kA fault current interrupting has been completed [9,27]. Thus, the DCCB is able to interrupt the DC fault current within 10 ms without blocking the MMC. In this test system, a 4500 V/3000 A IGBT module can be applied (ABB 5SNA3000K452300). For the IGBT, manufacturers can guarantee the withstand capability of commercial devices up to 10  $\mu$ s under the short-circuit current  $I_{SC}$  [28].  $I_{SC}$  of the 4500 V/3000 A IGBT is 12 kA. In this case, the maximum arm current of the MMC within 10 ms after the DC fault is 7.19 kA, which is below 12 kA, and thus the IGBT will not be destroyed without blocking the MMC. Therefore, it is feasible to investigate the impact of the AC infeed on the DC fault current estimation on the premise that the MMC blocking has not occurred.

#### 4.3. Validation of the proposed criteria on the second test system

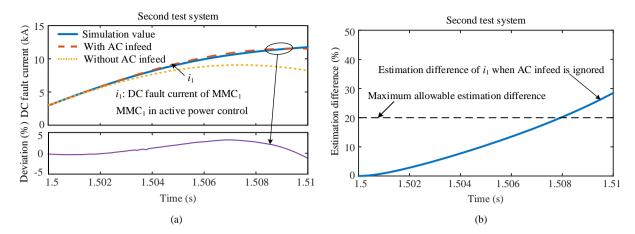

1) Active power control mode: when the MMC<sub>1</sub> is in active power control mode while MMC<sub>2</sub> controls the DC voltage, the parameter K can be calculated as 2.88. The corresponding 1/(1+K) = 25.8 %, which is larger than the predefined 20% maximum allowable difference. In contrary to the first test system case, the AC infeed cannot be neglected in estimating the fault current.

It can be found from Fig. 9(a) that the maximum deviation between the estimation result considering the AC infeed and the simulation result is within 3%. The results show good agreement between the theoretically estimated currents obtained by the proposed method and the simulated values. Compared to the proposed method, the method without considering the AC infeed shows a clear deviation in the fault current estimation. During the fault current rising stage, the maximum estimation difference caused by ignoring the AC infeed exceeds 25%, as shown in Fig. 9(b). The estimation difference can be very large without considering the AC infeed. The results show that the proposed criterion is applicable to determine the necessity of considering the AC infeed in the fault current assessment.

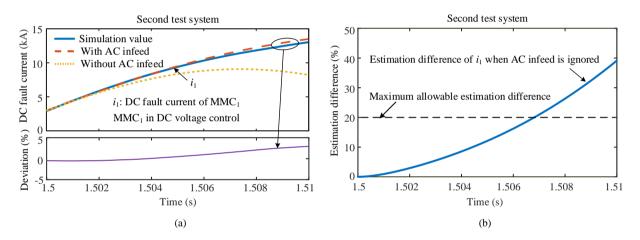

2) DC voltage control mode: the MMC<sub>1</sub> is in DC voltage control mode and MMC<sub>2</sub> is in active power control mode. Since  $V_{dcN}^2/(LP_N)$ =481.6, which is much larger than  $k_i$ , the first criterion is used to determine the impact of AC infeed. According to (25), M/(K+M) is calculated as 28.9 %, which is much larger than  $\sigma_{max}$ . The AC infeed can not be neglected.

This conclusion can be verified by the estimated results as shown in Fig. 10. From Fig. 10(a), the accuracy of the proposed method is much more superior for the current compared with the method without considering the AC infeed. Furthermore, the estimation difference within 10 ms caused by ignoring the AC infeed reaches more than 30%, as shown in Fig. 10(b). The proposed criterion focuses on the maximum estimation difference over a period of time after the fault, not for the whole fault stage. If this value exceeds the maximum allowable difference, the actual difference during the fault current rising stage certainly exceeds the allowable one, since the estimation difference increases with time. When the fault current assessment focuses on the system response for a certain period of time and requires high accuracy determining the estimation difference at a specific moment, the detailed equation given in (18) is preferred.

In the second test system, when the  $MMC_1$  is in active power and DC voltage control modes, the DC fault current reaches 11.7 kA and 13 kA in 10 ms after the DC fault, respectively. Similarly, the DCCB with capacity of  $\pm 25$ kA is able to interrupt the DC fault current without blocking the MMC [9,27]. In this test system, the maximum arm currents within 10 ms are 8.63 and 9.42 kA under the active power and DC voltage control modes, respectively. By using the 4500 V/3000 A IGBT, it will not be destroyed without blocking the MMC.

Compared with the active power control mode, the fault current is increased under the DC voltage control mode, as shown in Figs. 7 to 10. Besides, ignoring the AC infeed has a larger influence on the fault assessment for the DC voltage controlled MMC. This is because the DC voltage control mode improves the ability of the converter to control the DC voltage. The converter transmits more energy to the DC side to suppress the voltage drop. As a result, the fault current increases with the ability to control the DC voltage. The proposed method can analyze the current characteristics under different MMC controls, while the method without considering the AC infeed is not able to reflect the impact of the control modes on the fault current.

Fig. 9. DC fault current results of MMC<sub>1</sub> in the second test system and active power control mode. (a) estimated and simulated values of  $i_1$  (the deviation is defined in Fig.7); (b) fault current estimation difference of  $i_1$  within 10 ms caused by ignoring the AC infeed.

Fig. 10. DC fault current results of MMC<sub>1</sub> in the second test system and DC voltage control mode. (a) estimated and simulated values of  $i_1$  (the deviation is defined in Fig.7); (b) fault current estimation difference of  $i_1$  within 10 ms caused by ignoring the AC infeed.

# 4.4. Parameter sensitivity analysis

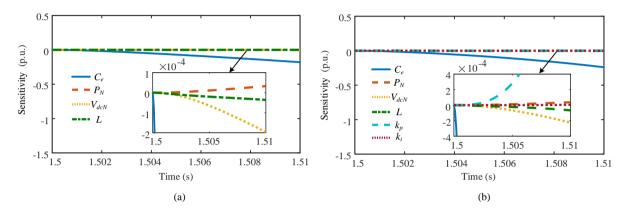

The estimation difference caused by ignoring the AC infeed is influenced by the system parameters, including the equivalent SM capacitance  $C_e$ , the rated active power  $P_N$ , the rated DC voltage  $V_{dcN}$  and the equivalent inductance L. For the MMC in the DC voltage control mode, the estimation difference is also influenced by the control parameters  $k_p$  and  $k_i$ .

The parameters' sensitivity on the output is defined as [29]

$$\frac{\partial f\left(t,\theta\right)}{\partial \theta} = \lim_{\Delta\theta \to 0} \frac{f\left(t,\theta_0 + \Delta\theta\right) - f\left(t,\theta_0\right)}{\Delta\theta} \tag{31}$$

where  $f(t,\theta)$  is the output of the index. When the MMC is in the active power and DC voltage control modes,  $f(t,\theta)$  is the output of (13) and (18), respectively.  $\theta$  is the system and control parameter.  $\Delta\theta$  is the relative change of  $\theta$ .

The first test system is adopted to analyse the parameters sensitivity. For MMC in the active power control mode, the system parameters sensitivity to the estimation difference caused by ignoring the AC infeed is shown in Fig. 11(a). It shows that the equivalent SM capacitance represents great influence on the fault current estimation difference caused

by ignoring the AC infeed. The next is parameter  $V_{dcN}$ . The rated active power and the equivalent inductance have a relatively little effect on the estimation difference. This means that the discharge capacity of the SMs has a major effect on the AC infeed contribution. When the equivalent SM capacitance is larger, the energy storage of the capacitor is larger. As a result, the rising rate and the maximum value of the fault current are increased. Compared with the AC infeed, the capacitor discharging is the dominant process. The proportion of AC infeed contribution to the total fault current is decreased, making the AC infeed negligible in the fault current assessment. For instance, the equivalent SM capacitance of the first test system is 0.369 mF, while that of the second test system is 0.122 mF. The maximum estimation difference within 10 ms caused by ignoring the AC infeed is 6.5% and 25.8%, respectively, for the first and second test systems.

Fig. 11. Parameters' sensitivity to the estimation difference caused by ignoring the AC infeed. (a) MMC in the active power control mode; (b) MMC in the DC voltage control mode.

For MMC in the DC voltage control mode, the system and control parameters sensitivity to the index is shown in Fig. 11(b). It shows that the SM equivalent capacitance represents a great influence on the estimation difference caused by ignoring the AC infeed. The maximum differences within 10 ms caused by ignoring the AC infeed are 7.7% and 39.1%, respectively, for the first and second test systems. The next is parameter  $k_p$ . The rated active power, the rated DC voltage, the equivalent inductance, and the integratal gain have relatively little effect on the estimation difference. Compared with the active power control mode, the system parameters sensitivity to the estimation difference is larger under the DC voltage control mode.

# 4.5. Impact of the current limiting reactor

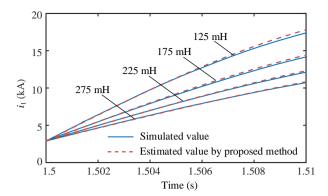

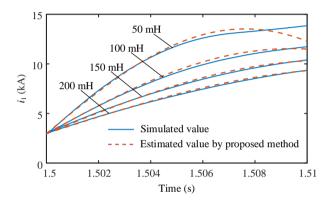

The impact of the DC current limiting reactor on the proposed method is analyzed. Taking the first test system as an example, when the MMC<sub>1</sub> is in active power control mode, Fig.12 shows the estimated DC fault currents  $i_1$  considering the AC infeed and the simulated DC fault currents when the DC reactor varies from 125 mH to 275 mH. It can be seen that the estimated results based on the proposed method are in close agreement with the simulated results under different current limiting reactors. After compared with the results without considering the AC infeed, the proposed method thus can reflect the estimation deviation of the fault current caused by neglecting the AC infeed.

In the second test system, Fig. 13 shows the DC fault currents when the DC reactor varies from 50 mH to 200 mH. As the DC inductance decreases, the fault current reaches its peak more quickly. It is shown that the DC fault currents obtained by the proposed method is nearly identical to the simulated values before the current reaches its maximum value. But the estimated DC current becomes inaccurate after it surpasses the maximum value. This is because if the DC short-circuit fault lasts too long, the MMC capacitors will continue to discharge, so the DC voltage will collapse eventually. At this point, the assumptions based on which the MMC equivalent model is built have been destroyed, thus the characteristics of the DC fault current can no longer be described by the proposed equivalent circuits [23]. However, it should be noted that the proposed method only focuses on the rising phase of the DC fault current. Therefore, the DC inductor doesn't influence the performance of the proposed method.

Fig. 12. Estimated and simulated values of  $i_1$  with different DC reactors in the first test system. MMC<sub>1</sub> is in active power control mode.

Fig. 13. Estimated and simulated values of  $i_1$  with different DC reactors in the second test system.  $MMC_1$  is in active power control mode.

#### 5. Discussion

When evaluating the DC fault current considering the AC infeed, this paper ignores the dynamics of the current control loop. The simplification of ignoring the current control loop may lead to some deviations in the DC fault current estimation. However, if the dynamics of the current control loop is considered, the equivalent circuit in terms of complex frequency domain is complex, and it is a very difficult task to derive the time domain expression of the DC fault current. The obtained criterion with complicated expression is difficult to be applied in practical situations. For practical purpose of the method, the current control loop is ignored through the simplification.

For the d axis, Fig.14 shows the block diagram of the inner current control loop of the MMC, where  $k_{pi}$  and  $T_{ii}$  are the proportional gain and integral time constant of the current loop PI controller, respectively,  $T_a$  is the time delay caused by the MMC switches,  $R_{eqac}^*$  is the equivalent resistance which is composed of the AC resistance and half of the arm resistance, and  $\tau$  is the time constant which is defined by  $L_{eqac}^*/R_{eqac}^*$ , where  $L_{eqac}^*$  is the equivalent inductance which is composed of the AC inductance and half of the arm inductance. The variables with the superscript "\*" are of per-unit values. Based on Fig. 14, the closed loop transfer function of current controller is given as

$$H_{CL}(s) = \frac{i_{sd}^*}{i_{sdref}^*} = \frac{k_{pi}(1 + T_{ii}s)}{R_{eqac}^* T_{ii}s(1 + T_as)(1 + \tau s) + k_{pi}(1 + T_{ii}s)}$$

(32)

Taking the DC voltage controlled MMC as an example, the current source in the MMC equivalent circuit can be obtained as

Fig. 14. Block diagram of the current control loop.

$$i_{s} = \frac{P_{N}}{V_{dcN}^{2}} \left( \frac{V_{dcref}}{s} - sLI_{dc}\left(s\right) + Li_{dc}\left(s_{0}\right) \right) \cdot \left(k_{p} + \frac{k_{i}}{s}\right) H_{CL}\left(s\right) + \frac{i_{s0}}{s}$$

$$(33)$$

The DC fault current in terms of complex frequency domain considering the current loop thus can be obtained as

$$I_{dc}(s) = \frac{V_{dcN}^{2} \left[ s^{2} C_{e} L i_{dc(0_{-})} + s V_{dc(0_{-})} C_{e} + i_{dc(0_{-})} \right] + P_{N} \left( V_{dcref} + s L i_{dc(0_{-})} \right) \cdot (k_{p} + \frac{k_{i}}{s}) H_{CL}(s)}{s^{2} C_{e} V_{dcN}^{2} (R + s L) + s V_{dcN}^{2} + s L P_{N} \left( s k_{p} + k_{i} \right) H_{CL}(s)}$$

(34)

It can be seen from (42) that the order of  $I_{dc}(s)$  reaches seven. The time domain expression of the DC fault current is too complicated to apply in practical situations. Therefore, the simplification of the dynamics of the control loop is needed to improve practicability of the method.

To achieve better dynamic performance and adequate speed response of the inner control loop, modulus optimum is conventionally used for tuning the current control parameters due to the fast response and simplicity [30-33]. The PI parameters then can be written as [30-32]

$$k_{pi} = \frac{R_{eqac}^* \tau}{2T}, T_{ii} = \tau \tag{35}$$

Thus, the closed loop transfer function is simplified to

$$H_{CL}(s) = \frac{1}{2T_a^2 s^2 + 2T_a s + 1} \tag{36}$$

$T_a$  is defined as  $1/(2f_{sw})$  [30,31], where  $f_{sw}$  is the switching frequency of the converter. Since  $f_{sw}$  is usually large enough for the system to achieve ideal modulation, the closed loop transfer function can be simplified as [22]

$$H_{CL}(s) = \frac{i_{sd}^*}{i_{sdref}^*} \approx 1 \tag{37}$$

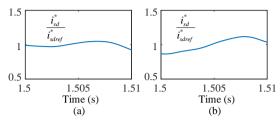

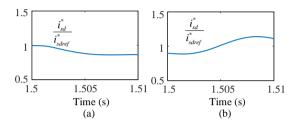

According to (37),  $i_{sd}$  tracks  $i_{sdref}$  instantaneously, so the dynamics of the current control is ignored. Based on the case study, Figs. 15 and 16 show the variation of  $i_{sd}^*/i_{sdref}^*$  in the first and second test system, respectively. It can be seen that  $i_{sd}^*/i_{sdref}^*$  varies between 0.88 and 1.2, which further confirms that the current loop can be ignored for simplification.

In addition, from Figs. 7 to 10, the maximum deviation between the estimation results which neglect the current loop and the simulation results which involve the current loop is within 3%. It indicates that ignoring the current loop has acceptable accuracy for the fault current estimation. Moreover, the displayed estimation deviation contains multiple sources, which means the deviation caused by ignoring the current loop control is much less. On the contrary, the AC infeed is the main source that results in the estimation deviation. The neglect of the current loop does not affect

the assessment of the impact of the AC infeed. We will perfect the proposed method by considering the dynamics of the current loop in the future research.

Fig. 15. The variation of  $i_{sd}^*/i_{sdref}^*$  in the first test system. (a) MMC<sub>1</sub> is in active power control mode. (b) MMC<sub>1</sub> is in DC voltage control mode.

Fig. 16. The variation of  $t_{sd}^*/t_{sdref}^*$  in the second test system. (a) MMC<sub>1</sub> is in active power control mode. (b) MMC<sub>1</sub> is in DC voltage control mode.

#### 6. Conclusion

Whether the AC infeed needs to be considered in the fault current assessment of the MMC without blocking is an important problem. Prior arts draw conclusions only based on specific parameters. This paper presents criteria for determining the necessity of considering the AC infeed in the fault current assessment. The proposed criteria rely on the system and control parameters, without limiting to some specific cases. They contribute to determining whether the AC infeed should be considered or not in order to avoid the potential risks of ignoring the AC infeed intuitively. Following conclusions can be drawn from both theoretical analyses and simulation verifications.

- The proposed criteria are effective and can be applied to determine the impact by ignoring the AC infeed in the DC fault assessment.

- The AC infeed contribution is proportional to the rated active power, the number of SMs, the integral and proportional gain of the DC voltage PI controller, while inversely proportional to the SM capacitance and the rated DC voltage.

- Among various factors, the equivalent SM capacitance, which is the ratio of SM capacitance to the number of SMs, has a large impact on the AC infeed contribution. When the equivalent capacitance is 0.122 mF, the estimation difference of the fault current caused by ignoring the AC infeed reaches 25.8% within 10 ms.

# Acknowledgements

The authors gratefully acknowledge the financial support from the National Key R&D Program of China under Grant 2018YFB0904600.

#### Appendix A.

The detailed equations of the DC fault current under different control modes are given in this section.

A.1. Fault current of MMC considering the AC infeed

1) For the MMC in active power control mode: the DC fault current considering the AC infeed is given as:

$$i_{dc_{-P}}(t) = i_{dc(0_{-})} \left[ 1 - \frac{e^{-\xi_{1}\omega_{1}t}}{\sqrt{1 - \xi_{1}^{2}}} \sin\left(\omega_{1}\sqrt{1 - \xi_{1}^{2}}t + \varphi_{1}\right) \right] + \frac{V_{dc(0_{-})}e^{-\xi_{1}\omega_{1}t}}{\omega_{1}L\sqrt{1 - \xi_{1}^{2}}} \sin\left(\omega_{1}\sqrt{1 - \xi_{1}^{2}}t\right) - \frac{i_{dc(0_{-})}e^{-\xi_{1}\omega_{1}t}}{\sqrt{1 - \xi_{1}^{2}}} \sin\left(\omega_{1}\sqrt{1 - \xi_{1}^{2}}t - \varphi_{1}\right)$$

(A1)

$$\omega_{\rm l} = \sqrt{\frac{1}{LC_e}}, \ \xi_{\rm l} = \frac{R}{2} \sqrt{\frac{C_e}{L}}, \ \varphi_{\rm l} = \arctan \frac{\sqrt{1 - \xi^2}}{\xi}$$

(A2)

2) For the MMC in DC voltage control mode: the DC fault current in terms of complex frequency domain is obtained as:

$$I_{dc\_DC}(s) = \frac{sC_e V_{dcN}^2 L i_{dc(0_-)}}{G_1} + \frac{C_e V_{dcN}^2 V_{dc(0_-)} + P_N L i_{dc(0_-)} k_p}{G_1} + \frac{P_N V_{dcN} k_i}{s^2 G_1} + \frac{P_N L i_{dc(0_-)} k_i + i_{dc(0_-)} V_{dcN}^2 + P_N V_{dcN} k_p}{sG_1}$$

(A3)

$$G_1 = s^2 L C_e V_{dcN}^2 + s \left( R C_e V_{dcN}^2 + P_N L k_p \right) + V_{dcN}^2 + P_N L k_i$$

(A4)

By the inverse Laplace transform, the time-domain expression of the fault current considering AC infeed is derived as

$$i_{dc\_DC}(t) = -i_{dc(0_{-})} \frac{e^{-\xi_{2}\omega_{2}t}}{\sqrt{1-\xi_{2}^{2}}} \sin\left(\omega_{2}\sqrt{1-\xi_{2}^{2}}t - \varphi_{2}\right) + \frac{\left(V_{dc(0_{-})}C_{e}V_{dcN}^{2} + P_{N}Li_{dc(0_{-})}k_{p} - P_{N}k_{i}V_{dcN}/\omega_{2}^{2}\right)}{LC_{e}V_{dcN}^{2}\omega_{2}\sqrt{1-\xi_{2}^{2}}}$$

$$\cdot e^{-\xi_{2}\omega_{2}t} \sin\left(\omega_{2}\sqrt{1-\xi_{2}^{2}}t\right) + \frac{P_{N}k_{i}}{\omega_{2}^{2}LC_{e}V_{dcN}}t + \frac{\left(P_{N}Li_{dc(0_{-})}k_{i} + i_{dc(0_{-})}V_{dcN}^{2} - 2\xi_{2}P_{N}k_{i}V_{dcN}/\omega_{2} + P_{N}k_{p}V_{dcN}\right)}{\omega_{2}^{2}LC_{e}V_{dcN}^{2}}. \tag{A5}$$

$$\left[1 - \frac{e^{-\xi_{2}\omega_{2}t}}{\sqrt{1-\xi_{2}^{2}}}\sin\left(\omega_{2}\sqrt{1-\xi_{2}^{2}}t + \varphi_{2}\right)\right]$$

$$\omega_2 = \sqrt{\frac{1}{LC_e} + \frac{P_N k_i}{C_e V_{dcN}^2}} \tag{A6}$$

$$\xi_2 = \frac{R/L + P_N k_p / C_e V_{dcN}^2}{2\omega_2} \tag{A7}$$

$$\varphi_2 = \arctan \frac{\sqrt{1 - \xi_2^2}}{\xi_2} \tag{A8}$$

#### A.2. Fault current of MMC without considering the AC infeed

$$i_{dc}(t) = \frac{V_{dc(0_{-})}e^{-\xi_0\omega_0 t}}{\omega_0 L\sqrt{1-\xi_0^2}} \sin\left(\omega_0 \sqrt{1-\xi_0^2 t}\right) - \frac{i_{dc(0_{-})}e^{-\xi_0\omega_0 t}}{\sqrt{1-\xi_0^2}} \sin\left(\omega_0 \sqrt{1-\xi_0^2 t} - \varphi_0\right)$$

(A9)

$$\omega_0 = \omega_1, \ \xi_0 = \xi_1, \ \varphi_0 = \varphi_1 \tag{A10}$$

#### References

- [1] Li X, Zhao B, Wei Y, Xie X, Hu Y, Shu D. DC fault current limiting effect of MMC submodule capacitors. Int J Elect Power Energy Syst 2020; 115: 105444.

- [2] Wang S, Li C, Adeuyi OD, Li G, Ugalde-Loo CE, Liang J. Coordination of MMCs with hybrid DC circuit breakers for HVDC grid protection. IEEE Trans Power Del 2019; 34(1): 11-22.

- [3] Stumpe M, Tünnerhoff P, Dave J, Schnettler A, Ergin D, Schön A, et al. DC fault protection for modular multi-level converter-based HVDC multi-terminal systems with solid state circuit breakers. IET Gener Transm Distrib 2018; 12(12): 3013-3020.

- [4] Cwikowski O, Wickramasinghe HR, Konstantinou G, Pou J, Barnes M, Shuttleworth R. Modular multilevel converter DC fault protection. IEEE Trans Power Del 2018; 33(1): 291-300.

- [5] Li B, Li Y, He J. A DC fault handling method of the MMC-based DC system. Int J Elect Power Energy Syst 2017; 93: 39-50.

- [6] Nguyen TH, Hosani KA, El Moursi MS, Blaabjerg F. An overview of modular multilevel converters in HVDC transmission systems with STATCOM operation during pole-to-pole DC short circuits. IEEE Trans Power Electron 2019; 34(5): 4137-4160.

- [7] Li P, Ma J, Zhou X, Zhang M, Thorp JS. A protection scheme for DC-side fault based on a new MMC sub-module topology. Int J Elect Power Energy Syst 2020: 114: 105406.

- [8] Zhou G, Han M, Filizadeh S, Cao X, Huang W. Studies on the combination of RSFCLs and DCCBs in MMC-MTDC system protection. Int J Elect Power Energy Syst 2021; 125: 106532.

- [9] Zhou Y, Huang Y, Liu H, Tai Y, Yang H, Men B. Research and development of 500kV hybrid HVDC circuit breaker with current commutation drive circuit. In: Proc. IEEE eGRID; Nov. 2019.

- [10] Xue S, Liu B, Wang S, Chen X, Zhu X, Lu J. A modular hybrid DC circuit breaker with fault current self-adaptive control and protection coordination. Int J Elect Power Energy Syst 2022; 134:107434.

- [11] Pei X, Smith A, Cwikowski O, Barnes M. Hybrid DC circuit breaker with coupled inductor for automatic current commutation. Int J Elect Power Energy Syst 2020; 120: 106004.

- [12] Song G, Wang T, Huang X, Zhang C. An improved averaged value model of MMC-HVDC for power system faults simulation. Int J Elect Power Energy Syst 2019; 110: 223-231.

- [13] Xu J, Zhu S, Li C, Zhao C. The enhanced DC fault current calculation method of MMC-HVDC grid with FCLs. IEEE J Emerg Sel Topics Power Electron 2019; 7(3): 1758-1767.

- [14] Wang Y, Yuan Z, Fu J, Li Y, Zhao Y. A feasible coordination protection strategy for MMC-MTDC systems under DC faults. Int J Elect Power Energy Syst 2017; 90:103-111.

- [15] Li C, Zhao C, Xu J, Ji Y, Zhang F, An T. A pole-to-pole short circuit fault current calculation method for DC grids. IEEE Trans Power Syst 2017; 32(6): 4943-4953.

- [16] Langwasser M, Carne GD, Liserre M, Biskoping M. Fault current estimation in multi-terminal HVdc grids considering MMC control. IEEE Trans Power Syst 2019; 34(3): 2179-2189.

- [17] Gao S, Ye H, Liu Y. Accurate and efficient estimation of short-circuit current for MTDC grids considering MMC control. IEEE Trans Power Del 2020; 35(3): 1541-1552.

- [18] Guo Y, Li H, Liang Y, Wang G. A method to calculate short-circuit faults in high-voltage DC grids. IEEE Trans Power Del 2021; 36(1): 267-279

- [19] Yang H, Dong Y, Li W, He X. Average-value model of modular multilevel converters considering capacitor voltage ripple. IEEE Trans Power Del 2017: 32(2): 723-732.

- [20] Beddard A, Sheridan CE, Barnes M, Green TC. Improved accuracy average value models of modular multilevel converters. IEEE Trans Power Del 2016; 31(5): 2260-2269.

- [21] Zhang Y, Ravishankar J, Fletcher J, Li R, Han M. Review of modular multilevel converter based multi-terminal HVDC systems for offshore wind power transmission. Renew Sustain Energy Rev 2016; 61: 572-586.

- [22] Liu S, Xu Z, Hua W, Tang G, Xue Y. Electromechanical transient modeling of modular multilevel converter based multi-terminal HVDC systems. IEEE Trans Power Syst 2014; 29(1): 72-83.

- [23] Xiao L, Xu Z, Xiao H, Zhang Z, Wang G, Xu Y. Electro-mechanical transient modeling of MMC based multi-terminal HVDC system with DC faults considered. Int J Elect Power Energy Syst 2019; 113: 1002-1013.

- [24] Tao Y, Li B, Liu T. Pole-to-ground fault current estimation in symmetrical monopole high-voltage direct current grid considering modular multilevel converter control. Electron Lett 2020; 56(8): 392-395.

- [25] Wang Y, Wen W, Zhang C, Chen Z, Wang C. Reactor sizing criterion for the continuous operation of meshed HB-MMC-based MTDC system under DC faults. IEEE Trans Ind Appl 2018; 54(5): 5408-5416.

- [26] Pan E, Yue B, Mei N, Yuan B. System Design of ±420 kV Chongqing-Hubei Back-to-Back HVDC Project of China. Autom Electric Power Syst 2021; 45(10): 175-183.

- [27] Feng L, Gou R, Zhuo F, Yang X, Zhang F. Research on the breaking branch for a hybrid DC circuit breaker in ±500 kV voltage-sourced converter high-voltage direct current grid. IET Power Electron 2020; 13(16): 3560-3570.

- [28] Chen Y, Li W, Iannuzzo F, Luo H, He X, Blaabjerg F. Investigation and Classification of Short-Circuit Failure Modes Based on Three-Dimensional Safe Operating Area for High-Power IGBT Modules. IEEE Trans Power Electron 2018; 33(2): 1075-1086.

- [29] Shu L, Zheng J, Shen X, Yin H, Li J. Parameters' sensitivity analysis of grid-connected photovoltaic power generation model under different kinds of disturbances. In: Proc. IEEE Symp Elect Electron Eng; 2012. p. 4-27, Kuala Lumpur, Malaysia.

- [30] Rabie D, Mohamed YS, Shehata EG. Voltage Source Converter Control and Stability Analysis of VSC-HVDC System with High DC-Link Impedance. In: Proc. Int Mid East Power Syst Conf; 2019. p. 667-674, Cairo, Egypt.

- [31] Bajracharya C, Molinas M, Suul JA, Undeland TM. Understanding of tuning techniques of converter controllers for VSC-HVDC. In: Proc. Nordic Workshop Power Ind Electron; 2008. Espoo, Finland.

- [32] Xu K, Xian X, Cheng J, Tao F. Tuning method of PI controller of VSC-HVDC based on modulus and symmetrical optimum. Power Syst Prot Control 2016; 44(2): 122-127.

- [33] Faisal SF, Beig AR, Thomas S. Time Domain Particle Swarm Optimization of PI Controllers for Bidirectional VSC HVDC Light System. Energies 2020; 13(4):866.