# **Aalborg Universitet**

# Reliability Enhancement of 1500-V DC-link Photovoltaic Power Converters

He, Jinkui

DOI (link to publication from Publisher): 10.54337/aau466407351

Publication date: 2021

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

He, J. (2021). *Reliability Enhancement of 1500-V DC-link Photovoltaic Power Converters*. Aalborg Universitetsforlag. https://doi.org/10.54337/aau466407351

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# RELIABILITY ENHANCEMENT OF 1500-V DC-LINK PHOTOVOLTAIC POWER CONVERTERS

# BY JINKUI HE

**DISSERTATION SUBMITTED 2021**

# Reliability Enhancement of 1500-V DC-link Photovoltaic Power Converters

Ph.D. Dissertation Jinkui He Dissertation submitted: November, 2021

PhD supervisor: Prof. Francesco Iannuzzo

Aalborg University

Assistant PhD supervisors: Assistant Prof. Ariya Sangwongwanich

Aalborg University

Prof. Yongheng Yang Zhejiang University, China

PhD committee: Associate Professor Szymon Bęczkowski

Aalborg University, Denmark

Professor Marta Molinas

Norwegian University of Science and Technology,

Norway

Professor Martin Ordonez

University of British Columbia, Canada

PhD Series: Faculty of Engineering and Science, Aalborg University

Department: Department of Energy Technology

ISSN (online): 2446-1636

ISBN (online): 978-87-7573-979-0

Published by: Aalborg University Press Kroghstræde 3

DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk

forlag.aau.dk

© Copyright: Jinkui He

Printed in Denmark by Rosendahls, 2021

# **Abstract**

Photovoltaic (PV) systems are becoming ever more popular in the power industry. It is expected that PV energy will share a more significant part in the world's future energy production. In this energy transition, the reduction of PV energy cost is of great importance. One standard solution is adopting the 1500-V PV strings instead of the 1000-V ones. By doing so, the installation cost, as well as the power losses (e.g., due to cabling), can be reduced significantly, which contributes to the cost reduction of PV energy. However, the increased PV voltage also poses challenges to PV inverters. The increased voltage stress has pushed the inverter design from the conventional two-level topology toward multi-level topology for achieving efficient and reliable power conversion. Although a few commercial PV power converters are already available on the market, the converter reliability assessment for this particular application is of high interest. Moreover, the control strategy should also be improved in order to maintain high reliability under the 1500-V operation.

Thus, this Ph.D. project has explored the design and control of 1500-V PV power converters with a focus on reliability enhancement. The research work can be divided into three major aspects: 1) comparative evaluation of 1500-V PV power converters in terms of reliability, 2) investigation of system parameters on the reliability of 1500-V PV power converters, and 3) thermal optimized control for more reliable and cost-effective 1500-V PV power converters.

Firstly, to design a reliable PV power converter, an early-stage converter reliability evaluation is of great importance in the design phase. A comparative thermal performance evaluation of 1500-V PV inverters based on standard two-level and three-level topologies has been presented in Chapter 2, which is based on the thermal stress analysis under constant power generation (CPG) control operation. The result comparison indicated that, compared with the two-level topology, the three-level topologies are more suitable for 1500-V PV applications due to their lower thermal stresses. Furthermore, the reliability performance of the three-level topologies, i.e., I-type and T-type, has been evaluated considering the influence of voltage stress, switching frequency, and mission profile. The results reveal that these factors have a significant

influence on the inverter lifetime and can be used to justify the topology selection for the corresponding systems.

Secondly, except for the topology selection for designing a highly reliable 1500-V PV system, it is also important to consider the impact of system parameters on the performance and reliability of PV power converters, which has been presented in Chapter 3. The performance of 1500-V PV systems with centralized string inverter solutions has been discussed, where the power losses on the main components, i.e., DC wires, inverters, AC filters, and isolation transformers, are estimated considering the impact of system voltage ratings. The comparison results indicate that the centralized string inverter solutions with higher DC and AC voltages outperform the solutions with lower DC and AC voltages in terms of loss and cost reduction (lower wire loss and fewer inverter units). In addition, the 1500-V PV-battery system has been investigated with a comparison of DC- and AC-coupled configurations. With the reliability analysis from the component level to the system level, the most lifetime-critical part in each level has been identified, which will be beneficial to the design of the PV-battery systems in terms of reliability.

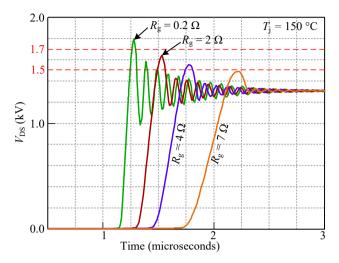

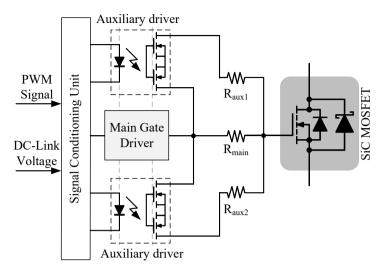

Thirdly, considering the 1500-V PV applications, new reliability concerns are raised, which are related to the increased DC-link voltage stress. Several methods for improving the reliability of 1500-V PV inverters have been presented in Chapter 4. For the SiC-based 1500-V two-level PV inverters, the possibility for improving their reliability through the variable gate resistance design was investigated considering mission profiles. Compared with the fixed gate resistance design for the highest voltage stress, the proposed approach, i.e., the variable gate resistance, could vary the external gate resistance based on the DC-link voltage variation, minimizing the power loss thus the thermal stress while keeping a safe blocking voltage margin. The reliability improvements can also be achieved through the control in operation. A junction temperature control strategy has been proposed in Chapter 4. By applying this control strategy, the device junction temperature would not exceed a certain threshold value during operation, hence extending the device lifetime. Moreover, the solution for improving the thermal performance of PV inverters during abnormal grid conditions has also been explored. With the proposal to achieve an improved thermal balance among the power devices of the three-level I-type 1500-V PV inverters, a modified discontinuous modulation strategy has also been proposed in Chapter 4, where enhanced reactive power support is expected during low-voltage ride-through operations.

# Resumé

Fotovoltaiske (PV) systemer er ved at blive en af de væsentlige vedvarende energikilder og spiller en voksende rolle i dagens elnet. Flere solcelleanlæg forventes at blive installeret i den kommende fremtid og vil dække en stor del af elproduktionen. I denne overgang, bør omkostningerne til PV-energi reduceres yderligere. En standardløsning er at øge den maksimale DC-linkspænding i PV-systemet fra de traditionelle 1000 V til 1500 V. Fordelen ved at gøre det er et betydeligt fald i installationsomkostningerne, strømtab (f.eks. på grund af kabler) og dermed omkostningerne til PV-energi. Den øgede DC-link-spænding stiller dog også en udfordring for PV-invertere, som er nøglekomponenterne for at opnå effektiv og pålidelig strømkonvertering. Den øgede spændings ved DC-forbindelsen har skubbet inverterdesignet fra den konventionelle to-niveauer topologi til multilevel topologi. Selvom nogle få kommercielle produkter allerede er tilgængelige på markedet, er vurderingen af konverterens pålidelighed for denne særlige anvendelse af stor interesse at blive undersøgt. Desuden bør kontrolstrategien også forbedres for at opretholde høj pålidelighed under 1500-V driften.

Denne ph.d. projektet har udforsket design og styring af 1500-V PV-strømomformere med fokus på øget pålidelighed. Forskningsarbejdet kan opdeles i tre hovedaspekter: 1) Komparativ evaluering af 1500-V PV-effektomformere med hensyn til pålidelighed, 2) Undersøgelse af systemparametre vedrørende pålideligheden af 1500-V PV-effektomformere og 3) Termisk optimeret styring for mere pålidelige og omkostningseffektive 1500-V PV-strømomformere.

For det første, for at sikre en effektiv og pålidelig PV-effektkonvertering, er en tidlig pålidelighedsvurdering vigtig i designfasen af PV-strømkonverteren og derefter hele systemet. En sammenlignende termisk ydeevneevaluering af 1500-V PV-invertere baseret på to-niveau- og tre-niveau-topologier er præsenteret i kapitel 2, som er baseret på den termiske spændingsanalyse under konstant strømgenerering (CPG). Resultaterne indikerede, at sammenlignet med to-niveau-topologien er tre-niveau-topologierne mere egnede til 1500-V PV-anvendelser på grund af deres lavere termiske stress. Derudover blev pålidelighedsydelsen af de to tre-niveau topologier (dvs. I-type og T-type)

evalueret med hensyn til virkningen af spænding stress, switching frekvens og missionsprofil. Resultaterne afslører, at disse faktorer har en betydelig indflydelse på inverterens levetid og kan bruges til at retfærdiggøre valget af topologier for tre-niveau inverterne i de tilsvarende systemer.

For det andet, bortset fra topologivalget til at designe et yderst pålideligt 1500-V PV-system, er det også vigtigt at overveje indvirkningen af systemparametre på ydeevnen og pålideligheden af PV-strømomformere, som blev præsenteret i kapitel 3. Ydeevnen af 1500-V PV-systemer med centraliserede strenginverterløsninger blev diskuteret, hvor effekttabene på hver hovedkomponent, dvs. DC-ledninger, invertere, AC-filtre og isolationstransformatorer, er estimeret under med hensyn til forskellige DC- og AC-sider spændingsværdier. Sammenligningsresultaterne indikerer, at strenginverterløsningerne med højere DC- og AC-spændinger overgår løsningerne med lavere DC- og ACspændinger med hensyn til tab og omkostningsreduktion (lavere ledningstab og mindre antal inverterenheder). Derudover er 1500-V PV-batterisystemet blevet undersøgt med en sammenlignende pålidelighedsanalyse af to konfigurationer, dvs. DC-kobling og AC-kobling. Med pålidelighedsanalysen på komponent-, konverter- og systemniveau er den mest skrøbelige del i hvert niveau blevet identificeret, hvilket bidrager til PV-batterisystemernes design-til-pålidelighed.

For det tredje, i betragtning af 1500-V PV-anvendelser, rejses nye pålidelighedsproblemer, som er relateret til den øgede DC-link spændingsstress. Visse metoder til at forbedre pålideligheden af 1500-V PV-invertere blev præsenteret i kapitel 4. For de SiC-baserede 1500-V to-niveau PV-invertere er en variabel hastighed gate-driver blevet foreslået. Den kan justere gate modstandmodstanden i henhold til variationen af DC-linkspændingen i takt med missionsprofilen. Ved at gøre det kan switching overshoot på grund af den spredte induktans i kommutationsloop reduceres, når PV-array-spændingen er høj, hvilket holder strømenhederne inden for deres spændingsværdier. De tilsvarende pålidelighedsvurderingsresultater indikerer, at PV-inverteren med det foreslåede design har en bedre levetidsydelse end den med gatedrivere med fast hastighed, hvor gatemodstanden typisk er designet til de højeste spændingstress. Pålidelighedsforbedringerne kan også opnås gennem kontrol i drift. En overgangstemperaturstyringsstrategi er foreslået i kapitel 4. Hermed kan overgangstemperaturen for effektenhederne i PV-inverteren holdes under en vis grænse under drift, og dermed reducere temperaturvariationerne. Desuden er løsningen til at forbedre den termiske ydeevne af PV-invertere under unormale netforhold også blevet undersøgt. Med forslaget om at opnå en forbedret termisk balance mellem effektenhederne i tre-niveau 1500-V PVinverterne, er en modificeret diskontinuerlig moduleringsstrategi også blevet foreslået i kapitel 4, hvor en avanceret reaktive strøm sunderstøttelse forventes under low-voltage-ride-through tilfælde.

# **Preface**

This Ph.D. thesis is written in connection to the Ph.D. project entitled "Reliability Enhancement of 1500-V DC-link Photovoltaic Power Converters". This Ph.D. project is supported by AAU Energy, Aalborg University, Denmark, and China University of Petroleum (East China). In addition, I would like to convey my acknowledgments to the Center Of Reliable Power Electronics (CORPE) and Otto Mønsteds Fond, who supported me in the conference participation and study abroad during my entire Ph.D. study.

This Ph.D. project was done under the supervision of Prof. Francesco Iannuzzo, Assist. Prof. Ariya Sangwongwanich, and Prof. Yongheng Yang. I would like to express my heartfelt gratitude to them, for their patient guidance and insightful suggestions during the study. It was their support and encouragement that made me feel confident to complete my Ph.D. study.

Then, I would like to sincerely thank Prof. Yunwei(Ryan) Li for providing me an opportunity to visit the University of Alberta, Canada. Although the physical visit was not coming true due to the COVID-19 crisis, the 4 months of online study abroad has also been a great experience for me because of Prof Li's constant encouragement and guidance.

Also, I would like to thank all my colleagues at AAU energy, Aalborg University for their help and support, as well as for the living environment and the endless friendship.

In particular, I take this opportunity to express my thanks to Prof. Rende Zhao from China University of Petroleum (East China). His encouragement and support gave me much strength during the entire Ph.D. study.

Finally, I would like to extend my deep gratefulness to my family, especially my wife Lu, for their unconditional love and care, which are the source of my energy.

Jinkui He Aalborg University, November 24, 2021

# **Contents**

| A  | bstrac | et                                                         | ii |

|----|--------|------------------------------------------------------------|----|

| R  | esum   | é                                                          | iv |

| Pı | reface |                                                            | vi |

|    | Rep    | ort                                                        | 1  |

| 1  | Intr   | oduction                                                   | 2  |

|    | 1.1    | Background                                                 | 2  |

|    | 1.2    | State of the Art                                           | 4  |

|    |        | 1.2.1 Topologies to Accommodate the 1500-V DC-Link Voltage | 4  |

|    |        | 1.2.2 Factors Affecting Reliability                        | 5  |

|    |        | 1.2.3 Design and Control for Improving Reliability         | 6  |

|    | 1.3    | Project Motivation                                         | 7  |

|    | 1.4    | Research Questions and Objectives                          | 8  |

|    |        | 1.4.1 Research Questions                                   | 8  |

|    |        | 1.4.2 Project Objectives                                   | 9  |

|    | 1.5    | Thesis Outline                                             | 9  |

|    | 1.6    | List of Publications                                       | 11 |

| 2  | Reli   | ability Investigation of 1500-V PV Inverter Topologies     | 13 |

|    | 2.1    | System Modeling                                            | 14 |

|    | 2.2    | Thermal Performance Analysis                               | 15 |

|    | 2.3    | Lifetime Evaluation                                        | 17 |

|    |        | 2.3.1 Damage Caused by the Line-Frequency Power Cycling.   | 20 |

|    |        | 2.3.2 Damage Caused by the Low-Frequency Thermal Cycling   | 20 |

|    |        | 2.3.3 Lifetime Consumption Results                         | 21 |

|    | 2.4    | Reliability Assessment                                     | 22 |

|    | 2.5    | Summary                                                    | 25 |

# Contents

| 3  | Imp   | act of System Parameters on Reliability                                                            | 28  |

|----|-------|----------------------------------------------------------------------------------------------------|-----|

|    | 3.1   | Large-Scale Photovoltaic Architecture                                                              | 29  |

|    |       | 3.1.1 System Configuration                                                                         | 29  |

|    |       | 3.1.2 Comparative Study                                                                            | 30  |

|    | 3.2   | Energy Storage Integration                                                                         | 33  |

|    |       | 3.2.1 System Description                                                                           | 35  |

|    |       | 3.2.2 Reliability Comparison                                                                       | 39  |

|    | 3.3   | Summary                                                                                            | 41  |

| 4  | Met   | hods for Improving Reliability                                                                     | 44  |

|    | 4.1   | Variable Gate Resistance Design                                                                    | 44  |

|    |       | 4.1.1 Proposed Approach                                                                            | 45  |

|    |       | 4.1.2 Reliability Assessment                                                                       | 47  |

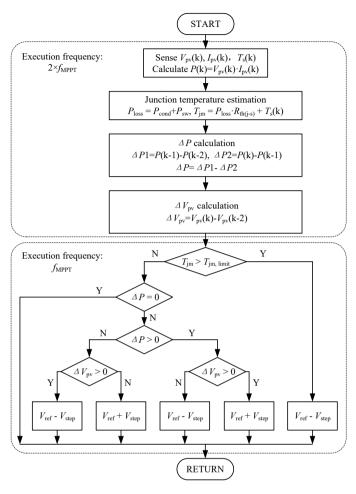

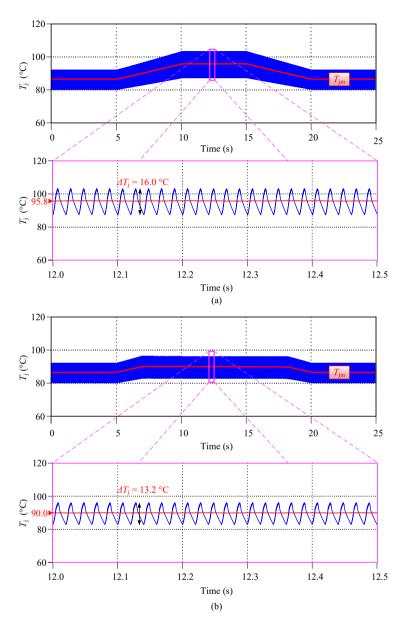

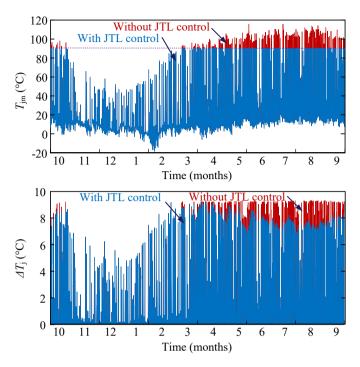

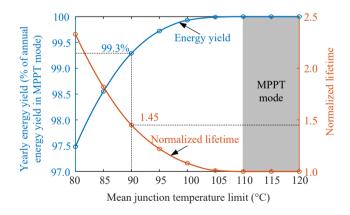

|    | 4.2   | Junction Temperature Limit (JTL) Control                                                           | 48  |

|    |       | 4.2.1 Proposed Approach                                                                            | 48  |

|    |       | 4.2.2 Reliability Assessment                                                                       | 51  |

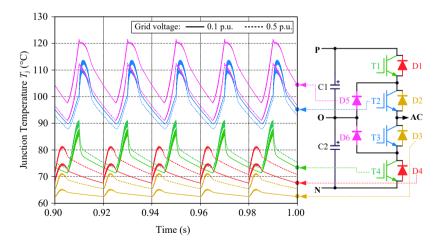

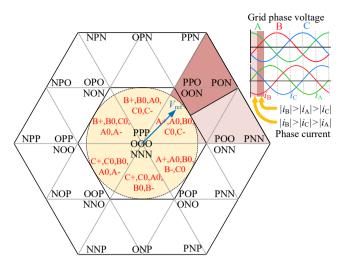

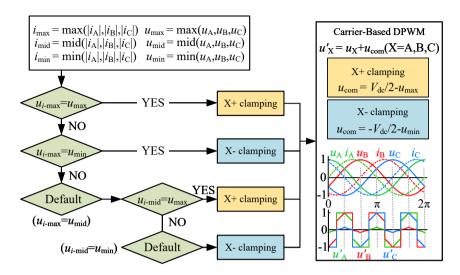

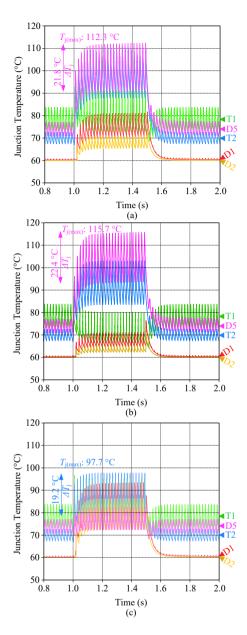

|    | 4.3   | DPWM for Improved Thermal Balance during LVRT                                                      | 54  |

|    |       | 4.3.1 Proposed Approach                                                                            | 55  |

|    |       | 4.3.2 Analysis of Thermal Redistribution                                                           | 56  |

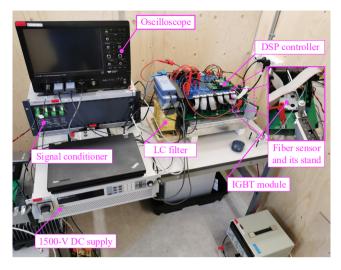

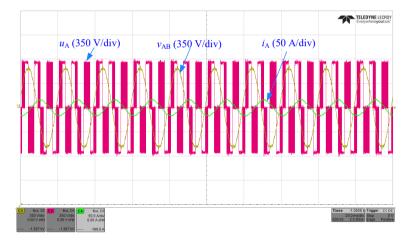

|    |       | 4.3.3 Experimental Validation                                                                      | 57  |

|    | 4.4   | Summary                                                                                            | 58  |

| 5  | Con   | clusions                                                                                           | 63  |

|    | 5.1   | Summary                                                                                            | 63  |

|    | 5.2   | Main Contributions                                                                                 | 64  |

|    | 5.3   | Research Perspectives                                                                              | 65  |

| Bi | bliog | graphy                                                                                             | 67  |

|    | Refe  | erences                                                                                            | 67  |

|    |       |                                                                                                    |     |

|    | Sele  | ected Publications                                                                                 | 73  |

| 1  | Life  | time Evaluation of Three-Level Inverters for 1500-V Photovoltaic                                   |     |

|    | Sys   | tems                                                                                               | 74  |

| 2  |       | rgy Storage for 1500 V Photovoltaic Systems: A Comparative ability Analysis of DC- and AC-Coupling | 90  |

| 3  | Das   | ign for Reliability of SiC-MOSFET-Based 1500-V PV Inverters                                        |     |

| J  |       | •                                                                                                  | 108 |

| 4  | The   | rmal Performance Evaluation of 1500-VDC Photovoltaic Inverters                                     |     |

| 4  |       |                                                                                                    | 119 |

## Contents

5 Lifetime Evaluation of Power Modules for Three-Level 1500-V Photo-

|   | voltaic Inverters                                                                                | 126       |

|---|--------------------------------------------------------------------------------------------------|-----------|

| 6 | Design for Reliability of SiC-MOSFET-Based 1500-V PV Inverters with Variable Gate Resistance     | s<br>134  |

|   |                                                                                                  | 101       |

| 7 | Enhanced Reliability of 1500-V Photovoltaic Inverters with Junction<br>Temperature Limit Control | n<br>142  |

| 8 | Performance Comparison of PV Inverter Systems Considering Sys                                    | <b>3-</b> |

|   | tem Voltage Ratings and Installation Sites                                                       | 151       |

| 9 | Discontinuous Modulation for Improved Thermal Balance of Three                                   |           |

|   | Level 1500-V Photovoltaic Inverters under Low-Voltage Ride-Through                               | h<br>159  |

|   |                                                                                                  | 10)       |

# Report

# Chapter 1

# Introduction

This chapter firstly introduces the background of the Ph.D. project. Then, a short state-of-the-art is presented, followed by the project motivation. Accordingly, the research questions and objectives are summarized. After that, the outline of the Ph.D. thesis is presented to show the overview of this research work. All the research outcomes during this Ph.D. study are provided at the end of this chapter.

# 1.1 Background

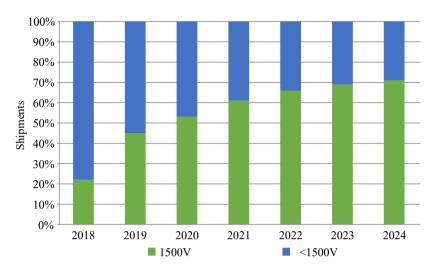

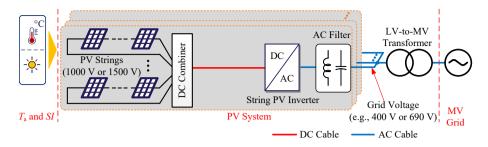

Photovoltaic (PV) systems have become dominant in renewable energy applications. It is expected that more utility-scale PV systems will be installed, and solar energy will account for a major part of the energy production in the future [1–3]. In order to increase the generation capacity of PV systems, the common strategy is to use a large number of combiner boxes to parallel the PV strings, and thus increasing the output current. However, this usually results in a high number of cables, increasing power losses and installation costs, and thereby limiting the competitiveness of large-scale PV power plants. In fact, recent studies have shown that, for increasing PV system capacity, higher PV string /DC-link voltage, i.e., with more PV panels connected in series, could be a cost-effective solution [4–7]. A higher DC-link voltage operation can considerably reduce the requirements of Balance of Systems (BOS), hence the installation cost. By doing so, the ohmic losses in the DC wires can be reduced, which brings the potential to increase the system efficiency. Accordingly, the maximum PV string voltage has been increased from 1000 V to 1500 V in the relevant international standards [8]. Adopting 1500-V PV inverters has quickly become the mainstream in the newly built large-scale PV plants due to its potential in reducing installation costs. As shown in Fig. 1.1, 1500-V PV inverters have already accounted for over 50% of high power PV inverter

#### 1.1. Background

Fig. 1.1: Global trend of three-phase PV inverter shipments by voltage [9].

shipments in 2020, in comparison to just 22% two years earlier [9]. It is also predicted that, by 2024, 54% of new PV inverters will be utility-scale, and 1500-V PV systems are forecast to account for 70% of global three-phase shipments.

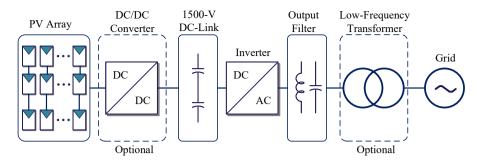

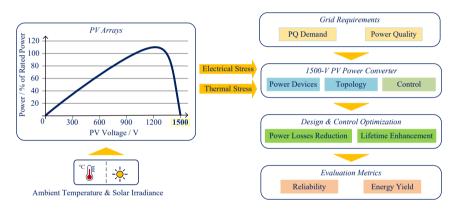

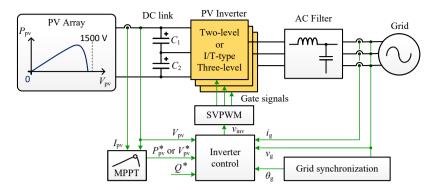

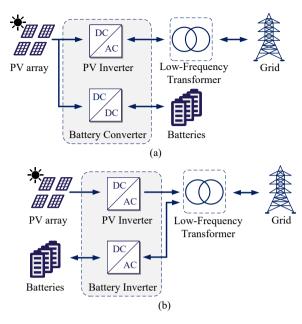

Nevertheless, the increased voltage stress at the DC-link imposes new challenges for the PV power inverter. Fig. 1.2 shows the generic structure of 1500-V grid-connected PV system. The increased PV voltage requires careful consideration when designing and controlling the PV inverters, which play a key role in achieving the power conversion reliably and efficiently. For instance, the use of two-level inverters, which is a popular solution in 600-/1000-V PV systems, may be challenging for 1500-V ones, as it would result in high power losses in the semiconductors and increased filtering efforts in the outputs. As a consequence, shifting to multi-level topologies is the trend. Although a number of commercial products [10, 11], based on two-level or multi-level topologies, are already available on the market, the converter reliability for this particular application is of high interest to be investigated. The main goal of 1500-V PV applications is cost reduction, which should be achieved without introducing adverse impacts on PV power converters.

The reliability improvements can be achieved in the design phase (Design for Reliability), but also in operation, via a smart control. For instance, by applying a proper active thermal control strategy, the thermal loadings of the lifetime-critical components (e.g., DC-link capacitors and power semi-conductors) can be reduced, achieving improved reliability of the overall system [12, 13].

Fig. 1.2: Generic structure of a 1500-V grid-connected PV system.

# 1.2 State of the Art

As mentioned, to ensure a reliable PV system, the reliability performance of the 1500-V PV inverters should be investigated. At the same time, design and control may be explored and revised to achieve the reliability enhancement of the 1500-V PV power converters. The relevant state-of-the-art is reviewed in this section.

# 1.2.1 Topologies to Accommodate the 1500-V DC-Link Voltage

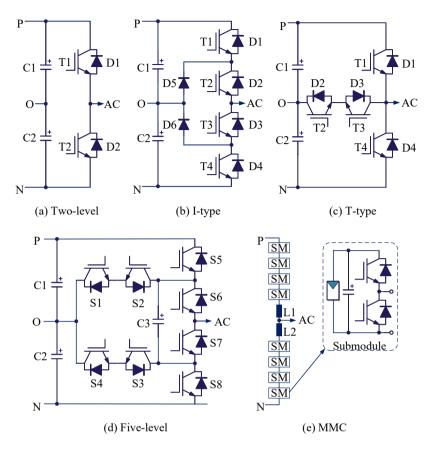

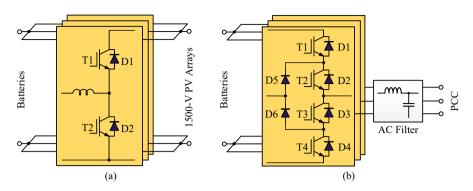

This 1500-V DC voltage requirement certainly affects the choice of the inverter topologies. The conventional two-level topology in Fig. 1.3(a), which is the mainstream for low-voltage applications thanks to its simplicity, has several drawbacks when the voltage stress at the DC-link is high. Power devices with high blocking-voltage capability are required, resulting in higher power losses, lower switching speeds, hence increased filtering efforts. To improve the inverter performance at the higher PV string voltage, i.e., 1500 V, multi-level topologies are preferred alternatives due to their superior features like low output harmonic distortion, decreased power losses, and reduced dv/dt stress [14]. The two standard three-level topologies, i.e. the I-type one in Fig. 1.3(b) and the T-type one in Fig. 1.3(c), are the most popular choices. For the inverter applications with lower DC voltage rating, i.e.,  $\leq 1000$  V, the preferred choice is the T-type topology due to its advantages in efficiency and power quality [15]. However, at 1500 V, the I-type topology seems to be a more promising alternative due to its superiority in blocking-voltage capability [16]. For the I-type topology, All the IGBTs and diodes (referring to Fig. 1.3(b)) only require to withstand 50% DC-link voltage during blocking states. Thanks to this feature, power devices with 900-V to 1200-V voltage ratings would be enough to guarantee safety when applying the I-type topology in 1500-V PV applications. In contrast, the T-type topology would require switches with a higher blocking voltage (≥ 1700 V). For an even higher DC-link voltage

Fig. 1.3: Possible inverter topologies for 1500-V DC-link PV power inverters.

(> 1500 V), five-level topologies (see Fig. 1.3(d)) and modular multi-level converters (e.g., Fig. 1.3(e)) may be suitable with the trade-off in the control complexity and gate driving effort [17, 18]. These multi-level topologies can also be applied in the 1500-V PV systems with increased component count and control complexity. Overall, considering the 1500-V DC-link operation, a comprehensive comparison should be made to benchmark the performance of different PV inverter topologies.

# 1.2.2 Factors Affecting Reliability

considering a long-term operation, the PV power converters are less reliable in comparison to other components in PV systems. In general, the reliability of PV power converters is limited by two main critical components: power devices and DC-link electrolytic capacitors [19].

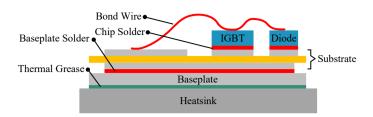

It has been reported that the thermal fatigue of power modules is one of

Fig. 1.4: Principle cross-section of an IGBT module.

the most wearing-out factors, which may lead to failures and destruction [20]. Fig. 1.4 shows the principle cross-section of an IGBT module, where different materials are used, also implying various coefficients of thermal expansion (CTE). Due to the CTE difference between the bond wire (aluminum) and the silicon chip, cracks occur at their interface due to temperature swings during operation. For the same reason, fatigue of the baseplate solder joint could appear.

For PV applications, the power converter's electrical and thermal stresses are strongly affected by the mission profiles of the installation sites, i.e., solar irradiance and the ambient temperature. Based both on real mission profiles and the knowledge of the PV system architecture, a meaningful reliability estimation of PV power converters can be performed. Bearing this in mind, the influence of PV array sizing [21], panel degradation [22], voltage and power control [12, 23], gate driver parameters [24], modulation methods [25], and battery energy storage integration [26], on remaining useful lifetime (RUL) has been analyzed for residential PV systems. These attempts provide guidelines for the design-for-reliability (DfR) of PV power converters with lower PV-array voltage (< 1000 V). However, for 1500-V PV power converters, the same conclusions may not apply as-is, e.g., due to the different topology adopted.

# 1.2.3 Design and Control for Improving Reliability

In general, there are various stressors, i.e., voltage, current, temperature, temperature cycling, humidity, and their combinations, that affect the reliability and failure rate of power semiconductors and DC-link capacitors [27]. Considering the 1500-V DC-link operation, one of the main reliability concerns is related to the increased voltage stress. In the case of adopting the two-level inverter topology for 1500-V PV inverters, the 1700-V power devices may not be specifically applicable [6, 28]. Moreover, the high voltage stress can increase the power semiconductor's failure rate caused by the impact of cosmic radiation [29]. For instance, the Sunny Central 2500-EV inverter of SMA Technology, which is based on the two-level topology, employs a series-connection (2  $\times$  1200 V IGBTs), in order to ensure the voltage stress margin considering the

cosmic rays failure [30]. However, the series-connection method would increase the conduction losses and the gate driver effort. In [6], the performance characterization of 2500-V SiC MOSFETs was reported, and the potential application of this device for 1500-V PV inverters was also evaluated. However, the 2500-V SiC MOSFET has not yet been made commercially available.

Power device's reliability can also be significantly affected by thermal stresses (e.g., thermal cycling) [31]. Here, the operating conditions play an important role in the thermal stresses of these reliability-critical components. On the one hand, the operating condition is affected by the available PV power, which is determined by its mission profile, i.e., the solar irradiance and ambient temperature. On the other hand, control strategies like limiting power injection, reactive power injection, and Maximum Power Point Tracking (MPPT) operation also impose power loss variations and thereby thermal stress on the components [12, 32, 33]. Alternatively, advanced control strategies can be applied to reduce thermal loading. In [12], a hybrid power control strategy was proposed for PV applications, which can improve the PV inverter's thermal performance thus its utilization factor. In [33], a "lifetime-optimized" MPPT scheme was proposed to restrict the maximum junction temperature and reduce the thermal stress variation caused by fast-varying solar irradiance. In order to control the thermal stress of power devices, in [32], a thermal optimized control strategy for PV inverters was proposed considering the low-voltage-ride-through (LVRT) operation, where the thermal performance enhancement was achieved by reassigning the active and reactive power of the PV inverters. However, how to design control strategies for reducing thermal stresses on 1500-V PV inverters has not been extensively discussed yet.

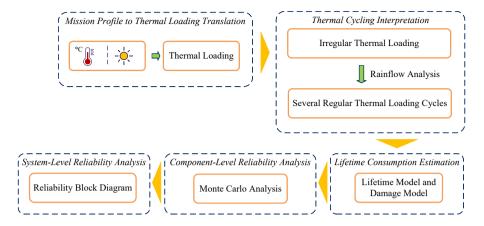

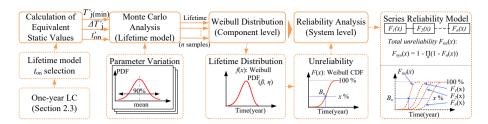

In order to achieve the design and control for reliability, a reliability evaluation should be performed [34]. It mainly involves five steps, as shown in Fig. 1.5): 1) mission profile to thermal loading translation [35], 2) thermal cycling interpretation [36], 3) lifetime consumption estimation, 4) component-level reliability analysis, and 5) system-level reliability analysis [37]. This reliability evaluation approach will be used to investigate the reliability performance of the 1500-V PV power converters under different operating conditions.

# 1.3 Project Motivation

Based on the state-of-the-art, further attempts should be made to bridge the following research gaps. Firstly, it is necessary to make a comprehensive comparison to benchmark the performance of different inverter topologies for 1500-V applications. Secondly, it is important to consider the impact of system parameters on the reliability of 1500-V PV power converters. Thirdly, it is attractive to explore design and control solutions to guarantee the reliable operation of 1500-V PV power converters.

#### 1.4. Research Questions and Objectives

Fig. 1.5: Flowchart of the mission profile-based reliability assessment of PV inverters.

Fig. 1.6: Objective of this Ph.D. work: reliability enhancement of 1500-V PV power converters.

The above research gaps initiated this Ph.D. project. In summary, the main motivation is to investigate how the increased DC-link voltage affects the reliability performance of PV power inverters, hence developing viable design and control solutions to ensure a reliable energy conversion while fulfilling the grid requirements, as summarized in Fig. 1.6.

# 1.4 Research Questions and Objectives

# 1.4.1 Research Questions

The objective of this Ph.D. project is twofold: to reduce power losses hence reducing the temperature swing and to enhance the reliability of 1500-V DC-

link PV power converters. As a result, the fundamental research hypothesis is formulated as:

• How to improve the reliability of 1500-V DC-link PV power converters through design and control strategies?

Accordingly, some subsequent research questions can be formulated as:

- What is the most suitable inverter topology to be applied in the 1500-V technology considering reliability?

- How do the system parameters affect the reliability of the 1500-V PV power converters?

- How to improve the PV inverter's control to enhance its reliability?

# 1.4.2 Project Objectives

Bearing the above in mind, the objective of this Ph.D. project is to investigate the performance of inverters potentially used in 1500-V DC-link PV systems, with a special focus on design and control for enhancing reliability. More specifically, this project is dedicated to:

- Compare the performances of the state-of-the-art PV inverter topologies considering the 1500-V DC-link operation in terms of reliability.

- Investigate the impact of system parameters on the inverter reliability, and provide principles for achieving sufficient reliability performance.

- Propose viable design and control solutions to achieve high reliable 1500-V DC-link PV converters.

# 1.5 Thesis Outline

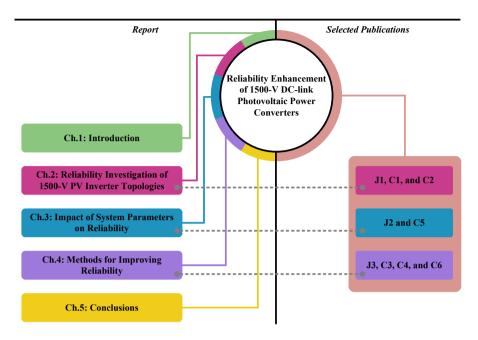

Fig. 1.7 shows the structure of this Ph.D. thesis, which includes two parts: the report and the selected publications. The report summarizes the research outcomes of this Ph.D. project and contains five chapters. Fig. 1.7 also illustrates the relationship between the selected publications and the main body of the report, i.e., *Chapters 2 to 4*. The list of publications is presented at the end of this chapter. A brief introduction of each chapter is given here below:

• **Chapter 1** has given the introduction of the Ph.D. project by presenting the background, state-of-the-art, motivation, research questions, and project objectives.

**Fig. 1.7:** Structure of this Ph.D. thesis: relationship between the report and the selected publications.

- Based on [J1], [C1], and [C2], Chapter 2 presents a comparative reliability

assessment of two-level and three-level 1500-V PV inverters on the base

of the thermal stress analysis of these inverter topologies considering the

impact of voltage stresses, switching frequencies, and mission profiles.

- Based on [J2] and [C5], Chapter 3 investigates the impact of system parameters on the PV inverter reliability, where two aspects are considered, one is the system voltage rating, another is the integration of battery energy storage systems.

- Based on [J3], [C3], [C4], and [C6], Chapter 4 presents design and control

solutions to enhance the reliability of 1500-V PV inverters during operation. Possible solutions are discussed, i.e., variable gate resistance design

for SiC-based two-level inverter, junction temperature limit control, and

discontinuous modulation strategy during low-voltage ride through.

- Finally, **Chapter 5** gives the concluding remarks and the main contributions of this Ph.D. project. The future research perspectives are also outlined in this chapter.

# 1.6 List of Publications

The research outcomes from the Ph.D. project have been disseminated in the form of publications, i.e., journal papers and conference publications, as listed below. Selected papers are summarized and used in the Ph.D. dissertation as previously listed.

#### Journal Papers

- **J1. J. He**, A. Sangwongwanich, Y. Yang, and F. Iannuzzo, "Lifetime Evaluation of Three-Level Inverters for 1500-V Photovoltaic Systems" *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 9, no. 4, pp. 4285-4298, Aug. 2021.

- **J2. J. He**, Y. Yang, and D. Vinnikov, "Energy Storage for 1500 V Photovoltaic Systems: A Comparative Reliability Analysis of DC- and AC-Coupling" *Energies*, vol. 13, no. 13, pp. 3355, Jul. 2020.

- **J3. J. He**, A. Sangwongwanich, Y. Yang, K. Zhang, and F. Iannuzzo, "Design for Reliability of SiC-MOSFET-Based 1500-V PV Inverters with Variable Gate Resistance" *IEEE Trans. Ind. Appl.*, awaiting submission, Nov. 2021.

#### Conference Papers

- **C1. J. He**, A. Sangwongwanich, Y. Yang, and F. Iannuzzo, "Thermal Performance Evaluation of 1500-VDC Photovoltaic Inverters Under Constant Power Generation Operation," in *Proc. IEEE CPERE*, pp. 579-583, Oct. 2018.

- **C2. J. He**, A. Sangwongwanich, Y. Yang, and F. Iannuzzo, "Lifetime Evaluation of Power Modules for Three-Level 1500-V Photovoltaic Inverters," in *Proc. IEEE APEC*, pp. 430-435, Mar. 2020.

- **C3. J. He**, A. Sangwongwanich, Y. Yang, and F. Iannuzzo, "Design for Reliability of SiC-MOSFET-Based 1500-V PV Inverters with Variable Gate Resistance," in *Proc. IEEE ECCE*, pp. 1850-1855, Oct. 2020.

- **C4. J. He**, A. Sangwongwanich, Y. Yang, and F. Iannuzzo, "Enhanced Reliability of 1500-V Photovoltaic Inverters with Junction Temperature Limit Control," in *Proc. IEEE ECCE-Asia*, 2020, p. 1850-1855, May 2021.

- **C5. J. He**, A. Sangwongwanich, Y. Yang, and F. Iannuzzo, "Performance Comparison of PV Inverter Systems Considering System Voltage Ratings and Installation Sites," in *Proc. IEEE APEC*, pp. 2620-2625, Jun. 2021.

- **C6. J. He**, A. Sangwongwanich, Y. Yang, Z. Quan, Y. Li, and F. Iannuzzo, "Discontinuous Modulation for Improved Thermal Balance of Three-Level 1500-V Photovoltaic Inverters under Low-Voltage Ride-Through," in *Proc. IEEE ECCE*, pp. 103-108, Oct. 2021.

The publications done during the study but not included in the Ph.D. thesis are listed below:

A. Sangwongwanich, J. He, and Y. Pan, "Advanced Power Control of Photovoltaic Systems," Control of Power Electronic Converters and Systems, 1st ed., Frede Blaabjerg, Ed.: Academic Press, 2021, ch. 15.

## 1.6. List of Publications

- K. A. Khan Niazi, Y. Yang, **J. He**, A. Z. Khan, and D. Sera, "Switched-Capacitor-Inductor-based Differential Power Converter for Solar PV Modules," in *Proc. IEEE ECCE*, pp. 4613-4618, Sep. 2019.

- G. Li, R. Zhao, J. He, H. Xu, and Q. Yan, "An Improved Boost Dual-Loop Control for Improving the MPPT Efficiency in Photovoltaic Systems," in *Proc. IET RPG*, pp. 1-8, Sep. 2019.

# Chapter 2

# Reliability Investigation of 1500-V PV Inverter Topologies

This chapter presents a comparative reliability investigation of the two-level and three-level 1500-V PV inverters. The comparison presented in this chapter includes the three topologies shown in Fig. 2.1, namely, the two-level, the I-type three-level and the T-type three-level topologies, which are the most common inverter topologies for 1500-V PV systems in the industry. Firstly, I provide the system description, the selected IGBT power modules, and thermal modeling principle, followed by a thermal performance comparison of these inverter topologies considering constant power generation operations, reflecting their thermal stress under different DC-link voltages. Then, the lifetime of the most stressed power semiconductors within the three-level topologies is evaluated. Based on that, a converter-level reliability evaluation is presented. Finally, a summary is provided at the end of this chapter.

**Fig. 2.1:** Considered topologies for 1500-V DC-link PV inverters: (a) two-level, (b) I-type three-level, and (c) T-type three-level. Source: **[C1]**.

#### 2.1. System Modeling

Fig. 2.2: Circuit diagram of the PV system and its maximum power point tracking (MPPT) control structure. Source: [J1].

Table 2.1: Specifications of the 1500-V PV System. Source: [J1].

| DV invovtov anacifications                      |                                                  |  |  |

|-------------------------------------------------|--------------------------------------------------|--|--|

| PV inverter specifications                      |                                                  |  |  |

| Nominal power $P_{nom}$                         | 160 kW                                           |  |  |

| Grid voltage $V_{\rm LL}^1$ (RMS <sup>2</sup> ) | 600 V                                            |  |  |

| Grid frequency $f_g$                            | 50 Hz                                            |  |  |

| Power factor $\cos(\varphi)$                    | 1.0                                              |  |  |

| Switching frequency $f_{sw}$                    | 2-6  kHz                                         |  |  |

| PV panel configuration                          |                                                  |  |  |

| PV panel type                                   | JKM360M-72-V [38]                                |  |  |

| Number of PV panels                             | 27 in series (PV string), 16 strings in parallel |  |  |

<sup>&</sup>lt;sup>1</sup> V<sub>LL</sub>: line-to-line voltage

# 2.1 System Modeling

A 160-kW single-stage PV system is considered in this project. The circuit diagram of the PV system and its general control structure are shown in Fig. 2.2, where either two-level or three-level inverters can be employed to transfer the energy from the 1500-V PV array to the AC grid. The specifications of the PV system and the selected IGBT modules are given in Tables 2.1 and 2.2, respectively. The nominal power of the PV system is 160 kW, where the switching frequency is chosen to be between 2-6 kHz to analyze its impact on inverter reliability. As for the PV array, the 1500-V PV panels from Jinko are adopted to match the ratings of the PV system.

Power losses on the power devices, i.e., IGBTs or diodes, cause the self-heating effect, which lead to large temperature gradients and thus affect the reliability. The switching losses and conduction losses of power devices can be modeled based on the switching energy  $E_{\rm sw}$  during switching transition and the forward voltage drop  $v_{\rm CE}$

<sup>&</sup>lt;sup>2</sup> RMS: Root-Mean-Square.

| Parameter           | 453GB17E4p  | 305MLI12E4 | 305TMLI17E4 |

|---------------------|-------------|------------|-------------|

| Topology            | Half-bridge | I-type     | T-type      |

| Nominal voltage (V) | 1700        | 1200       | 1700        |

| Nominal current (A) | 450         | 300        | 300         |

| Junction temp. (°C) | -40 to 150  | -40 to 150 | -40 to 150  |

Table 2.2: Adopted IGBT Modules for Building up the 1500-V PV Inverters. Source: [C1].

during conduction, respectively. Besides, the impact of the temperature variation on the power loss cannot be ignored, which can be considered in the loss model, e.g., in form of look-up tables.

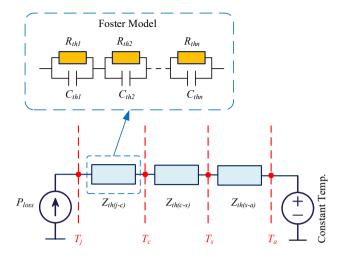

With the obtained power losses, the device junction temperature can be modeled based on their thermal models [35]. The typical diagram of the thermal model is illustrated in Fig. 2.3, where the junction-to-case thermal impedance, i.e.,  $Z_{\text{th(j-c)}}$ , is modeled by means of a thermal RC network, also referred to as Foster model. Accordingly, the junction temperature can be expressed as [35]

$$T_{i}(t) = P_{\text{tot}(T/D)}(t) \cdot Z_{\text{th}(i-c)}(t) + T_{c}(t)$$

(2.1)

$$T_{c}(t) = P_{\text{tot(T/D)}}(t) \cdot [Z_{\text{th(c-s)}}(t) + Z_{\text{th(s-a)}}(t)] + T_{a}(t)$$

(2.2)

where  $T_{\rm c}$  and  $T_{\rm a}$  are the case temperature (for modules with base plate) and ambient temperature, respectively,  $Z_{\rm th(c-s)}$  and  $Z_{\rm th(s-a)}$  represent the thermal impedance of the case-to-heatsink and the heatsink-to-ambient, respectively,  $P_{\rm tot(T/D)}$  is the total power losses of the power device (Transistor or Diode). The model parameters (i.e.,  $R_{\rm th}$  and  $C_{\rm th}$  in Fig. 2.3) can be acquired by using a three-/four-layer RC network to fit the transient thermal impedance curves in the module datasheet. These RC parameters determine the junction temperature dynamic.

# 2.2 Thermal Performance Analysis

The thermal performance of the aforementioned 1500-V PV inverters is compared under steady-state conditions, where they are assumed to operate under constant power generation (CPG) mode with the ambient temperature and the solar irradiance being constant, 25 °C and 1000 W/m², respectively.

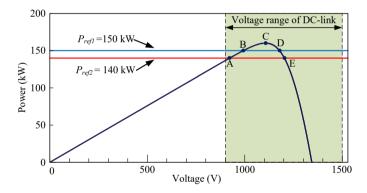

It is known than the PV inverters can operate on the left- or right-hand maximum power point (MPP) side during CPG operation. Fig. 2.4 shows the power-voltage (P-V) curve of the 1500-V PV array and two possible power references ( $P_{\rm ref1}$  and  $P_{\rm ref2}$ ) for CPG operations. With the system modeling in the previous section, the thermal performance of the 1500-V PV inverters based on different topologyies can be compared at these operating points. The comparison results have been discussed in [C1], and will be summarized in the following.

#### 2.2. Thermal Performance Analysis

Fig. 2.3: Structure of the thermal model. Source: [C1].

Fig. 2.4: P-V curve of the 1500-V PV array and possible power control reference for constant power generation. Source: [C1].

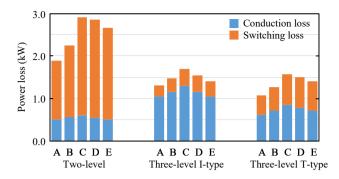

Fig. 2.5 shows the semiconductor power losses under different operating points. As can be seen in it, the power losses of the two-level inverter are dramatically higher than that of the three-level I-type/T-type inverter. Also, by comparing between the three-level inverters, it can be observed from Fig. 2.5 that the power losses of the I-type inverter are slightly higher than that of the T-type one for the considered switching frequency, i.e., 5 kHz. Overall, the higher the operating point voltage, the higher the inverter power losses, especially for the two-level and T-type three-level cases. On the contrary, the PV inverters have lower power losses when they operate at the left-side of the MPP, e.g., points A and B, and the power loss reduction is mainly contributed by the decrease in switching losses. Hence, it can be expected that, when the two-level or the T-type inverter operates at the left-hand side of the MPP, a higher efficiency can be achieved. As for the I-type inverter, it can be observed in Fig. 2.5 that its

**Fig. 2.5:** PV inverter power losses under different operating points (referring to Fig. 2.4). Source: **[C1]**.

switching losses are relatively small compared to the conduction losses under the 5-kHz switching frequency, and thus its total power losses under the left-hand MPP side are similar to that under the MPP right-hand side.

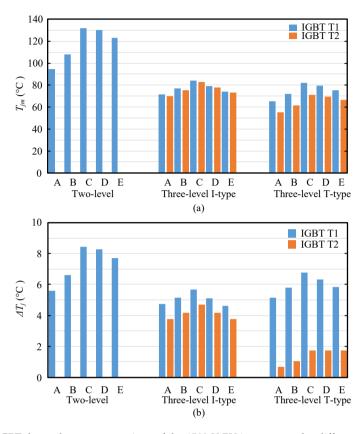

The thermal stresses of these two-level and three-level inverters are compared in Fig. 2.6 (a and b) in terms of the mean junction temperature  $T_{\rm jm}$  and the corresponding cycle amplitude  $\Delta T_{\rm j}$ . It can be observed from Fig. 2.6 that, overall, the relationship between the thermal stress and operating point is consistent with the power loss analysis, and the thermal stress of the two-level inverter is much higher than that of the three-level ones. In this case, much more cooling efforts are expected for the two-level inverter, otherwise, its reliability is challenged.

On the other hand, when the two-level and T-type inverters operate under the right-hand MPP side, their IGBTs have higher  $T_{\rm jm}$  and higher  $\Delta T_{\rm j}$  due to the high power losses in such a case. For the I-type inverter, similar to the power loss distribution, there is not much difference for the thermal stress under each side. It should be pointed out that, although the mean junction temperature of IGBT T1 (most stressed) in the I-type inverter is slightly higher in comparison to that in the T-type one, the cycle amplitude of the latter is higher. Both of these two stress indicators, i.e.,  $T_{\rm jm}$  and  $\Delta T_{\rm j}$ , are critical parameters in the empirical lifetime model [39]. The lifetime performance of the three-level inverters has been discussed in [C2, J1] and will be summarized in the following sections.

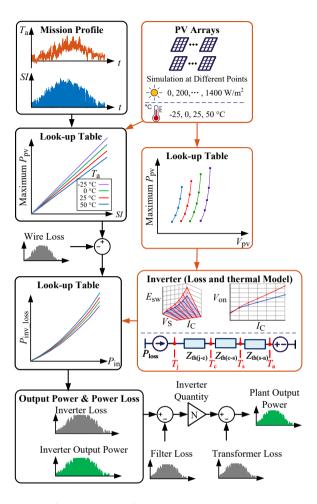

# 2.3 Lifetime Evaluation

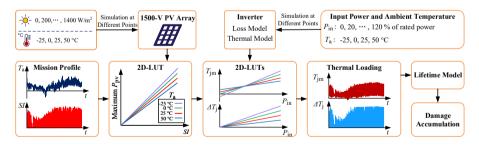

As discussed in *Chapter 1*, the PV inverter lifetime is influenced by their mission profiles. To evaluate the inverter lifetime, firstly, the mission profile should be translated into the device thermal loading. Then, a proper lifetime model can be applied to estimate the device lifetime based on the obtained thermal loading. The overall process is summarized in Fig. 2.7, where several look-up tables (LUTs) are used to deal with the long-term mission profiles [35].

First, as indicated in Fig. 2.7, the available power of the 1500-V PV array is

**Fig. 2.6:** IGBT thermal stress comparison of the 1500-V PV inverters under different operating points (referring to Fig. 2.4). Source: **[C1]**.

Fig. 2.7: Block diagram of the mission-profile based lifetime evaluation for the power devices of the 1500-V PV inverters. Source: [C2, J1].

determined under different operating points to obtain the LUT for translating the mission profile to the inverter's operating conditions, i.e., input power and ambient temperature. In parallel, the PV inverter is also simulated under a certain set of

**Fig. 2.8:** One-year mission profiles, i.e., solar irradiance SI and ambient temperature  $T_a$ , which are recorded with a sampling rate of 1 min/sample in: (a) Aalborg and (b) Sacramento. Source: [c2, J1].

operating points. Then, the LUTs for translating the operating conditions to the thermal loadings of the power devices can be built up. With these LUTs, the thermal loading of the power devices can be acquired when the long-term mission profiles are provided as the inputs, following the process in Fig. 2.7. Finally, an appropriate empirical lifetime model and damage model can be applied to estimate the device lifetime consumption under the mission profiles. With this procedure, a benchmarking of the three-level inverter topologies could be done in terms of component lifetime.

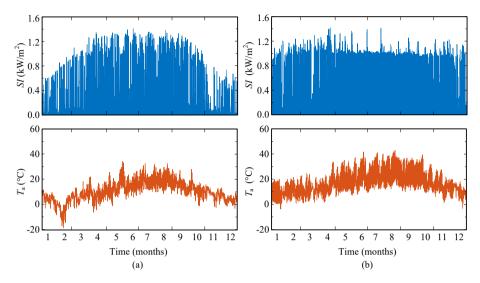

As for the mission profiles, the yearly solar irradiance and ambient temperature data of Aalborg (Denmark) and Sacramento (California) are adopted in this project, which are recorded with 1 minute/data sampling rate, as shown in Fig. 2.8. In Aalborg, the annual average temperature is 9.88 °C. Also, it can be observed from Fig. 2.8(a) that the temperature and solar irradiance in Aalborg fluctuate over a wide range. In contrast, the annual average temperature in Sacramento is 16.56 °C, and the solar irradiance and temperature are more stable as shown in Fig. 2.8(b), which are respectively higher than that in Aalborg.

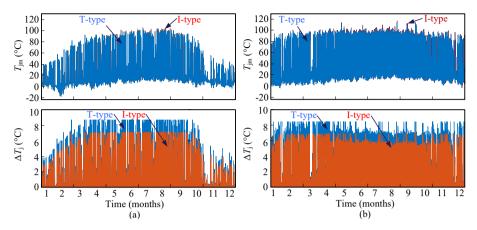

According to the translation process in Fig. 2.7 and take the above mission profiles as inputs, the thermal loadings of IGBT T1 (referring to Fig. 2.1) of the three-level topologies have been obtained, which are shown in Fig. 2.9. It can be observed from Fig. 2.9 that the inverter IGBT installed in Aalborg experience lower thermal stresses in comparison to that in Sacramento due to the lower average irradiance and temperature in Aalborg. Moreover, it can be observed from Fig. 2.9 that, the cycle amplitude  $\Delta T_j$  of the IGBT in the I-type inverter is lower than that in the T-type inverter. According to the lifetime model [39], the lifetime consumption of the IGBT for the I-type topology would be lower than that of the T-type one. The impact of thermal loadings on the

**Fig. 2.9:** One-year mean junction temperature  $T_{jm}$  and cycle amplitude  $\Delta T_j$  profiles for the IGBT T1 in the three-level inverters with 6-kHz switching frequency: (a) Aalborg and (b) Sacramento. Source: [C2, J1].

inverter reliability will be discussed in the following section.

# 2.3.1 Damage Caused by the Line-Frequency Power Cycling

The damage due to the power cycling with line frequency, i.e., 50 Hz, can be calculated directly, e.g., by Miner's rule [40]. The obtained thermal loadings have the same sampling rate as the mission profiles, i.e., 1 minute/sample. Thus, the damage during every minute can be calculated with the corresponding thermal stress data, i.e., mean junction temperature and cycle amplitude. Then, according to Miner's rule, the total damage due to a minute line-frequency power cycling can be calculated as

$$LC = \sum_{i} \frac{n_i}{(N_f)_i} = \sum_{i} \frac{3000}{(N_f)_i}$$

(2.3)

where  $n_i$  is a constant value and equals to 3000, i.e., the number of 50-Hz power cycles in one minute,  $(N_f)_i$  can be calculated according to the lifetime model and the thermal loading data. Table 2.3 summarizes the obtained damage results for both line-frequency and low-frequency damage type.

# 2.3.2 Damage Caused by the Low-Frequency Thermal Cycling

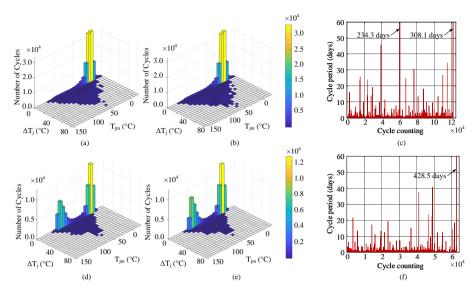

Typically, a cycle counting algorithm is required to take into account the irregular temperature loading profile. In this project, a rainflow counting analysis is used to categorize the irregular thermal cycles into a certain set of regular ones [36]. By doing so, the dynamics under the mission profiles, i.e., the number of cycles  $n_i$  for a certain set of thermal stress conditions (i.e., cycle amplitude  $\Delta T_j$ , mean junction temperature  $T_{\rm jm}$ , and cycle period) can be extracted. The rainflow counting results are shown in Fig. 2.10. A total of 121,699 and 62,890 low-frequency thermal cycles have been extracted

**Fig. 2.10:** Rainflow counting results of the one-year junction temperature profile of the IGBT T1 in the three-level inverters with a switching frequency of 6 kHz: (a) thermal cycles in Aalborg (I-type), (b) thermal cycles in Aalborg (T-type), (c) cycle period in Aalborg, (d) thermal cycles in Sacramento (I-type), (d) thermal cycles in Sacramento (T-type), (f) cycle period in Sacramento. Source: **[C1, J1]**.

for the IGBT thermal loading under the Aalborg and Sacramento mission profiles, respectively, and their periods vary from minutes to tens of days. Similarly, the same damage model as for the line-frequency power cycling can be applied on the rainflow counting results to obtain the corresponding damage results, which are summarized in Table 2.3 as well.

# 2.3.3 Lifetime Consumption Results

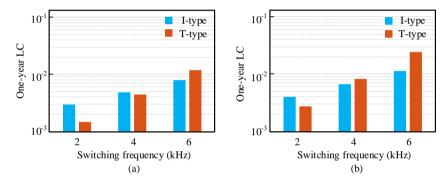

The one-year damage results in Table 2.3 are further summarized in Fig. 2.11. As can be seen in it, with the Aalborg mission profile, the IGBT for the I-type topology has lower lifetime consumption when the switching frequency is lower than 4 kHz compared to that in the T-type topology. In the case of a 2-kHz switching frequency under the Sacramento mission profile, the IGBT of the T-type inverter also has a lower lifetime consumption. However, when the switching frequency is higher than 4 kHz, the I-type topology is preferred for the Sacramento mission profile due to its lower lifetime consumption.

The lifetime consumption results can be summarized as: 1) the operation conditions, i.e., mission profile and switching frequency, have a considerable influence on the device reliability of the three-level 1500-V PV inverters, and 2) caused by the increased DC-link voltage stress, compared to PV systems with lower DC-link voltage, e.g., < 1000 V, the lifetime performance of the T-type inverter may be worse than that of the I-type one even for low switching frequencies, e.g., 4 kHz to 6 kHz. A converter-level

#### 2.4. Reliability Assessment

| Mission profile | Power module | Damage type | Switching frequency |        |        |

|-----------------|--------------|-------------|---------------------|--------|--------|

| Mission profile |              |             | 2 kHz               | 4 kHz  | 6 kHz  |

|                 | I-type       | Line-freq.  | 0.0002              | 0.0005 | 0.0009 |

| Aalborg         |              | Low-freq.   | 0.0027              | 0.0044 | 0.0070 |

| Aaiborg         | T-type       | Line-freq.  | 0.0003              | 0.0009 | 0.0032 |

|                 |              | Low-freq.   | 0.0012              | 0.0035 | 0.0087 |

|                 | I-type       | Line-freq.  | 0.0014              | 0.0025 | 0.0051 |

| Sacramento      |              | Low-freq.   | 0.0026              | 0.0041 | 0.0063 |

| Sacramento      | T-type       | Line-freq.  | 0.0014              | 0.0050 | 0.0164 |

|                 |              | Low-freq.   | 0.0013              | 0.0033 | 0.0078 |

Table 2.3: One-Year Lifetime Consumption. Source: [C1, J1].

Fig. 2.11: One-year lifetime consumption of the IGBT T1 under various switching frequencies and two installation sites: (a) Aalborg and (b) Sacramento. Source: [C1, J1].

reliability assessment will be given in the next section.

# 2.4 Reliability Assessment

With the above lifetime evaluation, the component damage under the mission profiles can be calculated and obtained for a given fixed lifetime value. However, it is known that the component lifetime varies within a certain range due to the variation at manufacturing time. Consequently, for lifetime prediction, the results are usually expressed in the form of statistical values instead of fixed ones. In this section, the converter-level reliability of the three-level inverter candidates is discussed statistically, which is done by applying Monte Carlo analysis [37, 41, 42]. Fig. 2.12 presents the block diagram of this reliability assessment. As can be seen in it, with the lifetime consumption results in the previous section, the equivalent static thermal stress parameters (i.e.,  $T'_{j(\min)}$ ,  $\Delta T'_{j}$ , and  $t'_{on}$ ) are obtained, which can result in the

#### 2.4. Reliability Assessment

Fig. 2.12: Block diagram of the reliability assessment based on Monte Carlo analysis. Source: [J1].

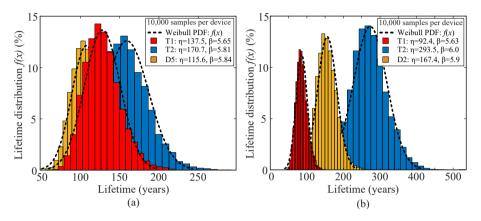

Fig. 2.13: Lifetime distribution of the most stressed power devices in the 1500-V PV inverters installed in Aalborg: (a) three-level I-type inverter and (b) three-level T-type inverter. Source: [J1].

same one-year lifetime consumption as the dynamic parameters (i.e.,  $T_{\rm j(min)}$ ,  $\Delta T_{\rm j}$ , and  $t_{\rm on}$ ) of the thermal loading profiles in the previous section. Then, the parameter variations have been considered to introduce uncertainties, where the equivalent static thermal stress parameters and all the parameters in the adopted lifetime model [39] are assumed to have a 5% variation (99% confidence level). After that, the corresponding lifetime distributions can be obtained. More importantly, a comparative evaluation of the converter-level reliability can be done according to the reliability block diagram (RBD) of the three-level topologies [34, 41, 43].

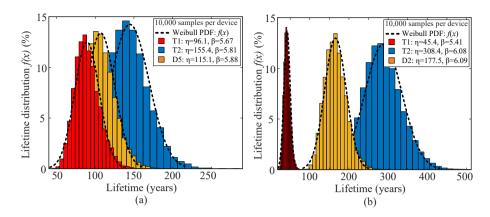

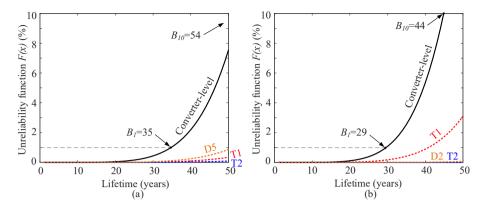

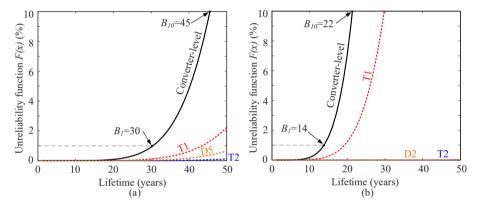

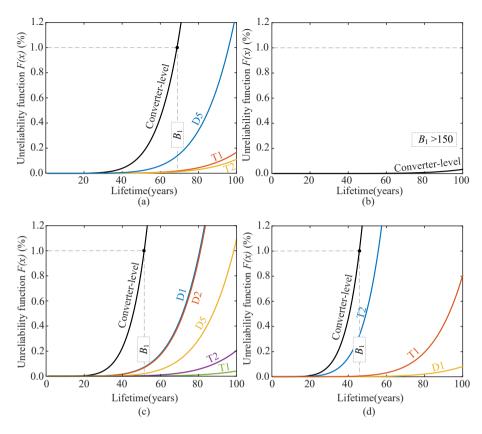

Considering 10,000 samples for each case, the lifetime distributions of the most stressed power devices of the three-level inverters have been obtained by Monte Carlo simulations, as shown in Figs. 2.13 and 2.14. As it can be seen in Figs. 2.13 and 2.14, overall, the lifetime distributions for the I-type inverters are less spread compared with that for the T-type inverters, where the lifetime distribution of IGBT T1 is far away from those of T2 and diode D2. This is more critical for a more severe mission profile, e.g., Sacramento, as shown in Fig. 2.14(b). This means that the device lifetime performance of the I-type inverter is more balanced in comparison to that of the T-type inverter. It can be expected that, when seeing the reliability performance from converter-level, the I-type inverter would be better in comparison to the T-type one in both cases (i.e., Aalborg and Sacramento), due to the high stressed 1700-V IGBTs in the T-type inverter.

#### 2.4. Reliability Assessment

**Fig. 2.14:** Lifetime distribution of the most stressed power devices in the 1500-V PV inverters installed in Sacramento: (a) three-level I-type inverter and (b) three-level T-type inverter. Source: [J1].

With the obtained lifetime distributions, the reliability of the three-level inverter candidates can be further evaluated with the cumulative density function (CDF), which can present the failure proportion as a function of operating time. It is also referred to as the Weibull unreliability function and can be given by

$$F(x) = \int_0^x f(x)dx, \quad f(x) = \frac{\beta}{\eta} \left(\frac{x}{\eta}\right)^{\beta - 1} e^{-\left(\frac{x}{\eta}\right)^{\beta}}$$

(2.4)

where x is the operating time, f(x) represents the probability density function (PDF) of the lifetime distribution,  $\eta$  and  $\beta$  denote the scale and shape parameters, respectively. Then, the lifetime prediction can be given in the form of  $B_x$  lifetime, which equals to the operating time when x% of the population reaches the end of life.

With the component-level unreliability functions, the unreliability function of the inverters (converter-level) can be obtained according to the reliability block diagram (RBD) of the inverter topologies, which describes the relationship between the component reliability and the reliability of the whole inverter [43]. For the three-level candidates, their fault-tolerant operation is not considered in this case study, since if any power device (IGBT or diode) fails, the inverter would fail or could not be operated up to the designed ratings (e.g., reduced output voltage/power [44, 45]). Thus, a series connection of the component-level RBDs is adopted to obtain the converter-level results, as shown in Fig. 2.15. Accordingly, the system unreliability function  $F_{\rm sys}(x)$  can be expressed as

$$F_{\text{sys}}(x) = 1 - \prod_{i=1}^{n} (1 - F_i(x))$$

(2.5)

with  $F_i(x)$  being the unreliability function of the  $i^{th}$  power device.

Figs. 2.16 and 2.17 present the unreliability functions of the considered three-level inverters, where dashed and solid lines indicate the component-level and the converter-level, respectively. As it can be observed from Figs. 2.16 and 2.17, the

**Fig. 2.15:** Reliability block diagram of the three-level inverters, where a series connection is considered both for the phase leg and the whole three-phase inverter. Source: [J1].

inverter candidates have considerably various  $B_x$  lifetime for the different mission profiles, reflecting their impact on inverter reliability. Under both cases, the three-level I-type inverter outperforms the T-type one in terms of reliability. Notably, for the Sacramento mission profile, it is not recommended to use the T-type inverter for the current heatsink/cooling condition due to its distinctly low  $B_x$  lifetime.

Table 2.4 summarizes some  $B_x$  lifetimes of the inverter candidates with switching frequencies from 2 kHz to 6 kHz. The results are consistent with the component lifetime evaluation in the previous section. On the one hand, for very low switching frequencies, e.g., 2 kHz, either inverter candidate can present a high  $B_x$  lifetime. On the other hand, for higher switching frequency, e.g., 6 kHz, the promising candidate is the I-type one, which can achieve a higher  $B_x$  lifetime. This is especially true for the Sacramento mission profile, where the  $B_x$  lifetime of the I-type inverter is more than twice as much as the T-type one. Besides, when it comes to an intermediate switching frequency, e.g., 4 kHz, the topology selection could depend on the mission profiles of the installation sites. In this work, the I-type topology is preferred for the Sacramento site, while for Aalborg, the T-type one is superior for this switching frequency. It is worth mentioning that it is still an open challenge when trying to verify the actual lifetime [31]. However, the reliability assessment can still be used for a qualitative comparison among the inverter candidates in the 1500-V range.

# 2.5 Summary

In this chapter, the reliability of the 1500-V PV inverters with standard two-level and three-level topologies has been investigated. Their power losses and thermal stresses were compared under different operating points on the P-V curve of the 1500-V PV arrays. The comparison results indicated that, compared with the two-level topology, the three-level ones are more suitable alternatives for 1500-V PV systems due to their higher efficiency and lower thermal stresses. Furthermore, the reliability

Fig. 2.16: Component-level and converter-level unreliability functions of the 1500-V PV inverters installed in Aalborg: (a) three-level I-type inverter and (b) three-level T-type inverter. Source: [J1].

**Fig. 2.17:** Component-level and converter-level unreliability functions of the 1500-V PV inverters installed in Sacramento: (a) three-level I-type inverter and (b) three-level T-type inverter. Source: **[J1**].

performance of the three-level inverters has been evaluated considering the impact of mission profiles and switching frequencies. The component- and converter-level reliability analyses reveal that these factors have a considerable influence on the inverter reliability, hence affecting the selection of topologies for the implementation of the three-level 1500-V PV inverters.

The lifetime of the power devices, i.e., IGBTs and diodes, of the three-level topologies was estimated with an empirical lifetime model. On this basis, the most critical power device of the three-level topologies has been identified in the component-level reliability analysis. Also, following converter-level reliability assessment presented how the most stressed IGBTs and diodes affect the reliability of the entire inverter. It should be mentioned that the reliability investigation was conducted with a number of assumptions (e.g., ideal grid, MPPT control, and linear and cumulative damage model) for a comparative analysis. However, this reliability assessment provides an indication

#### 2.5. Summary

**Table 2.4:**  $B_x$  Lifetime of the Three-Level Inverter Candidates. Source: [J1].

| Mission profile | Topology | $B_x$ lifetime switching frequer |       |       | uency |

|-----------------|----------|----------------------------------|-------|-------|-------|

|                 |          | (year)                           | 2 kHz | 4 kHz | 6 kHz |

| Aalborg         | I-type   | B <sub>10</sub>                  | 142   | 86    | 54    |

|                 |          | $B_1$                            | 97    | 58    | 35    |

|                 | T-type   | $B_{10}$                         | 381   | 123   | 44    |

|                 |          | $B_1$                            | 264   | 83    | 29    |

| Sacramento      | I-type   | B <sub>10</sub>                  | 118   | 77    | 45    |

|                 |          | $B_1$                            | 80    | 52    | 30    |

|                 | T-type   | $B_{10}$                         | 210   | 66    | 22    |

|                 |          | $B_1$                            | 144   | 44    | 14    |

of the reliability of 1500-V PV inverters, hence, the investigation is beneficial for the topology selection of the 1500-V PV systems for a given mission profile.

## **Related Publications**

- **J1. J. He**, A. Sangwongwanich, Y. Yang, and F. Iannuzzo, "Lifetime Evaluation of Three-Level Inverters for 1500-V Photovoltaic Systems" *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 9, no. 4, pp. 4285-4298, Aug. 2021.

- **C1. J. He**, A. Sangwongwanich, Y. Yang, and F. Iannuzzo, "Thermal Performance Evaluation of 1500-VDC Photovoltaic Inverters Under Constant Power Generation Operation," in *Proc. IEEE CPERE*, pp. 579-583, Oct. 2018.

- **C2. J. He**, A. Sangwongwanich, Y. Yang, and F. Iannuzzo, "Lifetime Evaluation of Power Modules for Three-Level 1500-V Photovoltaic Inverters," in *Proc. IEEE APEC*, pp. 430-435, Mar. 2020.

# Chapter 3

# Impact of System Parameters on Reliability

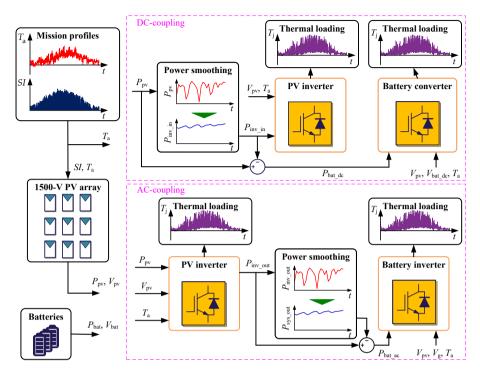

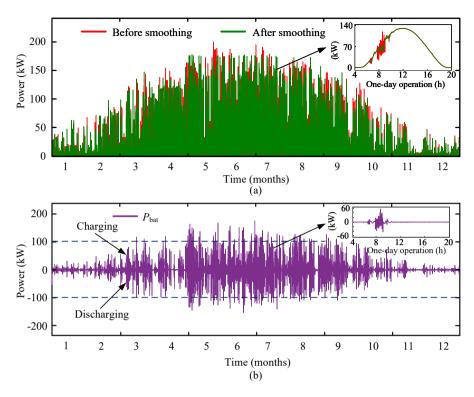

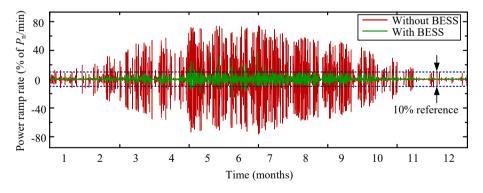

In addition to the topology selection for designing a highly-reliable 1500-V PV system, it is also essential to consider the influence of the system parameters on the reliability of PV power converters. The selection of system parameters plays a vital role in improving the performance of the PV systems in terms of energy production and reliability. This chapter aims to present the impact of system voltage ratings and integration of battery energy storage system (BESS) on the performance of 1500-V PV systems.

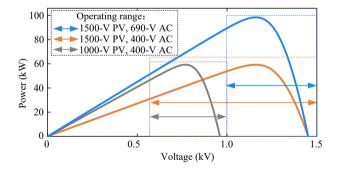

With a strong demand to guarantee the high availability of multi-megawatt (MW) PV plants, 1500-V string PV inverters are superior to centralized configurations [46, 47]. Normally, string PV inverters can provide wide operating voltage ranges both for the DC and the AC side [48, 49], e.g., they can be equipped with 1000-V/1500-V PV strings and connected to various AC voltages, e.g., 400 V or 690 V. Thus, the performance of 1500-V PV systems with centralized string inverter solutions, as depicted in Fig. 3.1, will be compared in this chapter, where the power/energy losses of on the main system components, i.e., DC wires, inverters, AC filters, and isolation transformers, will be estimated considering various DC- and AC-side voltage ratings.

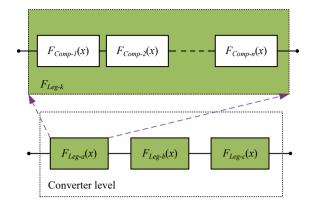

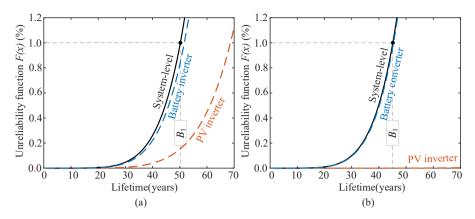

On the other hand, with an ever-increasing demand for enhancing the flexible grid-integration of PV systems, BESS integration is becoming increasingly popular, since it can smooth out the PV power fluctuation. The selection of system configuration, i.e., DC- or AC-coupling, should be carefully considered during the design stage of a 1500-V PV-battery system. Thus, it is essential to assess both the PV converters and the battery converters in terms of reliability, since they are the most lifetime-critical parts and determine the reliability of the entire PV-battery system. This Ph.D. project investigates the reliability of 1500-V PV-battery systems with a benchmarking of DC-and AC-coupled BESS configurations. In this chapter, the impact of BESS on the PV inverter reliability will be addressed, and the performance of all the power converters in these configurations will be assessed with reliability analysis from component- to system level.

**Fig. 3.1:** PV system based on centralized string inverter solution ( $T_a$ : ambient temperature, SI: solar irradiance). Source: [C5].

Table 3.1: Specifications of the String PV Inverter. Source: [C5].

| Parameter                                               | Value                          |  |

|---------------------------------------------------------|--------------------------------|--|

| Nominal output power P <sub>n</sub> [kW]                | 60 / 72 / 90 / 100             |  |

| Nominal output current In                               | 87 A                           |  |

| AC operating voltage $V_{LL}^1$ (RMS <sup>2</sup> ) [V] | 400 / 480 / 600 / 690          |  |

| Grid frequency $f_g$                                    | 50 Hz                          |  |

| Power factor $\cos(\varphi)$                            | 1.0                            |  |

| Maximum input voltage                                   | 1500 V                         |  |

| Input voltage range for nominal power                   | $1.44 \times V_{LL}$ to 1300 V |  |

| Switching frequency $f_{sw}$                            | 6 kHz                          |  |

| Adopted IGBT module                                     | Semikron 39MLI12T4V1           |  |

<sup>&</sup>lt;sup>1</sup> V<sub>I,I</sub>: line-to-line voltage

# 3.1 Large-Scale Photovoltaic Architecture

The influence of PV system voltage ratings on the system performance has been discussed in [C5], where a large-scale PV system based on the centralized string inverters is considered for case study, as presented in Fig. 3.1. In the case study of [C5], the impact of system voltage ratings (both DC and AC sides) and mission profiles on the power losses (on inverters, DC wires, AC filters, and transformers) and yearly energy yield of the PV system has been analyzed and will be summarized in this section.

# 3.1.1 System Configuration

Generally, the nominal power of string 1500-V PV inverters is not a fixed value. It can be varied from tens kW to over 100 kW, which is determined by the grid voltage. For the same reason, for a given PV system capacity, based on the grid voltage ratings, a certain number of string inverters are required. The considered string PV inverter is based on the three-level I-type topology, and its specifications are summarized in

<sup>&</sup>lt;sup>2</sup> RMS: Root-Mean-Square.

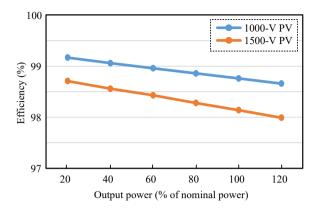

Fig. 3.2: Inverter efficiency comparison considering two PV string configurations, i.e., 1000-V PV and 1500-V PV. Source: [C5].

Table 3.1. The IGBT module is from Semikron [50], and its current and voltage ratings are 150 A and 1200 V, respectively.

By using an electro-thermal model, the efficiency characteristics of the string inverter have been obtained considering different PV string configurations, as shown in Fig. 3.2. Notably, the inverter efficiency with the 1500-V PV is slightly lower in comparison to that of the 1000-V PV. This reflects one of the drawbacks of the 1500-V configuration, i.e., increased inverter loading stress.

As for the DC wires between the PV arrays and the string inverters, in accordance with the National Electrical Code (NEC) [51], the wire ampacity, i.e., the maximum current carrying capacity, should be at least 1.25 times the PV array's short-circuit current. Regarding the wire length, the average DC wire length can be estimated based on the system capacity as discussed in [52]. Regarding the inverter output, as shown in Fig. 3.1, LCL filters are adopted to suppress the harmonics of the inverter and their outputs are connected to the low-frequency transformer, with which, the low-voltage (LV) outputs of the PV inverters are elevated to the medium voltage (MV) for connecting utility network. For the power losses on the LCL filters and the transformer, both comprise core losses and copper losses, which can be estimated by their loss models [53].

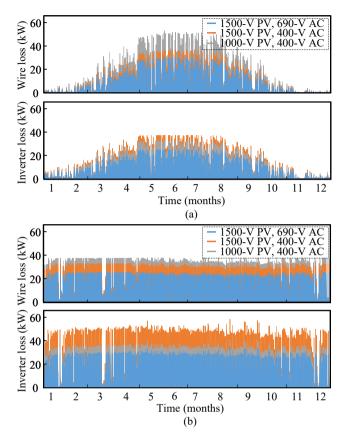

# 3.1.2 Comparative Study

Based on combinations of various DC and AC voltage ratings, three different centralized string PV inverter solutions have been considered for a 1.8-MW PV system, as summarized in Table 3.2, including the grid voltage, i.e., 400 V or 690 V, the PV string configuration, i.e., 1000- or 1500-V PV string, the DC wire size, and the number of inverter units. Notably, as it can be observed from Table 3.2, the PV string configuration and the grid voltage respectively determine the DC wire size and the number of inverter units, which will affect the amount of power losses and energy yield of the entire PV system. The procedure for the power loss analysis is summarized in Fig. 3.3. Similar to the mission profile translation presented in *Chapter 2*, the output

Table 3.2: Considered Centralized String PV Inverter Solutions. Source: [C5].

| Solution 1: 400-V grid voltage, 1000-V PV |                                  |  |

|-------------------------------------------|----------------------------------|--|

| PV panel configuration                    | $N_{\rm s} = 18,  N_{\rm p} = 9$ |  |

| DC wire gauge                             | 2 AWG                            |  |

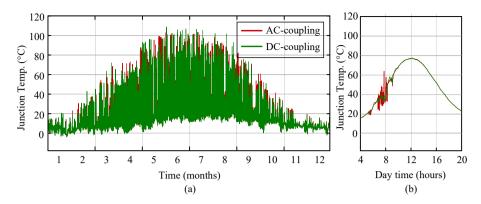

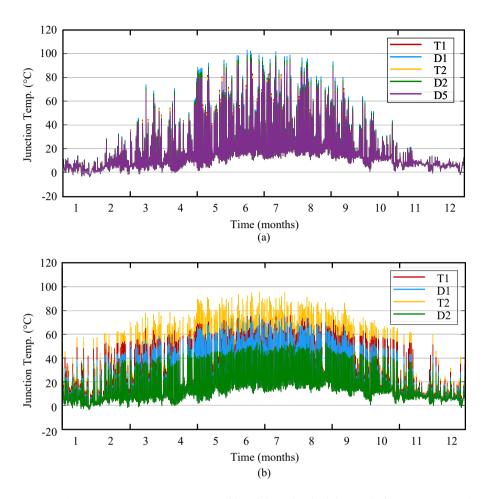

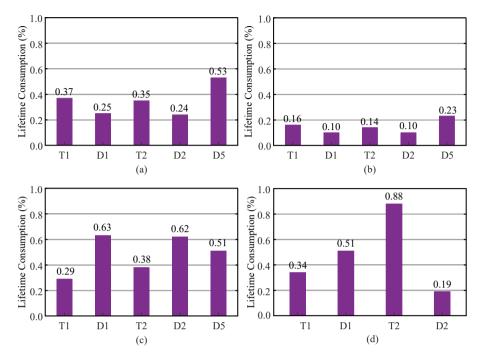

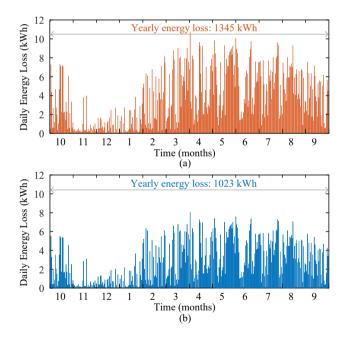

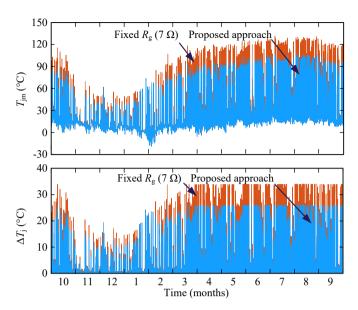

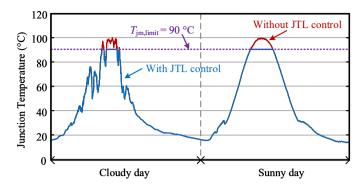

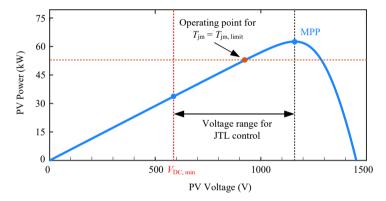

| Inverter units                            | 30                               |  |