# **Aalborg Universitet**

# Quantitative Feedback Design-Based Robust PID Control of Voltage Mode Controlled **DC-DC Boost Converter**

Kobaku, Tarakanath; Jeyasenthil, R; Sahoo, Subham; Ramchand, Rijil; Dragicevic, Tomislav

Published in:

I E E E Transactions on Circuits and Systems. Part 2: Express Briefs

DOI (link to publication from Publisher): 10.1109/TCSII.2020.2988319

Publication date: 2021

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Kobaku, T., Jeyasenthil, R., Sahoo, S., Ramchand, R., & Dragicevic, T. (2021). Quantitative Feedback Design-Based Robust PID Control of Voltage Mode Controlled DC-DC Boost Converter. *I E E Transactions on Circuits and Systems. Part 2: Express Briefs*, *68*(1), 286-290. Article 9069243. https://doi.org/10.1109/TCSII.2020.2988319

# **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

# Quantitative Feedback Design Based Robust PID Control of Voltage Mode Controlled DC-DC Boost Converter

Tarakanath Kobaku, R. Jeyasenthil, Subham Sahoo, Rijil Ramchand, *Senior Member, IEEE*, Tomislav Dragicevic, *Senior Member, IEEE*.

Abstract—This work addresses the problem of instability occurring in the voltage control mode of a non-minimum phase (NMP) DC-DC boost converter. To solve this instability issue in the presence of uncertainties and the external disturbances, quantitative feedback theory (QFT) is adapted to systematically design a robust proportional integral derivative (PID) controller, which is realized using only sensed output voltage as feedback. The advantages of the proposed PID design using the QFT are: (i) it eliminates the burden of tedious and ad-hoc tuning of PID gains using the conventional PID design approaches, (ii) current measurement is not required, (iii) disturbance dynamics (input voltage and load current variations) are included in the design stage itself, which further enhances the disturbance rejection performance of the output voltage, and (iv) it allows direct design for the non-minimum phase boost converter despite the bandwidth limitations. Extensive simulations and experiments are carried out to validate the efficacy of the proposed PID controller in the presence of the external disturbances and compared its superiority over a conventional PID controller.

Index Terms—DC-DC converter, Disturbance dynamics, PID, Quantitative feedback theory, Voltage regulation.

### I. INTRODUCTION

The growing applications of DC-DC boost converters in continuous conduction mode (CCM) have become prevalent in automotive, battery charging applications and so on, whose performance highly depends on the deployed control scheme [1]. The main objective is to always provide constant output voltage across the load despite input voltage and load variations. However, the control strategies for these converters are not robust against model uncertainties as well as the external disturbances. Thus, the closed-loop operation requires a robust control, which not only rejects the disturbance but also handles variations in the system parameters satisfactorily.

Current mode control (CMC) exhibit current loop instability for a duty ratio > 50% regardless of the DC-DC converter [2]. In voltage mode control (VMC), there is no duty ratio restriction. However, VMC operation provides a sluggish dynamic response for boost converters due to the presence of a right half plane (RHP) zero, thereby restricting the closed-loop bandwidth [2]. Hence, operating the non-minimum phase (NMP) boost converter close to the performance limits set by RHP zero is a challenging control task under VMC operation.

Tarakanath Kobaku and Rijil Ramchand are with the Department of Electrical Engineering, NIT, Calicut, Kerala, 673601, India, (e-mail:, tarak239@gmail.com; rijil@nitc.ac.in).

Among the robust control schemes [3-6, 25-27], sliding mode control (SMC) achieves the desired load voltage regulation at the extra cost of current and voltage sensors [3, 4, 5]. The usage of many sensors increases the overall cost and may also affect the reliability owing to fault in any of the additional sensors. Further, the presence of chattering phenomena in SMC prevents it from being used in commercial applications [4]. [6] implemented a model based internal model control (IMC) on NMP boost converter under VMC operation. this strategy significantly increases computational complexity. This serves as a motivation to design a computationally simple robust controller using only the measured output voltage as a feedback, avoiding the usage of many sensors as in SMC [3, 4,5], hybrid control [7], switching control [8] and in feed-forward control [9].

In the literature studies, several control schemes for dc-dc converters have been proposed but a simplified and systematic robust design are yet to be addressed. The PID controllers are employed to control the output voltage of dc-dc converters [6, 14, 15]. PID tuning is a cumbersome task, particularly in the presence of changes in input voltage, load current and parameter variations in the filtering components (L, C). In [15], PID tuning for a NMP boost converter is based on the phase margin obtained from an additional phase sensitive device. The tuning of conventional PID does not deal with a RHP zero and lacks the systematic design to control the output voltage. The PID design without RHP zero for a NMP boost converter exhibits overdamped/sluggish output voltage response [14]. The direct synthesis method based PID design incorporates RHP zero improves the output voltage [16]. Moreover, the conventional PID is non-robust for NMP boost converter using only single output voltage sensor.

The disturbance rejection capability of DC-DC converters can be improved by considering the disturbance dynamics in the controller design stage itself [6]. In the proposed work, a renowned robust control method known as the quantitative feedback theory (QFT) is employed [10-13]. The research works carried out in [10-13] consider the converter model of both minimum phase behavior and NMP boost converter [13]. These studies design the controller using the equivalent minimum phase system obtained with an all-pass filter. Most importantly, these works are entirely simulation studies carried under no real-world plant-model mismatch conditions. Further, it does not account dynamic disturbance models [2, 6] in their design process, which fails to improve the performance. The QFT method incorporates the disturbance models into PID design in a systematic manner (no ad-hoc tuning required). Such a design utilizing the disturbance dynamics in VMC operation is a challenging robust control problem. The effectiveness of proposed robust controller is validated extensively in simulations and verified under experimental conditions. It has been established that the

R. Jeyasenthil is with the Department of Electrical Engineering, NIT, Warangal, Telangana State, 506004, India (e-mail: jey@nitw.ac.in).

Subham Sahoo is with the Department of Energy Technology, Aalborg University (e-mail: sssa@et.aau.dk).

Tomislav Dragicevic is with the Center of Electric Power and Energy, Technical University of Denmark (e-mail: tomdr@elektro.dtu.dk)

designed robust PID controller works satisfactorily in the simulation and requires only one voltage sensor for conducting experiments. This constitutes the technical contribution of the paper.

# II. QFT DESIGN PROCEDURE FOR DISTURBANCE REJECTION PROBLEM

QFT is renowned for its suitability of implementation in the practical systems [12, 17]. The idea is to design a controller using the loop-shaping technique [18, 19], which reduces the controller gain at high frequency. The specifications are transformed into the so-called "QFT bounds," which is converting the closed loop specification into open loop bounds for subsequent controller design. The QFT bound captures the system uncertainty, which keeps the restriction on the controller design. Then, the loop shaping is carried out in such a way that it satisfies the QFT bounds. To generate the QFT bounds, there exist couple of algorithms based on quadratic inequalities for different specifications (disturbance rejection, set point tracking [17]). The uncertain linear time-invariant (LTI) plant is given by  $G(s) \in \{P(s, \lambda): \lambda \in \lambda\}$ , where  $\lambda \in$  $R^{l}$  is a vector of plant parameters whose values vary over a parameter box  $\lambda$  given by  $\lambda = \{\lambda \in \mathbb{R}^l : \lambda_i \in |\lambda_i, \overline{\lambda_i}|, \lambda_i \leq 1\}$  $\overline{\lambda_i}$ , i = 1, ..., l. The open-loop transmission function is defined as  $L(s, \lambda) = C(s)G(s, \lambda)$ . The objective is to synthesize the controller C(s) such that the following specifications are satisfied

Robust stability margin: 1.

$$\left| \frac{C(j\omega)G(j\omega)}{1 + C(j\omega)G(j\omega)} \right| \le \omega_s$$

Robust output disturbance rejection:

$$\left| \frac{1}{1 + C(j\omega)G(j\omega)} \right| \le \omega_d(\omega) \tag{2}$$

In the above specifications (1-2),  $\omega_s$  is the stability margin specification (M-circle magnitude corresponding to a desired gain and phase margin), and  $\omega_d$  is the output disturbance rejection specification. There are two ways to handle NMP system in QFT loop-shaping method [17]. First approach is by performing the loop-shaping design directly on the actual NMP system. Another way is to perform the loop-shaping on the minimum phase part of the actual system by shifting the minimum phase bound with the phase angle of the all-pass factor. In this work, the loop-shaping is carried out directly on the actual NMP system with the disturbance dynamics. This makes the proposed method different from the other methods in [12, 13] which does not account the disturbances in the design stage. With the addition of the disturbance dynamic models, the designed controller is more robust with respect to the disturbances than the design without it [12, 13].

The output disturbance rejection specification (2) with disturbance dynamics ( $\beta$ ) becomes as follows:

$$\left| \frac{\beta(j\omega)}{1 + C(j\omega)G(j\omega)} \right| \le \omega_d(\omega) \tag{3}$$

#### III. APPLICATION FOR NMP DC-DC BOOST CONVERTER

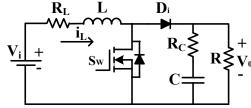

This section deals with the application of QFT design procedure outlined in section II to design a robust PID controller for a boost converter. The circuit diagram of a power stage boost circuit is shown in Fig. 1. The CCM operated DC-DC boost converter parameters are: L = 3.1 mH,  $R_L = 0.3 \Omega$ , and C =1930  $\mu F$ ,  $R_c$ =0.08  $\Omega$ . The nominal load resistance is  $R_n$ = 90  $\Omega$ . Switching frequency is 25 kHz. The input voltage,  $V_i = 10 \text{ V}$  and the output voltage,  $V_0 = 15 \text{ V}$ . From [2, 6], the plant model is given as:

$$= \frac{V_0}{1 - D} \frac{(1 + CR_C s)[R^2 (1 - D)^2 - (R + R_C)(R_{eq} + Ls)]}{\text{den}(s)}$$

(4)

where,  $den(s) = R(1 - D)[R(1 - D) + R_C(1 + C(R + R_C)s]$  $+(R + R_C)(R_{eq} + Ls)(1 + C(R + R_C)s)$

The uncertain transfer function of the boost converter system becomes as,

$$G(s) = \frac{k(a_1s+1)(a_2s+1)}{(b_1s^2+b_2s+1)}$$

(5)

The nominal parameters of transfer function are, k =22.0617,  $a_{1}$ =1.5440 × 10<sup>-4</sup>,  $a_{2}$ =-7.8287 × 10<sup>-5</sup>, b2 = 1.8847 × 10<sup>-3</sup>, b1 = 1.3345 × 10<sup>-5</sup>, With an uncertainty of about 10% [20-23],  $k \in [19.85, 24.27]$ ,  $a_1 \in [1.3896, 1.6984] \times$  $10^{-4}$ ,  $a_2 \in [-7.04583, -8.61157] \times 10^{-5}$ ,  $b_1 \in [1.20105,$  $1.46795 \times 10^{-5}$ ,  $b_2 \in [1.67, 2.073] \times 10^{-3}$ . The converter system exhibits a resonant behavior around 274 rad/s.

Fig. 1. Circuit diagram of a power stage dc-dc boost converter.

# **Design Specifications:**

A. ROBUST DISTURBANCE REJECTION PROBLEM:

(i). Audio susceptibility disturbance rejection problem: The dynamics of variations in the input voltage w.r.t the output voltage around the neighborhood of the operating point is given by the following transfer function (refer Fig.2):

$$D_a(s) = \frac{v_0(s)}{v_i(s)} = \frac{1.4857(0.0001544s + 1)}{(1.3345 \times 10^{-5}s^2 + 0.0018847s + 1)}$$

(6)

The specification for this disturbance rejection problem is

(for unit step input,  $|V_0| < 0.2 \text{ V}$  for time > 20 ms):

$$\left| \frac{D_{a}(j\omega)}{1 + L(j\omega)} \right| \leq \omega_{d}(\omega) = \left| \frac{s}{s + 75} \right|_{s = j\omega}$$

$$\underbrace{\frac{i_{L}(s)}{D_{o}(s)} D_{o}(s)}_{V_{i}(s)} D_{a}(s) + V_{o}(s) + V_{o}(s) + V_{o}(s) + V_{o}(s)}_{C(s)}$$

$$\underbrace{\frac{i_{L}(s)}{V_{i}(s)} D_{a}(s)}_{C(s)} D_{a}(s) + V_{o}(s) + V_{o}$$

Fig. 2 Feedback control for disturbance rejection problem of Boost converter.

The disturbance rejection specification chosen as the controller should reject the unit step disturbance within 20ms and keep the output voltage variation below 0.2 V. This time domain specification is captured by the tolerance  $(\omega_d)$ . Basically, the closed loop response should reject the effect of the disturbances once it is applied and settle down to its

desired position. So, the tolerance transfer function must have zero at the origin along with the one or more poles such that as time tends to infinity (i.e. Laplace operator  $s \to 0$ ), the tolerance approaches zero, i.e.,  $\omega_d(s) = \lim_{s \to 0} \frac{s}{s+a}$ .

By selecting just one parameter, the pole in the eq (7),

By selecting just one parameter, the pole in the eq (7), different performance levels of disturbance rejection can be achieved. Further guidelines/practical tips for selecting the output disturbance rejection specification are given in the reference [22, 24].

(ii). Output impedance disturbance rejection problem: The linear perturbations of load current w.r.t the output voltage around the neighborhood of the operating point is

$$D_o(s) = \frac{v_0(s)}{-i_L(s)}$$

$$= \frac{-0.8567(0.0001544s + 1)(0.0080639s + 1)}{(1.3345 \times 10^{-5}s^2 + 0.0018847s + 1)}$$

(8)

Specification for this disturbance rejection is same as in (7).

B. ROBUST STABILITY MARGIN:  $\omega_s = 1.2$  (Gain margin  $\geq 5$  dB, Phase margin (PM)  $\geq 60^{\circ}$ ).

The chosen design frequency set is

$$\mathbf{\Omega} = 2\pi \ [1,2.5,7.5,10,20,30,50,100,200,274,350,500,1000,2000.5000.125001 \ Hz]$$

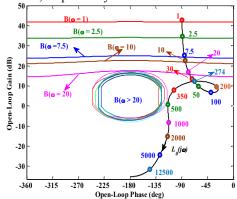

Note that the frequency set contains the frequencies upto half the switching frequency i.e., 12.5 kHz. The objective of loop-shaping is by adding the poles/zeros (real and/or complex) elements to the nominal plant such that it satisfies the QFT bounds at each frequency. Here, satisfying the bounds means the nominal *L* should lie on (or) above the open bounds at low frequency and lie outside the closed stability margin bounds at high frequency in order to satisfy the specification constraint. Figure 3 shows the nominal loop-shaping plot for the chosen converter and the designed feedback controller is

$$C(s) = \frac{6.14 \left(\frac{s}{117.9} + 1\right) \left(\frac{s}{150} + 1\right)}{s \left(\frac{s}{2000} + 1\right)}$$

(9)

Hereafter, the designed controller C is denoted as PID<sub>OFT</sub>.

# IV. SIMULATION STUDIES

This section evaluates the performance of the designed PID controllers to control the output voltage of a boost converter. The uncompensated NMP boost converter transfer function given by (4) exhibits a PM of 12<sup>0</sup> at a gain cross over frequency of 1.33 krad/s. For the NMP system, the achievable bandwidth is restricted by the position of RHP zero [2]. To have a fair comparison, a recently used PID controller from [6] is chosen as reference to obtain a PM of about 60<sup>0</sup> and a loop gain crossover frequency of 600 rad/s. In general, such a frequency domain designed PID has been considered for comparisons as delineated in [6, 17]. Following [2, 6, 16], the conventional PID parameters are given as:

$$K_p = 78.4 \times 10^{-3}, K_i = 3.34, K_d = 0.245 \times 10^{-3}$$

and  $T_f = 0.811 \times 10^{-3}$  (10)

K<sub>p</sub>,K<sub>i</sub>, K<sub>d</sub>, T<sub>f</sub> denotes the proportional, integral, derivative gains and derivative filter time constant, respectively.

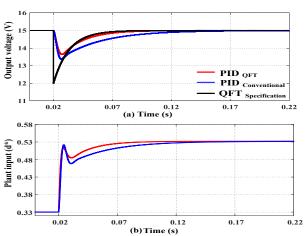

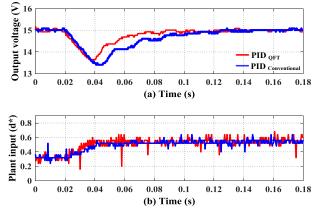

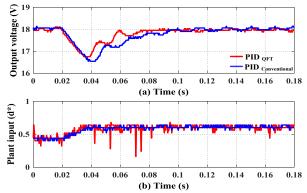

In linear simulation, a step change in the input source voltage is considered to analyze the performance of robust PID controller. The boost converter is operated in steady state with the output voltage  $V_0$ =15 V. Here, a step change in the input voltage from 10 V to 7 V is given at t=20 ms. As sown in Fig. 4(b), the proposed robust PID controller reacts quickly in the form of providing slightly large plant input (d\*) than the conventional PID controller during the transient time period to the external variation in the input voltage. Due to the quick corrective action with the proposed robust PID controller, the output voltage reaches back quickly to the nominal operating point ( $V_0$ =15 V) in comparison to the conventional PID with smaller undershoot, as shown in Fig. 4(a).

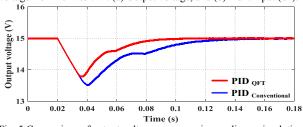

For simulation, the complete dynamics of DC-DC boost converter is realized using the SIMSCAPE POWER SYSTEMS toolbox of MATLAB/Simulink. A step change in the input voltage is considered in down direction (10 V to 7 V). During the transient (Fig. 5), the proposed robust PID controller input (d\*) provides a quick corrective action than the conventional PID and thereby achieving significant improvements such as fast settling time and reduced over/undershoot, respectively.

Fig. 3 Nominal loop shaping plot for the DC-DC boost converter.

Fig. 4 Regulatory behaviour in linear simulations for a change in input source voltage from 10 V to 7 V: (a) Output voltage, and (b) Plant input (d\*).

Fig. 5 Comparison of output voltage responses in non-linear simulations for a step change in input source voltage from  $10\ V$  to  $7\ V$ .

In the nonlinear simulations, the parameters for both the robust PID and conventional PID controllers are held identical as in linear simulations. The salient feature is that the closed-loop responses obtained here are similar to linear simulations. Hence for both linear and nonlinear simulations, it is observed that if the PID controller is designed by incorporating the disturbance models into the QFT design procedure, then such PID controller provides a quick corrective plant input to reject the effect of the external disturbances and provides robustness.

#### V. EXPERIMENTAL VERIFICATION

To validate the designed PID controller using QFT approach and the observations obtained from the simulations studies, a laboratory prototype of boost converter is built. The experimental setup is shown in Fig. 6. To expedite the experimental verification, dSPACE controller board was used. The prototype converter consists of a controllable MOSFET switch IRF 640, MUR 860 diode and TLP 250 gate driver circuit. To test the feasibility of designed P-I-D controllers on hardware experimental setup, the P-I-D parameters are kept as in the simulations (refer Section IV).

Fig. 6. Laboratory prototype of experimental setup.

Fig. 7. Regulatory responses for input voltage variation from  $10 \text{ V} \rightarrow 7 \text{ V}$  at nominal load: (a) Output voltage (b) Plant input.

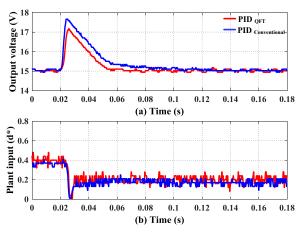

*Scenarios (a-b):* A step change in the input voltage from 10 V to 7 V and 10 V to 13 V are given at a nominal load current of 0.166 A. The proposed robust PID controller is able to bring the output voltage quickly to the reference voltage compared to the conventional PID controller as shown in Fig. 7 and 8 with plant inputs (duty ratio).

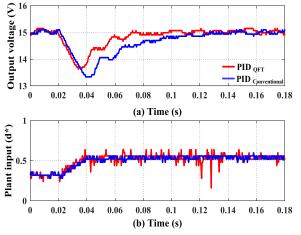

**Scenario** (c): For this case, it can be observed from Fig. 9that the conventional PID controller exhibits more deviation and takes long time to reach the steady-state in comparison to the proposed PID. Thereby, the response due to the proposed PID controller shows a significant improvement in the settling time with minimal deviation. The plant inputs for these scenarios are shown in Figs 9(b).

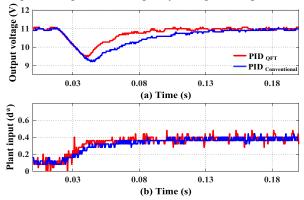

Scenarios (d-e): For a set-point of 18 V and 11 V, a step change in the input voltage is given from 10 V to 7 V and the corresponding closed-loop responses are shown in Fig. 10 and 11. It can be seen that, in both the scenarios, the output voltage reaches quickly with the proposed PID design as compared to the conventional PID. For instance, as shown in Fig. 11(a), the proposed PID reacts quickly with less deviation from the voltage reference i.e. peak deviation of 1.5 V as opposed to 2V in conventional PID and fast settling time of around 0.13 s against 0.18 s in existing PID.

Fig. 8. Regulatory responses for input voltage variation from  $10 \text{ V} \rightarrow 13 \text{ V}$  at nominal load: (a) Output voltage (b) Plant input.

Fig. 9. Regulatory responses for input voltage variation from  $10 \text{ V} \rightarrow 7 \text{ V}$  at a load current of 0.2A: (a) Output voltage (b) Plant input.

Fig. 10. Regulatory responses for a for input voltage variation from 10 V $\rightarrow$  7 V at a set-point of 18 V: (a) Output voltage (b) Plant input.

#### VI. CONCLUSIONS

In this work, a computationally simple robust PID controller is designed using QFT to control the output voltage of a NMPDC-DC boost converter under voltage mode control. The controller design for the disturbance rejection is formulated by including the disturbance dynamics of boost type dc-dc converter in the design stage itself. The proposed robust PID controller exhibits improvement in the output voltage response in the presence of uncertainty and external disturbances. The simulation results clearly show that the proposed robust PID controller performs better than the conventional PID controller for various disturbances. Further, the experimental results validate that the closed-loop responses guarantee significant improvement for all the disturbances. As a future scope of work, this work will be extended to deal with the tracking and start-up control problem using only a single voltage sensor.

Fig. 11 Regulatory responses for a for input voltage variation from 10 V → 7 V at a set-point of 11 V: (a) Output voltage (b) Plant input.

# REFERENCES

- [1] K. Venkata Ramana, S. Majhi and A. K. Gogoi, "Modeling and Estimation of DC–DC Buck Converter Dynamics Using Relay Feedback Output With Performance Evaluation," in *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 66, no. 3, pp. 427-431, March 2019.

- [2] R.W. Erickson and D. Maksimovic, Fundamental of Power Electronics, 2nd ed. Kuluwer, 2001, Newyork.

- [3] Siew-Chong Tan, Y. M. Lai and C. K. Tse, "A unified approach to the design of PWM-based sliding-mode voltage controllers for basic DC-DC converters in continuous conduction mode," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 53, no. 8, pp. 1816-1827, Aug. 2006.

- [4] S. Tan, Y. M. Lai and C. K. Tse, "General Design Issues of Sliding-Mode Controllers in DC–DC Converters," *IEEE Trans. Ind. Electron.*, vol. 55, no. 3, pp. 1160-1174, March, 2008.

- [5] A. Sferlazza, L. Martinez-Salamero, C. Albea Sanchez, G. Garcia and C. Alonso, "Min-Type Control Strategy of a DC-DC Synchronous Boost Converter," in *IEEE Transactions on Industrial Electronics*, (early access).

- [6] T. Kobaku, S. C. Patwardhan and V. Agarwal, "Experimental Evaluation of Internal Model Control Scheme on a DC–DC Boost Converter Exhibiting Nonminimum Phase Behavior," *IEEE Trans. Power. Electron.*, vol. 32, no. 11, pp. 8880-8891, Nov. 2017.

- [7] C. Sreekumar and V. Agarwal, "A Hybrid Control Algorithm for Voltage Regulation in DC–DC Boost Converter," *IEEE Trans. Ind. Electron*, vol. 55, no. 6, pp. 2530-2538, June 2008.

- [8] M. R. Mojallizadeh and M. A. Badamchizadeh, "Switched Linear Control of Quadratic-Boost Converters," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 7, no. 4, pp. 2196-2203, Dec. 2019.

- [9] C. Yao, X. Ruan and X. Wang, "Automatic Mode-Shifting Control Strategy With Input Voltage Feed-Forward for Full-Bridge-Boost DC-DC Converter Suitable for Wide Input Voltage Range," *IEEE Trans. Power. Electron.*, vol. 30, no. 3, pp. 1668-1682, March 2015.

- [10] C.Olalla, R. Leyva, A.E. Aroudi, P. Garces, QFT robust control of current-mode converters: application to power conditioning regulators, *Int. J. Electronics*. 96 (5), 503-520, 2009.

- [11] M. Veerachary, A.R. Saxena, Design of robust digital stabilizing controller for fourth-order boost DC-DC converter: A quantitative feedback theory approach, *IEEE Trans. Ind. Electron.*, 59 (2), 952-963, 2012.

- [12] Ali Al.Towati, Dynamic Analysis and QFT-Based Robust Control Design of Switched-Mode Power converters, Thesis for doctoral degree Helsinki University of Technology, 2008.

- [13] A. Altowati, K. Zenger and T. Suntio, "Analysis and design of QFT-based robust control of a boost power converter," 4th IET Conference on Power Electronics, Machines and Drives (PEMD), York, pp. 537-542, 2008

- [14] L. Guo, J. Y. Hung, R. M. Nelms, "Evaluation of DSP-based PID and fuzzy controllers for dc-dc converters", *IEEE Trans. Ind. Electron.*, vol. 56, no. 6, pp. 2237-2248, Jun. 2009.

- [15] K. I. Hwu and Y. T. Yau, "Performance Enhancement of Boost Converter Based on PID Controller Plus Linear-to-Nonlinear Translator," *IEEE Trans. Power. Electron.*, vol. 25, no. 5, pp. 1351-1361, May 2010.

- [16] K. Tarakanath, V. Agarwal, P. Yadav, "Hardware in the loop simulation of Direct Synthesis Based Two Degree of Freedom PID control for DC-DC boost converter using Real Time Digital Simulation in FPGA", *IEEE PEDES*, Mumbai, India, pp.1-5, 2014.

- [17] I. M. Horowitz, Quantitative Feedback Theory, QFT Publications, 1993, Colorado, USA.

- [18] R.D. Braatz, M. Morari, and S. Skogestad, "Loopshaping for Robust Performance", Int. J. Robu. Nonlin. Control, 6, 805-823,1996.

- [19] M.P.S. Gryning, Q. Wu, M. Blanke, H.H. Niemann, K.P.H. Andersen, Wind turbine inverter robust loop-shaping control subject to grid interaction effects, *IEEE Trans. Sust. Energy*, vol. 7, no. 1, pp. 41-50, Jan 2016

- [20] M. Kelemen , Y. Kanai, and I.M. Horowitz, One-point feedback approach to distributed linear systems. *Int. Jour. Control*, 49(3), 969– 980, 1989.

- [21] R. Jeyasenthil, S.B. Choi, H. Purohit, D. Jung, Robust position control and disturbance rejection of an industrial plant emulator system using the feedforward-feedback control, *Mechatronics (IFAC)*, vol. 57, pp. 29-38, Feb 2019.

- [22] M. Garcia-Sanz, Robust Control Engineering: Practical QFT Solutions, 2017, Taylor & Francis, USA.

- [23] Kang-Zhi Liu, Yu Yao, Robust Control: Theory and Applications, 2016, John Wiley& Sons, Singapore.

- [24] J.J. D"Azzo, C.H. Houpis, S.N. Sheldon. Linear control system analysis and design with MATLAB. Marcel Dekker; 2003.

- [25] N. Kumar and V. C. Mummadi, "Stability Region Based Robust Controller Design for High-gain Boost DC-DC Converter," in *IEEE Transactions on Industrial Electronics (Early Access)*.

- [26] F. Alonge, R. Rabbeni, M. Pucci and G. Vitale, "Identification and Robust Control of a Quadratic DC/DC Boost Converter by Hammerstein Model," in *IEEE Transactions on Industry Applications*, vol. 51, no. 5, pp. 3975-3985, Sept.-Oct. 2015.

- [27] Y. V. Hote, D. R. Choudhury and J. R. P. Gupta, "Robust Stability Analysis of the PWM Push-Pull DC–DC Converter," in *IEEE Transactions on Power Electronics*, vol. 24, no. 10, pp. 2353-2356, Oct. 2009.