### **Aalborg Universitet**

#### Resilient Operation of an MMC With Communication Interruption in a Distributed **Control Architecture**

Yang, Shunfeng; Chen, Haiyu; Sun, Pengfei; Wang, Haiyu; Blaabjerg, Frede

Published in: I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2021.3073432

Publication date: 2021

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Yang, S., Chen, H., Sun, P., Wang, H., & Blaabjerg, F. (2021). Resilient Operation of an MMC With Communication Interruption in a Distributed Control Architecture. *I E E E Transactions on Power Electronics*, 36(10), 12057 - 12069. Article 9405455. https://doi.org/10.1109/TPEL.2021.3073432

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 04, 2025

#### 1

# Resilient Operation of an MMC with Communication Interruption in a Distributed Control Architecture

Shunfeng Yang, Senior Member, IEEE, Haiyu Chen, Pengfei Sun, Haiyu Wang, Student Member, IEEE, Frede Blaabjerg, Fellow, IEEE, and Peng Wang, Fellow, IEEE

Abstract—Modular Multilevel Converters (MMCs) in HVDC applications usually adopt a distributed control architecture to manage a large number of sub-modules (SMs) through a communication network. The communication congestion and network disconnection might lead to communication interruption (CI) and eventually cause the system to malfunction. In this paper, a resilient operation strategy is proposed and studied to ride through the CI fault, in order to prevent frequent fault SM bypassing, replacement, or even system shutdown. The analysis of the MMC distributed control system with the presence of CI indicates that the insertion index of the faulted SM might become constant, which distorts the output current and results in over-voltage of the communication interrupted SM (CI-SM). The CI-SM capacitor voltage prediction can be used to determine the MMC safe operation period after CI occurs. During the safe operation period, the CI-SM power balance is sustained by utilizing pre-stored phase signals to generate a sinusoidal insertion index according to its capacitor voltage tracking error. Two operation modes are proposed and analyzed to ensure the MMC stable operation under various conditions. The system protection is sensibly used only if the CI duration exceeds a safe operation period, which avoids frequent SM cut-off. Good agreement of the CI-SM capacitor voltage is achieved between the theoretical and simulation results. The effectiveness and robustness of the proposed MMC resilient operation are experimentally confirmed.

Index Terms—Modular Multilevel Converters; distributed control; communication interruption; resilient operation

#### I. INTRODUCTION

odular Multilevel Converter (MMC) is one of the most promising topologies in recent years for medium or high voltage industrial applications, such as high-voltage dc transmission (HVDC), medium voltage micro-grids, and medium voltage motor drives [1-6]. The wide adoption of MMCs in industry is mainly due to their modularity, flexible expandability, common dc bus, etc. In HVDC applications, hundreds of

Manuscript received June 20, 2020; revised November 4, 2020 and February 12, 2021; accepted April 3, 2021. This work was conducted with the support from the National Natural Science Foundation of China under Grant 51807169, 62003283, and Sichuan Science and Technology Program under Grant 2021YFH0074. (Corresponding author: Pengfei Sun.)

Shunfeng Yang, Pengfei Sun, and Haiyu Wang are with the Department of Electrical Engineering, Southwest Jiaotong university, 611756, China. (e-mail: syang@swjtu.edu.cn; spf0325@163.com; wanghaiyu@my.swjtu.edu.cn).

Haiyu Chen is with the Xi'an Jiaotong University, Xi'an 710049, China (email: haiyuchen 0516@foxmail.com).

Frede Blaabjerg is with the Department of Energy Technology, Aalborg University, 9100 Aalborg, Denmark (e-mail: fbl@et.aau.dk).

Peng Wang is with the School of Electrical and Electronic Engineering, Nanyang Technological University, 639798, Singapore. (e-mail: ep-wang@ntu.edu.sg).

SMs are typically required for the MMCs to handle a high voltage level (hundreds of kilovolts) with relatively low-voltage power devices. In favor of properly manipulating such large numbers of SMs, distributed controls for MMCs are proposed in [7, 8], in order to distribute the heavy computational burden into different digital controllers. In the distributed structures, control messages are exchanged between the central and local controllers through the communication network [7-12]. However, communication failure during the data transmission (e.g. network congestion, communication interruption, etc.) is an inherent problem along with the distributed control structures for MMCs. The communication failure obstructs the data transmission between the central and local controllers, invalidating the central controller command, and might eventually cause the overall MMC system to malfunction.

In recent years, communication technologies for multilevel converters with distributed control systems have been investigated [12-15], while the communication reliability is a pending issue coming with the distributed network for the MMC system due to its massive communication links. The basic characteristics of the MMC communication network, which include the transmission media, synchronization accuracy, and network topology, are investigated in [15]. It indicates that the network topology has a strong impact on the network delay and the tolerance to failures. In [16], an additional leakage thyristor valve is applied in the LCC-MMC hybrid HVDC system in order to avoid the high voltage stress of the short-fault SMs in the communication failure condition. A fail-safe operation scheme is designed for the MMCs in [17], where the failure of slave controllers or SMs can be recognized in the communication break scenario by continuously checking the incoming data of the master controller. A fault-tolerant control architecture based on MMC distributed systems is presented in [18], in which a set of controllers are endowed with the capabilities to be the master controller and each controller in the control array is linked to the nearby controllers to improve the communication network redundancy. According to the previous research, the CI fault in an MMC system would terminate the data exchange among controllers and might cause system failure. To the best of our knowledge, existing solutions for MMC CI fault mostly focus on the post-fault operation. The network timeout method is mentioned in [18] to detect the failure in the controller modules. However, it is quite tricky to affirm a timeout in a real-time control system for the sake of an equilibrium between the effective protection and avoiding frequently triggering the fault alarm. Although redundant SMs are conven-

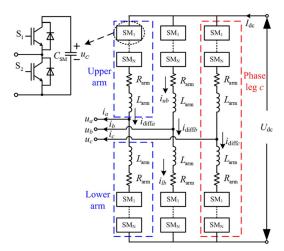

Fig. 1. Structure of a three-phase MMC.

tionally equipped in MMC system and can be simply switched-in during communication failure, the MMC resilient operation should be designed to ride-through the temporary CI faults avoiding frequently pre-charging, inserting/bypassing redundant SMs [19] and replace the SMs having possibly permanent faults with redundant ones.

In this paper, a resilient operation scheme, which ensures the safe and stable operation of the system after CI appears, is proposed according to theoretical analysis of the distributed controlled MMC performance with an SM CI fault. The analysis reveals that the interaction between the constant CI-SM insertion index and the additional dc component in the output current result in the CI-SM capacitor voltage ascent. The steepest CI-SM voltage ascent and the capacitor voltage safe margin are employed to determine the maximum allowable system operation period after CI occurs, which is used as the criterion to wisely classify the temporary and permanent communication network faults. During the allowable system operation period, the proposed resilient operation scheme utilizes pre-stored reference phase angle to implement the sinusoidal CI-SM insertion index, which stabilizes the SM capacitor voltage. The system would recover as long as the temporary CI fault is cleared. The resilient operation applying either stored output voltage or output current phase angles is discussed and compared in terms of the capacitor voltage deviation and the voltage balancing capability. The proposed resilient operation with MMC output reference amplitude and phase variation during the CI is investigated to reveal the restraints for a critical reference step change. Moreover, if the CI duration exceeds the maximum allowable operation period, a permanent network

fault will be affirmed by the system and protecting actions are implemented to decently cut the CI-SM off from the MMC main circuit. Simulation and experimental results are presented to verify the analytical findings. The effectiveness of the proposed resilient operation under both voltage and current phase conditions is verified on an MMC prototype.

#### II. MMC DISTRIBUTED CONTROL ARCHITECTURE

The basic structure and operation principles of an MMC with distributed control have been extensively explained in the literature [7, 20] and will not be discussed in this paper. The schematic diagram of a three-phase MMC is shown in Fig. 1. N half-bridge SMs are connected in series in one arm. Each arm is equipped with an arm inductor  $L_{\rm arm}$  and an equivalent resistor  $R_{\rm arm}$ . The three-phase output voltages and currents of the MMC are expressed as

$$\begin{cases} u_{ox} = U_o \cos(\omega_o t + \varphi_{ox}) \\ i_{ox} = I_o \cos(\omega_o t + \varphi_{ox} + \varphi_L) \end{cases}$$

(1)

where  $x \in (a, b, c)$ ,  $U_o$  and  $I_o$  are the amplitudes of  $u_{ox}$  and  $i_{ox}$  respectively,  $\omega_o$  refers to the fundamental angular frequency,  $\varphi_{ox}$  denotes the phase angle, and  $\varphi_L$  stands for the phase displacement between the output voltage and current. The differential current in phase leg x is defined as

$$i_{\text{diffx}} = I_{\text{dc}} + i_{\text{cirx}} \tag{2}$$

where  $I_{dc}$  is a dc current that maintains the power balance between the dc and ac sides of the MMC [3, 21], and  $i_{cirx}$  is the circulating current ripple, which is dominated by the  $2^{nd}$  order harmonic [20]. The arm currents can be written as

$$\begin{cases}

i_{ux} = i_{\text{diffx}} + 0.5i_{ox} \\

i_{lx} = i_{\text{diffx}} - 0.5i_{ox}

\end{cases}$$

(3)

Assuming the SM capacitor voltages are well-balanced, the normalized insertion index of the k<sup>th</sup> SM in the upper and lower arms can be obtained as

$$\begin{cases} n_{ukx} = 0.5 \left(1 - u_{ox}^{*}\right) \\ n_{lkx} = 0.5 \left(1 + u_{ox}^{*}\right) \end{cases}$$

(4)

where  $u_{ox}^* = 2u_{ox}/U_{dc}$ .

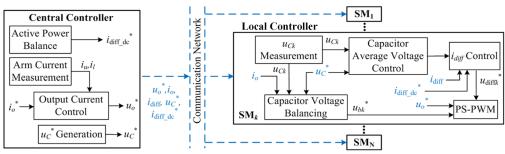

The structure of the distributed control architecture for the MMC is illustrated in Fig. 2, where the control tasks are assigned to different controllers, i.e. a central controller and local controllers in SMs [7]. The central controller mainly coordinates and manages the overall operation of the MMC. The output current control is implemented in the central controller

Fig. 2. Distributed control structure of the MMC.

with measured arm currents within each control cycle. The reference of the SM capacitor voltage  $u_c^*$  is calculated by the central controller according to the dc bus voltage and operation requirements of the MMC, e.g., in normal operation, in start-up process [7], or in fault-tolerant operation [22]. The local controller deals with the internal dynamics, PWM generation, and immediate protections [22] of the SM. It measures the capacitor voltage of the corresponding SM for voltage control and regulates the differential current of the MMC. The phase-shifted PWM (PS-PWM) scheme [23, 24] is adopted in the distributed control architecture. A phase-shifted triangular carrier is generated in each local controller. Necessary information is exchanged between the central and local controllers through a communication network. One message containing  $u_{ox}^*$ ,  $i_{diff dc}^*$ ,  $i_{ox}$  and  $i_{diffx}$ , which conveys adequate information for the real-time control in local controllers, is broadcasted by the central controller through the communication network in each control cycle. After receiving the message, an interrupt will be generated to enable the closed-loop control of each local controller in the same control period.

If CI happened, the corresponding local controller detects the fault once it cannot receive the message from the central controller on time. It should be noted that CI might be introduced by the network congestion lasting only for a few control cycles or by permanent network disconnection. Therefore, it is not practical to shut down the MMC system as soon as the occurrence of CI. Resilient protection and operation schemes under these circumstances have to be elaborately designed to prevent severe malfunctions or catastrophic damages of an MMC system without frequent operation interruptions.

## III. ANALYSIS OF MMC PERFORMANCE WITH COMMUNICATION INTERRUPTION

In the case of CI, the local controller of CI-SM is not able to receive the real-time control information from the master controller, which invalidates the local closed-loop control of CI-SM. The gating signals of CI-SM would be generated according to the insertion index calculated right before the occurrence of CI. Attention should be paid that the gating signals of the CI-SM become constant-duty-cycle square waves instead of SPWM waveforms, which greatly deteriorate the MMC performance. In this section, a single-phase MMC inverter is adopted to investigate the MMC performance with square-wave gating signals for one SM located in the lower arm, corresponding to a CI occurring at  $t_{\rm CI}$ . The analytical results can be utilized to determine the action instant of the proposed MMC CI protection.

#### A. Arm Voltage after CI

According to [25, 26], the output voltage of the  $i^{th}$  SM in the lower arm, i.e.,  $u_{ii}$  is obtained as

$$u_{li} = \frac{U_{dc}}{2N} + \frac{MU_{dc}}{2N} \cos(\omega_o t + \varphi_o)$$

$$+ \sum_{m=1}^{\infty} \sum_{n=-\infty}^{\infty} \frac{2U_{dc}}{m\pi N} \times \sin\left[\frac{(m+n)\pi}{2}\right] \times J_n\left(\frac{Mm\pi}{2}\right)$$

$$\times \cos\left\{m\left[\omega_c t + (i-1)\frac{2\pi}{N}\right] + n\left(\omega_o t + \varphi_o\right)\right\}$$

(5)

where  $M = 2U_o/U_{dc}$ ,  $\omega_c$  denotes the angular frequency of the triangular carriers, m is the harmonic order of the carrier wave  $(m=1,...,\infty)$ , n is the harmonic order of the reference  $(n=-\infty,...,\infty)$ , and  $J_n(x)$  refers to the Bessel coefficient of order n [25].

The output voltage of the CI-SM (e.g., the  $k^{\text{th}}$  SM in the lower arm,  $k \in [1, N]$ ) around CI instant can be expressed as

$$u_{lk} = \frac{U_{dc}}{N} n_{\text{CISM}} + \frac{U_{dc}}{N\pi} \sum_{n=1}^{\infty} \frac{1}{n} \left\{ \sin(n\pi n_{\text{CISM}}) - \sin \left[ 2n\pi (1 - \frac{n_{\text{CISM}}}{2}) \right] \right\} \cos(n\omega_c t)$$

(6)

where  $n_{\text{CISM}}$ =0.5+0.5 $M_{\text{CISM}}$ cos( $\omega_o t_{\text{CI}}$ + $\varphi_o$ ) is the insertion index of the CI-SM,  $t_{\text{CI}}$  is the time instant when CI appears [27]. The voltage of the lower arm near t= $t_{\text{CI}}$  can be derived accordingly

$$u_{l} = \sum_{i=1}^{N, i \neq k} u_{li} + u_{lk} = Q_{1} + Q_{2} + Q_{3} + Q_{4}$$

(7)

where  $Q_1$  represents the dc component,  $Q_2$  is the fundamental-frequency component,  $Q_3$  refers to the carrier-frequency components introduced by the CI-SM constant-duty-cycle output square waves, and  $Q_4$  stands for the carrier-frequency components introduced by the remaining healthy SMs.

#### B. Capacitor Voltage of CI-SM

The CI-SM without any control or protection operates in a critical condition, which makes it vital to investigate the operating condition of the CI-SM. Meanwhile, in order to obtain the CI-protection acting time, i.e., the safe operation period after the occurrence of CI at  $t_{\rm CI}$ , a relatively precise mathematical expression of the CI-SM capacitor voltage is crucial. The scenario that CI fault simultaneously occurs in multiple SMs is investigated in this sub-section for the sake of generality.

The capacitor voltages of CI-SMs are assumed the same in a relatively short period after CI. Considering the voltage of any CI-SM at  $t_{\rm CI}$  is  $U_{\rm dc}/N$ , the CI-SM capacitor voltage is yielded as

$$u_{\text{CISM}} = \frac{U_{\text{dc}}}{N} + \frac{1}{C} \int n_{\text{CISM}} \times i_l dt$$

(9)

where  $i_l$  is the lower arm current.

If the low-frequency harmonics in the differential current have been completely suppressed as in [28], the lower arm

$$Q_{1} = \frac{(N-1)U_{dc}}{2N} + \frac{U_{dc}}{N} n_{CISM}, \quad Q_{2} = \frac{(N-1)MU_{dc}}{2N} \cos(\omega_{o}t + \varphi_{o}), \quad Q_{3} = \frac{U_{dc}}{N\pi} \sum_{n=1}^{\infty} \frac{1}{n} \left\{ \sin(n\pi n_{CISM}) - \sin\left[2n\pi(1 - \frac{n_{CISM}}{2})\right] \right\} \cos(n\omega_{c}t),$$

$$Q_{4} = \sum_{m=1}^{\infty} \sum_{n=-\infty}^{\infty} \frac{2U_{dc}}{m\pi N} \times \sin\left[\frac{(Nm+n)\pi}{2}\right] \times J_{n}\left(\frac{MNm\pi}{2}\right) \times \cos\left\{Nm\left[\omega_{c}t + (i-1)\frac{2\pi}{N}\right] + n\left(\omega_{o}t + \varphi_{o}\right)\right\}$$

$$-\sum_{m=1}^{\infty} \sum_{n=-\infty}^{\infty} \frac{2U_{dc}}{m\pi N} \times \sin\left[\frac{(m+n)\pi}{2}\right] \times J_{n}\left(\frac{Mm\pi}{2}\right) \times \cos\left\{m\left[\omega_{c}t + (k-1)\frac{2\pi}{N}\right] + n\left(\omega_{o}t + \varphi_{o}\right)\right\}.$$

(8)

current can be written as

$$i_l = I_{\rm dc} - \frac{i_o}{2} \tag{10}$$

The output power is scarcely influenced in the steady-state by CI thanks to the high-bandwidth MMC output control, while it is assumed that a large number of SMs are used and the MMC is not over-modulated. According to the power balance of the single-phase MMC, the active power can be expressed as

$$I_{\rm dc}U_{\rm dc} = U_o I_o \cos \varphi_L = P_o \tag{11}$$

Combining (1), (10), (11) with (9), the capacitor voltage of the CI-SM can be derived as

$$u_{\text{CISM}} = \frac{U_{\text{dc}}}{N} + \frac{1}{C} \int n_{\text{CISM}} \left( \frac{P_o}{U_{\text{dc}}} - \frac{i_o}{2} \right) dt$$

(12)

According to (12), once CI occurs, the average dc component in the CI-SM capacitor current, which has a major contribution to the deviation of the CI-SM capacitor voltage, is randomly determined by the insertion index calculated in the last control cycle. However, on the account of the capacitor voltage control in normal SMs, the sum of the dc components of all the SM output voltages in one phase is forced to  $U_{\rm dc}$ .

$$U_{dc} = 0.5(N - N_{CI})U_{Cli} + n_{CISM}N_{CI}U_{CISM} + 0.5NU_{Cui}$$

(13)

where  $U_{Cui}$ ,  $U_{Cli}$ , and  $U_{CISM}$  stand for the dc capacitor voltages of the normal SMs in the upper and lower arms, and the CI-SM respectively, after the occurrence of CI, and  $N_{CI}$  refers to the number of CI-SMs.

At  $t=t_{CI}$  instant, the sum of the dc components of all the SM output voltages in one phase differs from the dc-bus voltage due to the CI-SMs. The voltage difference force  $I_{dc}$  to change. The changing  $I_{dc}$  causes almost the same capacitor voltage deviation, i.e., f(t), of all normal SMs in this phase in a short period after CI. The capacitor voltages of the upper and lower arm normal SMs can be expressed as

$$\begin{cases}

U_{Cui} = \frac{U_{dc}}{N} + f(t) \\

U_{Cli} = \frac{U_{dc}}{N} + f(t)

\end{cases}$$

(14)

By combining (13) and (14), f(t) can be derived as

$$f(t) = \frac{U_{dc} - N_{CI} n_{CISM} U_{CISM}}{N - 0.5 N_{CI}} - \frac{U_{dc}}{N}$$

(15)

Given that  $n_{\text{CISM}}$  becomes a constant value during CI, only the dc components in the lower arm current contribute to the CI-SM capacitor voltage deviation according to (12). And, the constant  $n_{\text{CISM}}$  introduces also extra dc components in the lower arm current. Based on (11),  $I_{\text{dc}}$  is almost the same before and after CI. Hence, the dc components introduced into  $i_o$  during CI should be investigated, which can be derived as

$$i_{o_{-}dc} = \frac{u_{o_{-}dc}}{R} = \frac{(u_{l} - u_{u})_{dc}}{2R}$$

$$= \frac{\left[0.5(N - N_{CI})U_{Cli} + N_{CI}n_{CISM}U_{CISM}\right] - \left[0.5NU_{Cui}\right]}{2R}$$

$$= \frac{N_{CI}}{N - 0.5N_{CI}} \times \frac{Nn_{CISM}U_{CISM} - 0.5U_{dc}}{2R}$$

(16)

where  $u_l$  and  $u_u$  indicate the upper and lower arm output voltage respectively, R is the load resistance. Equation (16) indicates

that the occurrence of CI induce an extra dc component in the output current, and such a dc current varies with  $n_{\text{CISM}}$ .

Substituting (16) into (12) and the average voltage of the CI-SM capacitors can be solved as

$$U_{\text{CISM}} = \left[ \left( \frac{N}{N_{\text{CI}}} - 0.5 \right) \frac{4RP_o}{n_{\text{CISM}}NU_{dc}} + \frac{U_{\text{dc}}}{2n_{\text{CISM}}N} \right] + \left[ \frac{U_{\text{dc}}}{N} - \left( \frac{N}{N_{\text{CI}}} - 0.5 \right) \frac{4RP_o}{n_{\text{CISM}}NU_{dc}} - \frac{U_{\text{dc}}}{2n_{\text{CISM}}N} \right] e^{-\frac{N_{\text{CI}} - n_{\text{CISM}}^2 N}{N - 0.5N_{\text{CI}} - 4RC}t}$$

(17)

The capacitor voltage variation of the CI-SMs can be described by (17). When  $n_{\text{CISM}} = 0$ , the CI-SM is bypassed, the capacitor voltages would stay at the initial voltage as described by (12). When  $n_{\text{CISM}} \neq 0$ , the first part of (17) determine the steady-state value of  $U_{\text{CISM}}$ , which is inversely proportional to  $n_{\text{CISM}}$ , while the second part indicates the rising rate of the capacitor voltage.

When CI happens,  $U_{\text{CISM}}$  would exceed the pre-defined safe-operation voltage range in a short period of time, i.e.,  $t_p$ . If the dc bus voltage, the rated power, the SM capacitance, the maximum modulation index, the number of CI-SMs, and the allowed capacitor voltage range of the MMC system are fixed,  $t_p$  can be calculated according to (17). Moreover, as can be calculated based on (17), the deviation of  $U_{\text{CISM}}$  decreases with the increase of the number of CI-SMs, as long as the assumptions made in this sub-section hold. Therefore,  $N_{\text{CI}} = 1$  is mostly considered for the analysis in this paper. Note that the CI occurring instant is not predictable, which makes it impossible to acquire the exact value of  $n_{CISM}$ . Thus,  $t_p$  should be selected according to the minimum value calculated by (17). In summary,  $t_p$  is related with the MMC dc bus voltage, the SM number, the output power, the SM capacitance, the maximum modulation index, and the allowed capacitor voltage deviation. It should be noted that the capacitor voltage ripple due to the ac components of the arm current, whose amplitude is normally less than 10% of the capacitor operating dc voltage, would also affect the CI-SM capacitor voltage value. Thus, adequate margin should be reserved in  $t_p$  selection.

### IV. PROPOSED RESILIENT OPERATION OF AN MMC WITH COMMUNICATION INTERRUPTION

In this MMC distributed control system, the safe operation period  $t_p$  calculated in the previous section can be utilized to make a distinction between the network congestion and network disconnection. Based on the MMC distributed control scheme, the central controller sends messages to SMs in each control cycle and the SMs update their status to the central controller by request for system monitoring [7]. On the one hand, if a local controller does not receive the central controller's message for a few control cycles and the request from the central controller is not acknowledged but the communication is recovered within  $t_p$ , no critical protection is required and the MMC operation is scarcely affected. On the other hand, if CI between the central and local controllers lasts for a period of  $t_p$ , network disconnection is present by both the central and local controllers and necessary protecting actions are required before any device damages or malfunctions of the system.

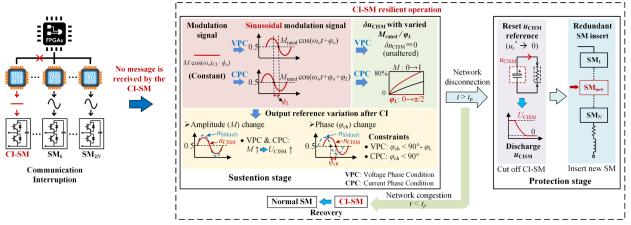

This section presents a resilient operation scheme for the MMC systems to ride through the CI problem. The resilient operation scheme can be divided into two stages: sustention stage and protection stage. At the sustention stage, the capacitor voltage of the CI-SM is stabilized and the system operates normally. At the protection stage, the CI-SM intentionally and gradually drifts its capacitor voltage down to zero and then cut itself off from the system automatically. Meanwhile, the central controller operates the MMC system with remaining SMs [22].

#### A. Sustention Stage

According to the analysis in section III, depending on the direction of the average CI-SM capacitor current, the  $U_{\rm CISM}$  might increase or decrease dramatically if the MMC operates at its rated power and the insertion index happens to be close to unity. In this case, the capacitor voltage likely reaches the safe-operation boundary when the period of CI is close to  $t_{\rm p}$ . The high capacitor voltage might cause overvoltage damage for the CI-SM capacitor and switching devices, and lead to the CI-SM malfunction. Moreover, the MMC performance might be deteriorated by the significantly increased CI-SM capacitor voltage.

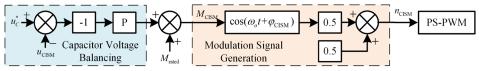

The essential reason for the CI-SM capacitor voltage ascent is that  $n_{\text{CISM}}$  becomes a constant value without the fundamental component for power balance [20]. To avoid the constant insertion index for the CI-SM, the discrete phase angles of the output voltage in the last fundamental period are stored in the memory of the local controllers. The stored phase angles are utilized to generate a sinusoidal signal with the fundamental frequency. The amplitude of the sinusoidal signal is generated by a local control loop, as shown in Fig. 3, where  $n_{\text{CISM}} = 0.5$  [1]  $+ M_{\text{CISM}} \times \cos(\omega_o t + \varphi_{\text{CISM}})$ ]. The values of  $\cos(\omega_o t + \varphi_{\text{CISM}})$  in the last fundamental period are recorded.  $M_{\text{rated}}$  is the modulation index of the rated operation point and  $u_c^*$  is the SM capacitor voltage reference. In order to eliminate the impact of voltage ripple on the control loop, the measured CI-SM capacitor voltage is low-pass filtered to obtain  $u_{CISM}$ . The capacitor voltage error is fed into a proportional (P) controller to change the amplitude of the sinusoidal signal, i.e.,  $M_{CISM}$ , for capacitor voltage balance. The output of the P controller in Fig. 3 is normalized by  $u_c^*$ .

Note that the stored sinusoidal signal can either be in phase with the output voltage or with the output current. For simplicity, the two conditions are named as the voltage phase condition (VPC) and the current phase condition (CPC), respectively.

It is assumed that all SMs operate in the rated operation point before CI appears. Considering that the output control for normal SMs functions effectively during CI, the fundamental frequency component in the MMC output switching function can be regarded as unchanged as given in (18).

$$NM_{\text{rated}} \cos(\omega_o t + \varphi_o) = \frac{1}{2} M_{\text{CISM}} \cos(\omega_o t + \varphi_{\text{CISM}}) + (N - 1) n_{li(\text{ac})} - N n_{ui(\text{ac})}$$

(18)

where  $n_{li(ac)}$  and  $n_{ui(ac)}$  stand for the fundamental components in the SM insertion indices for the lower and upper arms, respectively. The modulation indices of the normal SMs should have almost the same value during CI. Therefore  $n_{li(ac)}$  and  $n_{ui(ac)}$  can be expressed as

$$n_{ui\_(ac)} = -0.5 \times M' \times \cos(\omega_o t + \varphi_o')$$

$$n_{h_{(ac)}} = 0.5 \times M' \times \cos(\omega_o t + \varphi_o')$$

(19)

where M' and  $\varphi_o'$  represent the amplitude and the phase angle of  $n_{li(ac)}$  and  $n_{ui(ac)}$  during CI. Substitute (19) into (18), the fundamental frequency components in  $n_{li(ac)}$  and  $n_{ui(ac)}$  yields as

$$M'\cos(\omega_o t + \varphi_o') = \frac{2NM_{\text{rated}}\cos(\omega_o t + \varphi_o) - M_{\text{CISM}}\cos(\omega_o t + \varphi_{\text{CISM}})}{2N - 1}$$

(20)

The circulating current is directly generated by the difference between the dc-link voltage and the sum of the inserted voltages in the arms. Ignoring the impact of parasitic arm resistance  $R_{\text{arm}}$ ,  $i_{\text{cir}}$  can be derived as

$$i_{cir} = \frac{1}{2L_{arm}} \int \left[ U_{dc} - \left( u_u + u_l \right) \right] dt \tag{21}$$

The sum of the dc capacitor voltages in each arm remains constant, which equals  $U_{\rm dc}$ . Based on the effect of the voltage controllers, the capacitor voltages of normal SMs in one arm have an average distribution, and the output voltage of upper and lower arms can be derived accordingly

$$u_{u} = U_{dc} \left[ 0.5 - 0.5M ' \cos(\omega_{o} t + \varphi_{o} ') \right]$$

$$u_{l} = \left( U_{dc} - U_{\text{CISM}} \right) \left[ 0.5 + 0.5M ' \cos(\omega_{o} t + \varphi_{o} ') \right]$$

$$+ U_{\text{CISM}} \left[ 0.5 + 0.5M_{\text{CISM}} \cos(\omega_{o} t + \varphi_{\text{CISM}}) \right]$$

(22)

Substituting (20) and (22) into (21),  $i_{cir}$  is yielded as

$$i_{cir} = \frac{NU_{CISM}}{2(2N-1)\omega_o L_{arm}} \times \left[ M_{rated} \sin(\omega_o t + \varphi_o) - M_{CISM} \sin(\omega_o t + \varphi_{CISM}) \right]$$

(23)

According to (3), the lower arm current is  $i_l$ = $-0.5i_o$ + $I_{dc}$ + $I_{cir}$ . The current flowing through the capacitor in the CI-SM can be obtained as the product of the switching function and the lower arm current. However, only the dc component in CI-SM capacitor current contributes to the capacitor voltage shifting, thus the dc capacitor current is derived as

$$(n_{\text{CISM}}i_{l})_{\text{dc}} = \frac{1}{2}I_{\text{dc}} - \frac{1}{8}M_{\text{CISM}}I_{o}\cos(\varphi_{o} + \varphi_{L} - \varphi_{\text{CISM}}) + \frac{M_{\text{CISM}}M_{\text{rated}}NU_{\text{CISM}}}{8(2N-1)\omega_{o}L_{\text{arm}}}\sin(\varphi_{o} - \varphi_{\text{CISM}})$$

(24)

Note that  $I_{dc}$  can be substituted by  $M_{rated}I_o\cos(\varphi_L)/4$  according to the MMC active power balance [20], equation (24) is re-

Fig. 3. Block diagram of the capacitor voltage balancing loop in CI-SM.

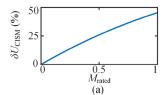

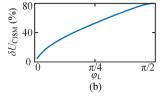

Fig. 4. Theoretical value of CI-SM capacitor voltage deviation rate  $\delta U_{\rm CISM} = |NU_{\rm CISM}/U_{\rm dc}-1|$  with varied: (a)  $M_{\rm rated}$ ; (b)  $\varphi_{\rm L}$ .

written as

$$(n_{\text{CISM}}i_{l})_{\text{dc}} = \frac{M_{\text{rated}}I_{o}}{8}\cos\varphi_{L} - \frac{M_{\text{CISM}}I_{o}}{8}\cos(\varphi_{o} + \varphi_{L} - \varphi_{\text{CISM}}) + \frac{M_{\text{CISM}}M_{\text{rated}}NU_{\text{CISM}}}{8(2N-1)\omega_{o}L_{\text{arm}}}\sin(\varphi_{o} - \varphi_{\text{CISM}})$$

(25)

Based on the aforementioned principle of resilient operation, the CI-SM would operate in either VPC or CPC during the sustention stage. The stability of the CI-SM under these two conditions should both be investigated.

When the CI-SM operates in VPC, the phase angle  $\varphi_{\text{CISM}}$  is equal to  $\varphi_{\text{o}}$ . The dc-component in the CI-SM capacitor current is derived as

$$\left(n_{\text{CISM}}i_{l}\right)_{\text{dc}} = \frac{1}{8}M_{\text{rated}}I_{o}\cos\varphi_{L} - \frac{1}{8}M_{\text{CISM}}I_{o}\cos\varphi_{L}$$

(26)

According to Fig. 3,  $M_{\rm CISM}$  should be equal to the rated modulation index  $M_{\rm rated}$  when CI occurs. Thus, the two terms in (26) spontaneously cancel each other out in VPC, which means no disturbance is introduced into the CI-SM capacitor current by CI fault in VPC. Hence the value of  $U_{\rm CISM}$  remains unchanged and (26) always equals zero during the sustention stage.

When the CI-SM operates in CPC, the phase angle  $\varphi_{\text{CISM}}$  equals  $\varphi_0 + \varphi_L$ . The de-component in the CI-SM capacitor current can be expressed as

$$(n_{\text{CISM}}i_l)_{\text{dc}} = \frac{1}{8}M_{\text{rated}}I_o\cos\varphi_L - \frac{1}{8}M_{\text{CISM}}I_o$$

$$-\frac{M_{\text{CISM}}M_{\text{rated}}NU_{\text{CISM}}}{8(2N-1)\omega_o L_{\text{arm}}}\sin\varphi_L$$

(27)

Given that a P-controller is applied in the CI-SM voltage balance control,  $M_{\text{CISM}}$  can be expressed as

$$M_{\text{CISM}} = M_{\text{rated}} + K_{\text{P\_bal}} \left( \frac{NU_{\text{CISM}}}{U_{\text{dc}}} - 1 \right)$$

(28)

where  $K_{\rm p\_bal}$  is the gain of the P-controller. Evaluating equation (27) in s-domain, the current disturbance in (27) is a zero-order element, which can be restrained by a first-order controller, i.e., the P-controller. Therefore, the capacitor voltage of the CI-SM can be stabilized based on the control structure in Fig. 3. Equation (27) would be equal to zero in steady state, and the CI-SM capacitor voltage in CPC can accordingly be derived as

$$U_{\text{CISM}} = -\frac{\left(2N-1\right)\omega_{o}L_{\text{arm}}I_{o}}{2NM_{\text{rated}}\sin\varphi_{L}} - \frac{U_{dc}\left(M_{\text{rated}} - K_{\text{P\_bal}}\right)}{2K_{P\_bal}N} + \left[\frac{\left(2N-1\right)I_{o}\omega_{o}L_{\text{arm}}}{2NM_{\text{rated}}\sin\varphi_{L}} + \frac{U_{dc}\left(M_{\text{rated}} - K_{\text{P\_bal}}\right)}{2K_{P\_bal}N}\right]^{2} + \left(\frac{U_{dc}I_{o}\left(2N-1\right)\omega_{o}L_{\text{arm}}}{K_{\text{P\_bal}}N^{2}M_{\text{rated}}\sin\varphi_{L}}\right)\left(M_{\text{rated}}\cos\varphi_{L} - M_{\text{rated}} + K_{\text{P\_bal}}\right)$$

However, a steady-state error might be introduced into  $U_{\text{CISM}}$  while using P-controller, which is evaluated as

$$\left[U_{\text{CISM}}\right]_{ss} = \left|U_{\text{CISM}} - \frac{U_{dc}}{N}\right| \tag{30}$$

According to (29), the deviation of  $U_{\text{CISM}}$  is positively related to  $M_{\text{rated}}$  and  $\varphi_{\text{L}}$ , while the correlations can be more intuitively observed from Fig. 4. It should be noted that the proportional-integral (PI) controller can be used to eliminate the steady-state error in (30).

The control abilities of the capacitor voltage balancing controller during CI with different phase conditions are also investigated. Based on the control structure depicted in Fig. 3 and the capacitor balancing control introduced in Fig. 15 in [7], the closed-loop transfer function of the voltage balance control loop is derived as (31) when the CI-SM operates in VPC.

$$\phi(s) = \frac{I_o \omega_x N \left( K_{P_{\_bal}} \cos \varphi_L \right)}{8s C_{SM} \left( s + \omega_x \right) U_{dc} + I_o \omega_x N \left( K_{P_{\_bal}} \cos \varphi_L \right)}$$

(31)

where  $\omega_x$  stands for the cut-off frequency of the low-pass filter. When the CI-SM operates in CPC, the closed-loop transfer function of the balancing controller is derived as

$$\phi(s) = \frac{I_o \omega_x N K_{P_bal}}{8s C_{SM} (s + \omega_x) U_{dc} + I_o \omega_x N K_{P_bal}}$$

(32)

It can be concluded from (31) and (32) that the balancing control ability is attenuated in VPC when compared with that in CPC. The control ability in VPC would be further deteriorated with the ascending of  $\varphi_L$ .

#### B. Reference variation during sustention stage

When CI happens, the local controller of the CI-SM couldn't receive the command from the central controller, which is critical if the output reference varies during this period. The MMC system performance with the proposed resilient operation during the output reference change is vital to be investigated.

Assuming the MMC output current amplitude  $I_0$  is increased, the value of M for normal SMs would be simultaneously raised while  $M_{\rm CISM}$  remains unaltered. It can be deduced from (26) and (27) that the dc capacitor current in CI-SM augments in both phase conditions, leading to an ascending  $U_{\rm CISM}$ . According to Fig. 3,  $M_{\rm CISM}$  would then rise up and  $U_{\rm CISM}$  will eventually be stabilized at a value higher than the capacitor voltage reference  $u_c^*$ , to retrieve the balance in (26) and (27). The increased  $U_{\rm CISM}$  contributes to the MMC output variation as well. Therefore, the proposed operation method ensures the MMC output reference tracking while its amplitude varies.

Fig. 5. Block diagram of the CI-SM resilient operation after CI occurs

Assuming that the phase of output reference is shifted during the sustention stage, an additional phase change  $\varphi_{ch}$  would be introduced into the output voltage and current:

$$\begin{cases} u_o = U_o \cos(\omega_o t + \varphi_o + \varphi_{ch}) \\ i_o = I_o \cos(\omega_o t + \varphi_o + \varphi_L + \varphi_{ch}) \end{cases}$$

(33)

However, the phase angle of CI-SM remains ( $\omega_o t + \varphi_{\text{CISM}}$ ) after the reference phase change. The upper and lower arm voltages are derived as

$$u_{u} = N \left( \frac{1}{2} - \frac{1}{2} M_{\text{rated}} \cos(\omega_{o} t + \varphi_{o} + \varphi_{ch}) \right) U_{Cui}$$

$$u_{l} = (N - 1) \left( \frac{1}{2} + \frac{1}{2} M_{\text{rated}} \cos(\omega_{o} t + \varphi_{o} + \varphi_{ch}) \right) U_{Cli}$$

$$+ \left( \frac{1}{2} + \frac{1}{2} M_{\text{CISM}} \cos(\omega_{o} t + \varphi_{\text{CISM}}) \right) U_{\text{CISM}}$$

(34)

For that the output current control is still efficient in sustention stage, the fundamental component in the normal SM insertion index can be derived similar to (20).

$$M' \times \cos(\omega_o t + \varphi_o' + \varphi_{ch}) = \frac{2NM_{\text{rated}} \cos(\omega_o t + \varphi_o + \varphi_{ch}) - M_{\text{CISM}} \cos(\omega_o t + \varphi_{\text{CISM}})}{2N - 1}$$

(35)

Taking CPC as an example, the additional ac component in  $i_{cir}$  is obtained as

$$i_{\text{cir\_ac}} = -\frac{M_{\text{rated}}}{4\omega_o L_{\text{arm}}} \left\{ (N-1) \left[ \sin(\omega_o t + \varphi_{\text{ch}}) (U_{Cli} - U_{Cui}) \right] + \left[ \sin(\omega_o t + \varphi_L) U_{\text{CISM}} - \sin(\omega_o t + \varphi_{\text{ch}}) U_{Cui} \right] \right\}$$

(36)

According to (3), the upper arm current is derived as

$$i_u = 0.5 [I_o \cos(\omega_o t + \varphi_{ch} + \varphi_L) + I_{o dc}] + I_{dc} + i_{cir ac}$$

(37)

The insertion index for the upper arm SMs considering reference phase change is

$$n_u = \frac{1}{2} - \frac{1}{2} M_{\text{rated}} \cos(\omega_o t + \varphi_o + \varphi_{ch})$$

(38)

During the steady-state operation, the circulating current control would properly adjust the dc components in the circulating current, to ensure that the dc capacitor current in the normal SMs, i.e.,  $(n_u i_u)_{dc}$ , approximately equals zero for the sake of system stable operation [11].

According to (37) and (38),  $(n_u i_u)_{dc}$  can be expressed as

$$(n_{u}i_{u})_{dc} = \frac{I_{dc}}{2} - \frac{M_{\text{rated}}I_{o}\cos\varphi_{L}}{8} + \frac{I_{o\_dc}}{4}$$

$$-\left[\frac{M_{\text{rated}}\cos(\omega_{o}t + \varphi_{o} + \varphi_{ch}) \times i_{\text{cir\_ac}}}{2}\right]_{dc}$$

$$= \frac{I_{o\_dc}}{4} - \left[\frac{M_{\text{rated}}}{2}\cos(\omega_{o}t + \varphi_{o} + \varphi_{ch}) \times i_{\text{cir\_ac}}\right]_{dc} = 0$$

(39)

Therefore,  $I_{o_{\underline{dc}}}$  can be obtained by substituting (36) in to (39).

$$I_{o_{-}dc} = \frac{M_{\text{rated}}^2 U_{\text{CISM}}}{4\omega_o L_{\text{arm}}} \sin(\varphi_{ch} - \varphi_L)$$

(40)

According to (36) and (40), the reference phase change during the sustention stage would bring an extra dc-component in  $i_0$  and a fundamental frequency component in  $i_{cir}$ . Based on (36) and (40), the direct component in the CI-SM capacitor current can be expressed as

$$(n_{\text{CISM}}i_l)_{\text{dc}} = \frac{1}{8}M_{\text{rated}}I_o\cos\varphi_L$$

$$-\frac{M_{\text{rated}}^2U_{\text{CISM}}}{16\omega_o L_{\text{arm}}}\sin(\varphi_{\text{ch}} - \varphi_L) - \frac{1}{8}M_{\text{CISM}}I_o\cos\varphi_{\text{ch}} \qquad (41)$$

$$-\frac{M_{\text{rated}}M_{\text{CISM}}}{16\omega_o L_{\text{arm}}} \left[ (N-1)(U_{Cli} - U_{Cui}) - U_{Cui} \right]\sin(\varphi_{ch} - \varphi_L)$$

When  $\varphi_{ch}$  changes, (41) can still be zero by properly adjusting  $M_{CISM}$ . The adjustment is accomplished by the capacitor voltage balance controller for CI-SM. Thus, the dc disturbance in CI-SM capacitor current would eventually be canceled out in steady-state when the output reference phase is changed. However,  $i_{diff\_ac}$  and  $I_{o\_dc}$  would increase when  $\varphi_{ch}$  augments, which subsequently causes the saturation of the voltage balance and circulating current controllers. Thus, a large reference phase shift during CI might induce the MMC distributed control system instability. Similar results can also be obtained in VPC. Note that  $\varphi_{ch}$  should not be more than 90° in CPC and (90°  $-\varphi_{L}$ ) in VPC, since the voltage control in CI-SM may have a reverse effect according to the capacitor voltage balance diagram in Fig. 15 in [7].

Based on the aforementioned investigation, it is found that VPC is superior to CPC in terms of the capacitor voltage steady-state error while utilizing a proportional controller to

TABLE I

SIMULATION PARAMETERS AND EXPERIMENTAL SETUP

| Parameters                           | Simulation  | Experiments |

|--------------------------------------|-------------|-------------|

| Number of SMs: N                     | 20 per arm  | 4 per arm   |

| DC-link voltage: $U_{dc}$            | 2000 V      | 160 V       |

| Modulation index: m                  | 0.7         | 0.85        |

| Arm inductance: $L_{arm}$            | 20 mH       | 5 mH        |

| SM capacitance: $C_{\text{SM}}$      | 3300 μF     | 940 μF      |

| Carrier frequency: $f_c$             | 500 Hz      | 2 kHz       |

| Load resistance: $R_l$               | $50 \Omega$ | 12 Ω        |

| Load inductor: $L_l$                 | 10 mH       | 0 / 20 mH   |

| Allowable $U_{\rm C}$ deviation rate | 50%         | 50%         |

Fig. 6. A down-scaled laboratory prototype of MMC.

regulate the CI-SM capacitor voltage. However, CPC possesses a better capacitor voltage balancing ability than that of VPC when  $\varphi_L$  is not zero. The preferred reference phase-change range is dependent of  $\varphi_L$ . Hence, the operation mode should be selected considering all the above aspects.

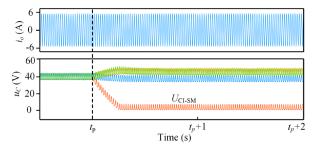

#### C. Protection stage

If CI lasts continuously for a period of  $t_p$ , the network disconnection is confirmed by both the central and local controllers and the protection for the CI-SM is activated. During the protection stage, the CI-SM capacitor voltage reference would be set to zero and  $U_{\text{CISM}}$  would drop to zero accordingly. The central controller would cut the CI-SM off and operate with the remaining SMs as discussed in [4, 22].

The overall procedure of the proposed resilient operation of the MMC encountering CI is illustrated in Fig. 5. The MMC with single SM communication failure is investigated in this section. It is possible that more than one SM in MMC occur CI problem. The proposed resilient operation method can be extended to the MMC with more than one CI-SM.

#### V. SIMULATION AND EXPERIMENTAL VERIFICATION

The theoretical analysis was validated by both simulation and experimental results. The specifications of the simulated system and the experimental setup are shown in TABLE I.

#### A. Simulation Results

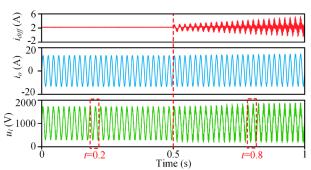

The simulation system with 20 SMs per arm was built to verify the proposed model with CI in Section III. Fig. 7 shows the waveforms of the MMC when CI occurs at 0.5 s with

Fig. 7. Simulated waveforms of the MMC when CI happens at t=0.5 s with  $n_{\text{CISM}}$  = 0.6.

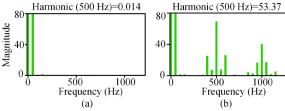

Fig. 8. Harmonic spectra of lower arm voltage  $u_l$  with  $n_{CISM} = 0.6$  at: (a) t = 0.2 s; (b) t = 0.8 s.

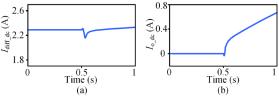

Fig. 9. Current during CI fault: (a) dc component in  $i_{\text{diff}}$ , (b) dc component in

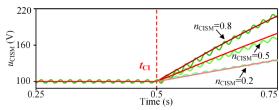

Fig. 10. Simulated CI-SM capacitor voltage when CI happens at t=0.5 s with different duty ratios.

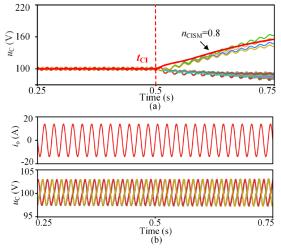

Fig. 11. Simulated waveforms of MMC when CI happens at *t*=1 s: (a) without resilient operation method; (b) with proposed resilient operation method.

$n_{\text{CISM}}$ =0.6. No resilient operation is applied to the CI-SM. It can

be observed that the differential current is drastically deteriorated due to the CI. While the fundamental frequency component in the output current is not severely affected. Also, the output voltage of the lower arm containing the CI-SM is distorted after CI ( $t_{\text{CI}}$ =0.5 s). The harmonic spectrums of the lower arm voltage at t=0.2 s and 0.8 s are depicted in Fig. 8(a) and (b), respectively. The harmonics around the carrier frequency (500 Hz) are largely introduced into the lower arm voltage, which coincides with the study of  $u_l$  in equations (7)-(8).

In Fig. 9, the dc current in  $i_{\rm diff}$  almost remains the same before and after CI. However, the dc component in  $i_{\rm o}$  keeps rising since  $t_{\rm CI}$ , which induces a non-negligible dc disturbance in the CI-SM capacitor current as given in (16).  $U_{\rm CISM}$  would be increased by the CI-SM dc current and eventually exceed the critical capacitor voltage. The CI-SM capacitor voltages with different  $n_{\rm CISM}$  are shown in Fig. 10. It can be observed that  $U_{\rm CISM}$  quickly ascends after CI. To verify the accuracy of the mathematical model,  $U_{\rm CISM}$  was calculated based on (17). The calculated  $U_{\rm CISM}$  was depicted as the red curves in Fig. 10. The figures

show that the simulation results of  $U_{\text{CISM}}$  have sufficient accordance with the calculated values under different conditions.

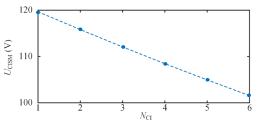

The  $U_{\text{CISM}}$  calculation and the proposed resilient operation for a 20-SM MMC with 4 CI-SMs in the lower arm is investigated by simulation as well. Fig. 11 shows that the capacitor voltage and output current are scarcely impacted by the multiple CI faults with the help of the proposed resilient operation method. Comparing  $U_{\text{CISM}}$  in Fig. 10 with that in Fig. 11, it can be found that the capacitor voltage deviation is decreased. The diagram showing  $U_{\text{CISM}}$ , which is calculated based on (17) and parameters in TABLE I, with different  $N_{\text{CI}}$  at t=0.58 s is depicted in Fig. 12. The insertion index of the CI-SMs, i.e.,  $n_{\text{CISM}}$ , is selected as 0.8 during the calculation. It can be seen that  $U_{\text{CISM}}$  deviation is mitigated with the increase of  $N_{\text{CI}}$ , and a larger  $t_p$  is sufficient to ensure the MMC safe operation in this case.

#### B. Experimental Results

In order to verify the validity of the proposed resilient operation method of the MMC, a single-phase MMC prototype with four SMs per arm was configured as shown in Fig. 6. Detailed parameters are specified in TABLE I.

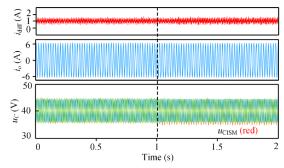

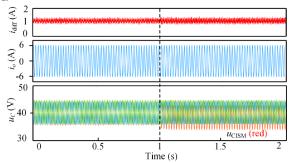

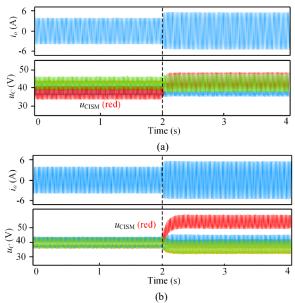

#### 1) Sustention stage of resilient operation

The effectiveness of utilizing the stored sinusoid signal and local voltage balance controller to maintain the capacitor volt-ages was verified in both current and voltage phase conditions by adopting different power factors (PFs) (1 and 0.874). The MMC system with a unity PF was firstly investigated. Fig. 13 and Fig. 14 present the output waveforms of the MMC operating in voltage and current phase conditions respectively. It can be seen that the MMC output current operated normally and the individual capacitor voltages remained stable after the CI occurred. As depicted in Fig. 13 and Fig. 14 the CI-SM capacitor voltage deviation is negligible, which agrees well with the analysis in (26) and (27).

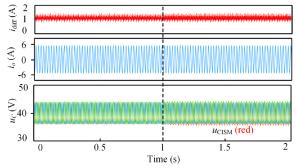

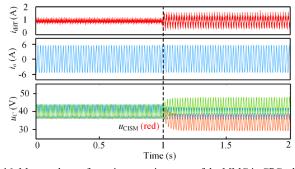

Fig. 15 and Fig. 16 represent the current and voltage wave-

Fig. 12. Capacitor voltage of CI-SM at t=0.58 s with different  $N_{\rm CI}$ .

Fig. 13. Measured waveforms in sustention stage of the MMC in VPC when  $\cos(\varphi_L) = 1$ .

Fig. 14. Measured waveforms in sustention stage of the MMC in CPC when  $\cos(\varphi_L) = 1$ .

Fig. 15. Measured waveforms in sustention stage of the MMC in VPC when  $\cos(\varphi_L) = 0.874$ .

Fig. 16. Measured waveforms in sustention stage of the MMC in CPC when  $\cos(\varphi_L) = 0.874$ .

Fig. 17. Measured waveforms of the MMC when the output current amplitude has a step change: (a) CPC; (b) VPC.

Fig. 18. Measured waveforms of the MMC when  $\varphi_{ch}$  changes from  $0^{\circ}$  to  $60^{\circ}$  and then to  $90^{\circ}$ : (a) circulating current and output current in VPC; (b) capacitor voltages in VPC and CPC operation.

Fig. 19. Measured waveforms while controlling the CI-SM capacitor voltage to zero in the protection stage when  $t > t_p$ .

forms of the MMC when PF was 0.874. The MMC output was connected to an R-L load in this set of experiments. No capacitor voltages diverging was found in VPC because (26) is satisfied regardless of the PF. In CPC, the output of the MMC remained stable, but the  $U_{\text{CISM}}$  in CPC showed an apparently

steady-state error compared with that in Fig. 14. This is explained by that the deviation of  $U_{\rm CISM}$  is positively related to the PF angle in CPC according to (30). With the help of the capacitor voltage control, the sum of the capacitor voltages in one arm remains approximately the same before and after CI [11]. Thus, in Fig. 16, the capacitor voltages of normal SMs in the lower arm increased while the  $U_{\rm CISM}$  decreased after CI, so that the arm voltage is almost unaltered.

#### 2) Reference change during sustention stage

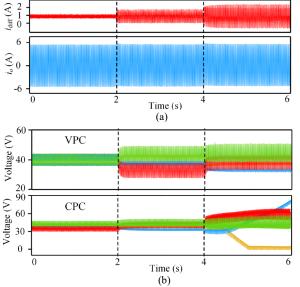

In the following set of experiments, the output reference variation during the sustention stage was studied. A resistor and inductor serial load is utilized for the sake of a 0.874 power factor. Both amplitude change and phase change scenarios were discussed to evaluate the MMC system performance.

Fig. 17 shows the capacitor voltages and the output current of the MMC when the modulation index changed from 0.6 to 0.85. According to the waveforms,  $U_{\text{CISM}}$  in both phase conditions climbed to a value higher than the reference value ( $U_{\text{dc}}/N$ ). The positive capacitor voltage deviation introduced a positive output in the voltage balance controller [7, 29]. Therefore,  $M_{\text{CISM}}$  is accordingly increased and the output active power of the CI-SM is improved to fulfill the MMC output ascent.

Fig. 18 (a) presents the circulating current and the output current in VPC, while Fig. 18 (b) presents the individual capacitor voltages in both VPC and CPC. The reference phase-change  $\varphi_{ch}$  was zero from 0 s to 2 s. When t=2 s,  $\varphi_{ch}$  was step-changed to  $60^{\circ}$  while at t=4 s it was subsequently changed to  $90^{\circ}$ . According to the analysis in section IV, phase change during the sustention stage would introduce an additional ac-component in  $i_{cir}$  and a dc-component in  $i_{o}$ , which was clearly verified as shown in Fig. 18 (a). It can be seen in Fig. 18 (b) that the capacitor voltages remained stable when  $\varphi_{ch}=60^{\circ}$ . However, when  $\varphi_{ch}$  stepped to  $90^{\circ}$ , the MMC system in CPC quickly became unstable. This is because the voltage balancing capability for CI-SM in CPC is deprived when  $\varphi_{ch}=90^{\circ}$ . The capacitor voltages in VPC remain stable since the critical  $\varphi_{ch}$  in VPC is  $(90^{\circ} - \varphi_{L})$  as in Section IV.B, where  $\varphi_{L} \leq 0$ .

#### 3) Protection stage of the resilient operation

After the period of  $t_p$ , the network disconnection was confirmed by the CI-SM local controller. The CI-SM capacitor voltage reference was then set to zero and  $U_{\text{CISM}}$  gradually drops to zero as given in Fig. 19. Afterward, the CI-SM could be cut off and the MMC was able to operate normally with the remaining SMs [22].

#### VI. CONCLUSION

In this paper, the influence of CI to the MMC distributed control system is analyzed. It shows that a CI might lead to a high increase of the CI-SM capacitor voltage and give instability of the system. According to the protection period  $t_{\rm p}$  associated with the voltage increase rate and the capacitor voltage safe margin, the CI faults are classified as temporary and permanent ones in the fault analysis. A resilient operation strategy having sustention and protection stages that correspond to the temporary and permanent CI faults, respectively, is proposed to ride-through a CI fault. In the sustention stage, pre-stored phase angles are utilized to generate the sinusoidal modulation signal

for the CI-SM in order to maintain the capacitor voltage of the CI-SM. If the network cannot recover within the pre-defined time period  $t_p$ , the protection stage will be triggered to discharge the capacitor and then bypass the CI-SM. The MMC operates with remaining SMs. The effectiveness of the proposed resilient operation strategy is experimentally verified on a prototype in the laboratory. The results show that, with the resilient operation strategy, the MMC distributed control system is immune to CI faults and can operate with higher reliability not only in the steady-state but also during the transient process. The MMC can operate normally during the CI fault without frequently triggering the protection actions and bypassing or replacing the faulty SMs.

#### REFERENCES

- [1] A. Nami, J. Liang, F. Dijkhuizen, and G. D. Demetriades, "Modular Multilevel Converters for HVDC Applications: Review on Converter Cells and Functionalities," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 18-36, Jan. 2015.

- [2] S. Yang, J. Fang, Y. Tang, H. Qiu, C. Dong, and P. Wang, "Modular Multilevel Converter Synthetic Inertia-Based Frequency Support for Medium-Voltage Microgrids," *IEEE Trans. Ind. Electron.*, vol. 66, no. 11, pp. 8992-9002, Nov. 2019.

- [3] M. Hagiwara, K. Nishimura, and H. Akagi, "A Medium-Voltage Motor Drive With a Modular Multilevel PWM Inverter," *IEEE Trans. Power Electron.*, vol. 25, no. 7, pp. 1786-1799, July. 2010.

- [4] P. Tu, S. Yang, and P. Wang, "Reliability- and Cost-Based Redundancy Design for Modular Multilevel Converter," *IEEE Trans. Ind. Electron.*, vol. 66, no. 3, pp. 2333-2342, March. 2019.

- [5] F. Deng, Q. Wang, D. Liu, Y. Wang, M. Cheng, and Z. Chen, "Reference Submodule Based Capacitor Monitoring Strategy for Modular Multilevel Converters," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4711-4721, May. 2019.

- [6] J. Huang, B. Yang, F. Guo, Z. Wang, X. Tong, A. Zhang, and J. Xiao, "Priority Sorting Approach for Modular Multilevel Converter Based on Simplified Model Predictive Control," *IEEE Trans. Ind. Electron.*, vol. 65, no. 6, pp. 4819-4830, June. 2018.

- [7] S. Yang, Y. Tang, and P. Wang, "Distributed Control for a Modular Multilevel Converter," *IEEE Trans. Power Electron.*, vol. 33, no. 7, pp. 5578-5591, July. 2018.

- [8] W. Yao, J. Liu, and Z. Lu, "Distributed Control for the Modular Multilevel Matrix Converter," *IEEE Trans. Power Electron.*, vol. 34, no. 4, pp. 3775-3788, April. 2019.

- [9] P. D. Burlacu, L. Mathe, and R. Teodorescu, "Synchronization of the distributed PWM carrier waves for modular multilevel converters," in 2014 International Conference on Optimization of Electrical and Electronic Equipment (OPTIM), Bran, 2014, pp. 553-559.

- [10] H. Wang, S. Yang, H. Chen, X. Feng, and F. Blaabjerg, "Synchronization for an MMC Distributed Control System Considering Disturbances Introduced by Sub-module Asynchrony," *IEEE Trans. Power Electron.*, vol. 35, no. 12, pp. 12834-12845, Dec. 2020.

- [11] S. Yang, S. Liu, J. C. Huang, H. Su, and H. Y. Wang, "Control Conflict Suppressing and Stability Improving for an MMC Distributed Control System," *IEEE Trans. Power Electron.*, vol. 35, no. 12, pp. 13735-13747, Dec. 2020.

- [12] L. Mathe, P. D. Burlacu, and R. Teodorescu, "Control of a Modular Multilevel Converter With Reduced Internal Data Exchange," *IEEE Trans. Ind. Informat.*, vol. 13, no. 1, pp. 248-257, Feb. 2017.

- [13] H. Geng, S. Li, C. Zhang, G. Yang, L. Dong, and B. Nahid-Mobarakeh, "Hybrid Communication Topology and Protocol for Distributed-Controlled Cascaded H-Bridge Multilevel STATCOM," *IEEE Trans. Ind. Appl.*, vol. 53, no. 1, pp. 576-584, Jan.-Feb. 2017.

- [14] S. Huang, R. Teodorescu, and L. Mathe, "Analysis of communication based distributed control of MMC for HVDC," in 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, 2013, pp. 1-10

- [15] T. P. Corrêa, L. Almeida, and F. J. Rodriguez, "Communication aspects in the distributed control architecture of a modular multilevel converter," in 2018 IEEE International Conference on Industrial Technology (ICIT), Lyon, 2018, pp. 640-645.

- [16] D. Xing, J. Su, D. Hu, S. Sun, Y. Chen, X. Wang, J. Zhang, W. Yao, and J. Wu, "Solution to reduce voltage stress of sub-module in LCC-MMC transmission system at the condition of communication fault," *The Journal of Engineering*, vol. 2019, no. 16, pp. 1873-1876. 2019.

- [17] C. L. Toh, and L. E. Norum, "Implementation of high speed control network with fail-safe control and communication cable redundancy in modular multilevel converter," in 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, 2013, pp. 1-10.

- [18] A. Azidehak, R. Agarwal, N. Yousefpoor, A. G. Dean, and S. Bhattacharya, "Resilient two dimensional redundancy based fault-tolerant controller array for modular multi-level converters," in 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 2017, pp. 722-729.

- [19] B. Li, Y. Zhang, R. Yang, R. Xu, D. Xu, and W. Wang, "Seamless Transition Control for Modular Multilevel Converters When Inserting a Cold-Reserve Redundant Submodule," *IEEE Trans. Power Electron.*, vol. 30, no. 8, pp. 4052-4057, Aug. 2015.

- [20] K. Ilves, A. Antonopoulos, S. Norrga, and H. P. Nee, "Steady-State Analysis of Interaction Between Harmonic Components of Arm and Line Quantities of Modular Multilevel Converters," *IEEE Trans. Power Electron.*, vol. 27, no. 1, pp. 57 - 68, Jan. 2012.

- [21] S. Yang, P. Wang, and Y. Tang, "Feedback Linearization-Based Current Control Strategy for Modular Multilevel Converters," *IEEE Trans. Power Electron.*, vol. 33, no. 1, pp. 161-174, Jan. 2018.

- [22] S. Yang, Y. Tang, and P. Wang, "Seamless Fault Tolerant Operation of a Modular Multilevel Converter with Switch Open-circuit Fault Diagnosis in a Distributed Control Architecture," *IEEE Trans. Power Electron.*, vol. 33, no. 8, pp. 7058-7070, Aug. 2018.

- [23] K. Ilves, L. Harnefors, S. Norrga, and H.-P. Nee, "Analysis and Operation of Modular Multilevel Converters With Phase-Shifted Carrier PWM," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 268-283, Jan. 2015.

- [24] S. Li, X. Wang, Z. Yao, T. Li, and Z. Peng, "Circulating Current Suppressing Strategy for MMC-HVDC Based on Nonideal Proportional Resonant Controllers Under Unbalanced Grid Conditions," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 387-397, Jan. 2015.

- [25] B. Li, R. Yang, D. Xu, G. Wang, W. Wang, and D. Xu, "Analysis of the Phase-Shifted Carrier Modulation for Modular Multilevel Converters," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 297-310, Jan. 2015.

- [26] S. Yang, H. Wang, H. Chen, W. Song, and T. Wang, "Probability-Based Modeling and Analysis for PS-PWM in an MMC Distributed Control System With Sub-Module Asynchrony," *IEEE Trans. Power Electron.*, vol. 34, no. 11, pp. 10392-10397, Nov. 2019.

- [27] D. G. Holmes, and A. L. Thomas, "Modulation of One Inverter Phase Leg," Pulse Width Modulation for Power Converters: Principles and Practice, pp. 95-153: IEEE, 2003.

- [28] M. Zhang, L. Huang, W. Yao, and Z. Lu, "Circulating Harmonic Current Elimination of a CPS-PWM-Based Modular Multilevel Converter With a Plug-In Repetitive Controller," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 2083-2097, April. 2014.

- [29] M. Hagiwara, and H. Akagi, "Control and Experiment of Pulsewidth-Modulated Modular Multilevel Converters," *IEEE Trans. Power Electron.*, vol. 24, no. 7, pp. 1737-1746, July. 2009.

Shunfeng Yang (S'15-M'18-SM'20) received the B.Eng. and M.Sc. degrees in Electrical Engineering from Southwest Jiaotong University, Chengdu, China, in 2007 and 2010, respectively, and the Ph.D. degree in power engineering from Nanyang Technological University, Singapore, in 2018. He was with Temasek Polytechnic, Singapore Technologies Kinetics Ltd, and Rolls-Royce@NTU Corporate Lab, Singapore, from 2009 to 2017. Currently, he is an Associate Professor in Southwest Jiaotong University, Chengdu, China.

Dr. Yang received one IEEE Prize Paper Award and one Highlighted Paper on IEEE Trans. Power Electron. 2018 July Issue. His research interests include power electronics, multi-level converters, and converter control techniques.

Haiyu Chen was born in Beijing, China, in 1997. He received the B.S. degree in electrical engineering in 2019 from Southwest Jiaotong University, Chengdu, China. He is currently working toward the Ph.D. degree at Xi'an Jiaotong University, Xi'an, China.

His research interests include power electronics and multilevel converter.

Electrical and Electronic Engineering, Nanyang Technological University, Singapore. His current research interests include power system planning and operation, renewable energy planning, solar/electricity conversion system, and power system reliability analysis.

Dr. Wang is currently an Associate Editor or Guest Editor-in-Chief for the IEEE Transactions on Smart Grid, IEEE Transactions on Power Delivery, Journal of Modern Power Systems and Clean Energy, CSEE Journal of Power and Energy Systems, and so on.

**Pengfei Sun** received the B.S. and M.S. degrees in electrical engineering from Southwest Jiaotong University, Chengdu, China, in 2009 and 2012, respectively, and the Ph.D. degree in automation from the Ecole Centrale de Lille, Lille, France, in 2015.

He has been a Lecturer with Southwest Jiaotong University since 2016. His current research interests include train optimal control theory and automatic train operation applications.

Haiyu Wang (S'19) received the B.Eng. degree in Electrical Engineering from the Anhui University of Technology, in 2018, where he is currently working toward the Ph.D. degree in electrical engineering from Southwest Jiaotong University, Chengdu, China.

His current research interests include the power electronics and multi-level converters.

Frede Blaabjerg (S'86–M'88–SM'97–F'03) was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. From 1988 to 1992, he got the PhD degree in Electrical Engineering at Aalborg University in 1995. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor of power electronics and drives in 1998. From 2017 he became a Villum Investigator. He is honoris causa at University Politehnica Timisoara (UPT), Romania and Tallinn Technical University (TTU) in Estonia. His current research interests include power electronics

and its applications such as in wind turbines, PV systems, reliability, harmonics and adjustable speed drives. He has published more than 600 journal papers in the fields of power electronics and its applications. He is the co-author of four monographs and editor of ten books in power electronics and its applications. He has received 32 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award 2014, the Villum Kann Rasmussen Research Award 2014, the Global Energy Prize in 2019 and the 2020 IEEE Edison Medal. He was the Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS from 2006 to 2012. He has been Distinguished Lecturer for the IEEE Power Electronics Society from 2010 to 2011 as well as 2017 to 2018. In 2019-2020 he serves a President of IEEE Power Electronics Society. He is Vice-President of the Danish Academy of Technical Sciences too.

He is nominated in 2014-2019 by Thomson Reuters to be between the most 250 cited researchers in Engineering in the world.

Peng Wang (M'00–SM'11–F'18) received the B.Sc. degree in electronic engineering from Xi'an Jiaotong University, Xi'an, China, in 1978, the M.Sc. degree from Taiyuan University of Technology, Taiyuan, China, in 1987, and the M.Sc. and Ph.D. degrees in electrical engineering from the University of Saskatchewan, Saskatoon, SK, Canada, in 1995 and 1998, respectively.

He is currently a Full Professor with the School of