# **Aalborg Universitet**

# Design for Reliability of SiC-MOSFET-Based 1500-V PV Inverters With Variable Gate Resistance

He, Jinkui; Sangwongwanich, Ariya; Yang, Yongheng; Zhang, Kaichen; lannuzzo, Francesco

Published in:

I E E E Transactions on Industry Applications

DOI (link to publication from Publisher): 10.1109/TIA.2022.3183029

Publication date: 2022

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA): He, J., Sangwongwanich, A., Yang, Y., Zhang, K., & Iannuzzo, F. (2022). Design for Reliability of SiC-MOSFET-Based 1500-V PV Inverters With Variable Gate Resistance. *I E E E Transactions on Industry Applications*, *58*(5), 6485-6495. https://doi.org/10.1109/TIA.2022.3183029

# **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 04, 2025

# Design for Reliability of SiC-MOSFET-Based 1500-V PV Inverters with Variable Gate Resistance

Jinkui He, Member, IEEE, Ariya Sangwongwanich, Member, IEEE, Yongheng Yang, Senior Member, IEEE, Kaichen Zhang, Student Member, IEEE, and Francesco Iannuzzo, Senior Member, IEEE

Abstract—1500-V Photovoltaic (PV) configuration is the standard design in the solar PV industry. Extending the maximum DC voltage from 1000 V to 1500 V can reduce the installation cost of the entire power plant. However, it may affect the reliability of the corresponding 1500-V PV inverters, due to the increased loading stresses, i.e., voltage stress and thermal loading of power devices. In this context, this paper proposes a solution to the reliability enhancement of SiC-MOSFET-based 1500-V PV inverters with variable gate resistance. This solution offers a possibility to adaptively adjust the switching speed to make a compromise between the switching power loss and voltage overshoot during commutation, thus enhancing the reliability. The evaluation results based on the mission profile of a 125-kW 1500-V PV system installed in Denmark indicate that the PV inverter with the proposed design, i.e., variable gate resistance, can improve reliability performance compared to the fixed gate resistance solution while ensuring a safer operating voltage margin.

Index Terms—Photovoltaic (PV) inverters, SiC-MOSFET, gate driver, lifetime, reliability.

### I. INTRODUCTION

More grid-connected PV systems are expected to be installed in the future and they will soon share a major part of the renewable energy generation [1]. Several studies have shown that increasing the DC voltage is an effective way to reduce the installation cost of PV power plants, hence further improving their competitiveness [2]–[5]. Currently, the mainstream DC voltage of large-scale PV plants has been increasing from 600 V or 1000 V to 1500 V, which is the maximum voltage limit in low-voltage grids according to the IEC standards [6]. There have been increasing discussions on higher DC voltages for PV systems to directly integrate into medium-voltage grids [7]. The increased voltage requires careful considerations in the design and control of PV inverters [8]–[10], which are the key to achieve the power conversion efficiently and reliably.

Single-stage energy conversion based on two-level inverter is a typical system configuration of PV systems with lower PV-string voltages, e.g., 1000-V. It offers a cost-effective solution

Manuscript received January 25, 2022; revised April 20, 2022; accepted June 2, 2022. This work was supported under the research project – Reliable Power Electronic based Power Systems (REPEPS) by The Velux Foundations under Award No.: 00016591, and also in part by the National Natural Science Foundation of China under Grant 52107212. (Corresponding author: Yongheng Yang.)

- J. He is with the College of New Energy, China University of Petroleum (East China), Qingdao 266580, China, and he was with the Department of AAU Energy, Aalborg 9220, Denmark (e-mail: hejk@upc.edu.cn).

- A. Sangwongwanich, K. Zhang, and F. Iannuzzo are with the Department of AAU Energy, Aalborg University, Aalborg 9220, Denmark (e-mail: ars@energy.aau.dk; kzh@energy.aau.dk).

- Y. Yang is with the College of Electrical Engineering, Zhejiang University, Hangzhou 310027, China (e-mail: yang\_yh@zju.edu.cn).

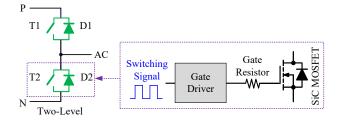

Fig. 1. Two-level inverter topology based on SiC power devices.

due to the reduced weight, size, and cost [3]. Nevertheless, the PV inverter based on two-level topology may not be a suitable candidate to accommodate the 1500-V technology. This is mainly due to the high power losses and increased filtering efforts as well as the voltage de-rating of the 1700-V IGBT power module to avoid an increase in the failure rate due to cosmic rays [11], [12]. On the other hand, the advances in power semiconductor technologies bring more opportunities to improve the performance of PV systems. Silicon-Carbide (SiC) devices offer lower power losses, faster switching capability, higher voltage blocking capability, and lower failure rates caused by cosmic radiation [13]–[15]. Thus, the use of the 1700-V SiC power devices, as illustrated in Fig. 1, can potentially enable the two-level inverter to be widely adapted in 1500-V PV systems. The corresponding SiC devices/modules and inverters for 1500-V PV applications are already available on the market [16], [17].

However, for 1500-V PV applications, the two-level topology with 1700-V SiC modules still has a limited voltage blocking margin, especially considering the voltage overshoot during the switching transients of a SiC MOSFET. This is primarily due to its high switching speed (i.e., large di/dt) and the stray inductance in the commutation loops, which could be higher than 100 nH for two-level inverter layouts [18]. During the cold days in winter, the voltage at the Maximum Power Point (MPP) of PV strings can reach 80-85% of the opencircuit voltage (i.e., 1500 V), which is approximately 1300 V or even higher [12] depending on the mission profiles of the PV system site, i.e., solar irradiance and ambient temperature. In this case, only a 400-V voltage overshoot is permissible to keep the power devices within their safe operating area in terms of voltage ratings.

To address this challenge, the switching speed of SiC MOSFETs should be reduced, e.g., by using a large gate resistor in practice. However, doing so will affect the semi-conductor efficiency and reliability, as discussed in [19]. It is preferable to limit the voltage overshoot, while minimizing the switching losses. This can be achieved by using active

TABLE I PV INVERTER MAIN SPECIFICATIONS.

| Nominal power $P_{\text{nom}}$              | 125 kW               |

|---------------------------------------------|----------------------|

| Power factor $\cos(\varphi)$                | 1.0                  |

| Grid line-to-line RMS voltage $V_{\rm LL}$  | 600 V                |

| Grid frequency $f_{\rm g}$                  | 50 Hz                |

| Switching frequency $f_{sw}$                | 8 kHz                |

| Heatsink thermal impedance $R_{ m th(s-a)}$ | 0.088 K/W per module |

gate driving technologies [18], [20], [21], which can adjust the gate resistance dynamically during every single switching transient. Notably, due to the fast switching speed of SiC MOSFETs, the implementation of active gate drivers is, however, challenging, which limits its practical applications. For the considered PV inverter in Fig. 1, a variable-resistance gate driver thus proposed, which adjusts the gate resistance with slower dynamic following the mission profiles (i.e., the PV voltage variations) rather than every switching transient. Accordingly, the proposed method is easier to implement in comparison with the state-of-the-art solutions, being a costeffective way to improve the reliability performance of PV systems. In light of the above, the impact of switching speed on the reliability of SiC-MOSFET-based 1500-V PV inverters is first analyzed in this paper. The analysis is carried out through a case study on a 125-kW two-level PV inverter employing 1700-V SiC power modules [22]. Subsequently, a variable-resistance gate driver is proposed and designed for the 1500-V two-level PV inverter system. The results indicate that, compared to the fixed-resistance gate driver, the lifetime of the SiC MOSFETs within the PV inverter can be improved by over 70% when using the proposed variable-resistance design.

The rest of this paper is organized as follows. In Section II, the system description is provided, which includes the specifications of the system and its operating conditions (i.e., the mission profiles). Then, the impact of the switching speed on the inverter loading stress is presented in Section III, where a variable-resistance gate driver is proposed for reducing the thermal stress, and thus, enhancing the reliability. A comparative reliability assessment of the PV inverter is carried out considering two scenarios (i.e., with the variable-resistance and the fixed-resistance gate drivers), which is presented in Section IV. Finally, concluding remarks are given in Section V.

# II. SYSTEM DESCRIPTION

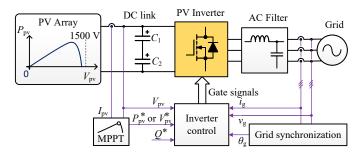

The general configuration of the considered 1500-V PV system is shown in Fig. 2. Here, a single-stage configuration is adopted, where a 125-kW three-phase two-level inverter based on three 1700-V SiC MOSFET power modules is employed as the power interfacing converter between the PV array and the AC grid. The specifications of the PV inverter and the adopted SiC module are given in Tables I and II, respectively. The heatsink is designed to limit the junction temperature to 125 °C at the rated operation (see Table I) with the ambient temperature  $T_{\rm a}$  being 50 °C.

Fig. 2. System configuration and the basic control structure of the 1500-V PV system based on two-level topology and SiC power devices:  $P_{\rm pv}, V_{\rm pv}$ , and  $I_{\rm pv}$  represent the output power, voltage, and current, respectively;  $P_{\rm pv}^*, Q^*$ , and  $V_{\rm pv}^*$  denote the control reference of the PV system, i.e., the active power, the reactive power, and the DC-link voltage, respectively;  $i_{\rm g}$ ,  $v_{\rm g}$ , and  $\theta_{\rm g}$  are the grid current, the grid voltage, and the phase angle of the grid voltage, respectively.

| Voltage rating                   | 1700 V               |

|----------------------------------|----------------------|

| Current rating                   | 250 A                |

| Minimum and maximum gate voltage | -6 V, 22 V           |

| Junction temperature             | -40 to 150 °C        |

| Internal gate resistance         | $1.4~\Omega$         |

| Stray inductance                 | 13 nH                |

| Diode type                       | SiC-SBD <sup>1</sup> |

<sup>&</sup>lt;sup>1</sup>Schottky barrier diode.

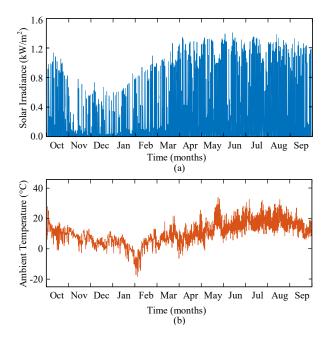

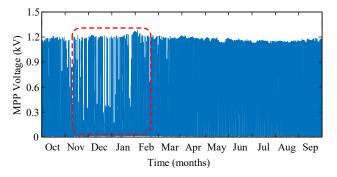

In addition, in order to evaluate the inverter lifetime under real operating conditions, a one-year mission profile recorded in Denmark with a sampling rate of 1 min/sample is used in this paper [24], which is shown in Fig. 3. The PV array configuration and the specifications of the adopted PV panel are summarized in Table III, where the PV array size is designed to match the inverter ratings under the Denmark mission profile.

As shown in Fig. 2, a Maximum Power Point Tracking (MPPT) operation is considered to obtain the operating conditions (e.g., power and DC-link voltage) of the PV inverter. This is normally achieved by the control of the PV inverter, which operates at the MPP of the PV array and then delivers the maximum available PV power to the AC grid. With these operational conditions, the impact of variable-resistance gate driver on the inverter reliability is analyzed in the following sections.

#### III. PROPOSED VARIABLE GATE-RESISTANCE DESIGN

The junction temperature of power devices rises above the ambient temperature when power losses, i.e., conduction and switching losses, are generated during operation, which is the origin of thermal-related wear-out failure. Generally, the power losses not only depend on the operating conditions (e.g., voltage, current, and switching frequency) but also the gate-driving parameters (e.g., the external gate resistance) [26]. It is expected to reduce the external gate resistance and increase the gate current in order to achieve high speed switching (less switching losses). However, accelerating the switching

Fig. 3. Yearly mission profiles for the 1500-V PV inverter installed in Denmark: (a) solar irradiance and (b) ambient temperature.

TABLE III

PV ARRAY CONFIGURATION AND SPECIFICATIONS [25].

| PV array configuration                  |                               |  |  |  |

|-----------------------------------------|-------------------------------|--|--|--|

| PV panel type                           | JKM380M-72-V                  |  |  |  |

| Number in series / parallel             | 28 / 12                       |  |  |  |

| PV panel specifications <sup>1</sup>    |                               |  |  |  |

| Maximum power $P_{\text{max}}$          | 380 W                         |  |  |  |

| Maximum power voltage $V_{\mathrm{mp}}$ | 40.5 V                        |  |  |  |

| Maximum power current $I_{mp}$          | 9.39 A                        |  |  |  |

| Open-circuit voltage $V_{ m oc}$        | 48.9 V                        |  |  |  |

| Short-circuit current $I_{sc}$          | 9.75 A                        |  |  |  |

| Temperature coefficient of $V_{ m oc}$  | -0.37 %/°C                    |  |  |  |

| Temperature coefficient of $I_{\rm sc}$ | $0.048~\%/^{\circ}\mathrm{C}$ |  |  |  |

<sup>&</sup>lt;sup>1</sup>Under the Standard Test Condition (STC).

would increase the voltage overshoot, which may destroy the devices and cause EMI issues. Consequently, an appropriate gate resistance design requires careful consideration on the tradeoff between power losses and voltage overshoot.

#### A. Gate Resistance Impact on Power Losses

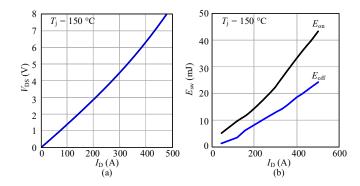

In this section, the impact of the SiC MOSFET switching speed on the PV inverter loading (power losses) is analyzed. Power losses, which are composed of conduction and switching losses, induce the thermal loading of the power devices. The forward voltage drop  $V_{\rm DS}$  during conduction and the turn-on/-off energy  $E_{\rm sw}$ , i.e.,  $E_{\rm on}$  and  $E_{\rm off}$ , during switching, respectively, contribute to the power losses. Fig. 4 shows the variation of the voltage drop  $V_{\rm DS}$  and switching energy  $E_{\rm sw}$  of the MOSFET in the selected SiC MOSFET module under different drain currents  $I_{\rm D}$ . In addition, the switching behaviors of both the MOSFET and the diode within the

Fig. 4. Voltage drop  $V_{\rm DS}$  and switching energy  $E_{\rm sw}$  of the MOSFET in the selected SiC module under different drain currents  $I_{\rm D}$ , when the junction temperature  $T_{\rm j}$  is 150 °C ( $E_{\rm on}$  and  $E_{\rm off}$  represent the switching energy during the turn-on and -off transients): (a) voltage drop and (b) switching energy.

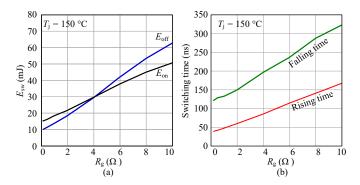

Fig. 5. Switching energy  $E_{\rm sw}$  and switching time of the MOSFET in the selected SiC module under various gate resistances  $R_{\rm g}$ , when the junction temperature  $T_{\rm i}$  is 150 °C: (a) switching energy and (b) switching time.

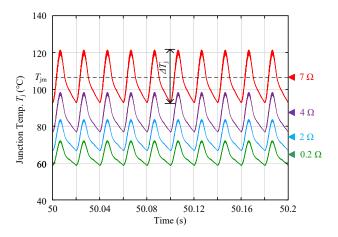

SiC MOSFET module are also affected by the gate resistor. Thus, the value of the gate resistance should be properly designed. The relationship between the gate resistor, switching speed, and switching energy is illustrated in Fig. 5, where a smaller gate resistance (i.e., a fast switching speed) results in lower switching energy losses. Nevertheless, for 1500-V PV applications, the two-level topology with 1700-V devices has a limited voltage blocking margin. As a consequence, its switching speed (dv/dt and di/dt) should be slowed down by using a larger resistor to reduce the switching overshoot due to the stray inductance in the commutation loops. This, however, negatively affects the thermal performance of the PV inverter because of the increased switching losses, as shown in Fig. 6, where the thermal loading of the SiC MOSFET rises drastically with the increase of the gate resistance.

#### B. Gate Resistance Impact on Voltage Overshoot

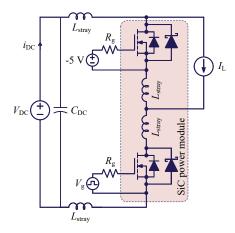

To further explain the switching voltage overshoot issue, a detailed switching overvoltage analysis is performed in simulations considering a total stray inductance of 100 nH within the commutation loop. Fig. 7 depicts the schematic representation of the simulation model with all the stray inductances. Since the SiC MOSFET module has a junction barrier Schottky diode instead of using its own body diode, the reverse recovery problems such as current and voltage overshoots during turnon transients can be effectively suppressed [27]. Thus, only

Fig. 6. Thermal loading of the SiC MOSFETs in the considered inverter under the rated operation condition (see Table I) and various gate resistance  $R_{\rm g}$ , where  $T_{\rm jm}$  and  $\Delta T_{\rm j}$  are the mean value and the cycle amplitude of the junction temperature, respectively.

Fig. 7. Schematic representation of the simulation model for the SiC MOSFET module with all the stray inductances:  $L_{\rm stray}$  – stray inductance;  $i_{\rm DC}$  – DC-link current;  $I_{\rm L}$  – load current;  $V_{\rm DC}$  – DC-link voltage;  $R_{\rm g}$  – gate resistor.

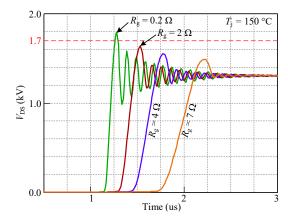

the turn-off transients are analyzed. Fig. 8 presents the turn-off transients of the lower MOSFET with different gate resistance values. In the simulation, the DC-link voltage is kept at 1300 V, and the drain current is 250 A with the junction temperature of  $T_{\rm j}=150$  °C. It can be observed in Fig. 8 that using a small gate resistance value, i.e.,  $R_{\rm g}=0.2~\Omega$  (the minimum permissible external gate resistor in the datasheet), results in large voltage overshoots even exceeding the device voltage rating (i.e., 1700 V). When using higher value of  $R_{\rm g}$ , the voltage overshoots will be reduced. However, the voltage-changing slope becomes smaller, which will result in higher switching losses as aforementioned.

#### C. Variable Gate Resistance Design

To achieve a high reliability performance, it is expected to attain fast switching transients to reduce switching loss while ensuring a safe voltage overshoot margin. A variable-resistance gate driver, which can dynamically change the gate resistance following the mission profiles, can be a cost-effective solution in this case. Fig. 9 presents the MPP voltage

Fig. 8. Turn-off transients of the lower MOSFET in the selected SiC module (see Fig. 7) under various gate resistances  $R_{\rm g}$ , when the junction temperature  $T_{\rm j}$  is 150 °C.

Fig. 9. MPP voltage profile under the one-year Denmark mission profile.

profile during the one-year Denmark mission profile (see Fig. 3). It should be pointed out that the MPP voltage varies from 1000 V to 1200 V during the yearly operation. However, the MPP voltage can reach 1300 V during the cold winter days (the highlighted area in Fig. 9). In addition, considering low-voltage ride-through operations, the PV inverter may need to provide reactive power with the DC-link voltage being the open-circuit voltage of the PV array, which could be as high as 1500 V. Correspondingly, the variable gate resistance is designed in the following considering three available gate resistors  $R_{\rm g}$ .

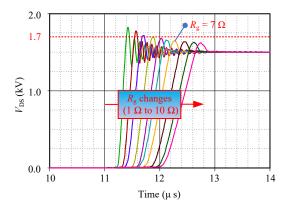

1) Maximum  $R_g$ : The maximum applied gate resistance considers the most severe operating condition in terms of voltage overshoot, i.e., reactive power support at 1500-V DC-link [28], [29]. Fig. 10 presents the turn-off transients of the lower MOSFET with various gate resistance values, where the device current is set to 188 A (1.1 times of the inverter's rated current) and the DC-link voltage is 1500 V. It can be observed from Fig. 10 that small gate resistance, e.g.,  $< 5 \Omega$ , should not be adopted; otherwise, the voltage overshoot would exceed the device rating. Consequently, the maximum gate resistance is determined as  $7 \Omega$  to limit the voltage overshoot and avoid significant switching losses.

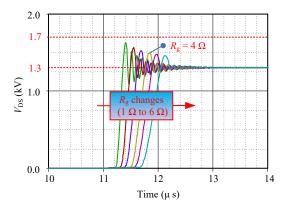

2) Medium  $R_g$ : Regarding the medium gate resistance, the most stressed case during normal operating conditions is considered, i.e., maximum output current under the highest MPP voltage (e.g., 1300 V). Fig. 11 presents how the gate resistance affects the voltage overshoot in such a case, where

Fig. 10. Turn-off transients of the lower MOSFET in the selected SiC module (see Fig. 7) under various gate resistances  $R_{\rm g}$ , when the DC-link voltage is 1500 V and the load current is 188 A.

Fig. 11. Turn-off transients of the lower MOSFET in the selected SiC module (see Fig. 7) under various gate resistances  $R_{\rm g}$ , when the DC-link voltage is 1300 V and the load current is 188 A.

several gate resistance could be adopted depending on the expected blocking voltage margin. The medium gate resistance value is considered to be 4  $\Omega$  for ensuring a 200-V voltage margin.

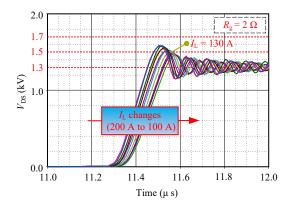

3) Minimum  $R_g$ : As for the minimum gate resistance, a moderate value should be considered to avoid the high switching ringing [19]. For the case study, the minimum gate resistance value is set to  $2 \Omega$ .

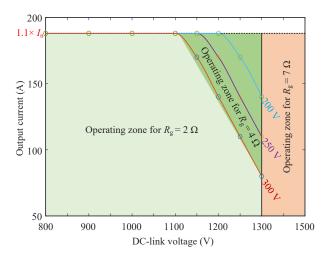

To obtain the usable range of the minimum gate resistance for a certain blocking voltage margin, a series of parametric sweeps have been performed, as presented in Fig. 12, where the load current I<sub>L</sub> varies from 100 A to 200 A before turning off the MOSFET at 1300-V DC-link. It is indicated in Fig. 12 that, for a 200-V voltage margin, the load current should be lower than 130 A. Fig. 13 indicates the operating zone for each gate resistance. When the DC-link and the output current are lower than a certain level, the minimum  $R_{\rm g}$  can be applied; otherwise, the applied gate resistance should be changed to the medium  $R_{\rm g}$ , e.g., the green triangular area. In case of a high DC-link voltage, e.g., during reactive power support with open-circuit voltage (>1300 V), the maximum  $R_{\rm g}$  is used. Alternatively, the applied gate resistance can be simply determined according to the variation of the DC-link voltage. According to the previous switching overshoot analysis, the applied  $R_{\rm g}$  and the corresponding DC-link voltage  $V_{\rm DC}$  can

Fig. 12. Turn-off transients of the lower MOSFET in the selected SiC module (see Fig. 7) under under various load current  $I_{\rm L}$ , when the DC-link voltage is 1300 V and the external gate resistance is 2  $\Omega$ .

Fig. 13. Operating zone for each gate resistance, where 200 V, 250 V, and 300 V represents the expected blocking voltage margin when  $R_{\rm g}=2~\Omega.$

be correlated and designed as

$$R_{\rm g} = \begin{cases} 2 \ \Omega, V_{\rm DC} \le 1000 \ \text{V} \\ 4 \ \Omega, 1000 \ \text{V} < V_{\rm DC} \le 1200 \ \text{V} \\ 7 \ \Omega, V_{\rm DC} > 1200 \ \text{V} \end{cases}$$

(1)

in which 1000 V and 1200 V are selected as the DC-link thresholds to ensure a sufficient blocking voltage margin.

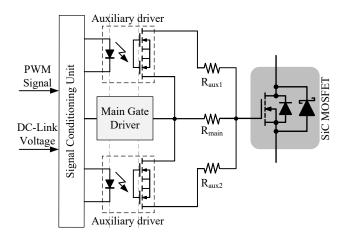

# D. Implementation of the proposed method

The proposed variable-resistance driver consists of three main parts: a signal conditioning unit, two auxiliary gate resistors, and the main gate driver. The overall block diagram of the proposed design is shown in Fig. 14. As it can be seen in it, the pulse width modulation (PWM) signal and the DC-link voltage signal are fed to a signal conditioning unit, which decides the input signals of the variable-resistance gate driver. As a consequence, the SiC MOSFET is driven by the main gate driver through  $R_{\rm main}$  when the DC-link voltage is higher than 1200 V, and the effective gate resistance can be reduced to  $R_{\rm main} \| R_{\rm aux1} \|$  or  $R_{\rm main} \| R_{\rm aux2} \|$  in the case of lower DC-link voltages. It should be mentioned that the turn-on and -off gate resistances are assumed to have the same value (e.g.,

Fig. 14. Circuit diagram of the variable-resistance gate driver:  $R_{\rm main}$  – main gate resistors,  $R_{\rm aux}$  – auxiliary gate resistors.

$R_{\rm main,on} = R_{\rm main,off} = R_{\rm main}$  in Fig. 14) in this paper for simplicity. In practice, a smaller turn-on gate resistance can be applied in order to further reduce the switching losses.

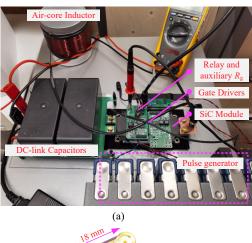

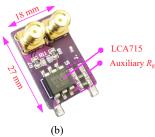

A hardware prototype employing the considered SiC MOS-FET module is built for experimental verification of the proposed gate driver design, as shown in Fig. 15(a). The main gate driving circuits are realized by using the galvanic isolated driver IC UCC21710, which is designed for up to 1700-V SiC MOSFETs by Texas Instruments. This gate driver IC features over 2-kV isolation voltage rating and 10-A peak source/sink current capability. For the auxiliary gate resistors, they are switched by the solid-state relays LCA715 from IXYS for industrial application, featuring 3750-V input-to-output isolation and ultra-low on-resistance for up to 10-A peak current capability. The LCA715 has no moving parts, offering faster, bounce-free switching in a more compact surface mount package, which is well-suited to the variable gate resistance design. The auxiliary gate resistors and the relays are placed on a separate small printed circuit board to avoid affecting the layout of the main gate driver and making a large gate driving loop, as shown in Fig. 15(b).

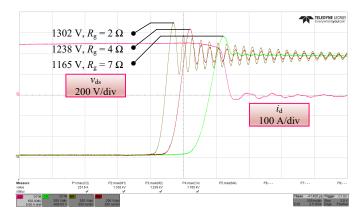

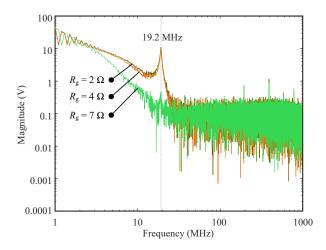

A double pulse test (DPT) under a 1000-V supply voltage and 250-A load current is performed to validate the proposed design, where a high-voltage passive probe and a current probe based on Rogowski coils are used to measure the drainsource voltage  $v_{\rm ds}$  and the drain current  $i_{\rm d}$ , respectively. The experimental results are shown in Fig. 16, which are captured with three gate resistor combinations (i.e.,  $R_{\text{main}}$ ,  $R_{\text{main}} || R_{\text{aux}1}$ , and  $R_{\text{main}} \| R_{\text{aux}2}$ ) controlled by the solid-state relays, i.e., LCA715. It should be pointed out that during the turn-off transient, the switching speed can be increased by enabling the auxiliary gate resistors, thus reducing the switching losses when the voltage stress on the DC-link is low. On the contrary, when the DC-link voltage is high, only the gate resistance on the main gate driver will be applied to reduce the voltage overshoot. The voltage spectrum for the transient waveforms of the drain-source voltage  $v_{\rm ds}$  are estimated with Fast Fourier Transform (FFT), as shown in Fig. 17. The resonant frequency 19.2 MHz is the ringing frequency of the turn-off overshoot in Fig. 16, and the magnitude at this point increases with

Fig. 15. Prototype for the proposed variable-resistance gate driver: (a) photo of the prototype and (b) the implementation of the auxiliary gate resistors.

Fig. 16. Turn-off transient waveforms of the drain-source voltage  $v_{\rm ds}$  and the drain current  $i_{\rm d}$  under different turn-off gate resistance.

the decrease of gate resistance. This is the drawback of the proposed design compared to a fixed one with large gate resistance, i.e., increased filtering efforts for EMI [30], [31].

It should be mentioned that the estimation of the total stray inductance  $L_{\rm stray}$  in the commutation loop is critical for modeling the switching process, thus affecting the variable gate resistance design. A robust measurement of  $L_{\rm stray}$  can be performed by using the DPT turn-off waveforms, which can be estimated by [32]

$$L_{\text{stray}} = \frac{V_{\text{DM}} - V_{\text{DC}}}{\left|\frac{di_{\text{D}}}{dt}\right|} \tag{2}$$

where  $V_{\rm DM}$  denotes the peak drain-source voltage during turn-off,  $V_{\rm DC}$  is the DC-link voltage, and  $di_{\rm D}/dt$  is the current slope during the initial drain current fall. With the turn-off

Fig. 17. Voltage spectrum for the transient waveforms of the drain-source voltage  $v_{\rm ds}$  under different turn-off gate resistance.

waveforms in Fig. 16,  $L_{\rm stray}$  for the realized prototype is estimated to be 90 nH.

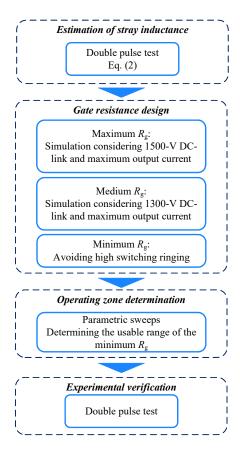

The general steps for applying the variable-resistance gate driver on the SiC-MOSFET-based 1500-V PV inverters can be summarized based on the above discussion, which is presented in Fig. 18. Firstly, the stay inductance of the inverter's commutation loop should be estimated experimentally. Then, the gate resistance value for each considered case can be designed. After that, the operating zone for each gate resistance can be determined. Finally, the gate resistance design should be verified experimentally, e.g., by double pulse tests.

# IV. RELIABILITY ASSESSMENT

In this section, a comparative lifetime evaluation will be performed to analyze the impact of the proposed gate driver design on the lifetime of the 1500-V PV inverter.

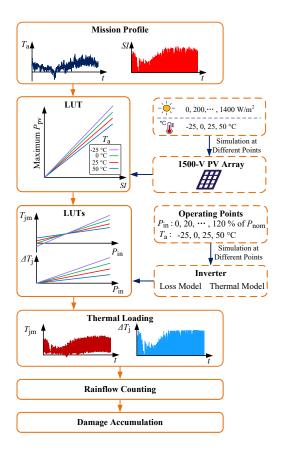

Fig. 19 shows the general procedure of the lifetime evaluation. As it can be observed in it, several steps are required to estimate the power device lifetime under certain mission profiles [24]. First, the thermal stress of the power device in the PV inverter should be simulated for a set of operating conditions, in order to obtain look-up tables (LUTs) for the long-term mission profile translation. Then, the thermal loading of the power device can be obtained. Subsequently, a counting algorithm (e.g., rainflow method [33]) can be applied to extract the thermal stress information which can later on be applied to the lifetime model. After that, the lifetime consumption (LC) can be estimated with a specific lifetime model and damage accumulation method. More details regarding the lifetime evaluation have been discussed in [24].

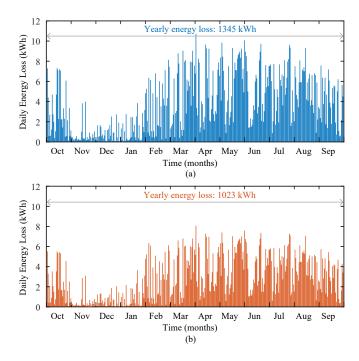

The power loss analysis in Fig. 20 shows that, with the proposed variable gate-resistance design, energy losses can be reduced during operation compared to a fixed gate-resistance design which considers the highest voltage stresses. This energy loss reduction, i.e., over 300 kWh difference per year as shown in Fig. 20, will certainly contribute to a higher reliability performance, which will be analyzed in the following.

After a certain number of power cycles, the SiC MOSFETs tend to fail due to accumulative bond-wire fatigue [34], [35].

Fig. 18. General steps for applying the proposed variable-resistance gate

In this paper, the lifetime model proposed in [36] is used. It describes the number of cycles to failure  $N_{\rm f}$  under a certain thermal stress (i.e., mean junction temperature  $T_{\rm jm}$  and cycle amplitude  $\Delta T_{\rm i}$ ) as

$$N_f = A \times (\Delta T_j)^{\alpha} \times (ar)^{\beta_1 \Delta T_j + \beta_0} \times \left[ \frac{C + (t_{\text{on}})^{\gamma}}{C + 1} \right] \times \exp\left( \frac{E_a}{k_b \times T_{\text{jm}}} \right)$$

(3)

where the impact of technology fact A, activation energy  $E_{\rm a}$ , bond wire aspect ratio ar, and heating time  $t_{\rm on}$  is considered, as summarized in Table IV. More details regarding this lifetime model have been discussed in [36]. Normally, it is assumed that various thermal loading events are independent, and the impact of the damage can be linearly accumulated following the Miner's rule [37]. With that, the LC during operation is then calculated as

$$LC = \sum_{i} \frac{n_i}{N_i} \tag{4}$$

in which  $n_i$  is the number of temperature cycles under a certain thermal stress, and  $N_i$  is the corresponding number of cycles to failure according to the lifetime model given in (3). It is considered as the end of the component life when LC equals to one.

Considering the Denmark mission profile, the above reliability assessment procedure is used to analyze the LC of the

Fig. 19. Lifetime evaluation procedure:  $T_{\rm a}$  – ambient temperature, SI –solar irradiance,  $P_{\rm pv}$  – PV output power,  $P_{\rm in}$  – inverter input power, LUT – lookup table,  $T_{\rm jm}$  – mean junction temperature,  $\Delta T_{\rm j}$  – cycle amplitude of junction temperature.

TABLE IV PARAMETERS OF THE LIFETIME MODEL [36].

| Parameter      | Value                                   | Test condition                                             |

|----------------|-----------------------------------------|------------------------------------------------------------|

| $\overline{A}$ | $3.4368 \times 10^{14}$                 |                                                            |

| $\alpha$       | -4.923                                  | $64~\mathrm{K} \leq \Delta T_j \leq 113~\mathrm{K}$        |

| $eta_1$        | $-9.012 \times 10^{-3}$                 | $0.19 \leq ar \leq 0.42$                                   |

| $\beta_0$      | 1.942                                   |                                                            |

| C              | 1.434                                   |                                                            |

| $\gamma$       | -1.208                                  | $0.07 \text{ s} \le t_{\text{on}} \le 63 \text{ s}$        |

| $E_a$          | 0.06606 eV                              | $32.5  ^{\circ}\text{C} \le T_j \le 122  ^{\circ}\text{C}$ |

| $k_B$          | $8.6173324 \times 10^{-5} \text{ eV/K}$ |                                                            |

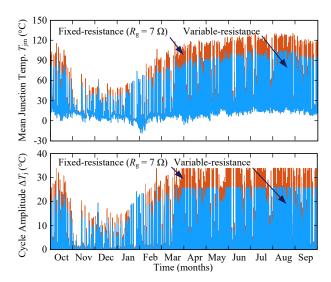

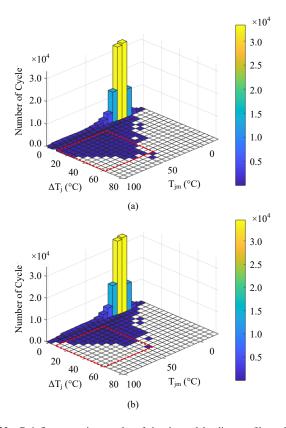

SiC-MOSFET two-level 1500-V PV inverter with a variable-resistance gate driver. For comparison, the LCs of the same PV inverter with various fixed-resistance gate drivers are also estimated. Fig. 21 shows the one-year thermal loadings of the SiC MOSFETs, and Fig. 22 presents the corresponding rainflow counting results. It can be observed in Fig. 21 that the PV inverter with the proposed variable-resistance gate driver experiences much lower thermal stresses than that with a fixed gate resistance value of 7  $\Omega$ . When comparing the rainflow counting results, as it can be seen in Fig. 22(a) and (b), the proposed design can reduce the number of thermal cycles with high mean junction temperature  $T_{\rm jm}$  and cycle amplitude  $\Delta T_{\rm j}$  (the circled area in Fig. 22(b)) in comparison to that with

Fig. 20. Daily energy loss under the Denmark mission profile (see Fig. 3): (a) with the fixed gate-resistance design ( $R_{\rm g}=7~\Omega$ ) and (b) with the proposed variable gate-resistance design.

TABLE V LIFETIME CONSUMPTION COMPARISON.

| Gate driving methods                        | LC     | LC compared to Case 5 |

|---------------------------------------------|--------|-----------------------|

| Case 1: variable $R_{\rm g}$ : 2-7 $\Omega$ | 0.0071 | 72.8% lower           |

| Case 2: fixed $R_{\rm g}=4~\Omega$          | 0.0070 | 73.2% lower           |

| Case 3: fixed $R_{\rm g}=5~\Omega$          | 0.0134 | 48.7% lower           |

| Case 4: fixed $R_{\rm g}=6~\Omega$          | 0.0198 | 24.1% lower           |

| Case 5: fixed $R_{\rm g}=7~\Omega$          | 0.0261 | _                     |

a fixed gate-resistance (the circled area in Fig. 22(a)). Table V presents the comparison of the LCs. It can be seen in Table V that the proposed design can reduce the LC of the SiC MOSFETs by 72.8% compared to the fixed gate resistance case. Moreover, the proposed design achieves a similar lifetime performance as that with a fixed gate resistance value of 4  $\Omega$  (i.e., Case 2). The LCs of Case 1 (i.e., the proposed design) and Case 2 are clearly lower than that with a higher fixed gate resistance value. More importantly, compared to Case 2, the proposed design can have a better voltage margin according to the analysis in the previous section.

Table VI further summarizes the comparison of the gate-resistance design in terms of switching losses, voltage overshoot, and LC. As seen in Table VI, with the conventional fixed gate-resistance design, there will be a trade-off between switching losses and voltage overshoot. In contrast, the variable gate-resistance design pushes this trade-off forward and enhances the PV inverter reliability, thus leading to potential reduced cost of PV energy.

Fig. 21. Thermal loadings (i.e., mean junction temperature  $T_{\rm jm}$  and cycle amplitude  $\Delta T_{\rm j}$ ) of SiC MOSFETs with different gate drivers under the Denmark mission profile (see Fig. 3).

Fig. 22. Rainflow counting results of the thermal loading profile under the Denmark mission profile (see Fig. 3): (a) with the fixed gate-resistance design ( $R_{\rm g}=7~\Omega$ ) and (b) with the proposed variable gate-resistance design.

# V. CONCLUSION

In this paper, a method to enhance the reliability of the SiC-MOSFET-based two-level inverter through the design of variable-resistance gate drivers was proposed considering the 1500-V PV application and mission profiles. The proposed variable-resistance gate driver can adjust the gate resistance according to the variation of the DC-link voltage due to the

TABLE VI GATE-RESISTANCE DESIGN COMPARISON.

| Gate resistance | Switching losses | Voltage overshoot | LC   |

|-----------------|------------------|-------------------|------|

| Large           | High             | Low               | High |

| Small           | Low              | High              | Low  |

| Variable        | Low              | Low               | Low  |

mission profile. By doing so, the switching overshoot due to the stray inductance in the commutation loops can be reduced when the PV array voltage is high, keeping the power devices within their voltage ratings. The proposed design was validated with double pulse tests at 1000-V DC-link and 250-A load current. The corresponding reliability assessment results indicate that the PV inverter with the proposed design has a better lifetime performance than that with fixed-resistance gate drivers, where the gate resistance is typically designed for the highest voltage stresses. It should be mentioned that more EMI filtering efforts may be required for the proposed design when compared to a fixed-type gate driver with relatively larger gate resistance.

### REFERENCES

- S. Kouro, J. I. Leon, D. Vinnikov, and L. G. Franquelo, "Grid-connected photovoltaic systems: An overview of recent research and emerging PV converter technology," *IEEE Ind. Electron. Mag.*, vol. 9, no. 1, pp. 47– 61, 2015.

- [2] R. Inzunza, R. Okuyama, T. Tanaka, and M. Kinoshita, "Development of a 1500Vdc photovoltaic inverter for utility-scale PV power plants," in *Proc. IFEEC*, pp. 1–4, Nov. 2015.

- [3] E. Serban, M. Ordonez, and C. Pondiche, "DC-bus voltage range extension in 1500 V photovoltaic inverters," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 3, no. 4, pp. 901–917, Dec. 2015.

- [4] B. Stevanović, D. Serrano, M. Vasić, P. Alou, J. A. Oliver, and J. A. Cobos, "Highly efficient, full ZVS, hybrid, multilevel DC/DC topology for two-stage grid-connected 1500-V PV system with employed 900-V SiC devices," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 7, no. 2, pp. 811–832, Jun. 2019.

- [5] SMA. White paper: True 1500 V technology for higher availability and more energy yields. (2020). [Online]. Available: https://www.sma.de/en/industrial-systems/old-hidden/powerplants/1500v-projects-even-more-profitable.html

- [6] E. I. Wiki. Electrical regulations and standards. (2019). [Online]. Available: https://www.electrical-installation.org

- [7] M. Rabiul Islam, A. M. Mahfuz-Ur-Rahman, K. M. Muttaqi, and D. Sutanto, "State-of-the-art of the medium-voltage power converter technologies for grid integration of solar photovoltaic power plants," *IEEE Trans. Energy Convers.*, vol. 34, no. 1, pp. 372–384, 2019.

- [8] W. Xu, Z. Guo, S. M. Tayebi, S. Rajendran, A. Sun, R. Yu, and A. Q. Huang, "Hardware design and demonstration of a 100kW, 99% efficiency dual active half bridge converter based on 1700V SiC power MOSFET," in *Proc. IEEE APEC*, pp. 1367–1373, 2020.

- [9] J. He, A. Sangwongwanich, Y. Yang, and F. Iannuzzo, "Lifetime evaluation of power modules for three-level 1500-V photovoltaic inverters," in *Proc. IEEE APEC*, pp. 430–435, 2020.

- [10] J. He, Y. Yang, and D. Vinnikov, "Energy storage for 1500 V photovoltaic systems: A comparative reliability analysis of DC- and AC-coupling," *Energies*, vol. 13, 2020.

- [11] M. Schweizer, T. Friedli, and J. W. Kolar, "Comparative evaluation of advanced three-phase three-level inverter/converter topologies against two-level systems," *IEEE Trans. Ind. Electron.*, vol. 60, no. 12, pp. 5515–5527, Dec. 2013.

- [12] K. Lenz, T. Franke, and H. Stroebel-Maier, "IGBT power module solution in three-level topologies for 1MW 1500VOC solar applications," in *Proc. PCIM Asia*, pp. 1–8, 2016.

- [13] L. Zhang, X. Yuan, X. Wu, C. Shi, J. Zhang, and Y. Zhang, "Performance evaluation of high-power SiC MOSFET modules in comparison to Si IGBT modules," *IEEE Trans. Power Electron.*, vol. 34, no. 2, pp. 1181– 1196, 2019.

- [14] C. Felgemacher, "Investigation of reliability aspects of power semiconductors in photovoltaic central inverters for sunbelt regions," Ph.D. dissertation, Kassel University, Kassel, Germany, Mar. 2018.

- [15] J. Zhang, F. L. Rees, B. Hull, J. B. Casady, S. Allen, and J. W. Palmour, "Impact of next-generation 1700V SiC MOSFETs in a 125kW PV converter," in *Proc. IEEE ECCE*, pp. 911–916, 2017.

- [16] CREE. 1700V Silicon Carbide MOSFETs. 2018. [Online]. Available: https://www.wolfspeed.com/power/products/sic-mosfets/1700v-silicon-carbide-mosfets

- [17] L. Stevanovic. From SiC MOSFET Devices to MW-scale Power Converters. Keytalks in IEEE APEC 2017. [Online]. Available: https://ieeetv.ieee.org/ieeetv-specials/keytalk-ljubisa-stevanovic-from-sic-mosfet-devices-to-mw-scale-power-converters-apec-2017/apec.dev.itswebs.com

- [18] P. Nayak and K. Hatua, "Active gate driving technique for a 1200 V SiC MOSFET to minimize detrimental effects of parasitic inductance in the converter layout," *IEEE Trans. Ind. Appl.*, vol. 54, no. 2, pp. 1622–1633, 2018

- [19] C. Sintamarean, H. Wang, F. Blaabjerg, and F. Iannuzzo, "The impact of gate-driver parameters variation and device degradation in the PVinverter lifetime," in *Proc. IEEE ECCE*, pp. 2257–2264, 2014.

- [20] S. Acharya, X. She, F. Tao, T. Frangieh, M. H. Todorovic, and R. Datta, "Active gate driver for SiC-MOSFET-based PV inverter with enhanced operating range," *IEEE Trans. Ind. Appl.*, vol. 55, no. 2, pp. 1677–1689, 2019.

- [21] S. Zhao, A. Dearien, Y. Wu, C. Farnell, A. U. Rashid, F. Luo, and H. A. Mantooth, "Adaptive multi-level active gate drivers for SiC power devices," *IEEE Trans. Power Electron.*, vol. 35, no. 2, pp. 1882–1898, 2020

- [22] J. He, A. Sangwongwanich, Y. Yang, and F. Iannuzzo, "Design for reliability of SiC-MOSFET-based 1500-V PV inverters with variable gate resistance," in *Proc. IEEE ECCE*, pp. 1850–1855, 2020.

- [23] ROHM. Silicon-Carbide (SiC) Power Module BSM250D17P2E004. (2019). [Online]. Available: https://www.rohm.com/products/sic-power-devices/sic-power-module/bsm250d17p2e004-product

- [24] Y. Yang, H. Wang, F. Blaabjerg, and K. Ma, "Mission profile based multi-disciplinary analysis of power modules in single-phase transformerless photovoltaic inverters," in *Proc. EPE*, pp. 1–10, Sep. 2013.

- [25] Jinko. JKM380M-72-V Solar Panel. (2019). [Online]. Available: http://jinkosolar.com.au/wp-content/uploads/2019/03/EaglePerc-JKM360-380M-72-V-A1-EN.pdf

- [26] H. Luo, F. Iannuzzo, K. Ma, F. Blaabjerg, W. Li, and X. He, "Active gate driving method for reliability improvement of IGBTs via junction temperature swing reduction," in *Proc. IEEE PEDG*, pp. 1–7, 2016.

- [27] D. Jiang, R. Burgos, F. Wang, and D. Boroyevich, "Temperature-dependent characteristics of SiC devices: Performance evaluation and loss calculation," *IEEE Trans. Power Electron.*, vol. 27, no. 2, pp. 1013–1024, 2012.

- [28] Y. Bae, T.-K. Vu, and R.-Y. Kim, "Implemental control strategy for grid stabilization of grid-connected PV system based on German grid code in symmetrical low-to-medium voltage network," *IEEE Trans. Energy Convers.*, vol. 28, no. 3, pp. 619–631, 2013.

- [29] M. Mirhosseini, J. Pou, and V. G. Agelidis, "Single-stage inverter-based grid-connected photovoltaic power plant with ride-through capability over different types of grid faults," in *Proc. IEEE IECON*, pp. 8008– 8013, 2013.

- [30] Y. Shi, Y. Zhang, L. Wang, and H. Li, "Reduction of EMI noise due to nonideal interleaving in a 100 kW SiC PV converter," *IEEE Trans. Power Electron.*, vol. 34, no. 1, pp. 13–19, 2019.

- [31] Y. Yang, Y. Wen, and Y. Gao, "A novel active gate driver for improving switching performance of high-power SiC MOSFET modules," *IEEE Trans. Power Electron.*, vol. 34, no. 8, pp. 7775–7787, 2019.

- [32] A. Bryant, X. Kang, E. Santi, P. Palmer, and J. Hudgins, "Two-step parameter extraction procedure with formal optimization for physicsbased circuit simulator IGBT and p-i-n diode models," *IEEE Trans. Power Electron.*, vol. 21, no. 2, pp. 295–309, 2006.

- [33] H. Huang and P. A. Mawby, "A lifetime estimation technique for voltage source inverters," *IEEE Trans. Power Electron.*, vol. 28, no. 8, pp. 4113– 4119, Aug. 2013.

- [34] P. D. Reigosa, H. Wang, Y. Yang, and F. Blaabjerg, "Prediction of bond wire fatigue of IGBTs in a PV inverter under a long-term operation," *IEEE Trans. Power Electron.*, vol. 31, no. 10, pp. 7171–7182, Oct. 2016.

- [35] L. Ceccarelli, R. M. Kotecha, A. S. Bahman, F. Iannuzzo, and H. A. Mantooth, "Mission-profile-based lifetime prediction for a SiC MOS-FET power module using a multi-step condition-mapping simulation strategy," *IEEE Trans. Power Electron.*, vol. 34, no. 10, pp. 9698–9708, 2019.

- [36] U. Scheuermann, R. Schmidt, and P. Newman, "Power cycling testing with different load pulse durations," in *Proc. IET PEMD*, pp. 1–6, 2014.

- [37] M. Miner, "Cumulative damage in fatigue," J. Appl. Mech., vol. 12, pp. 159–164, 1945.

**Jinkui He** (S'19-M'22) received the B.S. degree in electrical engineering and the M.S. degree in control engineering from China University of Petroleum (East China), Qingdao, China, in 2010 and 2012, respectively, and the Ph.D. degree in electrical engineering from the Aalborg University, Aalborg, Denmark, in 2022.

He is currently working as an Experimental Lecturer at the College of New Energy, China University of Petroleum (East China). From March to June 2021, he was a Visiting Researcher with the

University of Alberta, Canada. His research interests include grid-connected converter design and control, reliability in power electronics, and photovoltaic systems.

Ariya Sangwongwanich (S'15-M'19) received the M.Sc. and Ph.D. degree in energy engineering from Aalborg University, Denmark, in 2015 and 2018, respectively. He is currently working as an Assistant Professor at the Department of Energy Technology, Aalborg University, where he is a Vice-Leader of Photovoltaic Systems research program. His research interests include control of grid-connected converters, photovoltaic systems, reliability in power electronics, and multi-level converters.

He was a Visiting Researcher with RWTH Aachen, Aachen, Germany from September to December 2017. Dr. Sangwongwanich was the recipient of the Danish Academy of Natural Sciences' Ph.D. Prize and the Spar Nord Foundation Research Award for his Ph.D. thesis in 2019.

Yongheng Yang (SM'17) received the B.Eng. degree in electrical engineering and automation from Northwestern Polytechnical University, China, in 2009 and the Ph.D. degree in energy technology (power electronics and drives) from Aalborg University, Denmark, in 2014.

He was a postgraduate student with Southeast University, China, from 2009 to 2011. In 2013, he was a Visiting Scholar at Texas A&M University, USA. During 2014-2020, he was with the Department of Energy Technology, Aalborg University,

where he became a tenured Associate Professor in 2018. In January 2021, he joined Zhejiang University, China, as a ZJU100 Professor. His research focuses on the grid-integration of photovoltaic systems and control of power converters, in particular, the grid-forming technologies.

Dr. Yang was the Chair of the IEEE Denmark Section (2019-2020). He is an Associate Editor for several IEEE Transactions. He was the recipient of the 2018 IET Renewable Power Generation Premium Award and was an Outstanding Reviewer for the IEEE TRANSACTIONS ON POWER ELECTRONICS in 2018. He was the recipient of the 2021 Richard M. Bass Outstanding Young Power Electronics Engineer Award from the IEEE Power Electronics Society (PELS) and the 2022 Isao Takahashi Power Electronics Award. In addition, he has received two IEEE Best Paper Awards. He has been included on the list of Highly Cited Chinese Researchers by Elsevier in 2022. He is currently the Secretary of the IEEE PELS Technical Committee on Sustainable Energy Systems and a Council Member of the China Power Supply Society.

**Kaichen Zhang** (S'21) received the B.Eng. degree in electrical engineering and automation from Huazhong University of Science and Technology, China, in 2018, and the M.S. degree in energy technology (power electronics and drives) from Aalborg University, Denmark, in 2020.

He is currently a Research Assistant with the Department of Energy, Aalborg University, Aalborg, Denmark. From September 2019 to February 2020, he was with ABB Corporate Research Center, Baden, Switzerland. He is also a part of the Center

of Reliable Power Electronics (CORPE), Aalborg University. His current research interests focus on the reliability of power electronic devices, including condition monitoring, and lifetime modeling and prediction of power modules.

Francesco Iannuzzo (SM'12) received the M.Sc. degree in Electronic Engineering and the Ph.D. degree in Electronic and Information Engineering from the University of Naples, Italy, in 1997 and 2002, respectively.

He is currently a professor of reliable power electronics at the Aalborg University, Denmark, where he is also part of CORPE, the Center of Reliable Power Electronics. His research interests are in the field of reliability of power devices, condition monitoring, failure modelling and testing up to megawatts

under extreme conditions. He is author or co-author of +260 publications on journals and international conferences, three book chapters and four patents, and has edited a book on Modern Power Electronic Devices (2020, IET). Besides the publication activity, over the past years he has been contributing +20 technical seminars about reliability at top-tier conferences as ISPSD, IRPS, EPE, ECCE, PCIM and APEC.

Prof. Iannuzzo currently serves as the chair of the IEEE IAS Power Electronic Devices and Components Committee. In 2018 he was the general chair of the 29th ESREF, the first European conference on the reliability of electronics, and has recently been appointed general chair for the 2023 EPE-ECCE Europe conference in Aalborg.