# **Aalborg Universitet**

# Digital design demonstration of 10kV SiC-MOSFET power module to improve wirebonding layout for power cycle capabilities

Takahashi, Masaki; Aunsborg, Thore Stig; Uhrenfeldt, Christian; Munk-Nielsen, Stig; Jørgensen, Asger Bjørn

Published in:

2022 IEEE International Workshop on Integrated Power Packaging (IWIPP)

DOI (link to publication from Publisher): 10.1109/IWIPP50752.2022.9894237

Publication date: 2022

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Takahashi, M., Aunsborg, T. S., Uhrenfeldt, C., Munk-Nielsen, S., & Jørgensen, A. B. (2022). Digital design demonstration of 10kV SiC-MOSFET power module to improve wire-bonding layout for power cycle capabilities. In 2022 IEEE International Workshop on Integrated Power Packaging (IWIPP) Article 3 IEEE (Institute of Electrical and Electronics Engineers). https://doi.org/10.1109/IWIPP50752.2022.9894237

# **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

# Digital design demonstration of 10kV SiC-MOSFET power module to improve wire-bonding layout for power cycle capabilities

Masaki Takahashi Department of Energy Aalborg university Aalborg, Denmark mata@energy.aau.dk Thore Stig Aunsborg Department of Energy Aalborg university Aalborg, Denmark tsu@energy.aau.dk Christian Uhrenfeldt Department of Energy Aalborg university Aalborg, Denmark chu@energy.aau.dk Stig Munk-Nielsen Department of Energy Aalborg university Aalborg, Denmark smn@energy.aau.dk

Asger Bjørn Jørgensen Department of Energy Aalborg university Aalborg, Denmark abj@energy.aau.dk

Abstract— Determining the reliability of 10 kV SiC-MOSFET power modules experimentally, is challenging due to the low number of samples available in the market. A digital design based on 3D thermal calculations is demonstrated to improve reliability capability in a 10 kV SiC-MOSFET power module. The module design was determined based on the calculation with digital twin modelling. The correctness of the digital twin model was confirmed by fabricating a 10kV SiC-MOSFETs power module sample and comparing the calculation temperature with the measured results. The design was focused on aluminum wires on chips, and the effect of the wire temperature by changing the wire layout was clarified. The results show that the improved wire layout reduces the wire temperature by 2.2-5.3% compared to the conventional design. This is expected to increase the power cycle capability by up to 31%, according to predictions based on the Coffin-Manson model.

Keywords—  $-10~\rm kV~SiC~MOSFET$ , power module, digital design, 3D thermal simulation, power cycle

### I. INTRODUCTION

Power modules with Silicon Carbide metal-oxide-semiconductor field effect transistors (SiC-MOSFET) can be applied in higher voltage ranges than the currently mainstream Silicon insulated-gate bipolar transistor (Si-IGBT) power modules due to the material properties of SiC. For applications of 10kV or higher, SiC MOSFETs have superior output characteristics compared to Si IGBTs [1], which has led to increased interest in SiC MOSFET medium voltage power modules. However, there are currently only engineering samples of 10kV SiC-MOSFET chips available on the market. Therefore, it is challenging for module designers to obtain the necessary number of chips for their design verification of reliability. Thus, following a conventional procedure of

The power module characteristics covered by the design process include electrical, thermal, mechanical, structural, and reliability [3, 4]. Reliability design, as typified by power cycle capability, is a process that requires many prototypes and much evaluation time. For example, five samples are required per one reliability test, so dozens of samples are needed for all reliability tests [4]. Moreover, each test takes about 2-3 months, which adds up as "design lead time" as the number of tests increases. In addition, it is difficult to prepare the required number of samples for reliability testing for modules with devices that are not widely available in the market, such as 10kV SiC-MOSFETs. In such reliability design, the product structure can be optimized before physical measurements are made by utilizing digital design. As a result, the number of physical prototypes and tests can be reduced compared to conventional trial-and-error design methods based on actual power cycling measurement results.

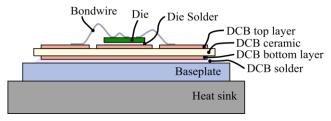

Fig. 1. Cross sectional image of power module structure

several experimental power cycling tests, may result in high design costs and long design lead times. Instead, design optimization by "digital design" is very useful for products with such scarce devices, as it enables optimized design parameters without building many physical prototypes in a laboratory. Digital design is gaining attention as a nextgeneration product design method for power electronics [2]. This is a method of optimizing product structures using a digital twin of the target product. This enables high-quality products to be designed in a short time and reducing the number of physical prototypes in the laboratory.

This research is conducted as part of the Center of Digitalized Electronics (CoDE) project, funded by the Poul Due Jensen Foundation Grant number 2020-070

The structure of a conventional power module (Direct Copper Bonding (DCB), solder, semiconductor chip and bondwire(Al)), which is shown in Fig. 1, typically has three weak points for long-term reliability tests. They are (1) Chipwire interface, (2) Chip-solder interface, (3) DCB-base plate interface [5]. Especially, (1) occurs most frequently in semiconductor packages and requires special attention in power modules that handle high temperature and high power [6]. Therefore, what is studied in this paper is how to improve the chip-wire interface delamination capability. This failure is due to strain and stress caused during heat generation between materials with different coefficients of thermal expansion (CTEs). Therefore, mitigating the thermal stress of wires on the chip when the device is operated improves the power cycle capability. As an example, it has been shown that, in the case of Si PIN diodes, the temperature difference between the aluminum wires and the device is reduced by optimising the wire layout on the chip [7]. This is one of the simplest design optimisations to improve the reliability of wire bonds, which does not require more advanced material technologies for connections. For devices with new materials or structures, such as 10 kV SiC-MOSFETs, the temperature distribution model on the chip surface has not been sufficiently validated. Therefore, it is unclear to what extent reliability will be affected.

In this paper, 10kV SiC-MOSFET modules are investigated based on the 3D thermal calculation to improve the power cycle capability. First, a simulation framework for calculation of thermal parameters is experimentally verified through comparison with prototype measurements of existing 10kV SiC-MOSFET power modules. Second, the thermal distribution effect of the larger edge length in 10 kV SiC-MOSFETs is analyzed in the calculation. Finally, the module design is demonstrated in the digital twin, with particular focus on the wire layout on the chip source pad. The "digital design" method was evaluated by estimating the effect of the design on power cycle performance improvement.

# II. METHODOLOGY

The target module in this research is a package with a half-bridge power module incorporating 10 kV SiC-MOSFETs [8, 9] which is the same structure in Fig. 1. The device installed is a Wolfspeed 3rd generation SiC-MOSFET CMP3-100000-035B (Ron= $350\text{m}\Omega$ ). Thermal simulation was performed using ANSYS mechanical (Workbench 2021 R1) [10].

# A. 3D Thermal modelling of 10kV SiC-MOSFET modules

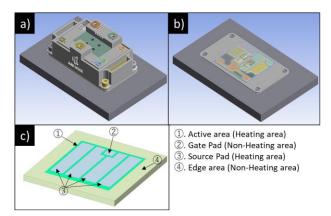

First, it was checked whether the thermal calculation results from the 3D model can be correctly reproduced by comparing the calculations with the actual measurements. The module and SiC-MOSFET 3D models in this calculation are shown in Fig. 2. The module layout detail is found in [9] [11]. In thermal calculations, the module model without the case, terminals and gel shown in Fig. 2-b was used. The components of the module and the various physical properties used in the calculations are shown in TABLE I [9, 12-15]. The SiC-MOSFET is modelled

Fig. 2. 3D model of power modules and SiC-MOSFET

a). 3D model of the 10kV SiC-MOSFET power module package with a heat sink. b). 3D model for thermal calculations without the case, terminals, and isolation gel. c). 3D model of a 10 kV SiC-MOSFET device that consists of heating area (Active area, Source pad) and non-heating area (Gate pad, Edge area).

as four parts: active part, gate pad, source pad and edge part (i.e. Edge areas to reduce the concentration of electric fields generated at the perimeter of the chip), as shown in Fig. 2-c, and the active part and the source pad was calculated as the heating element [11]. For the operating conditions, a single DC constant power profile (on/off=2/3sec,  $T_0$ =23°C,) simulating a power cycle test was performed. In order to compare with the measurement results, the applied power value was determined so that the maximum chip surface temperature change  $\Delta T_{\rm chip}$  surface max=100°C.

TABLE I. THICKNESS AND PROPERTIES OF MATERIALS[9, 12-15]

| Structure              | Material                 | Thickness [9] | Density<br>[kg/m3] | Thermal conductivity [W/(m • K)] | Heat capacity [J/(kg • K)]] |

|------------------------|--------------------------|---------------|--------------------|----------------------------------|-----------------------------|

| Bondwire               | Al                       | 250μm         | 2689*              | 237.5*                           | 880*                        |

| Die                    | 4H-SiC                   | 500μm         | 3240<br>[12]       | 353.3<br>[12]                    | 551.8<br>[12]               |

| Die<br>solder          | 96.5Sn-<br>3Ag-<br>0.5Cu | 50μm          | 7370<br>[12]       | 57<br>[12]                       | 220<br>[12]                 |

| DCB top<br>layer       | Cu                       | 300µm         | 8960<br>[13]       | 400<br>[13]                      | 385<br>[13]                 |

| DCB<br>ceramic         | AlN                      | 630µm         | 3300<br>[14]       | 150<br>[14]                      | 710<br>[14]                 |

| DCB<br>bottom<br>layer | Cu                       | 300µm         | 8960               | 400                              | 385                         |

| DCB<br>Solder          | 96.5Sn-<br>3Ag-<br>0.5Cu | 50µm          | 7370               | 57                               | 220                         |

| Baseplate              | AlSiC                    | 1.5mm         | 2600<br>[15]       | 140<br>[15]                      | 730<br>[15]                 |

| Heat sink              | Al                       | 10cm          | 2689               | 237.5                            | 880                         |

\* General material properties in the ANSYS material library

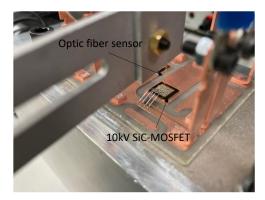

For actual measurements, the test sample of 10 kV SiC-MOSFET module without gel was manufactured. The power was energized under the same conditions as the calculation, and the chip surface temperature was measured with an optical fiber (OTG-F type-10-62ST, from OpSens Solutions) as shown in Fig. 3.

Fig. 3. The picture of chip surface temperature measurement by the optic fiber sensor

# B. Temperature distribution for the SiC-MOSFET

3D thermal calculations focusing on the chip edge length were performed to verify the surface temperature distribution of the 10kV SiC-MOSFET. SiC-MOSFETs with different edge length were analyzed. The temperature distribution of 10 kV SiC-MOSFETs was characterised by comparing the other edge length SiC-MOSFETs calculation results. The calculation conditions were DC constant power profile (on/off=2/3sec,  $T_0$ =25°C). Therefore, the applied power value was adjusted so that the maximum chip surface temperature  $T_{\rm chip}$  surface  $T_{\rm chip}$  surface

# C. Design of modules structures to improve the power cycle capabilities

According to the thermal characteristics of the 10 kV SiC-MOSFETs shown in the above calculations, the module structures that improve power cycle capability were estimated and module design in 3D models were created. 3D thermal calculations were performed on these models to confirm the effect of improved power cycle performance. The calculation conditions were similar to methodology B.

# III. RESULT

# A. Comparison of 3D thermal simulation and actual sample measurements

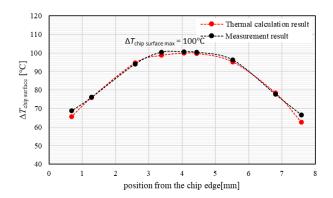

The temperature distribution of the 10kV SiC-MOSFET surface by calculations is compared with the measured results. The one-dimensional profile of chip surface temperature  $\Delta T_j$  with respect to position on the chip are shown in Fig. 4. The results show that the calculated surface temperature agree well with the measured results with a error value of less than 4 K. The simulated line profile is visualized in Fig. 5-a (bottom).

# B. The variation in surface temperature distribution of SiC-MOSFETs due to the edge length

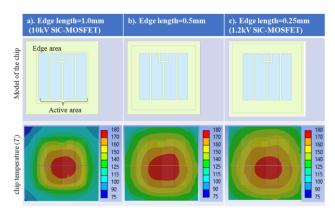

The variation in temperature distribution with geometry of the 10kV SiC-MOSFET was evaluated. As a comparison, three different edge widths SiC-MOSFET models with the same chip

Fig. 4. Comparative results of 3D thermal calculations and measured 10kV SiC-MOSFET temperatures  $\Delta T_{\text{chip surface}}$ . (line profile on the chip)

Fig. 5. Calculated surface temperature distribution of SiC-MOSFETs with different edge sizes.

- a). Edge width 1 mm (10 kV SiC-MOSFET), b). Edge width 0.5 mm

- c). Edge width 0.25 mm (1.2 kV SiC-MOSFET)

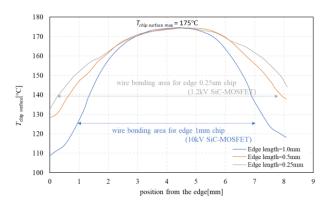

size (8.1×8.1 mm²) were investigated and the temperature was calculated. In this calculation, all other module structures and operating conditions are the same. Fig. 5 a-c shows SiC-MOSFET models with edge widths of 1 mm (i.e. edge length of 10kV SiC-MOSFETs), 0.5 mm and 0.25 mm (i.e. edge length of 1.2kV SiC-MOSFETs) and the temperature calculation results. Fig. 6 shows a comparison of one-dimensional temperature profiles at the same line of Fig.5 a, b and c. The result shows that the 10kV SiC-MOSFET with

Fig. 6. Calculated temperature  $T_j$  (line profile on the chip) comparison between 10kV SiC-MOSFETs and different edge sizes.

1mm edge length has the largest temperature gradient on the chip surface (*T*<sub>chip</sub> <sub>surface</sub>). These results show that the temperature gradient on the chip surface increases when the edge structure, which acts as a heat conductor, increases in relation to the active area, which is the heat-generating element. Therefore, for high-voltage devices such as 10kV SiC-MOSFETs where large edge isolation areas are used, optimising the wire bonding layout to suppress wire temperature is more effective than for low-voltage devices, due to the large surface temperature gradient across the device as will be shown below.

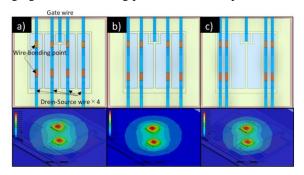

# C. Results of wire layout on 10kV SiC-MOSFET module to reduce the wire temperature in the digital twin

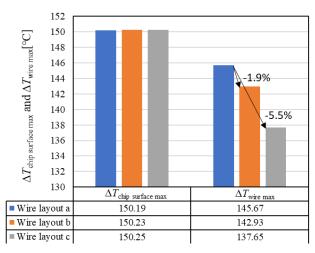

According to the above results, 10kV SiC-MOSFETs have a comparatively large temperature gradient across the surface. Therefore, the Al wire temperature on the source pad of the chip is highly dependent on the bonding position on the chip source pads. From the module design point of view, it suggests that the wire temperature can be reduced by optimizing wire layout on source pads. In this section, the effect of wire temperature reduction was calculated when the wire layout was changed. The wire layout design of 10kV SiC-MOSFET modules is carried out in the 3D model to compare the maximum wire temperature swing (= $T_{\text{wire max}}$ - $T_0$ ). Three wire layout patterns were considered, including a reference layout. Wire layouts and the temperature calculation results are shown in Fig. 7. The standard layout (Fig. 7-a) is the one in which the wires are placed in the center of source pads where wire bonding is possible. As modified wire layouts, two layouts were considered to avoid the center of source pads, which is the highest temperature on the chip surface (Fig. 7-b, c). The temperatures calculated for these three model patterns under the same power value (380W/chip) are shown in Fig. 8. The maximum chip heating  $\Delta T_{i,max}$  shown on the left side of Fig. 8 is almost constant regardless of the wire layout. In contrast,  $\Delta T_{\text{wire max}}$  shown on the right side of Fig. 8 is smaller due to the wire layout modified. Compared to the standard layout, the improved layout reduced the maximum wire temperature swing by 2.7-8.0°C (1.9-5.5%). This is due to changing the wire bonding position on the chip to the source

Fig. 7. SiC-MOSFET wire layout model and temperature calculation results.

- a). Standard: Wire bonding position is the center of Al-source pads

- b). Modified: Wire bonding located on the edge of Al-source pads

- c). Further modified :Wire bonding only on Al-sorce pads at both edges.

Fig. 8. Calculate and compared results of  $\Delta T_{\rm j\,max}$  and  $\Delta T_{\rm wire\,max}$ . All model were applied the same power value ( $\Delta T_{\rm j\,max}$ =150°C).

pad end where the temperature is lower, as shown in Fig. 6.

# IV. DISCUSSION

The expected power cycle capabilities improvement effect of reduced wire temperature is discussed using prediction model. The device temperature during operation and power cycle capability are described using the Coffin-Manson model [16] as follows. Here, focusing that the power cycle failure is caused by thermal expansion due to the maximum wire temperature swing  $\Delta T_{\rm wire}$  is incorporated in the Coffin-Manson model. Therefore, the relationship between the  $\Delta T_{\rm wire \; max}$  and power cycle capability  $N_{\rm f}$  is described as follows:

$$N_{\rm f} = A(\Delta T_{\rm wire\ max})^{\rm a} \exp(B/T_{\rm i\ max}) \tag{1}$$

$N_f$  is the number of power cycles to failure, A, B and  $\alpha$  are constants.

According to (1), the effect of the power cycle capability improvement due to the reduction of wire temperature swing is estimated. The constants A, B and  $\alpha$  included in (1) are necessary for the calculation. Therefore,  $N_f$  was calculated using the various constants from the power cycle withstand capacity prediction models for power modules reported by other groups. A list of references and  $N_{\rm f}$  calculation formulae used for this calculation is given in TABLE II below. [16-21] On the other hand, it has been reported that the respective constants required to accurately predict  $N_{\rm f}$  depend on the device and module structure in higher detail [20], and in this case a power cycle test on a specific layout with a 10kV SiC-MOSFET is required. However, as mentioned earlier, by applying the wiring design method based on the results of the 3D thermal calculations, an improved structure of the module can be efficiently identified using the digital design approach.

TABLE II. LIFETIME MODELS AND CONSTANTS IN REFFERENCES

| REF. | Target<br>sample          | Lifetime model equation                                                                                           | Constant<br>Values                                                                             |

|------|---------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 16   | Si-IGBT<br>modules        | $N_f = K \cdot \Delta T_j^{\beta_1} \cdot e^{\frac{\beta_2}{T_j + 273}} \cdot t_{on}^{\beta_3} \cdot I^{\beta_4}$ | $\beta_1$ =-4.416<br>$\beta_2$ =1.29×10 <sup>3</sup><br>$\beta_3$ =-0.463<br>$\beta_4$ =-0.716 |

| 17   | Si-IGBT<br>modules        | $N_f = A \cdot \Delta T_j^{\alpha} \cdot e^{\frac{Q}{R \cdot T_m}}$                                               | A=640<br>$\alpha=-5$<br>$Q=7.8\times10^4$<br>R=8.314                                           |

| 18   | Si-IGBT<br>modules        | $N_f = C \times \left(\Delta T_{j,t}\right)^{-\alpha} \cdot e^{\frac{E_{\alpha}}{k_B \cdot T_{jm,t}}}$            | C=97.2<br>$\alpha=-3.1$<br>$E_{\alpha}=9.89\times10^{-20}$<br>$k_{B}=1.38\times10^{-23}$       |

| 19   | Si-IGBT<br>modules        | $N_f = A \cdot (\Delta T)^{\alpha_0}$                                                                             | $A=1.41\times10^{13}$<br>$\alpha=-4.3327$                                                      |

| 20   | SiC-<br>MOSFET<br>TO-247  | $N_f = A \cdot \Delta T^{\alpha} \cdot e^{\frac{\beta}{T_m}}$                                                     | $A=1.34\times10^{10}$<br>$\alpha=-2.7478$<br>$A=1.56\times10^{13}$<br>$\alpha=-4.2991$         |

| 21   | SiC-<br>MOSFET<br>modules | $N_f = K' \cdot \Delta T_{vj}^{\beta_1} \cdot e^{\frac{\beta_2}{T_{vjmin}}} \cdot I_{bw}^{\beta_4}$               | K'=1.31×10 <sup>10</sup><br>$\beta_1$ =-3.775<br>$\beta_2$ =1285<br>$\beta_4$ =-0.387          |

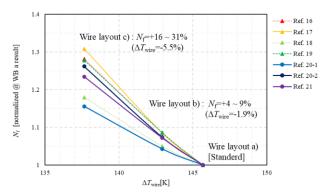

Using these equations and constants in TABLE II,  $N_{\rm f}$  values were calculated for each of the three wire layouts of  $\Delta T_{\rm wire\ max}$  and  $\Delta T_{\rm j\ max}$  obtained in this simulation. The results of the calculations are shown in Fig. 9. They are normalized with respect to  $N_{\rm f}$  at the calculation result for the standard wire layout (Wire layout a). This means that the values on the vertical axis show the rate of change with respect to the standard.

•  $\Delta T_{\text{wire max}} = 1.9\%$  reduction :  $N_f = +4 \sim 9\%$

(Wire layout Fig. 7-a  $\rightarrow$  Fig. 7-b)

•  $\Delta T_{\text{wire max}}$ =5.5% reduction :  $N_f$ =+16 ~ 31%

(Wire layout Fig. 7-a  $\rightarrow$  Fig. 7-c)

The results show that  $N_{\rm f}$  increases at a greater rate than the reduction rate of wire temperature  $\Delta T_{\rm wire\ max}$ . This is due to the

Fig. 9. Power cycle capability  $N_{\rm f}$  calculation results for each wire bonding layout in Fig. 6 a-c when the same power value (380W/chip) was applied ( $\Delta T_{\rm wire}$ =144°C). The value of  $N_{\rm f}$  is expressed as the percentage change in the value of WB a), normalized. Wire layout changes have reduced  $\Delta T_{\rm wire}$  max and increased  $N_{\rm f}$ . Mark  $\triangle$  shows the results quoted from References about Si-IGBTs and Mark  $\bigcirc$  shows the calculation results quoted from References about SiC-MOSFETs.

fact that, from (2),  $\Delta T_{\text{wire max}}$  varies with an exponent of constant  $\alpha$  (<2 in all references) with respect to  $N_{\rm f}$ . This indicates that a slight reduction in wire temperature, has a significant impact on the power cycle capability  $N_{\rm f}$ . Therefore designing a module structure that suppresses the wire temperature can effectively improve the power cycle capability without additional manufacturing complexity or cost. In this study, a design for improving power cycle was conducted based on thermal calculation. In actual product design, it is necessary to optimize the design by considering other electrical, thermal, and reliability characteristics. However, we have shown that wire layout design to minimize wire temperature for power cycle improvement can be performed on the digital twin. This method can determine the optimal structure for power cycle capability with a minimum number of physical prototypes, which previously required many actual samples and measurements, thus enabling efficient reliability design with a less cost and lead time.

# V. CONCLUSION

A digital design to improve the power cycle capability using 3D thermal calculations was demonstrated for 10kV SiC-MOSFET power modules.

First, it was confirmed that the thermal calculation results from the 3D model of the 10kV SiC-MOSFET matched well with the actual measurements.

Next, it was clarified that the spread of surface heat during energisation of 10kV SiC-MOSFETs is greater than for lower voltage devices such as 1.2kV due to the structure of the device, and the wire bonding points to the chip surface have a greater impact on the wire temperature.

An improved wire layout that avoids the hottest areas of the chip surface was proposed, and it was shown that the wire temperature swing during operation could be reduced by 1.9-5.5% compared to a standard layout.

Finally, the power cycle capability improvement due to the wire temperature reduction is estimated based on reference values, and the possibility of a larger power cycle capability improvement than the wire temperature reduction is shown. According to these results, an efficient design method for improving the power cycle using digital twin and 3D thermal simulation was proposed.

# REFERENCES

- [1] Jeffrey B. Casady, Vipindas Pala, Daniel J. Lichtenwalner, Edward Van Brunt, Brett Hull, Gang-Yao Wang, Jim. Richmond, Scott T. Allen, Dave Grider, John W., "New generation 10kV SiC power MOSFET and diodes for industrial applications", Proceedings of PCIM Europe 2015 (International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management. (2015)

- [2] Asger Bjørn Jørgensen, Stig Munk-Nielsen and Christian Uhrenfeldt, "Overview of digital design and finite element analysis in modern power electronic packaging", IEEE Transactions on Power Electronics, 35(10), 10892-10905. (2020)

- [3] Infineon Datasheet "FF1800R17IP5P", V3.1, 21-8-2020

- [4] Fuji Electric Co., Ltd. Application manual, Chapter 11 "Reliability of power module", REH984e, Janualy 2017

- [5] Josef Lutz, "IGBT-modules: design for reliability", Proceedings of 13th European Conference on Power Electronics and Applications. (2009)

- [6] Gregory Bower, Chris Rogan, P.E., James Kozlowski, and Michael Zugger, "SiC power electronics packaging prognostics", Proceedings of IEEE Aerospace Conference. (2008)

- [7] Masayasu Ishiko, Masanori Usui , Takashi Ohuchi and Mikio Shirai, "Design concept for wire-bonding reliability improvement by optimizing position in power devices", Microelectronics Journal 37, pp.262–268. (2006)

- [8] Asger Bjørn Jørgensen, Nicklas Christensen, Dipen Narendra Dalal, Simon Dyhr Sønderskov Szymon Be,czkowski, Christian Uhrenfeldt and Stig Munk-Nielsen, "Reduction of parasitic capacitance in 10 kV SiC MOSFET power modules using 3D FEM", Proceedings of 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe) IEEE Press. (2017)

- [9] Dipen Narendra Dalal, Nicklas Christensen, Asger Bjørn Jørgensen, Jannick Kjær Jørgensen, Szymon Beczkowski, Stig Munk-Nielsen and Christian Uhrenfeldt, "Impact of power module parasitic capacitances on medium voltage SiC MOSFETs switching transients" IEEE Journal of Emerging and Selected Topics in Power Electronics, 8(1), pp.298-310. (2020)

- [10] ANSYS, Inc. HP "Ansys Mechanical Finite Element Analysis (FEA) Software for Structural Engineering" [online] Available : https://www.ansys.com/products/structures/ansys-mechanical (veiwed at 1st June 2022)

- [11] Dipen Narendra Dalal, "Demonstration of 10 kV silicon carbide power semiconductor technology in medium voltage power conversion", Alborg university Press, PhD thesis, pp.70-75. (2021)

- [12] Asad Fayyaz, Li Yang and Alberto Castellazzi "Transient robustness testing of silicon carbide (SiC) power MOSFETs", Proceedings of 15th European Conference on Power Electronics and Applications (EPE). (2013)

- [13] Asger Bjørn Jørgensen, Tzu-Hsuan Cheng, Douglas Hopkins, Szymon Beczkowski, Christian Uhrenfeldt, Stig Munk-Nielsen "Thermal characteristics and simulation of an integrated GaN eHEMT power module", Proceedings of 21st European Conference on Power Electronics and Applications (EPE '19 ECCE Europe). (2019)

- [14] Ceramics processing "List of physical properties" (in Japanese) [online] Available : https://ceramics.s-projects.net/material/every-property/list.html (Veiw at 1st June 2022)

- [15] A.L.M.T. Corp. HP "List of heat sink material Properties" (in Japanese) [online] Available: https://www.allied-material.co.jp/dcms\_media/other/t52nn.pdf (Veiw at 1st June 2022)

- [16] Reinhold Bayerer, Tobias Herrmann, Thomas Licht, Josef Lutz and Marco Feller, "Model for power cycling lifetime of IGBT modules – various factors influencing lifetime", Proceedings of 5th International Conference on Integrated Power Electronics Systems. (2014)

- [17] M. Held, P. Jacob, G. Nicoletti, P. Scacco and M.-H. Poech, "Fast power cycling test for IGBT modules in traction application", Proceedings of Second International Conference on Power Electronics and Drive Systems, 1997, pp. 425–430. (1997)

- [18] Mohsen Akbari, Amir Sajjad Bahman , Paula Diaz Reigosa , Lorenzo Ceccarelli , Francesco Iannuzzo and Mohammad Tavakoli Bina, "Non-uniform temperature distribution implications on thermal analysis accuracy of Si IGBTs and SiC MOSFETs", Proceedings of 24th International Workshop on Thermal Investigations of ICs and Systems. (2018)

- [19] Yi Zhang, Huai Wang, Zhongxu Wang, Yongheng Yang and Frede Blaabjerg, "Impact of lifetime model selections on the reliability prediction of IGBT modules in modular multilevel converters", Proceedings of 2017 IEEE Energy Conversion Congress and Exposition (ECCE). (2017)

- [20] Felix Hoffmann and Nando Kaminski, "Impact of device design on the power cycling capability of discrete SiC MOSFETs at different temperature swings", Proceedings of the 32nd International Symposium

- on Power Semiconductor Devices and ICs (ISPSD) September 13 18. (2020)

- [21] Felix Hoffmann, Nando Kaminski and Stefan Schmitt, "Comparison of the power cycling performance of silicon and silicon carbide power devices in a baseplate less module package at different temperature swings", Proceedings of the 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD). (2022)