# **Aalborg Universitet**

# Learning-based Grid Impedance Shaping Method Applied for High-Accuracy Power Hardware-in-the-Loop

Oshnoei, Arman: De Araujo Ribeiro, Ricardo Lucio; Anvari-Moghaddam, Amjad; Blaabjerg, Frede

Published in:

ICPE 2023-ECCE Asia - 11th International Conference on Power Electronics - ECCE Asia

DOI (link to publication from Publisher): 10.23919/ICPE2023-ECCEAsia54778.2023.10213962

Publication date: 2023

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Oshnoei, A., De Araujo Ribeiro, R. L., Anvari-Moghaddam, A., & Blaabjerg, F. (2023). Learning-based Grid Impedance Shaping Method Applied for High-Accuracy Power Hardware-in-the-Loop. In *ICPE 2023-ECCE Asia* - 11th International Conference on Power Electronics - ECCE Asia (20.2548). Article 10213962 IEEE (Institute of Electrical and Electronics Engineers), https://doi.org/10.23919/ICPE2023-ECCEAsia54778.2023.10213962

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

# Learning-based Grid Impedance Shaping Method Applied for High-Accuracy Power Hardware-in-the-Loop

A. Oshnoei<sup>1</sup>, R. L. A. Ribeiro<sup>2</sup>, A. Anvari-Moghaddam<sup>1</sup>, F. Blaabjerg<sup>1</sup>

<sup>1</sup>AAU Energy, Aalborg University, 9220 Aalborg, Denmark <sup>2</sup> Department of Electrical Engineering, Federal University of Rio Grande do Norte (UFRN), Natal 59072-970, Brazil

Abstract-- Future power and energy systems integrate cutting-edge technologies such as power converter-interfaced distributed generation and energy storage systems and responsive loads organized as microgrid clusters. The performance evaluation of these complex systems requires flexible testbeds to provide relevant information under different operational scenarios. Thus, this paper proposes a Power Hardware-in-the-Loop (PHIL)'s power interface algorithm that uses a digital twin system (DTS) implemented through a learning-based virtual impedance control approach to provide high-accuracy experiments and enhance system stability. Experimental results obtained from a PHIL laboratory setup demonstrated the effectiveness of the proposed method.

*Index Terms*-- Power hardware-in-the-loop, virtual impedance, artificial intelligence, grid impedance estimation, brain emotional learning.

### I. INTRODUCTION

Renewable Energy Sources (RESs) have been steadily developing worldwide to address the energy shortage and the low-carbon motivations. However, the RESs such as the photovoltaic and wind generations largely depend on environmental conditions and exhibit intermittent and uncertain behavior. RESs are interconnected to the power grid through power converters operating as current- or voltage- controlled sources. These active front-end systems could modify the grid dynamics, addressing undesired stability issues. These effects are generally correlated to the impedance interaction among the grid and multiple grid-connected power converters [1]. The insertion of Grid-Forming Converters (GFCs) could overcome these drawbacks and enhance grid stability [2]. However, the insertion of GFCs into the network should be previously tested to forecast their operational constraints and the local and global stability. For secure reasons, it is impossible to perform tests and analyses directly in the power grid, particularly in complicated grids with many stakeholders and a heightened degree of distributed generation. Hence, the challenges for widespread power system integration with RESs require advanced analysis and simulation methods to evaluate their effectiveness and stability [3], [4].

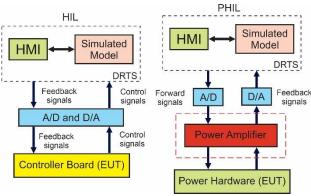

Hardware-in-the-Loop (HIL) system is usually used to test specific networks connected with various applications in the industry. It employs a controller board to perform a real-time network simulation, interconnected to the hardware under test through control and measurement signals. This setup provides enough information for evaluating embedded control boards or parts of equipment without power exchange. On the contrary, Power Hardware-in-the-Loop (PHIL) systems have been demonstrated to be attractive for testing RESs and their integration with the power system, with reduced cost and associated risk compared with their realization on large and complex power systems' testbeds [5], [6]. The use of PHIL as a power testbed avoids losses due to the possible design choices or specifications changing. Moreover, it produces precise and realistic testing conditions before installation, mitigating possible integration mismatches [4]. Differently of the HIL, PHIL deals with real power exchange between the Digital Real Time Simulator (DRTS) and Equipment under Test (EUT) by using a Power Amplifier (PA) normally implemented by a power converter as shown in Fig. 1. PHIL testing procedures have been used in several applications, such as electric ships [3], [5], nonlinear power electronics-based equipment [6], [7], renewable energy systems [8], [9], and energy storage systems [10]. However, although PHIL's testing and verification provide significant benefits, some drawbacks still arise due to its hybrid nature, resulting in accuracy and stability issues. For example, the required signal interchange, provided by an interface algorithm, results in closed-loop paths, inserting significant impacts on the PHIL's experiment stability [11]. In this context, nonideal characteristics such as time delay and bandwidth inherent to power amplifiers (PA), signal acquisition interfaces, output, and aliasing filters should also be considered [12], [13] in the design approach. In most applications, the representation of voltage and current variables in the DRTS or PA employs controlled voltage or current sources based on average models that neglect possible switching frequency effects. It reduces the computational burden but generates experimental results far from the real operation conditions. Further, the required stability and accuracy

occur when a virtual impedance is inserted into the simulated model with the same value as the physical system's internal impedance [3]. Thus, estimating EuT equivalent impedance can improve the PHIL experimental system stability. In this sense, this paper proposes a PHIL power interface algorithm (PIA) based on a twin digital system implemented through a learning-based Virtual Impedance (VI) control approach to overcome the drawbacks mentioned earlier. The proposed learning method continuously adjusts virtual impedance during the experiment based on impedance measurements of the EUT. The experimental results obtained from a PHIL laboratory setup demonstrate the effectiveness of the proposed method.

Fig. 1 Main differences between HIL and PHIL

#### II. CONFIGURATION OF THE PROPOSED PHIL SETUP

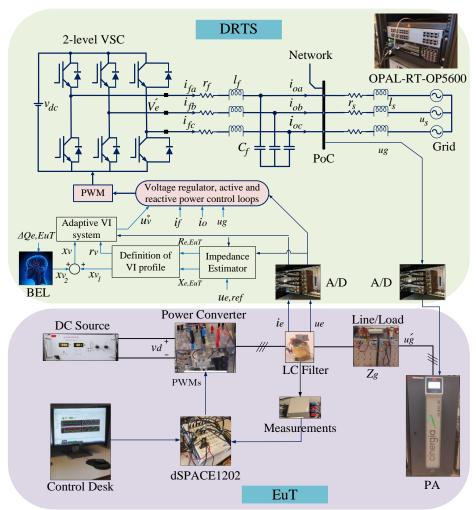

Fig. 1 shows the block diagram of the PIA used in the proposed PHIL. It is based on a hybrid twin system that interconnects the DRTS simulated model and EuT by interchanging the point of connection (PoC) voltages  $(u_a)$ and EuT output voltages and currents ( $u_e$  and  $i_e$ ). The PHIL experimental setup includes the following main components: (1) DRTS - OPAL-RT - OP5600; (2) Power Grid Emulator and PA - CINERGIA; (3) EuT - Semikron Two-Level Voltage Source Inverter (VSI), DC Power Supply, Drive Unit, LC Filter, and LEM Sensors; (4) Control Fast Prototype System - dSPACE Microlab 1202; (5) AC/DC Controlled Load - CINERGIA. This setup is realized based on RT-LAB environment of Opal-RT and dSPACE control environment MATLAB/Simulink. A windows-based host computer interconnects both OP5600 and DS1202 through TCP/IP protocol. OP5600's fast analog-digital (i.e., ADC or DAC converters) or digital output-input interfaces (i.e., I/O) interface OP5600 and DS1202. In the DS1202, the interconnection with the power converter or OP5600 employs I/O ports and BNC connectors. In contrast, DB-37 rear connectors access the I/O ports and AD/DA converters. For that reason, a dedicated PCB was manufactured to interconnect those connectors to BNC's cables, as presented in Fig. 2. This adaptation permits that BNC cables interconnect OP5600 with the DS1202 or power grid emulator (i.e., CINERGIA). In this setup, the real-time simulations are executed synchronously in both systems (i.e., OP5600 and DS1202-CINERGIA), demanding bidirectional communications of measurements and commands. The control algorithms executed in both systems (i.e., OP5600 and DS1202) employ a sampling rate of 20µs. The interconnection between the OP5600 and DS1202 follows the concept of twin systems for permitting the simultaneous dynamic evaluation of both systems with the same power conditions.

A grid-connected voltage source converter, operating as a GFC, implements both EuT and DRTS. The EuT is interconnected to the PA through the line impedance  $(z_s)$ . The implementation of the GFC incorporates a VSI connected to the PCC via an LC filter, regulated by a PI controller and a voltage regulator, according to Fig. 1. The details about the modeling and control strategies employed in the proposed GFC is addressed in next section. In addition, PIA employs a learning-based impedance shaping approach for assuring system stability. The proposed impedance shaping approach comprises an equivalent grid impedance estimator block, a VI profile definition block, adaptive VI system block and an intelligent method based on brain emotional learning (BEL), as shown in Fig. 2. In this scheme, the PIA is based on an ideal transformer model, in which the controlled voltage sources  $u'_e$  and  $u'_g$  represent the interaction between EuT and PoC. The controlled current source refers to the EuT output current used for emulating the virtual impedance. In Fig. 2,  $z_e = r_e + jx_e$  is the estimated equivalent impedance;  $r_v$  and  $x_v$  are VI components.  $x_{v2}$  is implemented through the BEL approach and added to  $x_{v1}$  to reach the X/R control objectives.

#### III. MODELING AND CONTROL

The voltage control loop uses a nested-loop control approach using conventional controllers in which the inner loop controls the filter current, and the outer loop controls the output voltage of the GFC [14]. Considering the GFC shown in Fig. 2 in the DRTS part, the power exchange between the VSI and grid can be written as follows:

$$P_{e,DRTS} = \frac{u_g u_s}{z_s} \cos(\varphi - \theta) - \frac{u_s^2}{z_s} \cos(\varphi)$$

(1)

$$Q_{e,DRTS} = \frac{u_g u_S}{z_S} \sin(\varphi - \theta) - \frac{u_S^2}{z_S} \sin(\varphi)$$

(2)

where  $V_g$  and  $V_s$  represent the root-mean-square (RMS) of voltages of the VSI, and the grid, respectively;  $\theta$  is power angle; and  $z_s < \varphi$  is line impedance. When the line impedance represents an inductive profile with a slight value of  $\theta$ , (1) and (2) can be given as:

$$P_{e,DRTS} = \frac{u_g u_S}{\chi_S} \theta \tag{3}$$

$$Q_{e,DRTS} = \frac{u_g}{X_S} (u_g - u_S) \tag{4}$$

where  $X_s = \omega l_s$  is the reactance of the line impedance.

Fig. 2 Configuration of the proposed PHIL setup

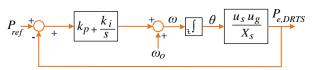

Proportional-integral (PI) controllers are commonly used to regulate signals with constant reference for reaching zero steady-state errors and could also be used in active and reactive power control loops. Traditionally, the gains of PI controllers are tuned for providing a control action with a fast and damp response. However, a modified controller tuning method should be employed to achieve the required inertia feature [15]. The control diagram of the active power loop is shown in Fig. 3. When the transfer function of a PI controller used, the active power regulating transfer function becomes

$$\frac{P_{e,DRTS}}{P_{ref}} = \frac{2\xi\omega_n + \omega_n^2}{s^2 + 2\xi\omega_n + \omega_n^2}$$

(5)

in which

$$\xi = \frac{\frac{u_g u_S}{X_S} k_p}{2\omega_n} \tag{6}$$

$$\omega_n = \sqrt{\frac{u_g u_s}{X_s} k_i} \tag{7}$$

where  $k_p$  and  $k_i$  are the controller gains of the PI employed in the active power control loop. This controller is named the Energy-PI controller [15] since it uses the

concept of power synchronizing, which distinguishes it from the objectives of a standard PI regulator. The reactive power control loop also employs a PI controller to suitably regulate the GFC's voltage.

Fig. 3 Control block diagram of the active power control loop

#### IV. LEARNING-BASED IMPEDANCE SHAPING APPROACH

As mentioned earlier, the proposed impedance shaping approach includes an equivalent grid impedance estimator block, a VI profile definition block, BEL-based VI system block. The output current and voltage of the EuT is used for emulating the VI in the DRTS. The following section describes their functionalities and how their integration adaptably shapes the equivalent grid impedance in the DRTS.

## A. Equivalent Grid Impedance Estimation

In order to estimate the equivalent impedance with a virtual impedance, the following procedure can be used [14]:

Initially, active and reactive powers related to the equivalent impedance can be calculated as:

$$P_{s} = \delta v_{s\alpha} i_{e\alpha} + \delta v_{s\beta} i_{e\beta} \tag{8}$$

$$Q_s = \delta v_{s\alpha} i_{e\beta} - \delta v_{s\beta} i_{e\alpha} \tag{9}$$

where  $\delta v_{s\alpha\beta} = u_{e\alpha\beta,ref} - u_{e\alpha\beta}$  is the voltage difference between the reference and output voltages of the EuT; and  $i_{e\alpha}$  is the current measurements at the PCC in the EuT part. Given that the system is balanced and symmetric, the module of the equivalent impedance could be estimated as follows:

$$Z_{e,EuT} = \frac{u_{e\alpha,ref}(rms)}{I_{e\alpha}(rms)} = \frac{u_{e\beta,ref}(rms)}{I_{e\beta}(rms)}$$

(10)

The resistance and reactance components of  $Z_e$  denote its real and imaginary parts, which can be given as:

$$R_{e,EuT} = \frac{Z_e P_s}{S_a} \tag{11}$$

$$X_{e,EuT} = \frac{z_e Q_s}{s_a} \tag{12}$$

where  $S_a = \sqrt{{P_s}^2 + {Q_s}^2}$  is the apparent power corresponding to the equivalent impedance. The proposed procedure reasonably estimates the resistive and reactive parts of the EuT's equivalent impedance. Then, it is used to find the suitable VI in the DRTS needed for achieving accuracy for PHIL experiments.

#### B. Definition of VI profile

The VI profile definition block represents the VI profile to achieve the same X/R ratio in the EuT based on its impedance estimation and availability of inverter power. The VI implementation uses an RL branch comprising virtual resistance and inductance. The error metric of (13) can then be calculated directly from the estimated impedance of the EuT ( $Z_{e,EuT} = R_{e,EuT} + jX_{e,EuT}$ ) and the estimated impedance of the DRTS ( $Z_{g,DRTS} = R_{g,DRTS} + jX_{g,DRTS}$ ). It should be noted that the procedure defined in section IV.A with  $u_e$  and  $i_e$  replaced by  $u_g$  and  $i_o$  (voltage and current measurements at the PCC in the DRTS part) can be employed to estimate the equivalent grid impedance in DRTS.

$$Z_{dif} = ||Z_{e,EuT}| - |Z_{g,DRTS}|| \tag{13}$$

Given the calculated metric, the value of virtual resistance and reactance  $(r_v \text{ and } x_v)$  is calculated by

$$r_v = \mu \times Z_{dif} \tag{14}$$

$$x_{v} = \gamma \times Z_{dif} \tag{15}$$

where  $\mu$  and  $\gamma$  are the reduction factors and determined based on the inverter stability limits and minimum error metric. The value of  $x_{\nu}$  is shared into two parts

determined using a distribution factor  $\lambda$ , which results in  $x_{v2} = \lambda x_v$  and  $x_{v1} = (1 - \lambda)x_v$ . The virtual reactance  $x_v$  uses a variable structure scheme, in which,  $x_{v1}$  follows the standard implementation and  $x_{v2}$  uses a BEL-based approach for compensating unmodeled disturbances and considering possible grid impedance variations and estimation inaccuracies of the EuT.

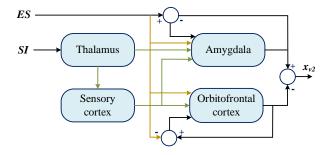

### C. BEL-based virtual impedance control approach

Motivated by the limbic system in the human brain, computer-based models can be designed to simulate various characteristics of the emotional system. This method is constituted of Amygdala, which is in charge of emotional learning; Orbitofrontal cortex, sensory cortex, and Thalamus [16], [17]. The model is provided with two inputs including sensory input (SI) and emotional signal (ES). Preprocessing on SI signal such as filtering or noise reduction is performed by the Thalamus. The sensory cortex receives the Thalamus output and then submits it to the Amygdala and Orbitofrontal cortex. A simplified layout of the BEL method employed in this study is shown in Fig. 4. The details about this approach can be found in [17]. To achieve the promising execution of the BEL method, making a relation between SI, ES, and output  $(x_{v2})$  is critical. The SI and ES inputs for the BEL to produce  $x_{v2}$  are written as follows.

$$SI = \tau_{1}(Q_{ref} - Q_{e,EuT}) + \tau_{2} \int (Q_{ref} - Q_{e,EuT}) dt$$

$$ES = \tau_{3}(Q_{ref} - Q_{e,EuT}) + \tau_{4} \int (Q_{ref} - Q_{e,EuT}) dt + \mu_{5} x_{v2}$$

(16)

where the weighting factors  $\tau_1, \tau_2, \tau_3$ , and  $\tau_4$  are calculated via a trial-and-error procedure. The functions S and ES are chosen as the outputs of a PI block in response to reactive power error  $(Q_{ref}-Q_{e,EuT})$  in EuT part.

Fig. 4 A simplified structure of BEL method

#### V. EXPERIMENTAL RESULTS

Experimental results obtained from a PHIL laboratory setup composed of DRTS, OP5600, and an EuT implemented by a GGC, controlled by a dSPACE, DS1202, have been carried out to validate the proposed method. The parameters of the system are given in Table 1. In the beginning, the DRTS sends the reference to the PA in an open-loop condition.

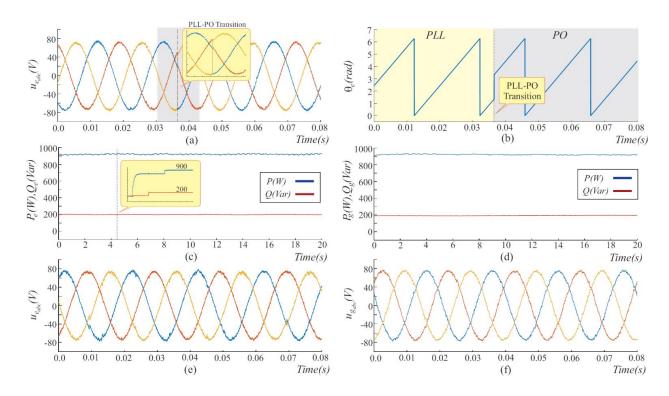

Fig. 5 PHIL experimental results; (a) EuT voltage waveforms during the startup procedure, (b) EuT voltage vector angle during the startup scheme, (c) EuT steady-state active and reactive powers, (d) DRTR simulated-model, steady-state, active and reactive powers, (e) EuT steady-state voltage waveforms, and (f) DRTS voltage waveforms.

Table 1 Parameters of the setup

| Description                       | Value                               |

|-----------------------------------|-------------------------------------|

| Grid voltage (RMS)                | 70                                  |

| Grid's nominal angular speed      | 100 πrad/s                          |

| Nominal frequency                 | 100 πrad/s                          |

| Line impedance                    | $3.6 \text{ mH}$ and $0.2\pi\Omega$ |

| LC-filter                         | 2.4 mH and 15 μF                    |

| Inverter rating                   | 1 kW                                |

| Voltage magnitude reference (RMS) | 70                                  |

| DC-side voltage                   | 200                                 |

| Switching frequency               | 20 kHz                              |

| Sampling time                     | 20 μs                               |

|                                   |                                     |

Then, the EuT synchronizes to the PA by using a synchronous- reference-frame phase-locked-loop (SRF-PLL). Thus, a transition scheme is employed to substitute the PLL to the power oscillator (PO) scheme to generate the suitable voltage vector, providing the required EuT power delivery. Figs 5(a) and 5(b) present the EuT voltage waveforms and voltage vector angle during this procedure. Also, the controlled active and reactive powers values follow the imposed voltage vector angle determined by the PLL (i.e., 80 W and 100 VAr). After that, positive and negative power steps are inserted in both EuT active and reactive reference power values for reaching the steadystate condition with  $P_e = 900 \text{ W}$  and  $Q_e = 200 \text{ VAr}$ , as shown in Fig. 5(c). The PIA reproduces the same power conditions at DRTS, as depicted in Fig. 5(d). Finally, Figs. 5(e) and 5(f) present the three-phase voltage waveforms in

the steady-state condition for both EuT and DRTS systems. The results demonstrate the accuracy and coherence of the experimental results obtained from the EuT and DRTS simulation.

#### VI. CONCLUSION

This paper has proposed a PHIL power interface algorithm based on a digital twin system, implemented through a learning-based virtual impedance control approach. The suitable impedance value is determined by estimating the EuT equivalent impedance. The proposed PIA uses a power converter model with the same EuT control approach in the DRTS simulation, in which a virtual scheme is employed for inserting the system's required impedance, thereby assuring the required stability. Experimental results obtained from the PHIL laboratory setup validate the proposed solution and demonstrate its effectiveness. The main features of the proposed PHIL testbed are: 1) Flexible DRTS for covering device-level studies (e.g., power converters) to systemlevel evaluations (e.g., full-scale energy systems); 2) Cosimulation of multiple power/energy networks through web interconnection; 3) Emulation of several operation scenarios such as faults, asymmetries, harmonic conditions, and frequency variation; 4) Interface EUT -DRTS implemented using digital twin systems; 5) Interconnection of different load types and energy storage

systems (ESS) with different technologies and dynamic behaviors.

#### **ACKNOWLEDGMENT**

This work was supported by the Reliable Power Electronic- Based Power Systems (REPEPS) project at the AAU Energy Department, Aalborg University, as a part of the Villum Investigator Program funded by the Villum Foundation.

#### REFERENCES

- [1] W. Du, R. H. Lasseter, and A. S. Khalsa, "Modular elliptic curves and fermat's last theorem," *IEEE Trans. Smart Grids*, vol. 10, no. 4, pp. 3515-3524, 2019.

- [2] B. Lundstrom and M. Salapaka, "Optimal power hardware-in-the-loop interfacing: applying modern control for design and veri\_cation of high-accuracy interfaces," *IEEE Trans. on Ind. Electron*, vol. 68, no. 11, pp. 10388-10399, 2020.

- [3] C. S. Edrington, M. Steurer, J. Langston, T. El-Mezyani, and K. Schoder, "Role of power hardware in the loop in modeling and simulation for experimentation in power and energy systems," In Proceedings of IEEE, vol. 103, no. 12, pp. 2401–2409, 2015

- [4] A. S. Vijay et al., "Real-time testing approaches for microgrids," *IEEE Journal of emerg. and select. topics in Power Electron.*, vol. 5, no. 3, pp. 1356–1376, 2017.

- [5] J. Langston, et al., "Megawatt-scale power hardware-in-the-loop simulation testing of a power conversion module for naval applications," in Proc. IEEE Elect. Ship Technol. Symp., pp. 268–275, 2015.

- [6] A. Benigni and A. Monti, "A parallel approach to real-time simulation of power electronics systems," *IEEE Trans. Power Electron.*, vol. 30, no. 9, pp. 5192–5206, 2015.

- [7] G. Li, D. Zhang, Y. Xin, S. Jiang, W. Wang, and J. Du, "Design of MMC hardware-in-the-loop platform and controller test scheme," *CPSS Trans. on Power Electron. and Applicat.*, pp. 143–151, 2019.

- [8] P. C. Kotsampopoulos et al., "The limitations of digital simulation and the advantages of phil testing in studying distributed generation provision of ancillary services, *IEEE Trans. Ind. Electron.*, vol. 62, no. 9, pp. 2285–2290, 2016.

- [9] F. M. El-Sousy et al., "A High-Speed Microturbine PMa-SynRG Emulation Using Power Hardware-in-the-Loop for Wind Energy Conversion Systems," *IEEE Access*, vol. 8, no. 0, pp. 194 612–194 622, 2020.

- [10] Y. J. Kim and J. Wang, "Power hardware-in-the-loop simulation study on frequency regulation through direct load control of thermal and electrical energy storage resources," *IEEE Trans. Smart Grid*, vol. 9, no. 4, pp. 2786– 2796, 2018.

- [11] A. Riccobono, E. Liegmann, M. Pau, F. Ponci, and A. Monti, "Online parametric identification of power impedance to improve stability and accuracy of power hardware-in-theloop simulations," *IEEE Trans. Instrum. Meas.*, vol. 66, no. 9, pp. 2247–2257, 2017.

- [12] N. D. Marks, W. Y. Kong, and D. S. Birt, "Stability of a switched mode power amplifier interface for power hardware-in-the-loop," *IEEE Trans. Ind. Electron.*, vol. 65, no. 11, pp. 8445–8454, 2018.

- [13] G. Lauss and K. Strunz, "Accurate and stable hardware-inthe-loop (hil) real-time simulation of integrated power electronics and power systems," *IEEE Trans. Power Electron.*, vol. 36, no. 9, pp. 10 920–10 932, 2021.

- [14] R. L. de Araujo Ribeiro, A. Oshnoei, A. Anvari-Moghaddam, F. Blaabjerg, "Adaptive Grid Impedance

- Shaping Approach Applied for Grid-Forming Power Converters," *IEEE Access*, vol. 10, pp. 83096 –83096, 2022.

- [15] W. Zhang, D. Remon, A. Mir, A. Luna, J. Rocabert, I. Candela, and P. Rodriguez, "Comparison of different power loop controllers for synchronous power controlled gridinteractive converters," in Proc. IEEE Energy Conversion Congress Exposition (ECCE), pp. 3780–3787, Montreal, CA, Sep. 2015.

- [16] M. S. O. Yeganeh, A. Oshnoei, N. Mijatovic, T. Dragicevic and F. Blaabjerg, "Intelligent Secondary Control of Islanded AC Microgrids: A Brain Emotional Learning-Based Approach," in IEEE Transactions on Industrial Electronics, vol. 70, no. 7, pp. 6711-6723, July 2023, doi: 10.1109/TIE.2022.3203677.

- [17] A. Oshnoei, O. Sadeghian and A. Anvari-Moghaddam, "Intelligent Power Control of Inverter Air Conditioners in Power Systems: A Brain Emotional Learning-Based Approach," in *IEEE Transactions on Power Systems*, 2022, doi: 10.1109/TPWRS.2022.3218589.