# **Aalborg Universitet**

# A Comparative Study on Parasitic Capacitance in Inductors With Series or Parallel Windings

Zhao, Hongbo; Yan, Zhixing; Luan, Shaokang; Dalal, Dipen Narendra; Jorgensen, Jannick Kjar; Wang, Rui; Zhou, Xiang; Beczkowski, Szymon Michal; Rannestad, Bjorn; Munk-Nielsen, Stig

Published in:

**IEEE Transactions on Power Electronics**

DOI (link to publication from Publisher): 10.1109/TPEL.2022.3187449

Creative Commons License CC BY-NC-ND 4.0

Publication date: 2022

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA): Zhao, H., Yan, Z., Luan, S., Dalal, D. N., Jorgensen, J. K., Wang, R., Zhou, X., Beczkowski, S. M., Rannestad, B., & Munk-Nielsen, S. (2022). A Comparative Study on Parasitic Capacitance in Inductors With Series or Parallel Windings. *IEEE Transactions on Power Electronics*, 37(12), 15140-15151. https://doi.org/10.1109/TPEL.2022.3187449

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 04, 2025

# A Comparative Study on Parasitic Capacitance in Inductors With Series or Parallel Windings

Hongbo Zhao, *Member, IEEE*, Zhixing Yan, Shaokang Luan, Dipen Narendra Dalal, Jannick Kjær Jørgensen, Rui Wang, *Student Member, IEEE*, Xiang Zhou, *Member, IEEE*, Szymon Michal Bęczkowski, Bjørn Rannestad, and Stig Munk-Nielsen, *Member, IEEE*

Abstract—In high-power medium-voltage applications, inductors usually have multiple windings on a single core, due to the high inductance value and high current stress. The multiple coils are electronically connected in either series or parallel, with considerations of windings loss and cost. However, the differences in parasitic capacitance of inductors using parallel and series connections are not discussed. Therefore, this article reveals that in comparison to parallel connections for windings, utilizing series connection for winding can significantly reduce the parasitic capacitance in multiwindings inductors without sacrificing the power density and adding manufacturing complexities. Physics-based models of parasitic capacitance in inductors with round-cable and copper-foil windings are developed for theoretical analysis. According to the theoretical analysis, the equivalent capacitance contributed by the stored electric field energy between two layers can be halved at least. The theoretical analysis is also verified by FEM simulations. Six prototyped inductors are experimentally compared to validate the theory.

*Index Terms*—Inductors, multiple windings, parasitic capacitance, parallel connections, series connections.

# I. INTRODUCTION

ASSIVE components are essential in power electronic converters [1], [2]. For the converters utilizing wideband-gap devices [3], [4], the parasitic capacitance in magnetic components, including inductors [5], [6], transformers [7], and motors [8], is of significant importance due to the fast switching characteristics (high dv/dt value) of the wideband-gap devices [8], [9]. It is reported that such parasitic capacitance can significantly

Manuscript received 29 December 2021; revised 29 March 2022 and 7 June 2022; accepted 14 June 2022. Date of publication 30 June 2022; date of current version 6 September 2022. This work was supported in part by MVolt project is cofunded by the Department of Energy Technology of Aalborg University, Innovation Fund Denmark, Siemens Gamesa, Vestas Wind System, and KK wind solutions and in part by PH-Mag is an internal project funded by Aalborg University. Recommended for publication by Associate Editor W. Huang. (Corresponding author: Zhixing Yan.)

Hongbo Zhao, Zhixing Yan, Shaokang Luan, Dipen Narendra Dalal, Jannick Kjær Jørgensen, Rui Wang, Szymon Michal Beczkowski, and Stig Munk-Nielsen are with the Department of Energy Technology, Aalborg University, 9220 Aalborg, Denmark (e-mail: hzh@et.aau.dk; zhya@energy.aau.dk; slu@energy.aau.dk; dnd@et.aau.dk; jkj@et.aau.dk; rwa@et.aau.dk; sbe@et.aau.dk; smn@et.aau.dk).

Xiang Zhou is with the College of Electrical Engineering, Xi'an Jiaotong University, Xian 710049, China (e-mail: pecel\_zhouxiang@163.com).

Bjørn Rannestad is with the KK Wind Solutions, 7430 Ikast, Denmark (e-mail: bjran@kkwindsolutions.com).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TPEL.2022.3187449.

Digital Object Identifier 10.1109/TPEL.2022.3187449

contribute to the capacitive current during the switching transients [10] and may result in increased conducted noise and increased switching energy dissipation in the transistors [11]–[14]. In [15] authors indicated that the parasitic capacitance is more important in medium-voltage applications since more electrical field energy is stored in the parasitic capacitors due to the higher voltage. Especially for medium-voltage SiC MOSFETs, greater than 99% is reported for kVA rated efficiency in converters at 5–10 kHz switching frequency with hard switching [16], where the parasitic resistance (skin and proximity effects) are not dominant, but the parasitic capacitance will be more significant due to the ultrafast switching speed (dv/dt up to 250 V/ns) [8]. Therefore, modeling and reducing parasitic capacitance is important for novel medium voltage power electronics systems enabled by advanced medium voltage SiC MOSFETs [17], [18].

Both physics-based [19], [20] and behavior-based [21], [22] modeling methods can be used to identify the parasitic capacitance and capacitive couplings in inductors. For reducing the parasitic capacitance in the inductors, besides using advanced dielectric material with lower permittivity, two main solutions have been researched: 1) Using spacers to decrease the electric field between the two plates [23], [24], at the cost of the power density. 2) Using advanced winding structures to decrease the electric field strength between the two adjacent plates [25], sacrificing manufacturing simplicity. The physical insights of the two main methods could be revealed by physics-based modeling methods of parasitic capacitance [26], [27].

To obtain the same current ripple to 15–30% ratio in medium-voltage inductors, a larger inductance value is required compared with low-voltage inductors at the same power rating. This implies a larger number of turns [14], [28], where multiple windings have to be placed [29]. Therefore, more electric field energy will be stored by the multiple windings and larger parasitic capacitance is introduced [19], [20]. More notably, in order to achieve lower dc/ac resistance and to simplify the manufacturing process (lower bending torque requirement), multiple windings are usually preferred to be electrically connected in parallel [30]. The multi-windings of inductors connected in either parallel or series can also be ruled by cost and manufacturing complexity.

However, no previous research has reported and studied the difference in parasitic capacitance in inductors between using the series connection and parallel connections of multiwindings. Therefore, a research gap can be identified as the potential impacts and analysis of using a series connection or parallel

connection of multiwindings on parasitic capacitance. Thus, this article analyzes and compares the parasitic capacitance in multiwinding inductors with parallel or series connections. The model is developed based on the winding layout, geometrical structures, and material parameters. The analytical analysis theoretically proves that the parasitic capacitance in inductors using parallel connections and series connections is significantly different.

Compared to the previous research, the main contributions of this article are summarized as follows:

- This article indicates that the parasitic capacitance of inductors can be significantly reduced by using the series connections of multiple windings, especially for the inductors that have more electric fields stored between adjacent layers. The theoretical analysis is addressed using physics-based modeling methods.

- 2) Both round-cable-based [20] and copper-foil-based [29] inductors are compared and analyzed, where this article concludes that using series connections of multiwindings in round-cable-based inductors can reduce more parasitic capacitance compared to the copper-foil-based inductors.

The remaining of this article is organized as follows. Section II gives a brief overview of the methodologies or approaches for reducing parasitic capacitance in multiwinding inductors. Section III presents the theoretical analysis and comparison of multiwinding inductors using either parallel connections or series connections. Both round-cable- and copper-foil-based inductors are discussed in Section III. In Section IV, the FEM simulations are presented to verify the theoretical analysis. Six prototyped inductors using the parallel connection and series connection of windings are shown to verify the theoretical analysis in Section V. Finally, Section VII concludes this article.

#### II. BRIEF OVERVIEW ON STATE OF THE ART

As introduced in [19], [20], [24], and [25], the parasitic capacitance of inductors is contributed by the energy stored inside the winding  $E_{\rm intra}$ , between the winding and core  $E_{\rm wc}$ , and between the two neighbor windings  $E_{\rm ww}$ , and therefore, could be written as (1). Then, the total capacitance can be represented by (2).  $C_{\rm intra}$  is the intrawinding capacitance contributed by the electric field energy between two neighbor turns, and the electric field energy between two layers.  $C_{\rm wc}$  is the capacitance contributed by the electric energy stored between winding and core,  $C_{\rm ww}$  is the capacitance between two windings

$$E_{\text{total}} = E_{\text{intra}} + E_{\text{wc}} + E_{\text{ww}} \tag{1}$$

$$C_{\text{total}} = C_{\text{intra}} + C_{\text{wc}} + C_{\text{ww}}.$$

(2)

According to previous research [20], [29],  $C_{\rm ww}$  usually has a very limited impact on the total equivalent capacitance due to the small overlapping area. Therefore, if  $C_{\rm wc}$  and  $C_{\rm intra}$  can be significantly reduced,  $C_{\rm total}$  can be reduced.

The parasitic capacitance in inductors could be reduced by adopting state of the art solutions such as using advanced dielectric material with low relative permittivity, as well as using improved geometrical structures and layout of windings according to the state of the arts.

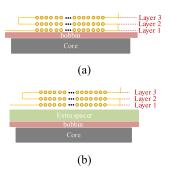

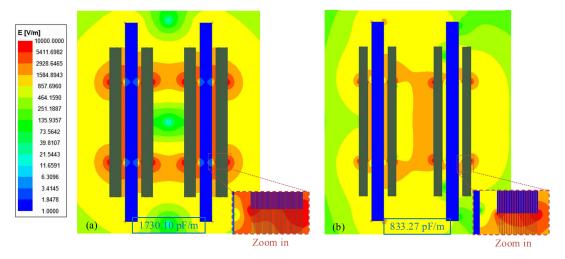

Fig. 1. Schematics of round-cable based inductors. (a) Original solution. (b) Improved solution with extra spacers between winding and core.

Fig. 2. Schematics of round-cable-based inductors with reduced layer-to-layer capacitance. (a) Using extra spacers between two adjacent layers. (b) Using the "flyback" winding layout.

# A. Reducing Capacitance $C_{wc}$ Between Winding and Core

In order to reduce  $C_{\rm wc}$ , spacers could be added between the inner layer of winding and the core. Fig. 1(a) is the original design without any spacers, Fig. 1(b) is the improved design with spacers. Obviously, using extra spacers in Fig. 1(b) will will result in larger area occupied by the windings occupied by the winding. According to the physics-based modeling of inductors, with a larger thickness of the extra spacer,  $C_{\rm wc}$  will become smaller.

# B. Reducing Intrawinding Capacitance Cintra

$C_{\rm intra}$  is contributed by the capacitance between two adjacent layers  $C_{ll}$  and between two adjacent turns  $C_{\mathrm{tt}}$ , however,  $C_{\mathrm{tt}}$  can be neglected due to the large number of turns [20]. In order to reduce  $C_{ll}$ , both extra spacers and improved winding structures can be utilized, as shown in Fig. 2. According to Fig. 2(a), using spacers between two adjacent layers can reduce the electric field energy stored in-between. However, it requires to have spacers between any two adjacent layers, which will further reduce the power density of the inductor. Similar to  $C_{\rm wc}$ , if the thickness of spacers is larger,  $C_{ll}$  will become smaller. As shown in Fig. 2(b),  $C_{ll}$  can also be reduced by around 8% using the "flyback" winding structure [25], without sacrificing the power density of winding but with increasing the manufacturing complexity. Other improved designs of winding are also reported, however, the reduced capacitance is still limited by either sacrificing winding power density or increasing manufacturing complexity.

#### C. Summary

According to the brief overview, there is no efficient method that can significantly reduce parasitic capacitance in inductors without sacrificing the power density of winding and increasing the manufacturing complexity.

Especially for medium-voltage inductors, due to the requirement of grounding of the core and the frame, a bobbin [23] and / or an extra spacer between the winding and core is provided for required dielectric satrength dielectric strength. Therefore, the winding to core capacitance  $C_{\rm wc}$  could be reduced by the spacers between winding and core, and consequentially the layer-to-layer capacitance  $C_{ll}$  becomes dominant in such inductors.

Besides, state of the art does not discuss the impacts of parasitic capacitance using series or parallel connections of multiwindings, which is interesting and important to investigate.

#### III. ANALYSIS USING PHYSICS-BASED MODELING METHOD

In this section, the physics-based modeling method is implemented in calculating parasitic capacitance in round-cable-based and copper-foil-based inductors, with both parallel and series connections of multiwindings. Two different capacitance, static capacitance and dynamic capacitance are mentioned in this section. The static capacitance is only dependent on the geometrical structure [29], [31]. The dynamic capacitance is dependent on the static capacitance [28], [31], and the actual voltage potential distribution across, where it is usually assumed to be linearly distributed in practice [25], [29], [32]. The dynamic capacitance mentioned in this article is the practical capacitance identified in real inductors [19].

For fair comparison of the inductors using either parallel or series connections of multiwindings, the researched cases in this article are constrained by the same electrical conductivity (cross-sectional area of the conductor), same inductance (same number of turns and same core structure), and the same main winding parameters (using the same winding layout, bobbins, and spacers). In this section, most parameters are parametrized values instead of constant values, therefore, the conclusions are valid for many cases and can be easily extended to more situations.

#### A. Round-Cable-Based Inductors With Two Windings

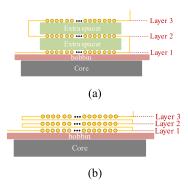

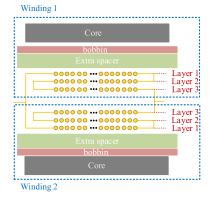

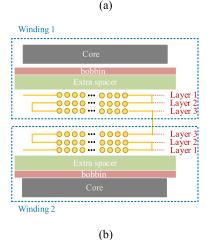

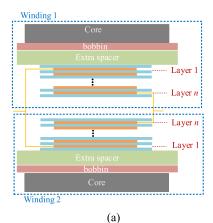

Fig. 3 shows the schematic of round-cable-based inductors with two windings in series and parallel connections.

As a constraint, the total effective cross-sectional areas (the same current rating) of the two inductors are designed as the same. Therefore, the inductor with series winding must have a larger wire diameter compared to the inductor with the parallel winding of the same power level. The two inductors considered in this studies have the with similar core structures, the same number of turns, and the same length of the air gap.

For developing the physics-based model, Table I summarized the critical geometrical parameters of the two inductors.

Since the resistivity of amorphous core and silicon steel is relatively low, the core is assumed to be a "perfect conductor," which has no ohmic voltage drop [19], [32]. Similar to the

Fig. 3. Schematics of two-winding three-layer round-cable based inductors.(a) Windings are connected in parallel. (b) Windings are connected in series.

TABLE I

KEY PARAMETERS OF THE ROUND-CABLE-BASED INDUCTOR

| Description                                                   | Symbol<br>(Parallel case) | Symbol<br>(Series case) |

|---------------------------------------------------------------|---------------------------|-------------------------|

| The radius of the cable                                       | $r_0$                     | $1.41r_0$               |

| The average length of the air gap between two adjacent layers | p                         | p                       |

| The average length of per turn for three layers               | l                         | 1                       |

| Number of turns of per layers                                 | n                         | n/2                     |

| Number of layers                                              | 3                         | 3                       |

| Number of the winding                                         | 2                         | 2                       |

state-of-the-art modeling methods, the voltage potential on the winding is assumed to be linearly distributed [19], [32].

To simplify the theoretical derivations, the parasitic capacitance contributed by the electric energy stored between two windings is considered very small in this article, since the distance between the two windings is usually large and can only contribute to a very small parasitic capacitance to the system.

Also, the coating material on the cable is neglected to simplify the physics-based modeling.

As mentioned previously, due to the extra spacers decreasing the electric field strength between the winding and core, the capacitance  $C_{\rm wc}$  contributed by the stored electric field energy could be reduced by the distance between the inner layer and core, where the relevant derivations are elaborated in [19] and [20]. The total equivalent capacitance contributed by two adjacent turns in the same layer is relatively small and, therefore, is not discussed in this article. Therefore, this article will only emphasize modeling and comparing  $C_{ll}$  ( $C_{\rm intra}$ ).

If there is an air gap between the two adjacent layers, most electric field energy will be stored in the air instead of the coating of cables, where the static layer-to-layer capacitance of inductors with parallel winding is represented as (3). Detailed derivation could be found in [20]

$$C_{sta-par} = nl \int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} \frac{\varepsilon_0 r_0}{p + 2r_0 (1 - \cos \theta)} d\theta$$

(3)

where  $\varepsilon_0$  is the value of permittivity in a vacuum.

The static layer-to-layer capacitance of inductors with series winding is represented as (4), where the only difference is the radius of the conductor. Detailed derivation could be found in [20]. It can be found that  $C_{sta-ser}$  is always small than  $\sqrt{2}$  the times of  $C_{sta-par}$

$$C_{sta-ser} = \frac{nl}{2} \int_{-\frac{\pi}{2}}^{\frac{\pi}{2}} \frac{\sqrt{2}\varepsilon_0 r_0}{p + 2\sqrt{2}r_0(1 - \cos\theta)} d\theta$$

$$C_{sta-ser} < \frac{\sqrt{2}}{2} C_{sta-par}.$$

(4)

The electric energy is stored between two adjacent layers due to the voltage drops on the windings. Snelling [19], Zhao *et al.* [20], and Biela and Kolar [25] elaborated the derivations of calculating stored electric energy between two adjacent windings according to the linear voltage potential distribution. Therefore, based on the energy-conservation-law of the electric field [19], [20], [25], the dynamic capacitance (equivalent capacitance of electric field energy) of inductors with parallel winding can be represented as

$$C_{ll-par} = \frac{16}{27} C_{sta-par} \tag{5}$$

where (5) is only available for two-winding three-layer inductors. However, it is feasible to extend the equation to inductors with more windings and layers.

Similarly, the dynamical capacitance of the inductor with parallel winding can be derived as

$$C_{ll-ser} = \frac{4}{27}C_{sta-ser}. (6)$$

If the  $C_{sta-ser}$  is the same as  $C_{sta-par}$ , it will imply that using the series connection of multiple winding can reduce 75% of the capacitance contributed by the energy stored between adjacent layers in round-cabled based inductors.

Indeed, due to the smaller number of turns is used in round-cable-based inductors,  $C_{sta-ser}$  should be smaller than  $C_{sta-par}$ . Therefore, the equivalent layer-to-layer capacitance  $C_{ll-ser}$  in

TABLE II

KEY PARAMETERS OF THE ROUND-CABLE-BASED INDUCTOR

| Description                    | Parallel connection | Series connection |

|--------------------------------|---------------------|-------------------|

| Width of winding               | $nr_0$              | $0.705nr_0$       |

| Total thickness of the winding | $p_1+2p+3r_0$       | $p_1+2p+4.242r_0$ |

\*It is assumed that the turns are placed close to the neighbor turns in the same layer.  $p_1$  is the distance between the inner layer and core

TABLE III

KEY PARAMETERS OF THE COPPER-FOIL-BASED INDUCTOR

| Description                                               | Symbol<br>(Parallel case)  | Symbol (Series case)   |

|-----------------------------------------------------------|----------------------------|------------------------|

| Width of copper-foil                                      | w                          | w                      |

| Thickness of copper-foil                                  | $t_{ m c}$                 | 2t <sub>c</sub>        |

| Thickness of insulating material between two foils        | $t_{ m m}$                 | $t_{ m m}$             |

| Permittivity of the insulating material between two foils | $\mathcal{E}_{\mathrm{r}}$ | $\mathcal{E}_{\Gamma}$ |

| Average length of per turn for three layers               | 1                          | 1                      |

| Number of layers per winding                              | n                          | n/2                    |

| Number of windings                                        | 2                          | 2                      |

a round-cable-based inductor with series connections of two windings should be further reduced by 25% of  $C_{ll\text{-}par}$  in a round-cable-based inductor with parallel connections. For example, in the presented case with 2 windings and 3 layers in each winding,  $C_{ll\text{-}ser}$  is around 18% of  $C_{ll\text{-}par}$ .

The area of the windings in inductors with either series or parallel connections are compared in Table II. It could be found that using series connections in round-cable-based inductors can help to achieve higher winding power density due to the smaller width of windings.

In this article, the number of layers is fixed as 3. It is worth mentioning that the parasitic capacitance contributed by adjacent layers can be further reduced by increasing the number of layers, however, the volume of winding will increase.

# B. Copper-Foil-Based Inductors With Two Windings

In copper-foil-based inductors, a single-layer copper-foil is constructed by a single foil.

To constrain the same electrical conductivity, the width of copper-foil is configured as a constant value w, where the thickness ( $t_c$ ) in series configuration is double that of parallel configuration as  $t_c$  and  $2t_c$ , respectively. The schematics of copper-foil-based two-winding inductors with parallel and series connections are shown in Fig. 4. The key parameters of their geometrical structures for modeling the parasitic capacitance

Fig. 4. Schematics of two-winding three-layer copper-foil-based inductors. (a) Windings are connected in parallel. (b) Windings are connected in series.

contributed by adjacent layers are shown in Table III. The two configurations utilizes similar insulating material (mylar).

The static capacitance of copper-foil-based inductors could be written as (7) for parallel and series connections, which are the same in this configuration due to the same width of foil

$$C_{sta-par} = C_{sta-ser} = \frac{\varepsilon_0 r_0 lw}{t_{\rm m}}. (7)$$

Since  $t_{\rm m}$  is usually very small, the static capacitance between two adjacent layers is usually very large, according to (7).

Then the dynamic capacitance  $C_{ll-par}$  of the presneted / two-winding copper-foiled inductor can be calculated as

$$C_{ll-par} = 2\frac{4(n-1)}{3n^2}C_{sta-par} = 2\frac{4(n-1)}{3n^2}\frac{\varepsilon_0 r_0 lw}{t_{\rm m}}.$$

(8)

Based on the energy-conservation law [19], the dynamical capacitance  $C_{ll-par}$  of the presented or considered two-winding copper-foiled inductor can be calculated as

$$C_{ll-ser} = \frac{4(n-2)}{3n^2} C_{sta-ser} = \frac{4(n-2)}{3n^2} \frac{\varepsilon_0 r_0 lw}{t_m}.$$

(9)

Comparing (8) and (9), it can be found that using the series connection of the two windings in copper-foil-based inductors can reduce  $C_{ll}$  by at least 50%. The parasitic capacitance in

TABLE IV

KEY PARAMETERS OF THE COPPER-FOIL-BASED INDUCTOR

| Description                | Parallel connection        | Series connection               |

|----------------------------|----------------------------|---------------------------------|

| Width of winding           | $\mathcal{W}_{\mathrm{m}}$ | $w_{ m m}$                      |

| Total thickness of winding | $nt_{c}+(n+1)t_{m}$        | $nt_{\rm c} + (n/2+1)t_{\rm m}$ |

<sup>\*</sup>  $w_{

m m}$  is the width of the mylar foil. To guarantee reliable insulation,  $w_{

m m}$  is always wider than w (width of copper foil).

inductors can be further reduced by using increased number of turns, however, it will increase the cost and winding area.

It can also be found that using a series winding structure can help to use less insulating material, e.g., in this case, the copper-foil inductor with the parallel connections requires to have 2(n+1) layers of mylar foils, where the inductor with series connection only require to have n+2 layers of mylar foils. Therefore, using the series connection in copper-foiled inductors can save cost and further increase power density depending on the thickness of copper-foil and mylar-foil. This is also reflected in the winding section area, where Table IV clearly shows the comparison of width and thickness of windings using series and parallel connections.

#### C. Comparison and Physical Insights

According to the theoretical analysis, using series connections of multiwinding can help to reduce the parasitic capacitance between two adjacent layers by 82% in round-cable-based inductors, and reduce by up to 50% in copper-foil-based inductors, compared to the inductors with parallel connections of multiwindings at the same power level and core configurations. This is because in the round-cable-based inductors, using series-connection can also reduce the capacitance contributed by two adjacent layers, where the copper-foiled-based inductors have the same electrical field strength between two adjacent foils that implies the same value of parasitic capacitance contributed by adjacent foils, with using either series or parallel connections of windings. Therefore, the reduction of parasitic capacitance using the series connection is smaller in copper-foil-based inductors, in comparison to the round-cable-based inductors.

Based on physics-based modeling, the basic difference between series and parallel connections of multiwinding configurations is that the stored energy between two adjacent layers is different. Using the parallel connections, each winding will be stressed by the full voltage drop. If the series connections are applied, the voltage drop on each winding is shared by multiple windings. According to the physics view point, with smaller voltage drop on the windings can result in less electric field energy stored in the winding, therefore, the parasitic capacitance could become smaller using the series connection of multiwindings.

It is also found that using series connections of multiwindings could help to achieve a smaller volume of windings, which is around 20% in the exampled cases. Besides, using series connections of multiwindings will not bring extra manufacturing complexity compared to the parallel windings of inductors

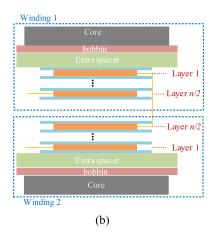

Fig. 5. Simulated results of electrical field distribution and equivalent parasitic capacitance of round-cable-based inductors. (a) Using series-connection of two windings. (b) Using parallel-connection of two windings.

TABLE V

KEY PARAMETERS OF ROUND-CABLE-BASED INDUCTORS SIMULATION

| Description                                              | Parallel | Series |

|----------------------------------------------------------|----------|--------|

| Diameter of the copper cable (same cross-sectional area) | 1.41 mm  | 2 mm   |

| Diameter of the copper cable (including insulation)      | 1.71 mm  | 2.3 mm |

| Distance between layer to core                           | 1.5 mm   | 1.5 mm |

| Distance between layer to layer                          | 1.5 mm   | 1.5 mm |

| Distance between turn to turn                            | 0.1 mm   | 0.1 mm |

| Number of layers per winding                             | 3        | 3      |

| Number of turns per windings                             | 48       | 24     |

#### IV. FINITE-ELEMENT-METHOD SIMULATIONS

In this section, the FEM-based simulations are presented to verify the theoretical analysis. Both round-cable and copperfoil-based inductors are studied using FEM analysis. The Ansys Maxwell is used to simulate the electric-field distribution and extract the total equivalent capacitance. In order to reduce the computation complexity, the three-dimensional (3-D) simulation of inductors is simplified to 2-D models [33], where the results can be easily integrated by the length of turns. The voltage potential of the winding is assumed to be linearly distributed, where each turn/foil is configurated as a discrete value from 0 V to (*N*-1) V, and *N* is the number of turns.

#### A. Round-Cable-Based Inductors With Two Windings

Case studies of two-winding round-cable-based inductors with series and parallel connections are simulated in Ansys. Table V shows the geometrical parameters of the simulated round-cable-based inductors. The geometrical parameters for FEM simulations are selected for approaching the real applications. However, it is not reasonable to have the same number of turns/layers as practical applications, e.g., 190 turns/layers in the prototyped inductors shown in the later section.

The simulated electric-field distribution of a round-cable-based inductor with the series connection of windings is shown in Fig. 5(a), where Fig. 5(b) shows the result of a round-cable-based inductor with parallel the connection of windings.

TABLE VI

KEY PARAMETERS OF COPPER-FOIL-BASED INDUCTORS SIMULATION

| Description                    | Parallel | Series  |

|--------------------------------|----------|---------|

| Thickness of the copper foil   | 0.05 mm  | 0.1 mm  |

| Width of the copper foil       | 30 mm    | 30 mm   |

| Thickness of the mylar foil    | 0.05 mm  | 0.05 mm |

| Width of the mylar foil        | 60 mm    | 60 mm   |

| Distance between layer to core | 1.5 mm   | 1.5 mm  |

| Number of layers per winding   | 48       | 24      |

In Fig. 5, the electrical-field distribution is more intensive in the round-cable-based inductors with parallel connections than with the series connection of two windings, where more electric-field energy is stored by the parallel connections of two windings.

According to the simulations, the simulated capacitance of round-cable-based inductors using the parallel connection of windings is 211.42 pF/m, as opposed to 45.02 pF/m while using the series connection of windings. Therefore, the parasitic capacitance in round-cable-based inductors using the series connection of windings is only 21.3% compared to using the parallel connection of windings. The result is very close (around 4% errors) to the theoretical analysis shown in (6). The error is caused by the parasitic capacitance contributed by the stored energy between the inner layer and core, where (6) only consider the parasitic capacitance between two adjacent layers.

#### B. Copper-Foil-Based Inductors With Two Windings

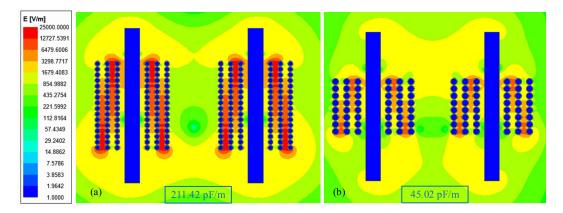

The simulated electric-field distribution of the round-cable-based inductor with the series connection of windings is shown in Fig. 6(a), where Fig. 6(b) shows the round-cable-based inductor with parallel the connection of windings. The geometrical parameters of the simulated copper-foil-based inductors are shown in Table VI, where the corresponding simulation results are presented in Fig. 6.

In Fig. 6(a), the electric field distribution in copper-foil-based inductors with parallel connections of the two windings is more intensive than using the series connection of the two windings. The equivalent capacitance is simulated as 833.27 pF/m with using the series connection of two windings, where the equivalent

Fig. 6. Simulated results of electrical field distribution and equivalent parasitic capacitance of copper-foil-based inductors. (a) Using series-connection of two windings. (b) Using parallel-connection of two windings.

capacitance in the copper-foil-based inductor using the parallel connection of two windings is simulated as 1730.10 pF/m. Using series connection results in a 51.8% reduction of parasitic capacitance compared to using parallel connections of the two-windings, which also shows very close agreement with the theoretical analysis.

#### C. Summary

The FEM analysis of electric field distribution, as well as the simulated equivalent parasitic capacitance, are presented in this section. The FEM simulations can verify the theory that using the series connection of multiple windings can significantly reduce the equivalent capacitance compared to using parallel connections, especially for round-cable-based inductors.

#### V. EXPERIMENTAL VERIFICATIONS

In total, six inductors, including two round-cable-based inductors with parallel and series connections, two copper-foil-based inductors with parallel and series connections, and two planar inductors with parallel and series connections, are prototyped to further validate the theory.

The four prototyped medium-voltage high-power inductors are constructed by two U-type amorphous cores with the same geometrical structures, with a length of 2 mm air gap. The two planar inductors are constructed by the same two C-type cores with no air gaps. The six inductors are configurated with two windings.

The prototyped inductors are not the most optimized inductors with reduced parasitic capacitance and increased utilization of window section (power density). Indeed, the prototyped inductors are aimed to verify the theoretical analysis of parasitic capacitance in multiwinding inductors using parallel or series connections. Therefore, only the amorphous cores in stock of suppliers are used, and it results in lower utilization of window section area. For the same type of inductors, the same electrical

TABLE VII

KEY PARAMETERS OF THE TWO ROUND-CABLE-BASED INDUCTORS

| Description                       | Parallel | Series  |

|-----------------------------------|----------|---------|

| Radius of the copper cable        | 0.67 mm  | 0.95 mm |

| Distance between the two windings | 55 mm    | 54 mm   |

| Number of layers per windings     | 3        | 3       |

| Total inductance (designed value) | 30 mH    | 30 mH   |

| Number of turns per windings      | 190      | 95      |

conductivity (cross-sectional area of the conductor), same inductance (same number of turns and same core structure), and the same main winding parameters (using the same winding layout, bobbins, and spacers) are ensured for a fair comparison.

To measure the parasitic capacitance of these inductors, the Keysight E4990A impedance analyzer and its adapter 16047E with a conventional two-terminal measurement method are applied [34], [35].

#### A. Round-Cable-Based Inductors With Two Windings

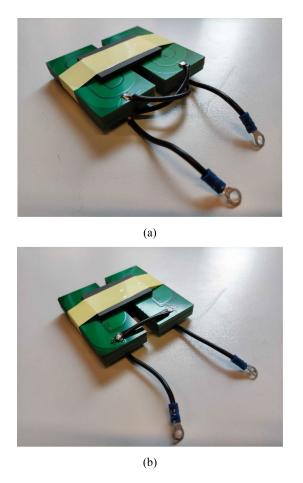

Fig. 7(a) is the picture of the prototyped round-cable-based inductor with parallel connections, whereas Fig. 7(b) is the picture of the prototyped round-cable-based inductor with series connections. The detailed parameters of the two round-cable-based inductors are listed in Table VII. By comparing Fig. 7(a) and (b), the prototyped inductor with series connections of windings has smaller width of winding compared to the prototyped inductor with parallel connections of windings.

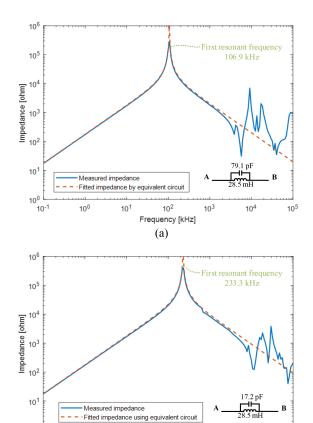

The measured impedance of round-cable-based inductors with parallel and series connections of two windings are shown in Fig. 8(a) and (b), respectively. The inductance of the two inductors is the same due to the same number of turns contributed by both windings. However, the first resonant frequency in Fig. 8(a) is lower than Fig. 8(b), which indicates the equivalent

Fig. 7. Pictures of prototyped round-cable-based inductors. (a) Windings are connected in parallel [the schematic is shown in Fig. 3(a)]. (b) Windings are connected in series [the schematic is shown in Fig. 3(b)].

parasitic capacitance using a parallel connection is larger than using the series connection of two windings. According to the measured impedance, the equivalent circuits of round-cable-based inductors with the parallel and series connections of windings are also given in Fig. 8. The equivalent parasitic capacitance using series connections is reduced by 78.3% compared to parallel connections of multiwinding in round-cable-based inductors, which is in a good agreement with the theoretical analysis.

# B. Copper-Foil-Based Inductors With Two Windings

Fig. 9(a) is the picture of the prototyped copper-foil-based inductor with parallel connections, whereas Fig. 9(b) is the picture of the prototyped copper-foil-based inductor with series connections. The detailed parameters of the two round-cable-based inductors are listed in Table VIII. In Fig. 9, although the width of winding is the same in both prototyped copper-foil-based inductors, the thickness of the copper-foil-based inductors with series connections of windings is smaller than the copper-foil-inductors with parallel connections.

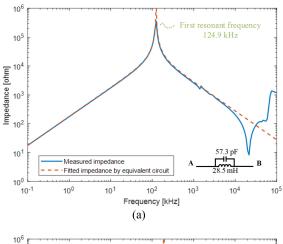

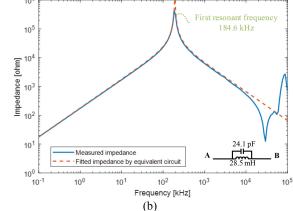

The impedance of the two prototyped copper-foil-based inductors is measured, as shown in Fig. 10. Based on the measured impedance, the equivalent parasitic capacitance of the copper-foil-based inductors using either parallel connection or series connection of two windings are identified, where the series connection of two windings in copper-foil-based inductors reduce the parasitic capacitance by 57.9% compared to using the parallel connection. The experimental results and comparisons

Fig. 8. Measured and fitted impedance of prototyped round-cable-based inductor. (a) Using parallel connections. (b) Using series connections.

10<sup>2</sup>

Frequency [kHz] (b)

10<sup>3</sup>

10<sup>4</sup>

verify the theory that using a series connection can significantly reduce the parasitic capacitance in copper-foil-based inductors.

#### C. Planar Inductors With Two Windings

10-1

The planar inductors with two windings are also prototyped and compared in this article. The two planar inductors are constructed by two C cores with Ferroxcube 3F36 material [36]. Fig. 11(a) is the picture of the prototyped planar inductor with two windings in parallel, where Fig. 11(b) shows the picture of the prototyped planar inductor with two windings in series. The detailed parameters of the two planar inductors are listed in Table IX.

The impedance of the two prototyped planar inductors is also measured, as shown in Fig. 12(a) and (b), for parallel and series connections of two windings, respectively. It can be found that for the same current level planar transformers using the same core, using the series connection of two windings can help to reduce the equivalent capacitance by around 71.5%, where the volume of windings also becomes smaller. The experimental results prove that using series connections of multiple windings in planar inductors can significantly reduce the equivalent capacitance without adding manufacturing complexity and sacrificing winding power density. The conclusion should be applied to

Fig. 9. Pictures of prototyped copper-foiled inductors. (a) Windings are connected in parallel [the schematic is shown in Fig. 4(a)]. (b) Windings are connected in series [the schematic is shown in Fig. 4(b)].

TABLE VIII

KEY PARAMETERS OF THE TWO COPPER-FOILED INDUCTORS

| Description                                     | Parallel   | Series     |

|-------------------------------------------------|------------|------------|

| Thickness of the copper foil                    | 0.05<br>mm | 0.1<br>mm  |

| Width of the copper foil                        | 30 mm      | 30 mm      |

| Thickness of the mylar foil                     | 0.05<br>mm | 0.05<br>mm |

| Width of the mylar foil (Height of the winding) | 60 mm      | 60 mm      |

| Distance between the two windings               | 19 mm      | 45 mm      |

| Number of layers per windings                   | 190        | 95         |

| Total inductance (designed value)               | 30 mH      | 30 mH      |

| Relative permittivity of the mylar foil         | 3.25       | 3.25       |

various types of inductors at the same power level by using series connections of the multiwindings.

# VI. ADVANTAGES AND DISADVANTAGES OF USING SERIES CONNECTIONS OF MULTIWINDINGS

# A. Advantages

The advantages of using series connections have been both theoretically and experimentally proved in this article. Most

Fig. 10. Measured and fitted impedance of prototyped copper-foil-based inductor. (a) Using parallel connections. (b) Using series connections.

TABLE IX

KEY PARAMETERS OF THE TWO PLANAR INDUCTORS

| Parallel | Series                                               |

|----------|------------------------------------------------------|

| 70 μm    | 70 μm                                                |

| 7.62 mm  | 15.24 mm                                             |

| 1.13 mm  | 1.13 mm                                              |

| 10 mm    | 10 mm                                                |

| 20       | 10                                                   |

| 700 μH   | 700 μH                                               |

| 4.4      | 4.4                                                  |

|          | 70 μm<br>7.62 mm<br>1.13 mm<br>10 mm<br>20<br>700 μH |

importantly, the parasitic capacitance of inductors can be significantly reduced using the series connections of multiwindings (at least by 50%). In the round-cable-based inductors, the voltage stress between the adjacent layers can also be reduced, which may help reduce partial discharge in medium-voltage applications [37]. Besides, the volume of windings could be reduced using the series connections of multiwindings.

Fig. 11. Pictures of prototyped planar inductors. (a) Windings are connected in parallel. (b) Windings are connected in series.

# B. Disadvantages

Since the parallel connections can share the current and at the same frequency, the ac resistance caused by skin effects and proximity effects [1], [38], is smaller than using the series connections of multiwindings. Therefore, using series connections of inductors with multiwindings can result in larger ac-resistance and more winding loss at high frequency.

#### C. Discussions

The main applications of this article are high-power applications, especially for medium voltage SiC MOSFET applications. In these cases, the inductors usually act as line filters, where the fundamental frequency is 50/60 Hz and the switching frequency is 5-10 kHz. Therefore, the ac-resistance at high frequency is not the most critical parameter in these applications. Instead, due to the high dv/dt of medium-voltage SiC MOSFETs, the parasitic capacitance in magnetics is the bottleneck. Therefore, it can be a solution to electronically connect then multiwindings in series for reducing parasitic capacitance, even with introducing larger ac-resistance.

Besides, in the case of further reducing the ac resistance, litz wire (without considering the cost) can also be applied with series connections of multiwindings.

Fig. 12. Pictures of prototyped planar inductors. Measured and fitted impedance of prototyped planar inductors. (a) Using parallel connections. (b) Using series connections.

Regarding the manufacturing complexity, using series connections of multiwindings will not add extra cost, which is almost the same as the manufacturing of inductors with parallel connections of multiwindings.

#### VII. CONCLUSION

This article investigates the difference in parasitic capacitance in inductors using parallel and series connections of multiwindings. The theoretical and experimental results prove that the multiwinding inductors with series connections of windings should exhibit a much smaller parasitic capacitance compared to the multiwinding inductors using parallel connections of windings without adding extra manufacturing cost and complexity. This article reveals that the equivalent layer-to-layer parasitic capacitance in inductors can be significantly reduced by means of series connections of windings, where the effects are more obvious in round-cable-based inductors compared with copper-foil-based inductors. The volume of windings can also be reduced using the series connections of multiwindings. Therefore, it is advantageous for medium-voltage and high-power inductors to use the series connections of multiwindings.

#### REFERENCES

- [1] W. G. Hurley and W. H. Wölfle, *Transformers and Inductors for Power Electronics: Theory, Design and Applications*. New York, NY, USA: Wiley, 2013.

- [2] Z. Zhao, P. Davari, W. Lu, H. Wang, and F. Blaabjerg, "An overview of condition monitoring techniques for capacitors in DC-link applications," *IEEE Trans. Power Electron.*, vol. 36, no. 4, pp. 3692–3716, Apr. 2021.

- [3] M. Montazeri et al., "Vertically stacked, flip-chip wide bandgap MOSFET co-optimized for reliability and switching performance," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 9, no. 4, pp. 3904–3915, Aug. 2021.

- [4] P. Yang, W. Ming, J. Liang, I. Lüdtke, S. Berry, and K. Floros, "Hybrid datadriven modeling methodology for fast and accurate transient simulation of SiC MOSFETs," *IEEE Trans. Power Electron.*, vol. 37, no. 1, pp. 440–451, Jan. 2022.

- [5] B. Ahmad, P. Jayathurathnage, W. Martinez, and J. Kyyra, "Parameter extraction technique for evaluation of inductive and capacitive elements of three-winding coupled inductor," *IEEE J. Emerg. Sel. Topics Ind. Electron.*, vol. 3, no. 3, pp. 616–625, Jul. 2022.

- [6] I. Lope et al., "First self-resonant frequency of power inductors based on approximated corrected stray capacitances," *IET Power Electron.*, vol. 14, no. 2, pp. 257–267, 2021.

- [7] H. Zhao et al., "Modeling and design of a 1.2 pF common-mode capacitance transformer for powering MV SiC MOSFETs gate drivers," in *Proc.* 45th Annu. Conf. IEEE Ind. Electron. Soc., Oct. 2019, pp. 5147–5153.

- [8] F. Luo, D. Dong, D. Boroyevich, P. Mattavelli, and S. Wang, "Improving high-frequency performance of an input common mode EMI filter using an impedance-mismatching filter," *IEEE Trans. Power Electron.*, vol. 29, no. 10, pp. 5111–5115, Oct. 2014.

- [9] C. DiMarino et al., "Design and experimental validation of a wire-bon-less 10-kv SiC MOSFET power module," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 1, pp. 381–394, Mar. 2020.

- [10] H. Zhao et al., "Behavioral modeling f ground current in filter inductors of medium-voltage SiC-MOSFET-based converters," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, Mar. 2020, pp. 1972–1978.

- [11] J. K. Jorgensen et al., "Loss prediction of meidum voltage power modules: Trade-offs between accuracy and complexity," in *Proc. Energy Conservation Congr. Expo.*, Oct. 2019, pp. 4102–4108.

- [12] Z. Ouyang and M. A. E. Andersen, "Overview of planar magnetic technology-fundamental properties," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp. 4888–4900, Sep. 2014.

- [13] B. Zhang and S. Wang, "A survey of EMI research in power electronics systems with wide-bandgap semiconductor devices," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 1, pp. 626–643, Mar. 2020.

- [14] A. Anurag, S. Acharya, S. Bhattacharya, and T. R. Weatherford, "Thermal performance and reliability analysis of a medium voltage three-phase inverter considering the influence of high dv/dt on parasitic filter elements," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 1, pp. 486–494, Mar 2020

- [15] J. K. Jorgensen, D. N. Dalal, S. Beczkowski, S. Munk-Nielsen, and C. Uhrenfeldt, "Multi-chip medium voltage SiC MOSFET power module with focus on low parasitic capacitance," in *Proc. 11th Int. Conf. Integr. Power Electron. Syst.*, Mar. 2020, pp. 1–6.

- [16] D. Dalal et al., "Demonstration of a 10 kV SiC MOSFET based medium voltage power stack," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, Mar. 2020, pp. 2751–2757.

- [17] C. Buchhagen, C. Reese, L. Hofmann, and H. Däumling, "Determination of a capacitance model for inductive medium voltage transformers," in *Proc. IEEE PES Transmiss. Distrib. Conf. Expo.*, May 2012, pp. 1–6.

- [18] A. Cremasco, D. Rothmund, M. Curti, and E. A. Lomonova, "Voltage distribution in the windings of medium-frequency transformers operated with wide bandgap devices," *IEEE J. Emerg. Sel. Topics Power Electron.*, to be publihed, doi: 10.1109/JESTPE.2021.3064702.

- [19] E. Snelling, SoftFerrites: Properties and Applications. London, U.K.: Iliffe Books Ltd., 1988.

- [20] H. Zhao et al., "Physics-based modeling of parasitic capacitance in medium-voltage filter inductors," *IEEE Trans. Power Electron.*, vol. 36, no. 1, pp. 829–843, Jan. 2021.

- [21] I. Stevanovic, S. Skibin, M. Masti, and M. Laitinen, "Behavioral modeling of chokes for EMI simulations in power electronics," *IEEE Trans. Power Electron.*, vol. 28, no. 2, pp. 695–705, Feb. 2013.

- [22] H. Zhao, D. Dalal, J. K. Jørgensen, M. M. Bech, X. Wang, and S. Munk-Nielsen, "Behavioral modeling and analysis of ground current in medium-voltage inductors," *IEEE Trans. Power Electron.*, vol. 36, no. 2, pp. 1236–1241, Feb. 2021.

- [23] M. Zdanowski, K. Kostov, J. Rabkowski, R. Barlik, and H. Nee, "Design and evaluation of reduced self-capacitance inductor in DC/DC converters with fast-switching SiC transistors," *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2492–2499, May 2014.

- [24] F. Salomez, A. Videt, and N. Idir, "Modeling and minimization of the parasitic capacitances of single-layer toroidal inductors," *IEEE Trans. Power Electron.*, vol. 37, no. 10, pp. 12426–12436, Oct. 2022.

- [25] J. Biela and J. W. Kolar, "Using transformer parasitics for resonant converters a review of the calculation of the stray capacitance of transformers," *IEEE Trans. Ind. Appl.*, vol. 44, no. 1, pp. 223–233, Jan./Feb. 2008.

- [26] J. Biela, D. Bortis, and J. W. Kolar, "Modeling of pulse transformers with parallel-and non-parallel-plate windings for power modulators," *IEEE Trans. Dielectrics Elect. Insul.*, vol. 14, no. 4, pp. 1016–1024, Aug. 2007.

- [27] F. Salomez, A. Videt, and N. Idir, "Semi-analytical model of parasitic capacitance of inductor with conductive core," in *Proc. PCIM Europe Digit.* Days, Int. Exhib. Conf. for Power Electron., Intell. Motion, Renewable Energy Energy Manage., May 2021, pp. 1–8.

- [28] S. Acharya, A. Anurag, Y. Prabowo, and S. Bhattacharya, "Practical design considerations for MV LCL filter under high dv/dt conditions considering the effects of parasitic elements," in *Proc. 9th IEEE Int. Symp. Power Electron. Distrib. Gener. Syst.*, Jun. 2018, pp. 1–7.

- [29] H. Zhao et al., "Parasitic capacitance modeling of copper-foiled medium-voltage filter inductors considering fringe electrical field," *IEEE Trans. Power Electron.*, vol. 36, no. 7, pp. 8181–8192, Jul. 2021.

- [30] C. Sullivan, H. Bouayad, and Y. Song, "Inductor design for low loss with dual foil windings and quasi-distributed gap," in *Proc. IEEE Energy Convers. Congr. Expo.*, Sep. 2013, pp. 3693–3699.

- [31] X. Liu, Y. Wang, J. Zhu, Y. Guo, G. Lei, and C. Liu, "Calculation of capacitance in high-frequency transformer windings," *IEEE Trans. Magn.*,vol. 52, no. 7, Jul. 2016, Art. no. 2003204.

- [32] Z. Shen, H. Wang, Y. Shen, Z. Qin, and F. Blaabjerg, "An improved stray capacitance model for inductors," *IEEE Transaction Power Electron.*, vol. 34, no. 11, pp. 11153–11170, Nov. 2019.

- [33] J. Biela, D. Bortis, and J. Kolar, "Modeling of pulse transformers with parallel-and non-parallel-plate windings for power modulators," *IEEE Trans. Dielect. Electr. Insul.*, vol. 14, no. 4, pp. 1016–1024, Aug. 2007.

- [34] Keysight Technology, "E4990A impedance analyzer," [Online]. Available: https://www.keysight.com/us/en/assets/7018-04256/data-sheets/5991-3890.pdf

- [35] Keysight Technology, "Impedance measurement handbook," [Online]. Available: https://www.keysight.com/dk/en/assets/7018-06840/ application-notes/5950-3000.pdf

- [36] Ferroxcube, "3F36, flat loss, medium to high frequency power material for broad temperature range applications," [Online]. Available: https://www. ferroxcube.com/en-global/download/download/99

- [37] Z. Yuan et al., "Insulation and switching performance optimization for Partial-discharge free laminated bus bar in More-electric aircraft applications," *IEEE Trans. Power Electron.*, vol. 37, no. 6, pp. 6831–6843, Jun. 2022.

- [38] I. Lope, C. Carretero, J. Acero, R. Alonso, and J. M. Burdío, "AC power losses model for planar windings with rectangular cross-sectional conductors," *IEEE Trans. Power Electron.*, vol. 29, no. 1, pp. 23–28, Jan. 2014.

**Hongbo Zhao** (Member, IEEE) received the Ph.D. degree in modeling and reducing parasitic capacitance in magnetic components from Aalborg University, Aalborg, Denmark, in 2021.

He is currently a Postdoctoral Researcher with Aalborg University, Aalborg, Denmark. His research interests include high-frequency modeling and analysis of high-power magnetics and filters, as well as medium-voltage converters enabled by wide bandgap power devices.

Zhixing Yan received the B.Eng. degree in electrical engineering and automation from Southwest Jiaotong University, Chengdu, China, in 2018, and the M.Eng. degree in electrical engineering from South China University of Technology, Guangzhou, China, in 2021. He is currently working toward the Ph.D. degree in power electronics in medium-voltage applications with Aalborg University, Aalborg, Denmark.

His current research interests include mediumvoltage converters enabled by wide band-gap power devices.

**Shaokang Luan** received the B.S. and M.S. degrees in electrical engineering from Huazhong University of Science and Technology, Wuhan, China, in 2017 and 2020, respectively.

He is currently working as a Research Assistant with the AAU Energy, Aalborg University, Aalborg, Denmark. His research interests include design and modeling of high-frequency planar magnetics with parasitic parameters.

**Xiang Zhou** (Member, IEEE) received the B.S. and Ph.D. degrees in electrical engineering from Southwest Jiaotong University, Chengdu, China, in 2013 and 2018, respectively.

From June 2018 to December 2019, he was with the Department of Electrical and Computer Engineering, Queen's University, Kingston, ON, Canada, as a Post-doctoral Research Fellow. Since 2019, he has been with Xi'an Jiaotong University, where he is currently an Assistant Professor with the School of Electrical Engineering.

His current research interests include soft switching dc-dc converter and dc-ac converter topology and control, resonant converters and server power supplies, and EV chargers.

**Dipen Narendra Dalal** received the M.Sc. degree in energy engineering (*with specialization in power electronics and drivers*) from Aalborg University, Aalborg, Denmark, in 2016, and the Ph.D. degree in power electronics with the Department of Energy Technology, Aalborg University, Denmark, in 2021.

He is currently a Postdoc Researcher with Aalborg University, Aalborg, Denmark. His current research interests include wide band-gap power semiconductor devices and medium voltage high power converters.

Szymon Michal Bęczkowski received the M.Sc. degree in electrical engineering from the Warsaw University of Technology, Warsaw, Poland, in 2007, and the the Ph.D. degree in control and driving for LED applications from Aalborg University, Aalborg, Denmark, in 2012.

He is currently an Associate Professor with the Department of Energy Technology, Aalborg University. His research interests include optimization of power electronic converters, power module packaging, and SiC technology.

**Jannick Kjær Jørgensen** received the master's degree in nanomaterials and nanophysics from Aalborg University, Aalborg, Denmark, in 2018.

He is currently a Research Assistant with the Department of Energy Technology, Aalborg University, Denmark. He has been working on design and manufacture of medium voltage SiC-based power modules since 2018, with a particular focus on challenges with scaling power of these. His research interests include parasitic parameters in medium voltage systems, and manufacturing and design constraints of SiC power modules.

**Bjørn Rannestad** received the industrial Ph.D. degree in high-power converters for wind applications from Aalborg University, Aalborg, Denmark, in 2019 (with a focus on megawatt power electronics converters for wind turbines).

He is currently the Senior Specialist for Power Converters, Global Technology and Innovation at KK Wind Solutions, Denmark. He has 14 years of experience in the development and research for wind turbine power electronic converters. Since 1999, he has been involved in power electronics design and

manufacturing. He has authored and coauthored more than 20 patent applications and academic papers on various power electronic topics.

Rui Wang (Student Member, IEEE) received the B.S. degree in electrical engineering and automation from Hunan University, Changsha, China, in 2017, and the M.S. degree in electrical engineering from Huazhong University of Science and Technology, Wuhan, China, in 2020. He is currently working toward the Ph.D. degree in design of gate drivers for power electronic converters with Aalborg University, Aalborg, Denmark.

His research interests include wide band-gap power semiconductor devices, their active gate drivers,

series-connection technology, and converter design.

**Stig Munk-Nielsen** (Member, IEEE) received the M.Sc. and Ph.D. degrees from Aalborg University, Aalborg, Denmark, in 1991 and 1997, respectively, both in three-phase resonant dc-link converters.

He is currently a Professor with the Department of Energy, Aalborg University. In the last ten years, he was involved in 10 research projects. He has authored and coauthored 244 international power electronics papers and applied for 4 patents. His research interests include LV and MV Si, SiC, and GaN technology, including power converter circuits and components.