# **Aalborg Universitet**

# A Symmetric Switched-Capacitor-Based Basic Inverter Unit for Grid-Connected PV **Systems**

Khoun Jahan, Hossein; Sarhangzadeh, Mitra; Ardashir, Jaber Fallah; Blaabjerg, Frede

Published in: I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2022.3184757

Publication date: 2022

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Khoun Jahan, H., Sarhangzadeh, M., Ardashir, J. F., & Blaabjerg, F. (2022). A Symmetric Switched-Capacitor-Based Basic Inverter Unit for Grid-Connected PV Systems. *I E E Transactions on Power Electronics*, *37*(12), 15594 - 15604. Article 9801666. https://doi.org/10.1109/TPEL.2022.3184757

### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 04, 2025

# A Symmetric Switched-Capacitor Based Basic Inverter Unit for Grid-Connected PV Systems

Hossein Khoun Jahan, Mitra Sarhangzadeh, Jaber Fallah Ardashir, and Frede Blaabjerg

Abstract- In this paper a new inverter unit is proposed. It is a compact switched-capacitor-based inverter, which is combined of four switches, two diodes and four capacitors. Since this inverter unit is a mid-point-clamped inverter, it can mitigate the capacitive leakage current in many applications. One of the main applications of the proposed inverter is in grid-tied photovoltaic (PV) systems, where the commonmode current brings many challenges. Other than the mentioned feature, the proposed inverter includes the following advantages: i) spontaneous balancing of the voltage across the capacitors without needing any control system or auxiliary circuits, ii) capability of full reactive power transfer, iii) low voltage stress on the capacitors compared to common three-level inverter topologies (NPC, T-type-NPC, FC and etc.), and iv) symmetric switching sequence, which causes a continuous input current. The feasibility and versatility of the proposed inverter unit is validated by experimental tests, which are conducted by using a lab-scale prototype.

Key Words- switched-capacitor, transformer-less inverter, self-balancing, leakage current, grid-tied PV system.

### I. INTRODUCTION

Due to energy shortage and environment pollution, using renewable energy resources instead of conventional fossilenergy-based power plants is inevitable. Renewable energies resources are mostly reliant on power electronic converter to meet the requirements of power networks and customers. Whereas the infrastructures of power systems are based on ac voltage, and most of the renewable energy resources produces de voltage, inverters play an important role in modern power systems. It goes without saying that among the renewable energy resources PV and wind systems are the most promising energy resources. PV-based electric sources mostly use dc-dc converter, dc-ac inverter or a combination of the two mentioned converters. The converters in PV systems are required to meet some special standards. The most important issues in this field are efficiency and the parasitic capacitor that appear between the PV panels and

Hossein Khoun Jahan is with the Azarbaijan Regional Electric Company, Tabriz, Iran (e-mail: hosseinkhounjahan@yahoo.com).

Mitra Sarhangzadeh (Corresponding Author) is with the Department of Electronics, Tabriz Branch, Islamic Azad University, Tabriz, Iran (e-mail: mitsarhang@iaut.ac.ir).

Jaber Fallah Ardashir is with the Department of Electronics, Tabriz Branch, Islamic Azad University, Tabriz, Iran (e-mail: j.fallah@iaut.ac.ir).

Frede Blaabjerg is with the Institute of Energy Technology, Aalborg University, DK-9220 Aalborg East, Denmark (e-mail: fbl@et.aau.dk).

ground, which brings troublesome leakage current [1-2]. In order to reduce the volume and cost of grid-connected PV systems many attempt to eliminate bulky low-frequency transformer [3-5]. Other than reducing the cost, bulkiness and weight, eliminating transformers reduces the power losses and improves the efficiency. However, by removing

transformer in PV systems the galvanic isolation will disappear and causes some new challenges. As mentioned above, the capacitive leakage current is one of the main problems which might reduce power quality, cause safety problems and increase power losses.

Several strategies have been proposed to address inverter problems and improve the performance of these devices. The strategies can be categorized in three branches as i) advanced controlling methods [6-7] ii) improved switching strategies [8-9] and iii) topological solutions [10-12]. Inverters in different applications have special requirements where these devices in PV applications are required to limit capacitive leakage current, which arises from parasitic capacitances of PV modules. Additionally, they have to be of high efficiency and reliability. So far, many PV inverters have been introduced to fulfill the mentioned requirements. In order to reduce the cost and volume of the whole PV system the attempt is to use transformerless inverters. To address the problems in grid-tied PV systems three classes of topological solutions can be considered for PV inverters. The first solution is to decouple the dc-side from ac-side during zero voltage state. The H5 and HERIC PV inverters are the example of inverters that employ the mentioned solution that is the core idea of references [13-14]. The second solution is to use common-ground inverters. These types of inverters try to eliminate the leakage current by connecting the negative pole of the PV module to the ground of the grid. Although these inverters have successfully caused zero leakage current, they suffer from non-symmetric usage and nonequal power loss of the utilized components. Several common-ground PV inverters are introduced in [15-17]. The topological solution for grid-tied transformerless PV inverters are to use neutral point clamped inverters like Neutral point clamped (NPC) and T-type-NPC [18-20]. These inverters are used in many industrial applications. However, they have a symmetric structure and many other advantages, while the buck characteristic is counted as their main drawback.

To cover the challenge, this work is conducted to put forth a new three-level transformerless PV inverter. The proposed inverter is a neutral-point-clamped inverter that uses four switches and two diodes. Two small inductors are also used to provide zero current switching condition for the diodes. The proposed inverter has a symmetric structure and it features leakage current limiting capability. Unlike the conventional NPC and T-type-NPC, this inverter has unity voltage gain and lower voltage stresses over the components. The proposed inverter can be configured as a three-phase inverter as well.

This work will be continued as follows; in the next section the configuration of the proposed inverter will be defined. Section III will deal with the component design of the proposed inverter. The three-phase configuration of the proposed inverter will be briefly explained in section IV. In section V, a detailed comparison will be provided where the proposed inverter will be compared with the well-known transformerless PV inverters. In section VI, by using a simulation model, the performances of the proposed inverter in a grid-tied PV system will be investigated. In order to prove the feasibility of the proposed inverter, it is tested experimentally using a lab-scale prototype. Experimental results are discussed in section VII. Finally, the overall work will be concluded in the last section.

#### II. CONFIGURATION OF THE PROPOSED INVERTER

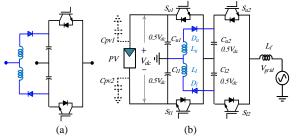

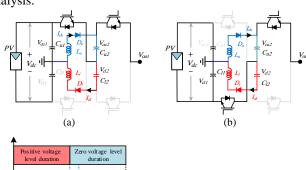

The basic unit and overall configuration of the proposed inverter are exhibited in Figs.1 (a) and (b) respectively. As it is seen in Fig. 1(a) the basic unit is a half-bridge equipped with two diodes and small inductors. These diodes are served to charge the capacitors in appropriate switching instances. As seen in Fig.1(b), the overall configuration of the proposed inverter is a mid-point clamped inverter that can easily mitigate the common-mode voltage and develop a symmetric three-level ac voltage. The switching method and components status in different switching patterns are defined in Table I.

Fig. 1. Proposed PV inverter, (a) basic unit, and (b) overall configuration.

TABLE I. OPERATION STATES OF THE INVERTER

| TABLE II OF ENVIRONMENTED OF THE INVERTER |                                  |                  |                     |            |  |

|-------------------------------------------|----------------------------------|------------------|---------------------|------------|--|

| Level                                     | Switches<br>states               | Diodes<br>states | Capacitors states   | $V_{out}$  |  |

| e                                         | $S_{u1}, S_{l1}, S_{u2}, S_{l2}$ | $D_u$ , $D_I$    | $C_{u2}$ , $C_{l2}$ | Oil        |  |

| 1                                         | 1010                             | 01               | D,C                 | $1V_{dc}$  |  |

| 0                                         | 0110                             | 10               | C,N                 | $OV_{dc}$  |  |

| 0                                         | 1001                             | 01               | N,C                 | $OV_{dc}$  |  |

| -1                                        | 0101                             | 10               | C,D                 | $-1V_{dc}$ |  |

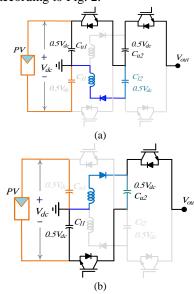

The current paths for the positive, zero and negative voltage levels are, respectively, depicted in Fig. 2(a), (b) & (c) and (d).

The operation principle can be defined as follows:

Positive voltage level: As seen in Fig. 2(a), to develop the positive voltage level the upper switches ( $S_{u1}$  and  $S_{u2}$ ) are turned on. Under this condition  $C_{l2}$  is connected in parallel with  $C_{ul}$  so it is charged to  $0.5V_{dc}$  through  $S_{u1}$ ,  $D_{l2}$  and  $C_{u1}$ , simultaneously.

Zero voltage level: As it is seen in Figs. 2(b) and (c), there are two switching patterns to realize the zero voltage level. In the first switching pattern that is shown in Fig. 2(b),  $S_{11}$ and  $S_{u2}$  are turned on. Under this condition  $C_{11}$  is paralleled with C<sub>u2</sub> and it stays in the charging mode. In the second switching pattern, which is depicted in Fig. 2(c), S<sub>u1</sub> and S<sub>12</sub> are turned on and put C<sub>12</sub> in the charging state. Since the zero voltage level is realized in each PWM switching cycle, and considering that during the two mentioned switching patterns two different capacitors are charged, it will be possible to reduce the voltage ripple across  $C_{u2}$  and  $C_{l2}$  as much as possible. Reduction in voltage ripple across the mentioned capacitors leads to a reduction in charging current of the capacitors. Considering that the main problem of switchedcapacitor based converters is the inrush current of utilized capacitors, this problem is attenuated in the proposed inverter.

Negative voltage level: as shown in Fig. 2(d), in order to develop the negative voltage level, the lower switches ( $S_{11}$  and  $S_{12}$ ) are turned on. Under this condition  $C_{u2}$  is put in the charging mode and it is charged to 0.5Vdc, spontaneously, through  $D_u$  and  $S_{11}$ .

It is obvious that the neutral balancing of capacitors and continuous input current are preserved with the switching sequences according to Fig. 2.

Fig. 2. Current path of (a) positive voltage level, (b) & (c) zero voltage level, and (d) negative voltage level.

#### III. COMPONENT SIZING

#### A. Voltage ripple and components sizing

The proposed inverter uses two splitting capacitors at the input cell and two switched-capacitors at the basic cell. The voltage across each of the input capacitor is calculated as

$$V_{C_{u1}} = V_{C_{l1}} = \frac{V_{dc}}{2} + \Delta v_{cin} \tag{1}$$

Where  $V_{CuI}$ ,  $V_{CII}$ , are the voltage stresses of the input capacitors and  $V_{dc}$  is the input voltage.  $\Delta v_{cin}$  is voltage ripple across the mentioned capacitors which is calculated as

$$C\frac{dv_{cin}}{dt} = \frac{mI_m}{2} (1 - \cos 2\omega t) \tag{2}$$

$$\Delta v_{cin} = \frac{mI_m}{4Cf} \tag{3}$$

Where m,  $I_m$ , f, and  $C(C=C_{ul}=C_{ll})$  are modulation index, the peak value of the output current, grid frequency and capacitances of the input capacitors.

As the switched-capacitors in the basic cell are in parallel with the input capacitors, in some proper switching instances, the voltage across these capacitors are the same as that across the input capacitors.

Referring to Figs. 2(a) and (d), it is understood that  $C_{u2}$  and  $C_{l2}$  are discharged when the positive and negative voltage levels are realized accordingly. Since in any switching period there are two switching strategies to develop the zero voltage level, we can put the desired capacitor in the charging mode during the zero voltage state. Thus the longest discharging duration of  $C_{u2}$  and  $C_{l2}$  is shorter than one switching cycle. Having this fact in mind, the maximum voltage ripple across  $C_{u2}$  and  $C_{2l}$  is given as

$$\Delta V_{C_{u2(l2)}} = \frac{mI_m}{2C_{u2(l2)}f_{sw}} \tag{4}$$

Where  $f_{sw}$  is the switching frequency.

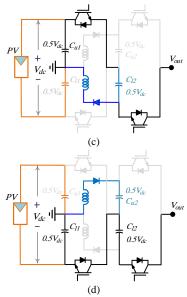

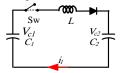

B. Charging inductors to prevent power loss

Paralleling capacitors with different initial charge, as it is the case in switched-capacitor cell will cause energy loss. The following equation define the way the energy loss takes place in the switched-capacitor shown in Fig. 3.

Fig. 3. Hard charging of capacitors

The energy before paralleling the capacitors is the summation of the energy stored in each capacitor as

$$U_0 = \frac{1}{2}C_1V_{c1}^2 + \frac{1}{2}C_2V_{c2}^2 \tag{5}$$

The voltage across the capacitors after paralleling the capacitors is given as

$$V_{C_t} = \frac{C_1 V_{c1} + C_2 V_{c2}}{C_1 + C_2} \tag{6}$$

The energy after paralleling the capacitors is given as

$$U_{1h} = \frac{1}{2} (C_1 + C_2) \left( \frac{C_1 V_{c1} + C_2 V_{c2}}{C_1 + C_2} \right)^2 = \frac{1}{2} \frac{(C_1 V_{c1} + C_2 V_{c2})^2}{C_1 + C_2}$$

(7)

In the case C1=C2=C, the aforementioned equations can be simplified as

$$U_0 = \frac{1}{2} C \left( V_{c1}^2 + V_{c2}^2 \right) \tag{8}$$

$$V_{C_t} = \frac{V_{c1} + V_{c2}}{2} \tag{9}$$

$$U_{1h} = \frac{1}{2} C V_{Ct}^2 = \frac{C}{4} (V_{c1} + V_{c2})^2$$

(10)

The energy loss after paralleling the capacitors is given as

$$\Delta U = U_0 - U_{1h} = \frac{1}{2} C (V_{c1} - V_{c2})^2$$

(11)

As it is understood from (11) the hard charging of the capacitors increase energy loss. For the sake of avoiding energy losses, the capacitors can be charged through a small inductor as shown in Fig. 4, and described by (12) to (17).

Fig. 4. Soft charging of capacitors.

After turning on the switch the current equation is obtained as

$$L\frac{di_l}{dt} = V_{c1} - V_{c2} = \Delta v \tag{12}$$

$$i_l = \frac{\Delta v}{l\omega_r} \sin \omega_r t \tag{13}$$

Where

$$\omega_r = \sqrt{\frac{2}{LC}}$$

Assuming an initial condition of  $V_{c1}(0)=V+\Delta v$  and  $V_{c2}(0)=V$ , the voltage equation after turning on the switch is obtained as

$$V_{c1}(T_s) = V + \Delta v - \frac{1}{C} \int_{0}^{T_s} i_l(t) dt = V$$

(14)

$$V_{c2}(T_s) = V + \frac{1}{C} \int_{0}^{T_s} i_l(t)dt = V + \Delta v$$

(15)

The total energy stored in the capacitors before turning on the switch is given as

$$U_0 = \frac{1}{2} C((V_{c1}(0))^2 + (V_{c2}(0))^2) = \frac{1}{2} C((V + \Delta v)^2 + V^2)$$

$$U_0 = CV^2 + CV\Delta v + \frac{1}{2} C\Delta v^2$$

(16)

The total energy after turning on the switch is given as

$$U_{1s} = \frac{1}{2} C (V_{c1}(T_s))^2 + (V_{c2}(T_s))^2 = \frac{1}{2} C (V^2 + (V + \Delta v)^2)$$

$$U_{1s} = CV^2 + CV\Delta v + \frac{1}{2} C\Delta v^2$$

(17)

$$\Delta U = U_0 - U_{1s} = 0 \tag{18}$$

As it is implied from (16), (17) and (18) the energy stored in the capacitors before and after switching action is the same and no energy is lost. As the capacitors are charged in each switching cycle, hard charging of the capacitor will lead to a significant power loss. Using small inductor in the charging path will avoid the mentioned power loss.

The inductor  $L_u$  and  $L_l$  in the proposed inverter are used to limit the inrush current of the capacitors and limit the power loss that arises from inrush current of capacitors. The size of these small inductors are calculated by considering the fact that the charging process of the capacitors should last during a switching interval. Therefore, the inductor size is calculated as

$$L_{u(l)} = \frac{1}{C_{u2(l2)} (2\pi f_{sw})^2} \tag{19}$$

The switches and diodes in the proposed inverter should withstand the input dc voltage.

The charging current of the switched-capacitors is given as

$$L_{u(l)} \frac{di_{u(l)}}{dt} + (r_d + r_{sw} + 2ESR)i_{u(l)} = \Delta V_c + V_{ow} + V_{od}$$

(20)

Where  $r_d$ ,  $r_{sw}$ , ESR,  $\Delta V_c$ ,  $V_{ow}$ , and  $V_{od}$  are resistance of diode,

on-state resistance of switch, equal series resistance of a capacitor, on-state voltage of switch, and on-state voltage of switch and on-state voltage of charging diode.

According to Eq. (20), the charging current is limited by the charging inductor and parasitic resistance of the components. What is more, the charging inductors can provide zero current switching condition for diodes and smooth the charging current which reduces the EMI. Fig. 5 shows the current and voltage curves of the diodes. To explain the charging process of the capacitors the charging mode in positive and zero voltage levels are represented. Referring to Fig. 5(a), It is seen that voltage across  $L_1$  is  $V_{cu1}$ - $V_{cl2}$ = $\Delta V$ , and voltage across Lu is zero, hence Idl (current of diode Dl) begins to increase as seen in Fig. 5(c). As seen in Fig. 5(b), at the end of switching cycle when the zero voltage level mode is switched, the voltage across L<sub>1</sub> becomes - $(V_{cl1}+V_{cl2})$ . When the voltage is reversed across  $L_1$  the current start to decrease abruptly during t<sub>s</sub> interval. As the current reaches to zero, the diode ceases to conduct. This is the case for L<sub>u</sub> and diode D<sub>u</sub> in the next switching period. Thus, the turn on and off of the diodes take palace under zero current condition. It is to be noted that, for simplicity, the parasitic resistance of the components is ignored in this analysis.

Fig. 5. Charging current and voltage of inductors and diodes, (a) charging mode in positive voltage level, (b) charging mode in zero voltage level, (c) voltage across  $L_l$  and current  $D_l$ .

The switches  $S_{uI}$  and  $S_{II}$  have to withstand the load current plus the charging current, however  $S_{u2}$  and  $S_{l2}$  only tolerate the load current.

#### IV. THREE-PHASE CONFIGURATION

The three-phase inverters are one of the most important components in industry. The common three-phase inverter is synthesized with three traditional half-bridge inverters which develops a two-level voltage in each phase. In order to enhance the quality of the converted voltage and develop a three-level phase voltage, NPC, T-type NPC and flying-capacitor inverters were introduced. Although the mentioned inverter topologies can develop a three-level voltage, they have a buck characteristics and cannot effectively use the input dc voltage.

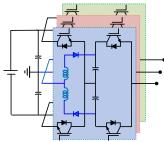

The three-phase configuration of the proposed inverter can cover many challenges in three-phase applications. As an advantage, the three-phase configuration can create three-level voltage with peak value equal to the input voltage. The three-phase configuration of the proposed inverter is exhibited in Fig. 6.

Fig. 6. Three-phase configuration of the proposed inverter.

#### V. BENCHMARKING WITH THE PRIOR-ART PV INVERTER

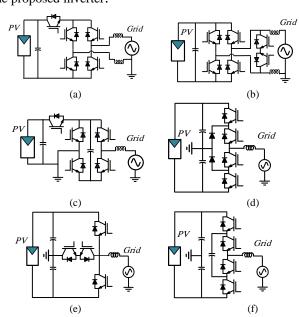

In this part the proposed inverter is compared with the well-known H5 [11], HERIC [12], Virtual-dc-bus [13], NPC [14], T-type NPC [15], and Flying-Capacitor [16] three-level inverters, from different point of views. All the mentioned inverters are employed in grid-tied PV applications and depicted in Fig.7. To do so, different features of the mentioned inverters along with the proposed inverter are indicated in Table II. As it is seen in this table the H5, and Virtual-dc-bus require five switches, HERIC uses six switches, the other inverters including the proposed one need four active switches. The NPC and the proposed inverter need two extra diodes, however, as the diodes in the proposed inverter are turned on and off in zero current condition, they experience no switching losses. As it is evident, the proposed and Flying-capacitor inverter use, respectively, two and one extra capacitor with respect to the other inverters. As an advantage, the voltage of the capacitors in the proposed topology are spontaneously balanced, which is not the case in the Flying-capacitor inverter as it needs auxiliary circuit and complicated switching methods to balance the voltage of the flying capacitor. Although to proposed inverter needs two inductors in charging path, these inductors are very small and would not add extra weight and cost to the inverter.

As it can be seen from the above paragraph, compared to some of the considered inverters, the proposed inverter uses some extra devices to approach a three-level voltage. This demerit can be ignored when considering the advantage that the voltage gain of the proposed inverter is unity and this important parameter in the NPC, T-type-NPC and Flying-capacitor inverters is half. Furthermore, the switches in the H5, HERIC, NPC, Flying-capacitor and the proposed inverter withstand the peak value of the output voltage (Vp), however, the voltage stress of the unidirectional switches in the T-type-NPC inverter is two times of the peak value of the output voltage (2Vp). Although the proposed inverter needs four capacitors, the voltage across the capacitors is 0.5Vp, as seen in Table II. The voltage stress of the capacitors in NPC, T-type-NPC, and Flying-capacitor is Vp. Hence, the capacitors in the proposed topology are small and cheap.

Other important feature is the possibility to be configured as a three-phase inverter. In this regards, the NPC, T-type-NPC, Flying-capacitor and the proposed inverters can be used as a three-phase converter by connecting three inverter units to a single input dc source. Nevertheless, this is not the case for the H5, HERIC, and Virtual-dc-bus inverters.

In the case of the common-mode voltage, the H5, and HERIC have a constant common-mode voltage equal to the input voltage. As the negative pole of input dc source is connected to the ground of the ac side in the Virtual-dc-bus inverter, this inverter develops zero common-mode voltage. The common-mode voltage in the other inverters including the proposed one varies with the ac-side voltage frequency and has a direct relation with the output current and an inverse relation to the input capacitors and ac-side frequency. Since the ac-side frequency is low compared to the switching frequency, the mentioned common-mode voltage would lead to an insignificant leakage current in grid-tied applications of the proposed inverter.

Fig. 7. Three-level inverter topologies in PV applications, (a) H5 [13], (b) HERIC [14], (c) Virtual-dc-bus [16], (d) NPC [19], (e) T-type-NPC [20], and (f) Flying-capacitor [18].

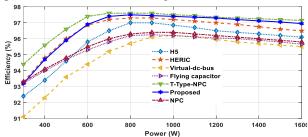

Efficiency is one of the most important parameters in converters. In order to compare the efficiency of the considered inverters, it is assumed that the inverters are all constructed with IXFT50N50P3 switch and VS-249NQ150Pbf diode. The equal series resistance of the capacitors, the switching frequency, line frequency and the peak value of the output voltage are assumed 70 m $\Omega$ , 24 kHz, 50 Hz, and 320 V, respectively. The efficiency of the compared inverters is shown in Fig. 8.

Fig. 8. Efficiency of the considered inverters.

Moreover, there are some other topologies that are based on switched-capacitor concept [11], [12], and [21]. As mentioned earlier, since the capacitors in the switched-capacitor cell are exposed to a hard charge, they experience energy loss as stated in (11). Other than energy loss, the inrush current appeared in these type of converters could increase the components' failure rate and bring about EMI. For instance, a sensor less cascaded half-bridge multilevel inverter, which is proposed in [21], would cause a significant energy loss when transferring the energy from the input source to several cascaded half-bridges cells. Using inductors to smoothly charge the capacitors can prevent the mentioned energy loss. However, using inductor would slow down the charging process and adversely affect the converter

dynamic performance. This can be the main drawback of the switched-capacitor based multilevel inverter in [21]. Since the proposed inverter and the inverters mentioned in Table II are voltage source inverter they could not limit the fault current.

The other solution to address the problems in grid-tied PV system is using two-stage converters. In these kinds of converters, a dc-dc converter is used to track the maximum power point and conditioning the dc-link voltage. To this end a Z-source, quasi-Z-source, boost and dual-boost dc-dc converter are connected to a front-end inverter [22], [23] and [24]. Although these types of converters meet several requirements of grid-tied PV system such as limiting the fault current, they have a complex structure, more passive elements, and require a complicated control strategy. A new two-stage converter is suggested in [25]. This inverter uses two boosting inductors and two diodes to form a dc-dc stage. In order to reduce the number of switches, two switches of the utilized H-bridge are used to fix the dc-voltage link and develop ac voltage simultaneously. Even though this inverter succeeded to reduce a switch and it can effectively limit fault currents, it has caused the controlling process to be very complicated and limited the duty ratio of the booting factor.

In comparison to the proposed inverter, the switched-capacitor based inverter experience higher energy loss and suffer from EMI and inrush current due to not using the charging inductors. Also compared to two-stage converters, the proposed inverter has a very simple structure and controlling strategy. Especially compare to the topology suggested in [25], the proposed inverter uses very smaller inductor and the switches with lower switching stress.

TABLE II.

COMPARISON OF THE CONSIDERED COMMON THREE-LEVEL TOPOLOGIES

| Topology Parameters                                  | H5<br>[13] | HERIC<br>[14] | Virtual<br>-dc-bus<br>[16] | Flying-<br>capacitor<br>[18]         | NPC<br>[19]                             | T-type-NPC [20]                         | Proposed inverter                       |

|------------------------------------------------------|------------|---------------|----------------------------|--------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|

| Number of switches                                   |            | 6             | 5                          | 4                                    | 4                                       | 4                                       | 4                                       |

| Number of diodes                                     |            | -             | -                          | 0                                    | 2                                       | -                                       | 2                                       |

| Number of capacitors                                 |            | 1             | 2                          | 3                                    | 2                                       | 2                                       | 4                                       |

| Total voltage stress of the switches ( $\times Vp$ ) | 4.5        | 5             | 5                          | 4                                    | 4                                       | 6                                       | 4                                       |

| Highest voltage stress of capacitors $(\times Vp)$   | 1          | 1             | 1                          | 1                                    | 1                                       | 1                                       | 0.5                                     |

| Voltage gain                                         | 1          | 1             | 1                          | 0.5                                  | 0.5                                     | 0.5                                     | 1                                       |

| Three-phase possibility                              | No         | No            | No                         | Yes                                  | Yes                                     | Yes                                     | Yes                                     |

| Common-mode-voltage                                  | $V_{dc}$   | $V_{dc}$      | 0                          | $\frac{I_m\cos(\omega t)}{2C\omega}$ | $\frac{I_m \cos(\omega t)}{2C  \omega}$ | $\frac{I_m \cos(\omega t)}{2C  \omega}$ | $\frac{I_m \cos(\omega t)}{2C  \omega}$ |

### VI. PERFORMANCE IN GRID-TIED PV SYSTEMS

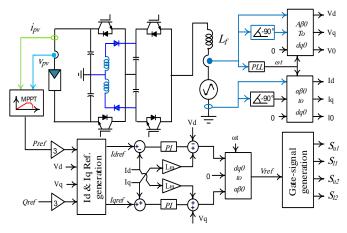

In order to assess the performance of the proposed inverter in PV system, it is used as an interface inverter to deliver the power produced by a PV array to the grid. To do so, Proportional-Integral (PI) controllers are used like shown in Fig. 9. The characteristics of the considered system are listed in Table III. In this system, the observe and perturb

maximum power point tracking algorithm is used to generate active power reference, the reactive power reference is assumed zero.

Fig. 9. Control schematics of the grid-connected PV system.

# TABLE III. CHARACTERISTICS OF THE SIMULATION MODEL

| Parameters                                | Values            |        |  |

|-------------------------------------------|-------------------|--------|--|

| Terminal voltage of PV u                  | 425 V             |        |  |

| Base voltage (Peak)                       | 320 V             |        |  |

| Grid Voltage (peak)                       | 320 V             |        |  |

| Grid Frequency (f)                        | 50 Hz             |        |  |

| $Grid$ -side filter $(L_f)$               | 3.18 mH           |        |  |

| Charging Inductors (Lu,                   | 4 μΗ              |        |  |

| Base Apparent Power (sin                  | 3 kVA             |        |  |

| Base Apparent Power (th                   | 14.4 kVA          |        |  |

| $C_{uI}$ , $C_{lI}$ , $C_{u2}$ , $C_{l2}$ | 2200 μF           |        |  |

| Cpv ( parasitic capacitan                 | 800 nF, 4.6 μF    |        |  |

| Switching Frequency                       | $Su_{I}, S_{II}$  | 24 kHz |  |

|                                           | $Su_2$ , $S_{l2}$ | 50 Hz  |  |

| Kp, Ki (PI coefficients) (a               | 15, 65            |        |  |

| Kp, Ki (PI coefficients) (g               | 0.15, 6.6         |        |  |

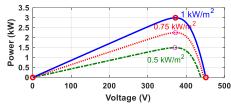

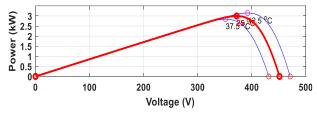

In order to investigate the performance of the proposed topology under different loading conditions, various irradiations are taken into account. Possible active power values for the assumed irradiations are exhibited in Fig. 10.

Fig. 10. Irradiances and related active power curves.

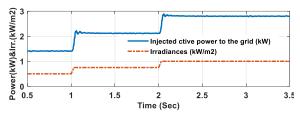

The injected power to the grid along with the irradiance are shown in Fig. 11. As seen in these figure, and referring to Fig. 10, it is evident that the injected power to the grid is according to the produced power of the PV module at the maximum power point and related irradiance.

Fig. 11. Injected power to the grid under different irradiances.

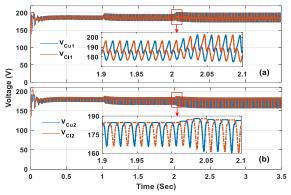

Under the assumed conditions the voltages across the capacitors are shown in Fig. 12. As seen in this figure the voltage across the capacitors are half of the output voltage which can reduce the size and cost of the capacitors. Furthermore, as seen in these figures, the voltage ripple across switched-capacitors (C<sub>u2</sub>, and C<sub>12</sub>) is insignificant because these capacitors reside in the charging mode in every switching cycle and experience a short discharging duration.

Fig. 12. Capacitor voltages (a) across  $C_{ul}$ ,  $C_{ll}$ , and (b) across  $C_{u2}$ ,  $C_{l2}$ .

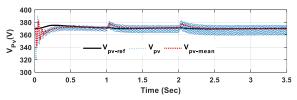

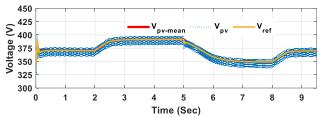

The reference, mean and instantaneous values of the voltage of the dc link (voltage at the output terminals of the PV module), are exhibited in Fig. 13. As seen in this figure, the voltage across the output terminals of the PV module is perfectly set to the reference value which is dictated by the MPPT system.

Fig. 13. Reference, mean and instantanious values of DC link voltage, under 25  $\rm C^o$  with different irradiances.

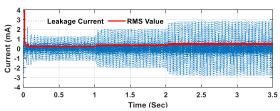

As mentioned earlier one of the most troublesome phenomenon in grid-tied PV system is the capacitive leakage current which appears due to the parasitic capacitor of the PV panels. The leakage current in the

studied system is depicted in Fig. 14. As seen, the RMS value of the leakage current is lower than 1 mA, which is far below the value issued by VDE-AR-N-4105 standard. Thus, it is proved that the proposed inverter has deservedly mitigated the leakage current.

Fig.14. Leakage current from the parasitic capacitors of PV module.

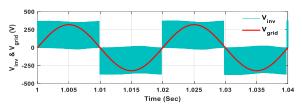

Moreover, the output voltage of the inverter and that of the grid is exhibited in Fig. 15. This figure shows the three-level voltage that is developed through the proposed inverter.

Fig. 15. Output voltage of inverter and grid-voltage.

The performance of the proposed inverter under harsh variation of the input voltage (which can happen under different temperature condition) is considered. by considering different temperatures which necessitates different voltage values on the output terminals of the PV module to track maximum power point, the performance of the proposed inverter is assessed. the maximum power point vs output voltage of the PV module for the assumed irradiance and temperatures is depicted in Fig. 16.

Fig. 16. Maximum power point under irradiance of 1000 W/m<sup>2</sup>, and temperature of [12.5 25 37.5 25] °C.

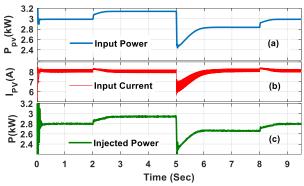

The voltage at the output terminal of PV module (input of the inverter) is shown in Fig.17, and the produced power, input current and the injected current are all exhibited in Fig.18. as seen in these figures, the MPPT system has succeeded to track the maximum power point by varying the terminal voltage of PV module. the input power with a

continuous input current has been properly injected to the grid.

Fig. 17. Reference, mean and instantanious values of DC link voltage, under irradianc of 1000 W/m<sup>2</sup> and tempratures of [12.5 25 37.5 25] C°.

Fig. 18. Powers under dierrent temprature, (a) produced power by PV module, (b) input current, and (c) injected power to the grid.

## VII. Experimental Results

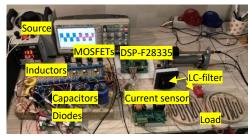

In order to prove the feasibility of the proposed inverter, a lab-scale prototype was constructed and tested under different loading conditions. The prototype is shown in Fig. 19 and the utilized components are listed in table IV.

TABLE IV. COMPONENT CHARACTERISTICS.

| TABLE IV. COMI CIVEIVI CITATORE |             |  |  |  |

|---------------------------------|-------------|--|--|--|

| Components                      | Туре        |  |  |  |

| Switches                        | IRFP450     |  |  |  |

| Opto-coupler                    | TLP250      |  |  |  |

| Microprocessor                  | DSP-F28335  |  |  |  |

| Capacitors                      | 3300 μF     |  |  |  |

| Diodes                          | FFPF20UP40S |  |  |  |

| Output Filter                   | 8 mH+20 μF  |  |  |  |

Fig. 19. Lab-scale prototype of the proposed inverter.

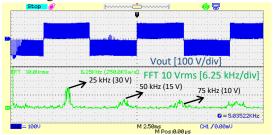

The three-level output voltage and its FFT analysis under no-load condition is shown are Fig. 20. As it is seen in this figure, the harmonics around the switching frequencies are dominant. As it is observable the magnitude of harmonics around the 25 kHz, 50 kHz,

and 75 kHz (dominant harmonics) are 30 V, 15 V, and 10 V, respectively. With these values the THD of the output voltage is calculated to 15.5%.

Fig. 20. Output voltage and its FFT analysis under no-load condition.

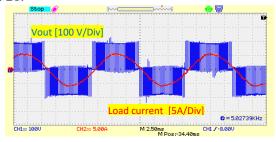

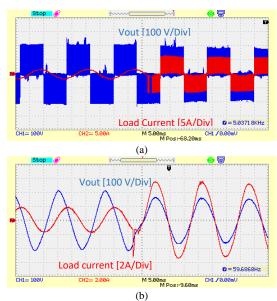

Further, the output voltage and load current under an inductive-resistive load of 30  $\Omega$  +15 mH is shown in Fig. 21.

Fig. 21. Output voltage and load current under an inductive-resistive load.

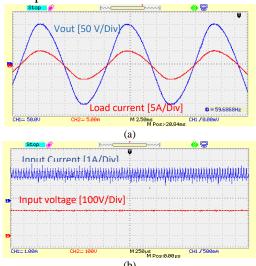

Additionally, the performance of the proposed topology is tested in the presence of an LC filter and a pure load of 30  $\Omega$ . The result is shown in Fig. 22. As seen in this figure the, the load power is 375 W and the input power is 405 W. Thus, the efficiency for the mentioned power is 92.5%.

Fig. 22. Performance in the presence of an LC filter and pure resistive load, (a) output voltage and load current, and (b) input voltage and current.

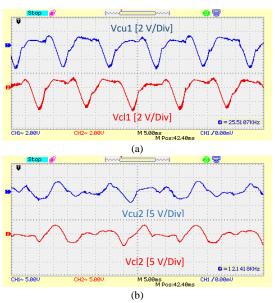

One of the challenging issues in switched-capacitorbased converters is the inrush current that appears when charging the capacitors. This current has a direct relation with the voltage ripple across the capacitors. In order to investigate the inrush current, the voltage ripple (ac components) of the capacitors and charging current of the switched capacitors are investigated. Figs. 23 (a) and (b) show the voltage ripple in the input capacitors.

Fig. 23. Voltage ripple of the capacitors (ac components) (a)  $C_{ul}$  &  $C_{ll}$ , and (b)  $C_{u2}$  &  $C_{l2}$ .

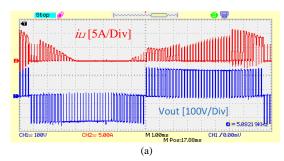

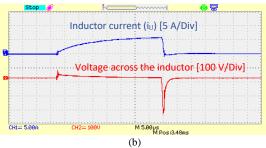

Further, the charging current of the capacitors (charging inductor current) along with the output voltage is depicted in Fig. 24 (a). By referring to Figs. 23 and 24, whereas the proposed inverter has a short discharging duration, the inrush current in this inverter is limited. For more clarity, the charging current and voltage across the charging inductor during one switching cycle are exhibited in Fig. 24(b). this figure proves the analysis provided for Fig. (5).

Fig. 24. Charging current and output voltage, (a) charging current  $(i_{II})$  of one of the capacitors and output voltage during a cycle of line frequency, and (b) charging current and voltage of one of the inductors during a switching cycle.

It is worth mentioning that using small inductors along the charging current path not only reduces the inrush current and its effect on power loss, but also they provide zero current switching condition for the diodes resulting in eliminating the switching losses in these devices. Furthermore, the performance of the proposed inverter under the condition of a dynamic load change is exhibited in Fig. 25. As seen in this figure, the proposed inverter can easily response any dynamic load change.

Fig. 25. Dynamic performance of the proposed inverter.

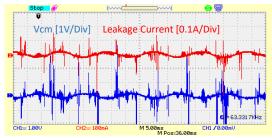

As a PV inverter, the proposed inverter should be able to reduce the leakage current which stems from the parasitic capacitors. In order to assess this capability, an impedance of 300 nF + 2  $\Omega$  was connected between the mid pint and negative polarity of the input dc source. The current passing through this impedance is shown in Fig. 26. As it is evident, the leakage current is under 25 mA.

Fig. 26. Leakage current and common-mode voltage curve.

#### VIII. CONCLUSION

A new three-level inverter with the ability to reduce voltage stress of components, leakage current reduction capability and possibility to configure as a three-phase inverter was proposed. The proposed inverter was constructed by using four switches, two diodes, four low voltage capacitors and two small inductors. In the proposed inverter topology, the common-mode voltage varies with the grid-frequency, and parasitic capacitors of PV panels are in parallel with the input capacitors, so the leakage current in gridtied PV applications of the proposed inverter will be mitigated. The tiny inductors, which are placed in the charging current path of the switched-capacitors provide zero current switching for the diodes leading in reduction in switching losses. By taking into account the above mentioned feature, the proposed inverter was compared with the state-of-the-art three-level inverters in PV applications. For compactness, only the features of the proposed inverter were investigated in a grid-tied PV system, however this inverter can address many problems in other industrial applications like motor drives. In order to prove the feasibility of the proposed inverter, a lab-scale prototype it was tested under different loading conditions.

#### References

- [1] M. N. H. Khan, M. Forouzesh, Y. P. Siwakoti, L. Li, T. Kerekes and F. Blaabjerg, "Transformerless Inverter Topologies for Single-Phase Photovoltaic Systems: A Comparative Review," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 8, no. 1, pp. 805-835, March 2020, doi: 10.1109/JESTPE.2019.2908672.

- [2] W. Li, Y. Gu, H. Luo, W. Cui, X. He and C. Xia, "Topology Review and Derivation Methodology of Single-Phase Transformerless Photovoltaic Inverters for Leakage Current Suppression," in IEEE Transactions on Industrial Electronics, vol. 62, no. 7, pp. 4537-4551, July 2015, doi: 10.1109/TIE.2015.2399278.

- [3] M. Sarhangzadeh, S. H. Hosseini, M. B. B. Sharifian and G. B. Gharehpetian, "Multiinput Direct DC–AC Converter With High-Frequency Link for Clean Power-Generation Systems," in IEEE Transactions on Power Electronics, vol. 26, no. 6, pp. 1777-1789, June 2011, doi: 10.1109/TPEL.2010.2080321.

- [4] Q. Huang, A. Q. Huang, R. Yu, P. Liu and W. Yu, "High-Efficiency and High-Density Single-Phase Dual-Mode Cascaded Buck-Boost

- Multilevel Transformerless PV Inverter With GaN AC Switches," in IEEE Transactions on Power Electronics, vol. 34, no. 8, pp. 7474-7488, Aug. 2019, doi: 10.1109/TPEL.2018.2878586.

- [5] H. K. jahan, M. Abapour, K. Zare, S. H. Hosseini, F. Blaabjerg and Y. Yang, "A Multilevel Inverter with Minimized Components Featuring Self-balancing and Boosting Capabilities for PV Applications," in IEEE Journal of Emerging and Selected Topics in Power Electronics, doi: 10.1109/JESTPE.2019.2922415.

- [6] S. Jahan, S. P. Biswas, S. Haq, M. R. Islam, M. A. P. Mahmud and A. Z. Kouzani, "An Advanced Control Scheme for Voltage Source Inverter Based Grid-Tied PV Systems," in IEEE Transactions on Applied Superconductivity, vol. 31, no. 8, pp. 1-5, Nov. 2021, Art no. 5401705, doi: 10.1109/TASC.2021.3094446.

- [7] K. Zhov, Y. Yang and F. Blaabjerg, "Frequency adaptive repetitive control of grid-tied single-phase PV inverters," 2015 IEEE Energy Conversion Congress and Exposition (ECCE), 2015, pp. 1689-1693, doi: 10.1109/ECCE.2015.7309898.

- [8] H. Xiao, L. Zhang, Z. Wang and M. Cheng, "A New Soft-Switching Configuration and Its Application in Transformerless Photovoltaic Grid-Connected Inverters," in IEEE Transactions on Industrial Electronics, vol. 65, no. 12, pp. 9518-9527, Dec. 2018, doi: 10.1109/TIE.2018.2826481.

- [9] A. K. Gupta, M. S. Joshi and V. Agarwal, "Improved Transformerless Grid-Tied PV Inverter Effectively Operating at Twice the Switching Frequency With Constant CMV and Reactive Power Capability," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 8, no. 4, pp. 3477-3486, Dec. 2020, doi: 10.1109/JESTPE.2019.2943773.

- [10] H. K. Jahan and M. Abapour, "Switched-Capacitor-Based Multilevel Inverter for Grid-Connected Photovoltaic Application," in IEEE Transactions on Power Electronics, vol. 36, no. 9, pp. 10317-10329, Sept. 2021, doi: 10.1109/TPEL.2020.3035598.

- [11] J. F. Ardashir, M. Sabahi, S. H. Hosseini, F. Blaabjerg, E. Babaei and G. B. Gharehpetian, "A Single-Phase Transformerless Inverter With Charge Pump Circuit Concept for Grid-Tied PV Applications," in IEEE Transactions on Industrial Electronics, vol. 64, no. 7, pp. 5403-5415, July 2017, doi: 10.1109/TIE.2016.2645162.

- [12] H. K. Jahan, "A New Transformerless Inverter With Leakage Current Limiting and Voltage Boosting Capabilities for Grid-Connected PV Applications," in IEEE Transactions on Industrial Electronics, vol. 67, no. 12, pp. 10542-10551, Dec. 2020, doi: 10.1109/TIE.2019.2960728.

- [13] Victor, M. et al., US Patent Application, Publication Number US 2005/0286281 A1, 29 December 2005.

- [14] Schmid, H. et al. US Patent 7046534, issued 16 May 2006.

Hossein Khoun Jahan received the M.S. degree in electrical engineering from the University of Shahid Madani of Azerbaijan, Tabriz, Iran, 2011. He received the PhD in power electric system at the University of Tabriz. Tabriz, Iran, 2019. He spent Visiting Scholar at the Department of Energy Aalborg University, Aalborg, Denmark. He was postdoctoral researcher at the university of

Tabriz. He is currently a senior engineer at Azerbaijan Regional Electric Company, Tabriz, Iran. His main research interests are power electronic converter, reliability of power electronic devises, Grid-connected PV systems, Distribution and Transmission systems, and renewable energy.

- [15] J. F. Ardashir, M. Gasemi, B. Rozmeh, S. Peyghami and F. Blaabjerg, "A Six-Switch Five-Level Transformer-less Inverter without Leakage Current for Grid-Tied PV System," 2021 IEEE Energy Conversion Congress and Exposition (ECCE), 2021, pp. 2550-2556, doi: 10.1109/ECCE47101.2021.9595014.

- [16] Y. Gu, W. Li, Y. Zhao, B. Yang, C. Li, and X. He, "transformerless inverter with virtual dc bus concept for cost-effective grid-connected pv power systems," *IEEE Trans. Power Electron.* vol. 28, no. 2, pp. 793-805, Feb. 2013.

- [17] Y. P. Siwakoti and F. Blaabjerg, "Common-Ground-Type Transformerless Inverters for Single-Phase Solar Photovoltaic Systems," in IEEE Transactions on Industrial Electronics, vol. 65, no. 3, pp. 2100-2111, March 2018, doi: 10.1109/TIE.2017.2740821.

- [18] C. Feng, J. Liang and V. G. Agelidis, "Modified Phase-Shifted PWM Control for Flying Capacitor Multilevel Converters," in IEEE Transactions on Power Electronics, vol. 22, no. 1, pp. 178-185, Jan. 2007, doi: 10.1109/TPEL.2006.886600.

- [19] L. Ma, T. Kerekes, P. Rodriguez, X. Jin, R. Teodorescu, and M. Liserre "A new PWM strategy for grid-connected half-bridge active NPC converters with losses distribution balancing mechanism," *IEEE Trans. Power Electron.* vol. 30, no. 9, pp. 5331-5340, Sept. 2015.

- [20] J. Wang, X. Mu, and Q. K. Li, "Study of passivity-based decoupling control of T-NPC PV grid-connected inverter," *IEEE Trans. Ind. Electron.*, vol. 64, no. 9, pp. 7542-7552, Sept. 2017.

- [21] J. Fang, Z. Li and S. M. Goetz, "Multilevel Converters With Symmetrical Half-Bridge Submodules and Sensorless Voltage Balance," in IEEE Transactions on Power Electronics, vol. 36, no. 1, pp. 447-458, Jan. 2021, doi: 10.1109/TPEL.2020.3000469.

- [22] M. Meraj, S. Rahman, A. Iqbal and L. Ben-Brahim, "Common Mode Voltage Reduction in a Single-Phase Quasi Z-Source Inverter for Transformerless Grid-Connected Solar PV Applications," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 7, no. 2, pp. 1352-1363, June 2019, doi: 10.1109/JESTPE.2018.2867521.

- [23] C. K. Das, K. Annamalai and S. Veeramraju Tirumala, "A Quasi-Z-Source-Based Five-Level PV Inverter With Leakage Current Reduction," in IEEE Transactions on Industry Applications, vol. 58, no. 1, pp. 400-412, Jan.-Feb. 2022, doi: 10.1109/TIA.2021.3119526.

- [24] Y. Zhou, W. Huang, P. Zhao and J. Zhao, "A Transformerless Grid-Connected Photovoltaic System Based on the Coupled Inductor Single-Stage Boost Three-Phase Inverter," in IEEE Transactions on Power Electronics, vol. 29, no. 3, pp. 1041-1046, March 2014, doi: 10.1109/TPEL.2013.2274463.

- [25] M. Chen and P. C. Loh, "A Dual-Boost H-Bridge Inverter With Common Ground for Photovoltaic Interfacing," in IEEE Transactions on Industrial Electronics, vol. 68, no. 10, pp. 9515-9526, Oct. 2021, doi: 10.1109/TIE.2020.3026275.

Mitra Sarhangzadeh (S'09) received the B.Sc., M.Sc. and Ph.D. degrees in 2001, 2004 and 2011 respectively from University of Tabriz, Iran. She is Assistant Professor in Department of Electrical Engineering, Tabriz Branch, Islamic Azad University, Tabriz, Iran. Her research interests include Power Electronic Application in Renewable Energy Systems, Energy Management in Power

Electronic Systems, Modeling and Control of Power Electronic Systems, Electrified Railway Systems, Inverters and Power Quality Compensation Systems such as SVC, UPQC, FACTS devices.

Jaber Fallah Ardashir received the B.Sc., M.Sc., and Ph.D. degrees in electrical engineering from the Electrical Engineering Department, Azerbaijan Shahid Madani University, Zanjan University, and Tabriz University in 2010, 2012, and 2017, respectively. From 2015 to 2016, he was a Visiting Ph.D. Scholar with the Department of Energy, Aalborg University, Aalborg, Denmark. He is

currently an Assistant Professor of electrical power engineering with Tabriz Branch, Islamic Azad University. His research interests include power electronic converters, renewable energy systems and reliability.

Frede Blaabjerg (S'86–M'88–SM'97–F'03) was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. From 1988 to 1992, he got the PhD degree in Electrical Engineering at Aalborg University in 1995. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor of power electronics and drives in 1998 at AAU Energy. From 2017 he became a Villum Investigator. He is honoris causa at University Politehnica Timisoara (UPT), Romania in 2017 and Tallinn

Technical University (TTU), Estonia in 2018.

His current research interests include power electronics and its applications such as in wind turbines, PV systems, reliability, harmonics and adjustable speed drives. He has published more than 600 journal papers in the fields of power electronics and its applications. He is the co-author of four monographs and editor of ten books in power electronics and its applications.

He has received 33 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award 2014, the Villum Kann Rasmussen Research Award 2014, the Global Energy Prize in 2019 and the 2020 IEEE Edison Medal. He was the Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS from 2006 to 2012. He has been Distinguished Lecturer for the IEEE Power Electronics Society from 2005 to 2007 and for the IEEE Industry Applications Society from 2010 to 2011 as well as 2017 to 2018. In 2019-2020 he served as a President of IEEE Power Electronics Society. He has been Vice-President of the Danish Academy of Technical Sciences.

He is nominated in 2014-2020 by Thomson Reuters to be between the most 250 cited researchers in Engineering in the world.