# **Aalborg Universitet**

# Single-Source Cascaded Multilevel Inverter With Voltage-Boost Submodule and **Continuous Input Current for Photovoltaic Applications**

Chen, Manxin; Yang, Yongheng; Liu, Xiong; Loh, Poh Chiang; Blaabjerg, Frede

Published in: I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2021.3098015

Publication date: 2022

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Chen, M., Yang, Y., Liu, X., Loh, P. C., & Blaabjerg, F. (2022). Single-Source Cascaded Multilevel Inverter With Voltage-Boost Submodule and Continuous Input Current for Photovoltaic Applications. *I E E Transactions on Power Electronics*, *37*(1), 955-970. Article 9492008. https://doi.org/10.1109/TPEL.2021.3098015

# **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 04, 2025

# Single-Source Cascaded Multilevel Inverter with Voltage-Boost Submodule and Continuous Input Current for Photovoltaic Applications

Manxin Chen, Student Member, IEEE, Yongheng Yang, Senior Member, IEEE, Xiong Liu, Senior Member, IEEE, Poh Chiang Loh, and Frede Blaabjerg, Fellow, IEEE

Abstract—Cascaded multilevel inverter produces a step-up output voltage by series-connection of several submodules supplied by isolated dc sources which can be implemented by photovoltaic (PV) sources. The unbalanced power provided by different PV sources may however distort the output voltage. To use a single dc source while retaining the voltage boosting, this paper proposes a novel cascaded multilevel inverter based on a four-switch submodule. It is conditioned by an input inductor, which discharges with boosted voltages across the submodules. Furthermore, a continuous input current is achieved by the inductor. The proposed inverter can be extended to higher voltage-level operations using capacitors to supply its extended submodules. To avoid switched-capacitive charging, a two-phase configuration where capacitors are directly charged by the inductive input current is presented. The voltages of capacitors are well balanced at the same average value and feature a similar ripple. The operating principles and pulse-width modulation scheme of the two-phase inverter are described. Theoretical analysis, calculations, and comparisons with the priorart cascaded multilevel inverters illustrate the superiorities of the proposed inverter. Simulation and experimental results agree well with each other and verify the feasibility of the proposed inverter for PV power applications.

Index Terms—Cascaded multilevel inverter, continuous input current, PV applications, single dc source, voltage boosting.

# I. INTRODUCTION

WHILE two-level voltage-source inverters have reached maturity and presented certain limitations for medium-voltage applications, many attempts to advance multilevel inverters (MLIs) with reduced voltage stresses on power switches have been made [1]–[3]. Additionally, the low total harmonic distortion (THD) of the output voltage achieved by MLIs has made them more and more commonly seen in applications requiring a high-quality output voltage. To date, MLIs are widely used in power electronics systems such as the ac adjustable speed drives [4], flexible ac transmission [5], and renewable energy generation [6].

Manuscript received March 7, revised June 9, and accepted July 13. (Corresponding author: Xiong Liu).

Manxin Chen and Poh Chiang Loh are with the Department of Electronic Engineering, The Chinese University of Hong Kong, Shatin, New Territories, Hong Kong (email: mxchen@link.cuhk.edu.hk; pcloh@ee.cuhk.edu.hk).

Yongheng Yang is with the College of Electrical Engineering, Zhejiang University, Hangzhou 310027, China (email: yang yh@zju.edu.cn).

Xiong Liu is with Energy Electricity Research Center, Jinan University, Zhuhai 519070, China (email: liushawn123@ieee. org).

Frede Blaabjerg is with the Department of Energy Technology, Aalborg University, 9220 Aalborg East, Denmark (email: fbl@et.aau.dk).

In general, the traditional MLIs are categorized into three groups including the cascaded multilevel inverter (CMI) [1], neutral-point-clamped (NPC) [2], and the flying capacitor (FC) inverters [3]. Among them, the CMI, which is mostly based on the series-connection of several full-bridges to form the cascaded H-bridge (CHB) inverter has been demonstrated to be advantageous over other MLIs in terms of producing a boosted voltage. However, it sometimes suffers from a large number of isolated dc sources [7]–[10].

For renewable energy applications such as PV power generation, the source requirement can be easily met due to the widespread PV sources that can be installed separately. The CMIs, however, still face certain challenges related to the variable voltage/power of the PV sources. If each seriesconnected submodule (SM) is directly supplied by an individual PV source, the same output current flowing through all of the SMs causes mismatching issues, since, in most cases, the active powers provided by different PV sources are unbalanced. The ac output voltage may be over-modulated, thus deteriorating the waveform quality [11].

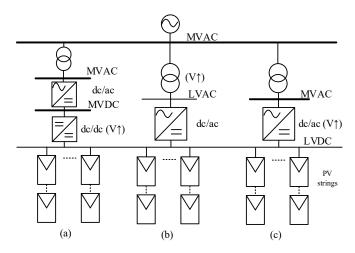

Despite that, the boosted output voltage of the CMIs makes them suitable for PV systems to reduce the requirement for high step-up transformers, as illustrated in Fig. 1 [11], [12]. Fig. 1(a) shows that a dc-dc front-end converter is used to boost the low-voltage dc (LVDC) link to a medium-voltage dc (MVDC) link for supplying a rear-end inverter. The two-stage power conversion, however, may require a larger number of components [12]. Alternatively, the low-voltage ac (LVAC) link can be interfaced with the medium-voltage ac (MVAC) link using a high step-up line transformer with a large turns-ratio (Fig. 1(b)). It is therefore promising to obtain a step-up voltage at the inverter output (Fig. 1(c)) and one straightforward solution is to use CMIs. But the mismatch problems among many of the PV sources need to be addressed [11].

Recently, reduced dc-source CHB inverter using capacitors to supply its SMs are presented [13]–[14]. However, the voltage balance of the capacitors becomes crucial and additional voltage sensing circuits cooperating with modified pulse-width modulation (PWM) scheme are required. Moreover, the voltages of the capacitors must be balanced at different values lower than the dc voltage. Different voltage-rating devices are used and the total output voltage is lowered [15]. Nonetheless, due to reduced source requirement, using capacitors for supplying some of the SMs has been proven to be an effective strategy [16]–[21].

With capacitors as the intermediate energy-storage devices, one alternative is to cascade several switched-capacitor (SC)

Fig. 1. Diagrams of PV power generation interfacing with MVAC link: voltage boosting (V↑) achieved by (a) step-up dc-dc converter, (b) step-up transformer, and (c) step-up dc-ac inverter.

Fig. 2. Prior-art CMIs using (a), (b) SCs with a single dc source [19], [20], and (c) SCs with a single dc source and auxiliary charging circuits [23].

SMs that generate different output voltages from a seriesparallel conversion. Despite that, switches used for the rear-end HB have to withstand the maximum output voltage, which requires high-voltage devices [16]—[18].

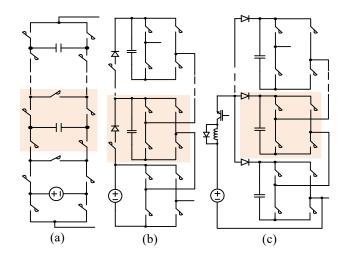

Cascaded SC MLI without the rear-end full-bridge is presented in [19], where a unique switching cell consisting of 5 power switches is used, as shown in Fig. 2(a). It exhibits an inherent polarity reversal capability and induces a uniform voltage on its devices. A similar approach is presented in [20] based on an extendable SC circuit (Fig. 2(b)). Both inverters use a single dc source and a number of floating capacitors. Different from the single-source CHB inverter [13]-[15], the charging currents of the capacitors are independent of the output current, and thus, the voltages across the capacitors can be maintained close to the dc voltage. However, the source-voltage regulation is not investigated and a voltage drop in the dc source essentially lowers the voltages across SMs. As a result, the total attainable voltage becomes lower. Additional dc-dc voltage stages may be required to address the source-voltage deficiency, as discussed in [21]–[23]. Note that, in [23] (Fig. 2(c)), a basic boost stage

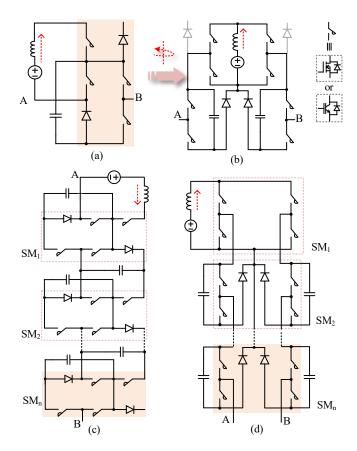

Fig. 3. Illustrations of the (a) proposed SM and (c) the one-phase  $(1\phi)$  extension of the proposed CMI; (b) two-phase  $(2\phi)$  symmetrical inverter topology and (d) the  $2\phi$  extension.

with multiple outputs is used to supply all capacitors. However, the switch and output diodes in the boost stage experiences high voltages.

In light of the above issues, this paper proposes a novel CMI, which is fed by a single dc source and uses capacitors to supply its SMs. The derivation of the proposed CMI begins with a basic SM that can be implemented by two half-bridges, as shown in Fig. 3 (a). It can be extended for a high voltage-level operation, using SC technique (see Fig. 3(c)) [24], [25].

In addition, the proposed CMI can be extended in a two-phase  $(2\phi)$  configuration. For that, a five-level inverter is preliminarily derived as shown in Fig. 3(b). The resultant  $2\phi$  five-level inverter is extended using a SM consisting of 4 switches and 2 diodes (see Fig. 3(d)). Both extensions in Fig. 3(c) and (d) have the following key features.

- 1) A single dc source for multiple series-connected SMs;

- 2) Built-in voltage boosting for stepping up the SM voltage and achieving source-voltage regulation;

- Voltages across the capacitors remain steady and balanced among the SMs automatically;

- 4) A continuous input current suitable for interfacing with renewable energy sources.

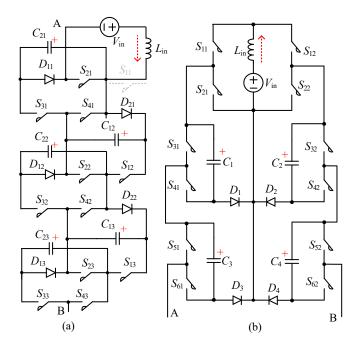

Circuit configurations of  $1\phi$  and  $2\phi$  seven-level inverters are exemplified as in Fig. 4. It is noticed that the  $1\phi$  topology uses one less switch since it maintains a continuous input current and thus,  $S_{11}$  is no longer necessary. However, the  $1\phi$  topology causes inrush switched-capacitive current, which remains a

Fig. 4. Proposed cascaded seven-level inverter configured in (a)  $1\phi$  topology (one less switch) and (b)  $2\phi$  topology.

concern for MV applications. Differently, the 2φ topology is directly charged by the inductive input current. Therefore, the operating principles of the 2φ CMI are discussed in detail in this paper. As for circuit components, the 2φ CMI uses the same number of switches as that of the conventional CHB inverter. The complexity of the proposed CMI is not high. An input inductor is required to step up the SM voltage, which is illustrated in Section II. The operating states and PWM scheme of the 2φ seven-level inverter are also presented. Theoretical analyses of voltage/current ratings, power losses, and commonmode voltage are presented in Section III. Section IV compares the proposed CMI with the prior-art MLIs to discuss the pros and cons. Simulation and experimental results are then given in Section V before a conclusion is drawn in Section VI.

## II. TWO-PHASE EXTENSION OF THE PROPOSED CMI

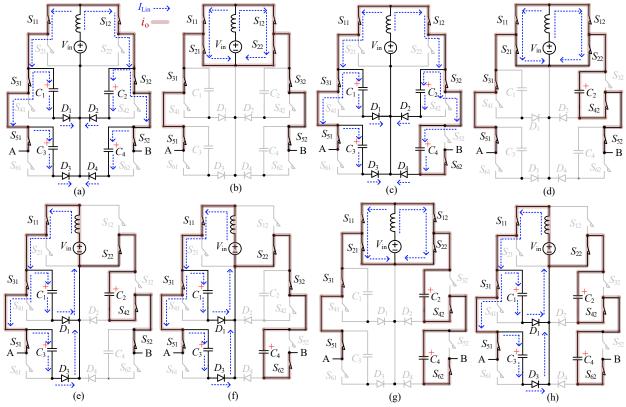

# A. Operating States

Assuming that the capacitors are with relatively large capacitances so that voltages across them remain steady with the same average value of  $V_{\rm C}$ , to be illustrated in Subsection C. Voltage levels across the output terminals ( $v_{\rm AB}$ ) during the positive half-cycle are 0,  $V_{\rm C}$ ,  $2V_{\rm C}$ , and  $3V_{\rm C}$ . To produce them, eight switching states are exemplified and described next.

Level 0 ( $v_{AB} = 0$ ): Fig. 5(a) shows the operating state where the inductor  $L_{in}$  is discharged to all capacitors, forming thus four discharging loops. Which discharging loop is established depends on the instantaneous voltages of capacitors. When capacitors  $C_1$  and  $C_3$  present lower voltages during the positive half-cycle, they are charged by  $L_{in}$ . Otherwise,  $C_2$  and  $C_4$  are charged. When switches  $S_{21}$  and  $S_{22}$  are turned on,  $L_{in}$  is charged by the dc source, and the operating state is shown in Fig. 5(b).

Level 1 ( $v_{AB} = V_C$ ): Fig. 5(c) shows the operating state where the capacitor  $C_4$  is discharged by the load current, maintaining the voltage of  $V_C$  across the output terminals. Similarly, the

inductor enters its charge state by turning on  $S_{21}$  and  $S_{22}$ . Moreover, aiming to keep voltages of  $C_2$  and  $C_4$  close to each other,  $C_2$  is made to discharge to the output in this state as shown in Fig. 5(d).

Level 2 ( $v_{AB} = 2V_C$ ): Fig. 5(e) and (f) show two operating states when  $C_2$  or  $C_4$  is placed at the output current path. Different from the previous states, the load current flows through the dc source. When the input current ( $I_{in}$ ) is larger than the load current ( $i_0$ ), the inductor keeps discharging to the capacitors  $C_1$  or/and  $C_3$ , and the voltage across the output is equal to  $2V_C$ . When  $I_{in}$  is equal to  $i_0$ , the inductor does not provide energy to the capacitors and the output voltage is reduced to ( $V_C + V_{in}$ ). The latter could occur under light load conditions, which occupies a relatively small duration since for the proposed single-source boost inverter, the average input current  $I_{in}$  is larger than the maximum output current  $i_{omax}$ , to be illustrated in the next subsection. When the inductor is charged in Fig. 5(g), the two capacitors  $C_2$  and  $C_4$  both discharge to the output to maintain the voltage level of  $2V_C$ .

Level 3 ( $v_{AB} = 3V_C$ ): Fig. 5(h) shows the operating state when the output voltage is  $3V_C$ . Similarly, the load current flows through the dc source. At light load conditions, the output voltage drops to  $(2V_C + V_{in})$ . Both capacitors  $C_2$  and  $C_4$  discharge to the output with their voltage dropping quickly in this state. As the discharging currents of  $C_2$  and  $C_4$  are the same  $(i_0)$ , their voltages keep close to each other.

Due to the symmetrical structure, capacitors  $C_1$  and  $C_3$  discharge during the negative half-cycle, which implies that the average voltages of capacitors and their ripples are the same. Moreover, the average voltage of capacitors can be regulated by controlling the charging duty ratio of the  $L_{\rm in}$  through the levelshift (LS) PWM scheme.

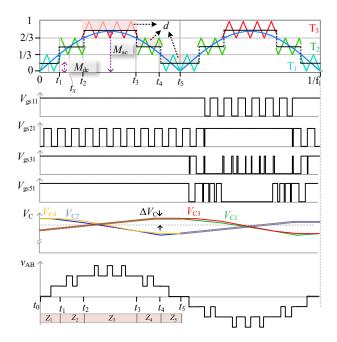

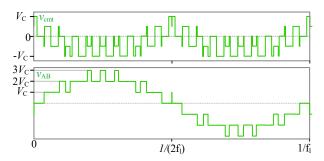

### B. LS PWM Scheme

To implement the LS PWM scheme for the  $2\phi$  seven-level inverter, three carriers  $(T_1-T_3)$  with the same frequency, phase, and peak-to-peak amplitude are deposited as shown in Fig. 6. A half-wave sinusoidal signal  $(0 < t < 1/(2f_1))$  is used as the modulation signal which is expressed as

$$v_{\rm ref} = M_{ac} \sin(2\pi f_1 t) \tag{1}$$

where  $M_{ac}$  is the amplitude of the modulation signal, and  $f_l$  is the fundamental frequency.

Additionally, a stepped dc signal  $(M_{\rm dc})$  is used to produce the shoot-through duty ratio for charging  $L_{\rm in}$  whenever  $M_{\rm dc}$  is less than the carrier in each carrier band. Considering that a constant dc signal  $M_{\rm dc}$  (0 <  $M_{\rm dc}$   $\leq$  1/3) is used and that the magnitude between two adjacent steps is 1/3, a constant inductive-charge duty ratio  $d = (1-3M_{\rm dc})$  can then be obtained in each switching period  $(T_{\rm s})$ . As seen from Fig. 5, when  $L_{\rm in}$  is discharged, the average discharging voltage of the inductor is found as  $(V_{\rm in}-V_{\rm C})$ . Applying volt-second balance to  $L_{\rm in}$ , the following equation is written

$$V_{in}dT_s + (V_{in} - V_C)(1 - d)T_s = 0 (2)$$

Consequently, the voltage  $V_{\rm C}$  is found as

$$V_C = V_{in}/(3M_{dc}) \tag{3}$$

Using Eq. (3), the ac voltage gain is calculated by

Fig. 5. Operating states of the  $2\phi$  seven-level inverter during positive half-cycle: (a), (b) Level 0; (c), (d) Level 1; (e), (f), (g) Level 2; and (h) Level 3 with possible input inductor current ( $I_{\text{Lin}}$ ) and output current ( $I_{\text{O}}$ ) paths.

$$G_{ac} = 3M_{ac}V_C/V_{in} = M_{ac}/M_{dc} \tag{4}$$

Furthermore, for a unity power factor operation, the relationship between the input current  $(I_{in})$  and the maximum output current  $(I_{omax})$  can then be established as

$$I_{in} = I_{omax} M_{ac} / (2M_{dc}) \tag{5}$$

To generate a seven-level output voltage,  $M_{\rm ac}$  should fulfill  $2/3 < M_{\rm ac} < 1$ . Additionally,  $M_{\rm dc}$  is confined to 1/3, i.e.,  $0 < M_{\rm dc} < 1/3$ . Therefore, it implies that the average input current should be larger than the maximum of the output current of the proposed  $2\phi$  CMI, which agrees well with the operating states in Fig. 5(e), (f), and (h). Though the output current flows through  $L_{\rm in}$ , it can still discharge to capacitors to maintain a boosted  $V_{\rm C}$ . Furthermore, both the inductive currents  $I_{\rm in}$  and  $i_{\rm o}$  are not disrupted abruptly when transiting from any inductor-charge to -discharge states.

Additionally, due to the cascaded feature, the phase-shift (PS) PWM scheme can also be applied to the  $2\phi$  CMI. Notably, the switching frequency for each SM can then be reduced while maintaining relatively high-quality output waveforms using the PS PWM scheme. However, the input current features a higher ripple if the switching frequency of SM<sub>1</sub> is too small.

Under the LS PWM scheme, the positive half-cycle is divided into five zones  $Z_1$  to  $Z_5$ . It is observed that capacitors are charged or discharged at a low frequency, featuring a low-frequency ripple as analyzed next.

C. Capacitor Voltage Ripple

Letting the modulation reference  $v_{ref}$  be 1/3, the duration of zone  $Z_1$  can then be calculated by finding  $t_1$ , according to

$$t_1 = \arcsin(3M_{ac})^{-1}/2\pi f_l \tag{6}$$

The same analysis applies to other zones by finding  $t_2$  to  $t_4$ . As seen in Fig. 5 (d) and (e), the capacitor  $C_2$  discharges to the output during Levels 1 and 2. Its reflection in Fig. 6 is that when the modulation reference  $v_{\rm ref} > (M_{\rm dc} + 1/3)$  in zone  $Z_2$ , the capacitor  $C_2$  keeps discharging to the output with its voltage dropping. The charge transferred from  $C_2$  to the output is calculated by

$$Q_{C2_{Z2}} = \int_{t_x}^{t_2} i_o(t) dt$$

(7)

where  $t_x$  is expressed as  $t_x = t_1 + 3M_{dc}(t_2 - t_1)$ .

Furthermore, the capacitor  $C_2$  discharges intermittently during zone  $Z_3$  which includes states in Fig. 5(f), (g), and (h). Since the three states account for  $(3v_{\rm ref}-3M_{\rm dc}-1)$  of the total duration  $(t_3-t_2)$  of zone  $Z_3$ , the discharge of capacitor  $C_2$  during zone  $Z_3$  is thus calculated by

$$Q_{C2_{Z3}} = \int_{t_2}^{t_3} i_o(t) (3v_{\text{ref}} - 3M_{dc} - 1) dt$$

(8)

Using Eqs. (7) and (8), the total charge loss of the capacitor  $C_2$  during the positive half-cycle is calculated by

$$Q_{C2} = 2Q_{C2\ Z2} + Q_{C2\ Z3} \tag{9}$$

The voltage drops across the capacitor  $C_2$  and the associate voltage ripple is calculated by

$$\Delta V_{C2} = Q_{C2}/2C_2 \tag{10}$$

Fig. 6. Level-shift (LS) PWM scheme for the  $2\phi$  seven-level inverter (gating signals of  $S_{41} = \overline{S}_{31}$  and  $S_{61} = \overline{S}_{51}$ ) and the resultant key voltages.

The same analysis applies to the capacitor  $C_4$ , whose voltage keeps close to that of  $C_2$ . For the other two capacitors ( $C_1$  and  $C_3$ ), their voltage ripples can also be analyzed following the same procedure. In fact, due to the symmetrical structure of the  $2\phi$  CMI, it can be deduced that the voltage ripples of capacitors  $C_1$  and  $C_3$  are equal to those of the  $C_2$  and  $C_4$ , respectively. If a low ripple voltage such that  $\Delta V_C \leq 10 \% V_C$  must be ensured, the capacitances should be selected according to

$$C_1(C_2) \ge 5 \frac{Q_{C2}}{V_C}$$

, and  $C_3(C_4) \ge 5 \frac{Q_{C4}}{V_C}$  (11)

Based on the above criterion and under the nominal operating power of 1 kW, the theoretical capacitances should fulfill  $C_1$  ( $C_2$ )  $\geq 0.46$  mF and  $C_3$  ( $C_4$ )  $\geq 0.43$  mF, respectively.

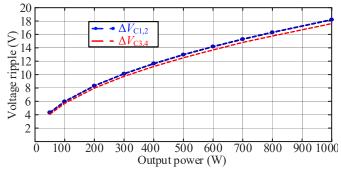

Accordingly, the numerical calculations of the ripple voltages of the four capacitors (0.47 mF each) versus the output power are studied in Fig. 7. As seen, the voltage ripples of capacitors are at a similar level. They increase as the output power rises, which is expected since the output current becomes larger. Therefore, to maintain a low voltage ripple across each capacitor, it is reasonable to use large capacitances suggested by Eq. (11). Furthermore, the total installed energy of capacitors is

$$E = \frac{1}{2}CV^2 \times 4 = 37.6 \text{ J/kW}$$

(12)

It should be mentioned that when the allowable voltage ripples of capacitors are larger, smaller capacitances can be considered to reduce the total installed energy, which is demonstrated in the simulated MV PV power generation using 0.25-mF capacitors.

# III. THEORETICAL ANALYSIS OF THE TWO-PHASE CMI

### A. Voltage and Current Stresses

According to the eight operating states shown in Fig. 5, the switches are clamped by the voltages across capacitors when they are turned off. The voltage stresses on the switches are thus

Fig. 7. Calculated voltage ripples of the capacitors versus output power.

the same, as given by  $V_{\rm ds} = V_{\rm C}$ . The blocking voltages of diodes are however different. The peak inverse voltages of  $D_3$  and  $D_4$  are  $2V_{\rm C}$ , higher than those of  $D_1$  and  $D_2$  ( $V_{\rm C}$ ). Furthermore, the currents flowing through switches are different as discussed next.

Assuming that the  $2\phi$  CMI operates with unity power factor, it is observed from Fig. 6 that the capacitors  $C_1$  and  $C_3$  are charged during the positive half-cycle when the input and output currents flow in the same direction. Due to the cascaded feature, the charging current of the capacitor in SM<sub>n</sub> must be transferred by switches in SM<sub>(n-1)</sub>. It should however be mentioned that the current stresses of switches in SM<sub>n</sub> are smaller than those of SM<sub>(n-1)</sub>. That is, the maximum current stress is induced on switches of SM<sub>1</sub>, which is estimated as the sum of the maximum input and output currents ( $I_{\rm in} + i_{\rm omax}$ ). During the positive half-cycle, assuming that the inductor current is discharged to the two capacitors  $C_1$  and  $C_3$  equally. The maximum current through switches in SM<sub>2</sub> is then given by  $(1/2I_{\rm in} + i_{\rm omax})$ . For SM<sub>3</sub>, it conducts only the output current, the current stresses on switches in SM<sub>3</sub> are  $i_{\rm omax}$ .

With different conducting currents, switches may present different switching losses. Assuming that the 2φ CMI operates under the unity power factor, the switching losses of switches are analyzed according to the five zones shown in Fig. 6.

## B. Switching Losses Under the LS PWM Scheme

Zone  $Z_1$  ( $t_0$  to  $t_1$ ): in this zone, switches  $S_{22}$ ,  $S_{52}$ , and  $S_{62}$  are switched at the carrier frequency  $f_s$ . The current flowing through switch  $S_{22}$  is  $I_{s22} = 1/2(I_{in} + i_o)$ , while the currents of switches  $S_{51}$  and  $S_{61}$  are the output current:  $I_{s51} = I_{s61} = i_o$ . Therefore, the switching losses of switches  $S_{22}$ ,  $S_{52}$ , and  $S_{62}$  in this zone are respectively calculated by

$$P_{sw22\_1} = \frac{V_{ds}f_{s}(t_{on} + t_{off})}{2(t_{1} - t_{0})} \int_{t_{0}}^{t_{1}} \frac{1}{2} (I_{in} + i_{o}(t)) dt$$

(13)

and

$$P_{sw52\_1} = P_{sw62\_1} = \frac{v_{ds}f_s(t_{on} + t_{off})}{2(t_1 - t_0)} \int_{t_0}^{t_1} \frac{1}{2}i_o(t) dt$$

(14)

where  $t_{\text{on}}$  and  $t_{\text{off}}$  are the turn-on and turn-off durations of the switches, respectively.

Furthermore, when  $v_{\text{ref}} > M_{\text{dc}}$ , switches  $S_{32}$  and  $S_{42}$  begin to operate at the carrier frequency from  $(2t_1-t_x)$  to  $t_1$ . Their conducting currents are  $I_{\text{s32}} = I_{\text{s42}} = i_{\text{o}}$ . The switching losses of them in zone  $Z_1$  are respectively calculated by

$$P_{sw32\_1} = P_{sw42\_1} = \frac{V_{ds}f_{s}(t_{on} + t_{off})}{2(t_{r} - t_{1})} \int_{2t_{1} - t_{x}}^{t_{1}} i_{o}(t) dt \quad (15)$$

Zone  $Z_2$  ( $t_1$  to  $t_2$ ): switches  $S_{12}$ ,  $S_{52}$ , and  $S_{62}$  are switched at the carrier frequency. The current of switch  $S_{12}$  is  $0.5(I_{\rm in} - i_{\rm o})$ , while switches  $S_{52}$  and  $S_{62}$  conduct the output current  $i_{\rm o}$ . The switching losses of them are thus calculated by

$$P_{sw12\_2} = \frac{V_{ds}f_s(t_{on} + t_{off})}{2(t_2 - t_1)} \int_{t_1}^{t_2} \frac{1}{2} (I_{in} - i_o(t)) dt$$

(16)

and

$$P_{sw62\_2} = P_{s52\_2} = \frac{V_{ds}f_s(t_{on} + t_{off})}{2(t_2 - t_1)} \int_{t_1}^{t_2} i_o(t) dt$$

(17)

Furthermore, from  $t_1$  to  $t_x$ , switches  $S_{22}$ ,  $S_{32}$ , and  $S_{42}$  still operate at the carrier frequency, their switching losses are, respectively, calculated by

$$P_{sw22\_1} = \frac{V_{ds}f_s(t_{on} + t_{off})}{2(t_r - t_1)} \int_{t_1}^{t_x} \frac{1}{2} (I_{in} + i_o(t)) dt$$

(18)

$$P_{sw32\_2} = \frac{V_{ds}f_{s}(t_{on} + t_{off})}{2(t_{x} - t_{1})} \int_{t_{1}}^{t_{x}} i_{o}(t) dt$$

(19)

and

$$P_{sw42\_2} = \frac{V_{ds}f_s(t_{on} + t_{off})}{2(t_x - t_1)} \int_{t_1}^{t_x} i_o(t) dt$$

(20)

Zone  $Z_3$  ( $t_2$  to  $t_3$ ): switches  $S_{12}$ ,  $S_{32}$ , and  $S_{42}$  operate at the carrier frequency. The conducting current of  $S_{12}$  is  $0.5(I_{\rm in}-i_{\rm o})$  while for switches  $S_{32}$  and  $S_{42}$ , their conducting currents are both  $i_{\rm o}$ . Therefore, the switching losses are calculated by

$$P_{sw12\_3} = \frac{V_{ds}f_s(t_{on} + t_{off})}{2(t_3 - t_2)} \int_{t_2}^{t_3} \frac{1}{2} (I_{in} - i_o(t)) dt$$

(21)

and

$$P_{sw32\_3} = P_{s42\_3} = \frac{V_{ds}f_s(t_{on} + t_{off})}{2(t_3 - t_2)} \int_{t_2}^{t_3} i_o(t) dt$$

(22)

Switching losses in zones  $Z_4$  and  $Z_5$  can be found due to the symmetry. Throughout the positive half-cycle, the switch  $S_{21}$  operates at the carrier frequency. As seen from Fig. 5(b), (d), and (g), the inductor-charge and output currents flow through the switch  $S_{21}$ , whose conducting current is  $I_{s21} = 0.5(I_{in} - i_o)$ . The switching losses of  $S_{21}$  are thus calculated by

$$P_{sw21} = \frac{V_{ds}f_{s}(t_{on} + t_{off})}{2} \frac{f_{1}}{2} \int_{t_{0}}^{t_{5}} \frac{1}{2} (I_{in} - i_{o}(t)) dt$$

(23)

Under the LS PWM scheme, although all switches need to operate at the carrier frequency during some zones of a fundamental cycle, it is deduced from Fig. 6 that except for the switches  $S_{21}$  and  $S_{22}$ , all other switches remain on/off in one half-cycle. The total switching loss is reduced, which will be examined through simulations, together with conduction losses analyzed as follows.

## C. Conduction Losses and Diode Reverse-Recovery Loss

Average currents of devices are considered to estimate their conduction losses. In each carrier period, the current flowing through switch  $S_{11}$  is  $(I_{\rm in}+i_{\rm o})$  in the inductor-discharge state, or  $1/2(I_{\rm in}+i_{\rm o})$  in the inductor-charge state. The average current flowing through  $S_{11}$  during the positive half-cycle is given by  $(I_{\rm in}+i_{\rm o})(1-0.5d)$ . During the negative half-cycle, the average current of  $S_{11}$  can then be estimated as  $0.5(I_{\rm in}+i_{\rm o})d$ . Therefore, the conduction loss of  $S_{11}$  is calculated by

$$P_{\text{con,s11}} = \frac{f_{l}R_{on}}{2} \left[ \int_{0}^{0.5/f_{l}} \left( 1 - \frac{1}{2}d \right)^{2} \left( I_{in} + i_{o}(t) \right)^{2} dt + \int_{0.5/f_{l}}^{1/f_{l}} \frac{1}{4}d^{2} (I_{in} + i_{o}(t))^{2} dt \right]$$

(24)

where  $R_{\rm on}$  is the on-state resistance of the switch.

The same conduction-loss analysis can be applied to other switches, whose details are not repeated here.

Similarly, the conduction loss of the inductor caused by the parasitic resistance  $r_L$  can be calculated according to

$$P_{\text{Lin}} = I_{\text{Lin}}^2 r_{\text{L}} = I_{\text{in}}^2 r_{\text{L}} \tag{25}$$

Capacitors are assumed to have the same conduction loss since they experience a similar charge/discharge current. Taking the capacitor  $C_1$  as an example, its conduction loss during the positive half-cycle when it is charged is expressed as

$$P_{\text{C1\_phc}} = \left[\frac{1}{2}I_{\text{in}}(1-d)\right]^2 r_{\text{Lin}} = \frac{1}{4}I_{\text{in}}^2 (1-d)^2 r_{\text{C}}$$

(26)

where  $r_{\rm C}$  is equivalent-series-resistance (esr) of the capacitor. During the negative half-cycle, the capacitor  $C_1$  discharges to the output. Using Eq. (9), and assuming  $Q_{\rm C1} = Q_{\rm C2}$ , the average current of the capacitor  $C_1$  during the negative half-cycle is

$$I_{C1} = 2Q_{C1}f_{l} (27)$$

based on which, the conduction losses of the capacitor  $C_1$  during the negative half-cycle is calculated by

$$P_{\text{C1\_nhc}} = [2Q_{c1}f_l]^2 r_{\text{Lin}} = 4Q_{c1}^2 f_l^2 r_{\text{C}}$$

(28)

The total conduction loss of the capacitor  $C_1$  is summarized as

$$P_{\rm C1} = 1/2(P_{\rm C1~phc} + P_{\rm C1~nhc}) \tag{29}$$

The diodes  $D_1$  and  $D_3$  (or  $D_2$  and  $D_4$ ) are turned on to conduct the inductor-discharge current during one of the half-cycles. Assuming that the forward voltage of a diode is  $V_{\rm Fd}$ , the conduction loss is expressed as

$$P_{\rm D} = \frac{1}{2} \left[ \frac{1}{2} I_{\rm in} (1 - d) \right] V_{\rm Fd}$$

(30)

Additionally, the reverse-recovery current of the diode induces additional power loss which can be calculated by

$$P_{\rm drr} = \frac{1}{2} V_{\rm d} Q_{\rm rr} f_{\rm s} \tag{31}$$

where  $V_{\rm d}$  is the peak-inverse voltage and  $Q_{\rm rr}$  the reverse-recovery charge of the diode.

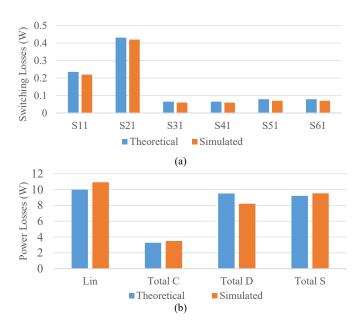

To verify the effectiveness of the theoretical calculations, power losses of different kinds of components are simulated through *PLECS*. During the simulation, parameters obtained from the datasheets of devices are considered, while the parasitic resistances of the reactive components are 0.1  $\Omega$ . Simulation results of switching losses are shown in Fig. 8(a), which indicates that theoretical losses are close to the simulations. The total switching loss (12 switches) is very low at 3.82 W. This is because only a few switches operate at the carrier frequency (10 kHz) concurrently (see Fig. 6). Similarly, power losses of different components are shown in Fig. 8(b), where the similarity between the calculated and simulated values is seen. The conduction loss of  $L_{\rm in}$  is relatively large since for the boost CMI, its  $I_{\rm in}$  is several times larger than the rms output current.

Fig. 8. Theoretical and simulated (a) switching losses and (b) power losses of different kinds of components under 1 kW ( $r_C = r_L = 0.1\Omega$ ; considering switches *IRF300P227* and diodes *DPG60I300HA*).

### D. Common-Mode Voltage

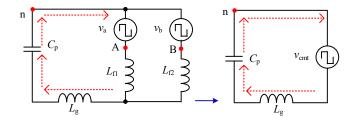

The common-mode model of the proposed  $2\phi$  seven-level inverter is shown in Fig. 9, considering the parasitic capacitance  $(C_p)$  that is connected between the negative terminal (point n) of the dc source and the ac neutral of the transformerless PV gridtied system. The ground stray inductance is notated as  $L_g$ . Accordingly, the common-mode voltage  $(v_{cm})$  is written as

$$v_{cm} = \frac{1}{2}(v_A + v_B) \tag{32}$$

where  $v_A$  ( $v_B$ ) is the voltage of the output terminal A (B) with respect to the negative terminal of the dc source.

Both the common-mode and differential-mode voltages contribute to the total excitation voltage ( $v_{cmt}$ ) of  $C_p$  and  $L_g$ , expressed as [27]

$$v_{cmt} = \frac{1}{2} (v_A + v_B) + \frac{1}{2} (v_A - v_B) \frac{L_{f2} - L_{f1}}{(L_{f1} + L_{f2})}$$

(33)

where  $L_{f1}$  and  $L_{f2}$  are line inductors of the two phases, respectively.

Assuming that the two inductances are close to each other, which usually is the case, the total excitation voltage can then be simplified as

$$v_{cmt} = v_{cm} = \frac{1}{2}(v_A + v_B)$$

(34)

Fig. 10 depicts the total common-mode voltage under each voltage level. The maximum value is  $v_{\rm cmt,max} = V_{\rm C}$ , lower than the maximum output voltage (3 $V_{\rm C}$ ). The suppression of the ground leakage current of CMIs for transformerless grid-tied applications is discussed in [27], where passive common-mode filters are mentioned. Details are however not included in this paper. Instead, the simulated leakage current is given and discussed in Section V considering the common-mode filters

Fig. 9. Common-mode model of the  $2\phi$  seven-level inverter ( $v_{cmt}$  is the total excitation voltage of  $C_p$  and  $L_g$ ).

Fig. 10. The total common-mode voltage ( $v_{cmt}$ ) with respect to  $v_{AB}$  under the LS PWM scheme.

[27]. Before proceeding with it, a comparative study of the proposed CMI is presented next.

### IV. INVERTER COMPARISON AND DESIGN CONSIDERATIONS

### A. Qualitative Comparison among the MLIs

A qualitative comparison among the conventional MLIs, prior-art CMIs, and the proposed CMI is illustrated in Table I. As seen, to produce the same number of voltage levels of (2n+1), the proposed CMI uses the same numbers of switches and gate drivers as those of the conventional CHB inverter. However, the proposed CMI uses a single dc source compared to the conventional CHB inverter, which requires multiple isolated dc sources. For PV applications where the isolated dc sources are no longer a major challenge, the conventional CHB inverter may use the smallest number of power devices [11].

Additionally, for low voltage-level applications, the proposed CMI can also be configured with fewer SMs. The numbers of the components used are thus at a similar level with those of the conventional NPC or FC inverter. The NPC/FC inverter may have difficulty in balancing the voltages of the dc-link or flying capacitors. Unlike the conventional multilevel inverters, however, the reverse-power flow is not allowed for the proposed CMI. Similarly, the reverse-power flow is not supported by the prior-art CMIs presented in [20] and [23]. The SC technique is used in [19], [20], and the proposed 1\phi CMI shown in Fig. 3(c). Their devices are thus burdened by the inrush currents of capacitors. They may be less suitable for higher voltage/power applications [24], [25]. Differently, for the CMI in [23] and the proposed 2\phi CMI shown in Fig. 3(d), the floating capacitors are charged by an inductive input current, and therefore free of the inrush currents.

The total capacitances of the compared MLIs are also given in Table I. As can be seen, for CMIs in [19], [20], and [23], large capacitances are used. Its total installed energy (total E) is thus

$\label{table I} Table\ I$  Comparison with Available MLIs Producing A (2n+1)-Level Voltage

| MLIs                  | The number of  |                      |        |       |                 | Total C(mF)<br>/Volt.               | Total E<br>J/kW | $V_{\mathrm{C}}$  | Contin-<br>uous   |          | Reverse power? | Remarks                                                                            |  |

|-----------------------|----------------|----------------------|--------|-------|-----------------|-------------------------------------|-----------------|-------------------|-------------------|----------|----------------|------------------------------------------------------------------------------------|--|

|                       | $N_S / N_{dr}$ | $I_{dr}$ $N_D$ $N_C$ |        | $N_L$ | N <sub>dc</sub> |                                     | J/K VV          |                   | I <sub>in</sub> ? | current: | power:         |                                                                                    |  |

| CMI [19]<br>Fig. 2(a) | 5n-1           | 0                    | n-1    | 0     | 1               | 3.3/100 V                           | N.I.            | $V_{in}$          | No                | Yes      | Yes            | SM using 5 switches,<br>SC voltage balancing                                       |  |

| CMI [20]<br>Fig. 2(b) | 5n-1           | n-1                  | n-1    | 0     | 1               | 4×4.7/100 V                         | 88.13           | $V_{\text{in}}$   | No                | Yes      | No             | SM using 5 switches and a diode,<br>SC voltage balancing                           |  |

| CMI [23]<br>Fig. 2(c) | 4n+1           | n                    | n      | 1     | 1               | 4×4.6/80 V                          | 58.88           | > V <sub>in</sub> | No                | No       | No             | Capacitor charged by input inductor, requiring high-voltage diodes                 |  |

| СНВ                   | 4n             | 0                    | 0      | 0     | n               | /                                   | /               | Vin               | No                | No       | Yes            | Series-connected two-level inverters,<br>multiple isolated and balanced dc sources |  |

| 1φ CMI<br>Fig. 3(c)   | 4n             | 2n-1                 | 2n-1   | 1     | 1               | 5×0.47/200 V                        | 47              | > V <sub>in</sub> | Yes               | Yes      | No             | SM using 4 switches and 2 diodes,<br>SC voltage balancing                          |  |

| 2φ CMI<br>Fig. 3(d)   | 4n             | 2(n-1)               | 2(n-1) | 1     | 1               | 4×0.47/200 V<br>or<br>4×0.25/2000 V | 37.6 or 20*     | > V <sub>in</sub> | Yes               | No       | No             | SM using 4 switches and 2 diodes, requiring high-voltage diodes (2 > 1)            |  |

| NPC                   | 4n             | 2n                   | 2n     | 0     | 1               | /                                   | /               | /                 | Yes               | No       | Yes            | Unbalanced dc-link voltage and requiring high-voltage diodes (n > 1)               |  |

| FC                    | 4n             | 0                    | 2n     | 0     | 1               | 2×10/1100 V                         | 18.15**         | /                 | Yes               | No       | Yes            | Non-uniform capacitors voltages require series-connected capacitors                |  |

Notes: "N.I." means no information; "/" not applicable; "\*" simulation value; "\*\*" excluding the dc-link capacitors [28].

higher. Similarly, the total *E* of the proposed CMI is relatively high compared to the conventional FC MLI [28]. Smaller capacitances can be used to reduce the total E if a lesser stringent voltage-ripple requirement is met.

### B. Discussions on Voltage- or Power-Level Extension

The proposed single-source CMI can be extended for higher voltage-level operations with proper design and selection of the semiconductor devices. Since the maximum current ( $I_{inmax} + i_{omax}$ ) arises in SM<sub>1</sub>, it is feasible to apply the switches in SM<sub>1</sub> to other SMs for generating higher voltage levels. Switches in the rear-end SMs are however over-designed. Such a characteristic of the proposed CMI however does not render it less superior compared to the counterparts including the prior-art single-source CMIs [19], [20], and [23]. One common feature of these CMIs is that different currents/voltages are induced on switches in different SMs which share the same circuit structure. Therefore, different current-rating switches may be required to optimize the overall circuit for these CMIs.

In terms of a high-quality waveform, the feasibility of the proposed CMI for higher voltage-level extensions is thus not limited. Higher voltage-level (7, 9, 11, ...) operations require higher voltage-rating diodes, which can be implemented by series-connected diodes similar to the conventional NPC MLI. As for power-level extension, however, unlike the multi-source CMIs whose total output power can be increased by increasing the number of SMs and their associated dc sources while maintaining the same voltage and current stresses, one limitation of the proposed single-source CMI is the operating power must be confined to the input power. It means scaling up the number of SMs does not necessarily enlarge the output power level. Raising the single input power necessitates an increase in the voltage or current rating of the devices. It is therefore imprudent to raise the output power by increasing the number of SMs indefinitely. Thus, the capability of the powerlevel extension of the proposed single-source CMI is indeed limited.

It is worth mentioning that for PV applications since the operating power of the inverter is confined to the maximum

power point, it is reasonable to use and design a few SMs to achieve a boosted and regulated output voltage. Moreover, like any of the CMIs, the cascaded feature of the proposed CMI somewhat reduces the maintenance effort.

### C. Component Design Consideration

Selections of the switches and diodes can be attained according to their voltage/current ratings. For the capacitors, their capacitances are designed according to the voltage-ripple requirements as mentioned in Section II.C. The design considerations of the input inductor are detailed below.

The boost inductor should ensure that it operates in the continuous conduction mode (CCM). In practice, the inductor current is coupled with high-frequency and low-frequency ripples. The high-frequency ripple during each carrier period is expressed as

$$\Delta I_{\rm HF} = \frac{V_{\rm in}d}{2L_{\rm in}f_c} \tag{35}$$

Assuming a constant shoot-through duty ratio is used in the LS PWM scheme, the voltage across  $L_{\rm in}$ , when it is charged, is  $V_{\rm in}$ . When it is discharged in series with the dc source to any of the capacitors ( $C_1$  to  $C_4$ ), the voltage across it ( $v_L$ ) is coupled with a second-order harmonic. The low-frequency current ripple of the inductor is expressed as

$$\Delta i_L = \frac{1}{2L_{in}} \int_0^{1/(4f_l)} v_L \, dt \approx \frac{1}{2L_{in}} \frac{1}{2} \left( \frac{\Delta V_c}{2} \frac{1}{4f_l} \right) = \frac{\Delta V_c}{32L_{in}f_l}$$

(36)

Using Eqs. (35) and (36), the total current ripple of the input inductor is thus calculated with

$$\Delta I_{L,t} = \Delta I_{\text{Lin}} + \Delta i_{\text{L}} = \frac{V_{\text{in}}d}{2L_{\text{in}}f_{\text{S}}} + \frac{\Delta V_{c}}{32L_{\text{in}}f_{\text{I}}}$$

(37)

Assuming that the current-ripple requirement of  $L_{\rm in}$  is  $\Delta I_{\rm L,t} < \alpha I_{\rm in}$ , the inductor is designed according to

$$L_{in} > \frac{1}{\alpha I_{in}} \left( \frac{V_{in}d}{2f_s} + \frac{\Delta V_c}{32f_l} \right)$$

(38)

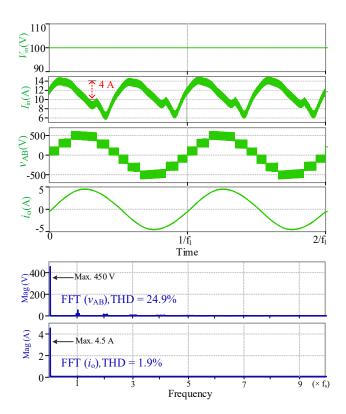

Fig. 11. Simulation results of  $2\phi$  seven-level inverters including input and output voltages ( $V_{\rm in}$ ,  $v_{\rm AB}$ ) and currents ( $I_{\rm in}$ ,  $i_{\rm o}$ ); FFT of  $v_{\rm AB}$  and  $i_{\rm o}$ , and their THD values considering high-frequency harmonics (up to  $10f_{\rm s}$ ).

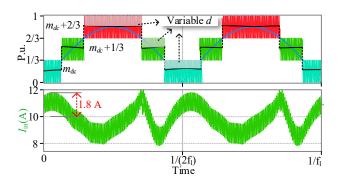

Fig. 12. Reduced input current ripple ( $\Delta I_{in}$ ) by a variable shoot-through duty ratio  $m_{dc}$ .

### V. SIMULATION AND EXPERIMENTAL RESULTS

# A. Simulation Results

The steady-state simulation results of the  $2\phi$  seven-level inverter are shown in Fig. 11. The inverter is fed by a constant dc source, while its ac output supplies an RL load ( $R=100~\Omega$ , L=50~mH) with the nominal output power of 1 kW ( $f_1=50~Hz$ ). It is seen that a boosted voltage with the peak value of 600~V is achieved from the 100-V input voltage. The THDs of output voltage and current are investigated through the fast Fourier transform (FFT). The THD of the seven-level output voltage is 24.9%, while the THD of the output current is very low at 1.9% due to the filtering effect of the loading inductance. It is seen that the instantaneous input current of the inverter is coupled with a relatively larger ripple of 4 A due to the single-phase

Fig. 13. Simulated voltages and currents of the capacitors  $C_1$  to  $C_4$ .

pulsating output power which fluctuates at the double-line frequency. To reduce the low-frequency current ripple, a modified  $M_{\rm dc}$  is considered for generating a variable shoot-through duty ratio as shown in Fig. 12, where  $m_{\rm dc} = 0.16 - 0.01(1-\cos(4\pi {\rm fit}))$  is used. The ripple current is then reduced to 1.8 A. In addition, power decoupling techniques using additional active or reactive components or control strategies can also be considered to remove the low-frequency input current ripple of a single-phase inverter [26], [29], which being general, is not shown here.

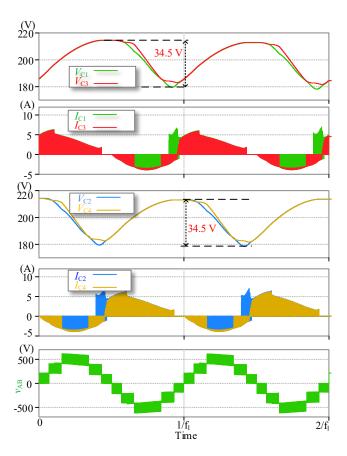

The voltages and currents of capacitors  $C_1$  to  $C_4$  are shown in Fig. 13. Under the nominal operating power, the voltage ripples of four capacitors are kept at a similar level at 17.25 V, which is close to the theoretical calculations presented in Fig. 7. It is evident that capacitors  $C_1$  and  $C_3$  are charged during the positive half-cycle while  $C_2$  and  $C_4$  are charged during the negative half-cycle, which confirms again the theoretical analysis presented in Section II.C. The voltage ripples of capacitors  $C_3$  and  $C_4$  are equal, slightly less than those of  $C_1$  and  $C_2$ . The voltages across all capacitors are balanced automatically at the same average value around 200 V. Furthermore, the average/maximum currents of capacitors are close, simplifying the designs and selection of capacitors.

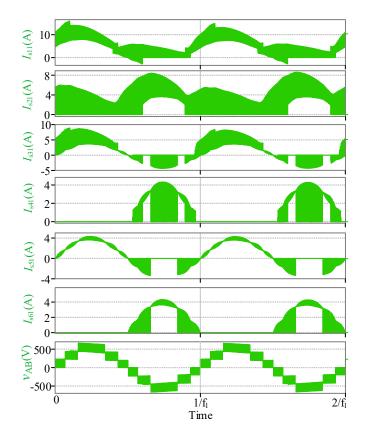

Nevertheless, the current stresses of switches are indeed different as shown in Fig. 14. The maximum and rms values of currents are summarized in Table II. As seen, the maximum current of switches in  $SM_1$  is 15.9 A. As expected, the rms currents of switches are not the same either. The switch  $S_{11}$  is loaded by the maximum rms current at 6.3 A, while the rms

Fig. 14. Simulated currents of switches  $S_{11}$  to  $S_{61}$  of phase A.

| TABLE II                                            |                   |                   |                   |                   |                   |                   |

|-----------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| MAXIMUM AND RMS CURRENTS UNDER NOMINAL OUTPUT POWER |                   |                   |                   |                   |                   |                   |

| Switches                                            | $S_{11} / S_{12}$ | $S_{21} / S_{22}$ | $S_{31} / S_{32}$ | $S_{41} / S_{42}$ | $S_{51} / S_{52}$ | $S_{61} / S_{62}$ |

| Max. (A)                                            | 15.9              | 8.6               | 8.9               | 4.3               | 4.3               | 4.3               |

| RMS (A)                                             | 6.3               | 4.1               | 3.5               | 1.8               | 2.2               | 1.8               |

Fig. 15. Simulated common-mode voltage ( $v_{cmt}$ ) and the leakage current ( $i_{Lk}$ ) under the operating power of 1 kW.

currents of switches  $S_{21}$  and  $S_{31}$  are 4.1 A and 3.5 A, respectively. The remaining three switches are loaded with a similar current of around 2 A. Another observation made is that although the maximum current of switches is larger than the average of the input current (10 A), its rms value is smaller.

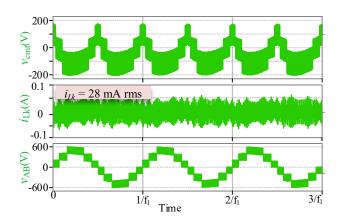

To examine the feasibility of the proposed CMI for transformerless grid applications, a small capacitor (50 nF) is

| Table III                                    |                                                                                              |  |  |  |  |

|----------------------------------------------|----------------------------------------------------------------------------------------------|--|--|--|--|

| SPECIFICATIONS OF THE EXPERIMENTAL PROTOTYPE |                                                                                              |  |  |  |  |

| Voltage ratings                              | $V_{\rm in}$ = 100 V, Max. $v_{\rm AB}$ = 600 V, 50 Hz, 1 kW                                 |  |  |  |  |

| Switches                                     | IRF300P227 (300 V, 50A, $R_{on} = 0.04\Omega$ )                                              |  |  |  |  |

| Diodes                                       | $D_1/D_2$ : DPG60I300HA (300 V, 60A, $V_{\text{Fd}}$ = 1.4 V)<br>$D_3/D_4$ : DPG60I300HA × 2 |  |  |  |  |

| Capacitors                                   | $C_1$ to $C_4$ 0.47 mF each                                                                  |  |  |  |  |

| Inductors                                    | Input $L_{in} = 3$ mH; filter $L_f = 2$ mH;                                                  |  |  |  |  |

| DW/M voriables                               | $M = 0.9 \cdot M_{\odot} = 0.16 \cdot f = 10 \text{ kHz}$                                    |  |  |  |  |

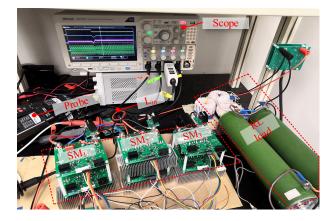

Fig. 16. Photographs of the experimental prototype.

used to simulate  $C_p$  (see Fig. 9). It is connected between the ac neutral and the negative terminal of the dc source with a nominal power of 1 kW. The stray inductance of the ground is assumed to be 1 uH. Additionally, the total common-mode filter used at the input and output is 20 mH [27]. Simulation results are shown in Fig. 15. As seen, the common-mode voltage matches well with the analysis in Section III.D. The leakage current is not zero, but at a low level with the peak value of 58 mA and rms value of 28 mA, which is compatible with the grid codes [27]. It is, therefore, able to apply the proposed CMI to transformerless grid application, especially considering its stepup feature which is further tested through experiment.

# B. Experimental Results

To verify the feasibility of the proposed CMI, two downscale experimental prototypes ( $1\phi$  and  $2\phi$ ) are built and tested. Results obtained from the  $2\phi$  seven-level inverter are shown here in comparison with the simulations. The components used in the experiment are listed in Table III. A constant dc source ( $V_{\rm in}$  =  $100~\rm V$ ) is used as the input of the inverter, while an RL load (R =  $100~\rm \Omega$ , L =  $50~\rm mH$ , see Fig. 16) is connected to the output through a filter inductor  $L_{\rm f}$  (2 mH). The inductor-charge duty ratio for the  $2\phi$  seven-level prototype is d = 0.52 ( $M_{\rm dc}$  = 0.16). Additionally, its ac modulation ratio used is  $M_{ac}$  = 0.8. The carrier frequency of the LS PWM scheme is  $10~\rm kHz$ . Steady-state experimental results are shown in Figs. 17-19. Experimental data are also captured and can be rebuilt using Matlab to increase the readability.

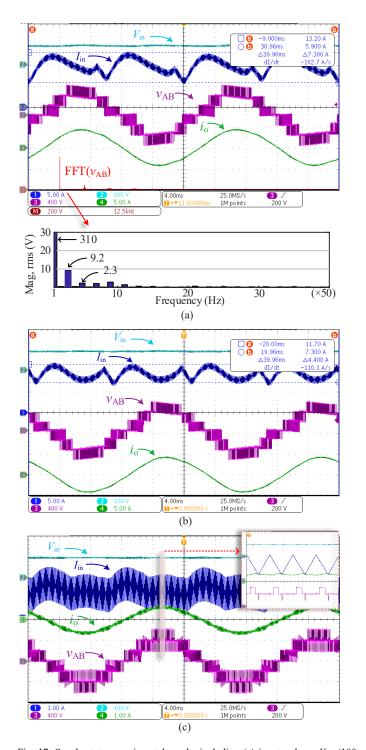

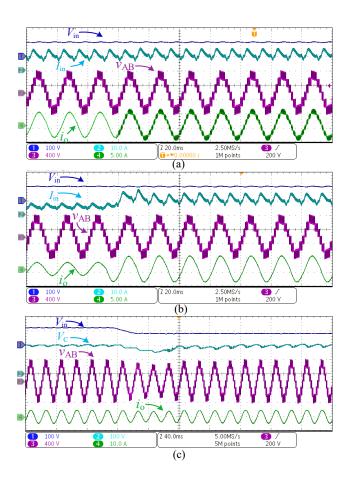

The key input and output waveforms are shown in Fig. 17(a), where the output voltage feature seven discrete voltage levels with the maximum value of  $|\pm 600|$  V obtained from the 100-V dc source. The harmonic contents (up to  $40^{th}$  order) of the output voltages are tested with the maximum value of the third-order harmonic at 9.18 V rms. Furthermore, due to the filtering effect

Fig. 17. Steady-state experimental results including (a) input voltage  $V_{\rm in}$  (100 V/div), input current  $I_{\rm in}$  (5 A/div), output voltage  $v_{\rm AB}$  (400 /div), and output current  $i_{\rm o}$  (5A /div), FFT test of the output voltage, low-order harmonics (up to 40<sup>th</sup> order) measured by the scope; (b) key waveforms with reduced input current ripple; (c) waveforms under light load condition (100 W).

of the loading inductance, the tested THD of the output current is very low at 1.74%. The input current couples a low-order ripple, which can be reduced by using a modified PWM signal  $m_{\rm dc}$  that produces a variable shoot-through duty ratio as shown in Fig. 17(b). The results obtained match well with the simulations shown in Fig. 12.

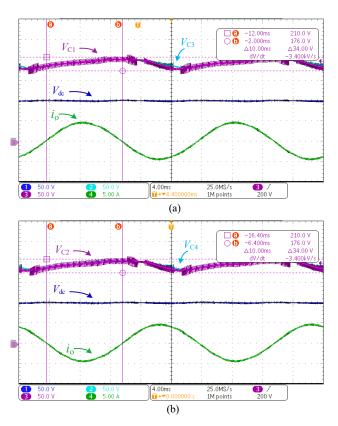

Fig. 18. Steady-state (a) capacitors' voltages  $V_{\rm Cl}$  (50 V/div),  $V_{\rm C3}$  (50 V/div) input voltage  $V_{\rm in}$  (50 V/div) and output current  $i_{\rm o}$  (5 A/div), and (b) capacitors' voltages  $V_{\rm C2}$  (50 V/div),  $V_{\rm C4}$  (50 V/div) input voltage  $V_{\rm in}$  (50 V/div) and output current  $i_{\rm o}$  (5 A/div).

The voltage and current waveforms are also measured under the light load condition (100 W) as shown in Fig. 17(c). It is observed that when the inductor discharges and  $I_{\rm in} = i_{\rm o}$  is met, the output voltage drops, which agrees with the analysis described in Section II.A. Such durations are relatively small since  $L_{\rm in}$  is charged and its current increases subsequently. The output sinusoidal current is not distorted under such a condition and the THD of the output current measured is 3.9%.

The voltages of capacitors are measured and shown in Fig. 18. It is seen that their voltages are balanced at the same average value. While capacitors  $C_1$  and  $C_3$  are charged during the positive half-cycle,  $C_2$  and  $C_4$  are charged during the negative half-cycle as shown in Fig. 18(b). Nevertheless, their voltage ripples are maintained at a similar level at about 17 V under the nominal output power. These results therefore match with the simulations, confirming again the theoretical analysis. Furthermore, since all the capacitors are charged directly by the input current, the currents flowing through them are relatively smooth, which is evaluated by testing the switch currents.

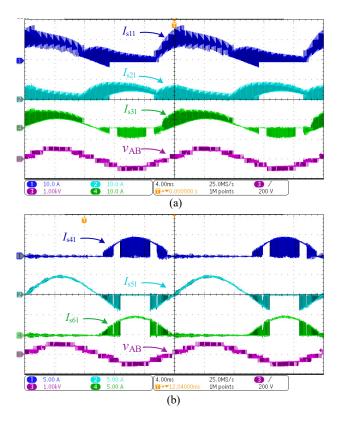

To illustrate, the current waveforms of switches in phase A are measured and shown in Fig. 19. The switches in the rear-end side (e.g.,  $S_{51}$  to  $S_{61}$ ) conduct only the ac output current, whose peak currents, and thus the rms currents are smaller as shown in Fig. 19 (b). Other switches (e.g.,  $S_{11}$  and  $S_{21}$ ) need to conduct capacitor-charging currents and the output current, and therefore, their current ratings are relatively large, as shown in Fig. 19(a). Nonetheless, the conducting currents of switches are in accordance with their simulation results shown in Fig. 14.

Fig. 19. Steady-state (a) switches currents  $I_{s11}$  (10 A/div),  $I_{s21}$  (10 A/div) and  $I_{s31}$  (10 A/div) and (b)  $I_{s41}$  (5 A/div),  $I_{s51}$  (5 A/div) and  $I_{s61}$  (5 A/div); output voltage  $v_{AB}$  (1 kV/div) is used as common reference in both captures.

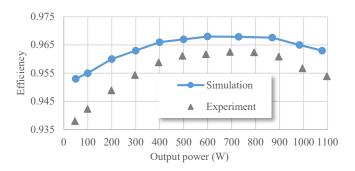

Fig. 20. Experimentally measured efficiency under different power levels ( $V_{\rm in}$  = 100 V,  $V_{\rm omax}$  = 600 V) in comparison with the simulated values.

The maximum switch current arises in SM<sub>1</sub> ( $I_{in} + i_{omax}$ ), agreeing with the theoretical analysis.

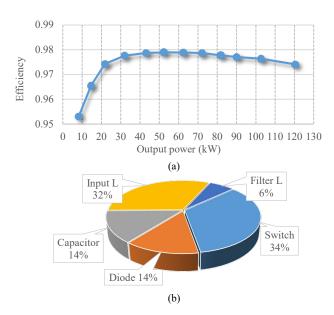

The steady-state efficiency versus output power is measured and shown in Fig. 20. During the experimental tests, the digital power analyzer WT333E is used for measuring the input and output power concurrently. By varying the loading resistance R, different sets of data corresponding to different input  $(P_{\rm in})$  and output  $(P_{\rm o})$  powers are tested and the efficiency is calculated with  $\eta = P_{\rm o}/P_{\rm in}$ . As seen from Fig. 20, the measured efficiency is close to the simulated value (differences mostly within 0.5%). It increases steadily as the operating power rises at lower power levels. The maximum efficiency achieved is 96.3% at  $P_{\rm o} = 690$  W. After reaching the maximum value, the efficiency curve begins to fall. Nonetheless, under a wide range of output power,

Fig. 21. Dynamic responses of the  $2\phi$  prototype under (a) a transient from an inductive load to a resistive load, (b) from half-load to full-load, and (c) a stepchange of  $V_{\rm in}$  from 120 V to 80 V.

the obtained data is well above 95%, demonstrating a high-efficiency dc-ac voltage-boost power conversion.

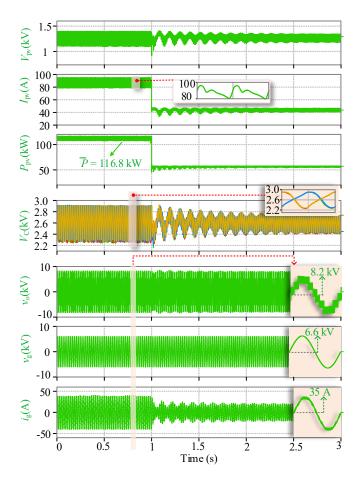

For verifying the stable operation of the proposed CMI under different loading conditions, the dynamic results of the prototype are tested and detailed in Fig. 21. Fig. 21(a) and (b) show the transient results of the inverter from an inductive load to a resistive load and from half-load to full-load condition. During these transients, the inverter operates properly. Furthermore, to illustrate the voltage regulation of the proposed CMI, the voltage of each series-connected SM and the total output voltage are sensed and a voltage closed-loop control is used to regulate the voltages of the capacitors. A sudden change in the input voltage from 120 V to 80 V is applied, which causes an under-shoot voltage across capacitors. Correspondingly, the output voltage sags during the transient before it returns to its nominal value within several cycles (Fig. 21(c)). Regulation of the ac voltage is achieved, and the proposed CMI can, therefore, operate with a varied dc source while at the same time providing a regulated output voltage.

Overall, the downscale experimental tests confirm the theoretical analysis and demonstrate the advantages of the proposed single-source CMI. Due to the constraint of the prototypes, higher voltage operations of the proposed CMI are not experimentally tested. Instead, a scale-up (voltage and current 10 times scaled up) PV power generation is simulated and discussed in the following.

Fig. 22. Simulation results of the MV PV power generation including PV voltage  $V_{\rm pv}$  and power  $P_{\rm pv}$ , SM capacitor voltage  $V_{\rm c}$ , output voltage  $v_{\rm e}$ , grid voltage  $v_{\rm g}$ , and current  $i_{\rm g}$  under a step-change of the PV irradiance.

### C. Simulation of A Scale-up PV Power Generation

A PV power generation system based on a  $2\phi$  seven-level inverter is studied through MATLAB/PLECS co-simulation environment. The PV source is realized by series and parallel connections of PV modules JKM360M-72-V. The maximum-power-point (MPP) PV voltage is at about 1.3 kV. A 0.25-mF capacitor is considered for each capacitor (15% ripple requirement), while the input and output line inductors are assumed to be 5 mH. The parasitic resistance of each reactive component is assumed to be 0.1  $\Omega$  for loss estimation. Note that since galvanic isolation is usually required in the point of coupling for interfacing with MV grid, the parasitic capacitance and leakage current issues in transformerless PV systems are not considered in the MV simulation.

Under the steady-state operation, the steady-state average voltages across capacitors are boosted to be about 2.6 kV. As a consequence, a step-up seven-level output voltage is produced and the amplitude of the fundamental component of the total output voltage is boosted at 6.6 kV. The peak-to-peak value of the PV current simulated is 14 A (average  $I_{pv}$  86 A), which means the PV current ripple is less than 10% of its average current. The average output power of the PV source ( $\bar{P}_{pv}$ ) is 116.8 kW out of its maximum power of 117.5 kW. The simulated maximum-power-point-tracking (MPPT) efficiency is thus 99.4%. A step-change in the PV irradiation is applied

Fig. 23. Simulated (a) efficiency of the scale-up  $2\phi$  inverter for MV PV applications ( $V_0 = 6.6 \text{ kV}$ ) and (b) the total loss (2488.1 W) breakdown under output power 100 kW.

which causes the output voltage/power of the PV source to reduce as shown in Fig. 22. During the transient, the output voltage ( $v_{AB}$ ) keeps steady, while the current injected to the grid ( $i_g$ ) reduces in accordance with the variation of the input PV power, thereby, maintaining MPPT.

The power losses and efficiency of the proposed CMI are simulated considering the semiconductor power module SKM450GB33F (including IGBT and diode) operating under a 2-kHz switching frequency. Its specific loss data are used to evaluate the losses of the switches and diodes. The simulated efficiency under different operating power is depicted in Fig. 23(a), where it can be seen that the efficiency across a wide range of operating power is larger than 97%. The total loss breakdown of the inverter under the rated power of 100 kW is also given in Fig. 23(b). The semiconductor switches cause the largest power loss, taking up 34% of the total loss. The input inductor consumes the second largest proportion of power since for a boost converter/inverter the input current (≈100 A) is several times larger than the output current. Nonetheless, with its boosted output voltage, the proposed CMI, therefore, provides a promising solution for a single-stage MV PV power generation using a single dc source.

### VI. CONCLUSION

A novel CMI fed by a single dc source is proposed, which reduces the requirement of dc sources for boost dc-ac multilevel voltage synthesis. The proposed inverter is conditioned by an input inductor that operates with shoot-through charging and discharges with a boosted voltage to the SMs. The capacitors in each SM are smoothly charged by the inductive input current. A 2\$\phi\$ symmetrical structure is presented and assisted by the LS PWM scheme to keep voltages of capacitors balanced in addition to producing a suitable inductive-charge duty ratio and voltage gain. The voltage and current ratings of the devices are analyzed, which shows that the proposed CMI is able to be extended for higher voltage-level operations using the same

circuit structure but with different current-rating switches and additional diodes. Furthermore, a qualitative comparison with the prior-art CMIs is given to illustrate the advantages of the proposed CMI. Simulations and experimental results obtained from downscale inverter prototypes have demonstrated the characteristics of the proposed CMI. In addition, the feasibility of the proposed CMI for MV applications has been tested through simulation of a single-source PV inverter producing a boosted ac voltage for interfacing with the MV grid.

### ACKNOWLEDGMENT

Manxin Chen acknowledges the financial support from The Chinese University of Hong Kong, under the postgraduate studentship PGS3131023. Xiong Liu's work was supported in part by Micro Electronics R&D center of Shenzhen Topband Co., Ltd under Grant No. 40121065.

### REFERENCES

- [1] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Pérez, "A Survey on Cascaded Multilevel Inverters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2197-2206, Jul. 2010.

- [2] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," *IEEE Trans. Ind. Appl.*, vol. IA-17, no. 5, pp. 518–523, Sep./Oct. 1981.

- [3] T. A. Meynard, H. Foch, P. Thomas, J. Courault, R. Jakob, and M. Nahrstaedt, "Multicell converters: Basic concepts and industry applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 5, pp. 955-964, Oct. 2002.

- [4] D. A. Rendusara, E. Cengelci, P. N. Enjeti, V. R. Stefanovic, and J. W. Gray, "Analysis of common mode voltage-'neutral shift' in medium voltage PWM adjustable speed drive (MV-ASD) systems," *IEEE Trans. Power Electron.*, vol. 15, no. 6, pp. 1124-1133, Nov. 2000.

- [5] T. H. Nguyen, K. A. Hosani, M. S. E. Moursi, and F. Blaabjerg, "An Overview of Modular Multilevel Converters in HVDC Transmission Systems with STATCOM Operation During Pole-to-Pole DC Short Circuits," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4137-4160, May 2019.

- [6] S. Alepuz, S. Busquets-Monge, J. Bordonau, J. Gago, D. Gonzalez, and J. Balcells, "Interfacing Renewable Energy Sources to the Utility Grid Using a Three-Level Inverter," *IEEE Trans. Ind. Electron.*, vol. 53, no. 5, pp. 1504-1511, Oct. 2006.

- [7] R. Teodorescu, F. Blaabjerg, J. K. Pedersen, E. Cengelci, and P. N. Enjeti, "Multilevel inverter by cascading industrial VSI," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 832-838, Aug. 2002.

- [8] K S. Kouro, S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, and et al., "Recent Advances and Industrial Applications of Multilevel Converters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2553-2580, Aug. 2010.

- [9] K. Gupta, A. Ranjan, P. Bhatnagar, L. K. Sahu, and S. Jain, "Multilevel Inverter Topologies with Reduced Device Count: A Review," *IEEE Trans. Power Electron.*, vol. 31, no. 1, pp. 135-151, Jan. 2016.

- [10] M. Vijeh, M. Rezanejad, E. Samadaei, and K. Bertilsson, "A General Review of Multilevel Inverters Based on Main Submodules: Structural Point of View," *IEEE Trans. Power Electron.*, vol. 34, no. 10, pp. 9479-9502, Oct. 2019.

- [11] L. Zhang, K. Sun, Y. W. Li, X. Lu, and J. Zhao, "A Distributed Power Control of Series-Connected Module-Integrated Inverters for PV Grid-Tied Applications," *IEEE Trans. Power Electron.*, vol. 33, no. 9, pp. 7698-7707, Sept. 2018.

- [12] H. Choi, M. Ciobotaru, M. Jang, and V. G. Agelidis, "Performance of Medium-Voltage DC-Bus PV System Architecture Utilizing High-Gain DC-DC Converter," *IEEE Trans. Sustain. Energy*, vol. 6, no. 2, pp. 464-473, April 2015.

- [13] Z. Du, B. Ozpineci, L. M. Tolbert, and J. N. Chiasson, "DC-AC Cascaded H-Bridge Multilevel Boost Inverter with No Inductors for Electric/Hybrid Electric Vehicle Applications," *IEEE Trans. Ind. Appl.*, vol. 45, no. 3, pp. 963-970, May/Jun. 2009.

- [14] Z. Du, L. M. Tolbert, B. Ozpineci, and J. N. Chiasson, "Fundamental Frequency Switching Strategies of a Seven-Level Hybrid Cascaded H-

- Bridge Multilevel Inverter," *IEEE Trans. Power Electron.*, vol. 24, no. 1, pp. 25-33, Jan. 2009.

- [15] R. Vasu, S. K. Chattopadhyay, and C. Chakraborty, "Asymmetric Cascaded H-Bridge Multilevel Inverter with Single DC Source per Phase," *IEEE Trans. Ind. Electron.*, vol. 67, no. 7, pp. 5398-5409, Jul. 2020.

- [16] Y. Hinago and H. Koizumi, "A Switched-Capacitor Inverter Using Series/Parallel Conversion with Inductive Load," *IEEE Trans. Power Electron.*, vol. 59, no. 2, pp. 878-887, Feb. 2012.

- [17] Y. Ye, K. W. E. Cheng, J. Liu, and K. Ding, "A Step-Up Switched-Capacitor Multilevel Inverter with Self-Voltage Balancing," *IEEE Trans. Ind. Electron.*, vol. 61, no. 12, pp. 6672-6680, Dec. 2014.

- [18] E. Babaei and S. S. Gowgani, "Hybrid Multilevel Inverter Using Switched Capacitor Units," *IEEE Trans. Ind. Electron.*, vol. 61, no. 9, pp. 4614-4621, Sept. 2014.

- [19] N. Sandeep, J. S. M. Ali, U. R. Yaragatti, and K. Vijayakumar, "A Self-Balancing Five-Level Boosting Inverter with Reduced Components," *IEEE Trans. Power Electron.*, vol. 34, no. 7, pp. 6020-6024, July 2019.

- [20] A. Taghvaie, J. Adabi, and M. Rezanejad, "A Self-Balanced Step-Up Multilevel Inverter Based on Switched-Capacitor Structure," *IEEE Trans. Power Electron.*, vol. 33, no. 1, pp. 199-209, Jan. 2018.

- [21] M. S. Manoharan, A. Ahmed, and J. Park, "A PV Power Conditioning System Using Nonregenerative Single-Sourced Trinary Asymmetric Multilevel Inverter with Hybrid Control Scheme and Reduced Leakage Current," *IEEE Trans. Power Electron.*, vol. 32, no. 10, pp. 7602-7614, Oct. 2017.

- [22] M. Lee, C.-S. Yeh, and J.-S. Lai, "A Hybrid Binary-Cascaded Multilevel Inverter with Simple Floating-Capacitor-Voltage Control," *IEEE Trans. Power Electron.*, vol. 36, no. 2, pp. 2218-2230, Feb. 2021.

- [23] H. Khoun Jahan, M. Abapour, and K. Zare, "Switched-Capacitor-Based Single-Source Cascaded H-Bridge Multilevel Inverter Featuring Boosting Ability," *IEEE Trans. Power Electron.*, vol. 34, no. 2, pp. 1113-1124, Feb. 2019

- [24] Fang Zheng Peng, "A generalized multilevel inverter topology with self voltage balancing," *Trans. Ind. Appl.*, vol. 37, no. 2, pp. 611-618, March-April 2001.

- [25] W. Peng, Q. Ni, X. Qiu, and Y. Ye, "Seven-Level Inverter with Self-Balanced Switched-Capacitor and Its Cascaded Extension," *IEEE Trans. Power Electron.*, vol. 34, no. 12, pp. 11889-11896, Dec. 2019.

- [26] H. Hu, S. Harb, N. Kutkut, I. Batarseh, and Z. J. Shen, "A Review of Power Decoupling Techniques for Microinverters with Three Different Decoupling Capacitor Locations in PV Systems," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2711-2726, June 2013.

- [27] Y. Zhou and H. Li, "Analysis and Suppression of Leakage Current in Cascaded-Multilevel-Inverter-Based PV Systems," *IEEE Trans. Power Electron.*, vol. 29, no. 10, pp. 5265-5277, Oct. 2014.

- [28] Q. A. Le and D. Lee, "A Novel Six-Level Inverter Topology for Medium-Voltage Applications," *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, pp. 7195-7203, Nov. 2016.

- [29] M. A. Vitorino, L. F. S. Alves, R. Wang, and M. B. de Rossiter Corrêa, "Low-Frequency Power Decoupling in Single-Phase Applications: A Comprehensive Overview," *IEEE Trans. Power Electron.*, vol. 32, no. 4, pp. 2892-2912, April 2017.

Manxin Chen (S'18) received his B.Sc. in Electronic Information Science and Technology, and M.Eng. in Electronic Engineering from Sun Yat-sen University, Guangzhou, China, in 2015, and 2018 respectively. He is currently working towards the Ph.D. degree in the Department of Electronic Engineering, The Chinese

University of Hong Kong, Shatin, Hong Kong SAR, China. His research focuses on power electronic converter design, PWM control, and grid-interface renewable energy applications.

Yongheng Yang (SM'17) received the B.Eng. degree in Electrical Engineering and Automation from Northwestern Polytechnical University, China, in 2009 and the Ph.D. degree in Energy Technology from Aalborg University, Denmark, in 2014. He was a postgraduate student with Southeast University, China, from 2009 to

2011. In 2013, he spent three months as a Visiting Scholar at Texas A&M University, USA. Since 2014, he has been with the Department of Energy Technology, Aalborg University, where he became a tenured Associate Professor in 2018. In January 2021, he joined Zhejiang University, China, as a ZJU100 Young Professor at the Institute of Power Electronics.

Dr. Yang was the Chair of the IEEE Denmark Section (2019-2020). He is the secretary for the Technical Committee of Sustainable Energy Systems of the IEEE Power Electronics Society (PELS). He is an Associate Editor for several IEEE Transactions/Journals and a Deputy Editor of the *IET Renewable Power Generation*. He received the 2018 *IET Renewable Power Generation* Premium Award and was an Outstanding Reviewer for the IEEE Transactions on Power Electronics in 2018. In addition, he has received two IEEE Best Paper Awards. He was the recipient of the 2021 IEEE PELS Richard M. Bass Outstanding Young Power Electronics Engineer Award. His research is to tackle the issues brought by the integration of photovoltaic systems and multi-energy vectors through developing reliable and efficient power converters with advanced control.

Xiong Liu (S'09–M'14–SM'19) received the B.E.and M.Sc. degrees from Huazhong University of Science and Technology, Wuhan, China, in 2006 and 2008, respectively, and the Ph.D. degree from Nanyang Technological University, Singapore in 2013, all in electrical engineering.

From July to November 2008, he was an Engineer with Shenzhen Nanrui Technologies Company Ltd., Shenzhen, China. From September 2011 to January 2012, he was a Visiting Scholar with the Department of Energy Technology, Aalborg University, Aalborg East, Denmark. From April 2012 to December 2013, he was a Researcher with the Energy Research Institute, Nanyang Technological University. From December 2013 to July 2020, He was working as a Principal Technologist in Rolls-Royce Electrical, Rolls-Royce Singapore Pte. Ltd.,

Singapore. He is currently an Associate Professor with the Energy Electricity Research Center, International Energy College, Jinan University, Zhuhai, China. His research interests include power electronics, motor drive, and electrical/hybrid propulsion systems for marine and aerospace.

Dr. Liu was the recipient of the Best Paper Award at the IEEE International Power Electronics and Motion Control Conference-Energy Conversion Congress and Exposition Asia in 2012.

**Poh Chiang Loh** received his B.Eng (Hons) and M.Eng from the National University of Singapore in 1998 and 2000 respectively, and his Ph.D. from Monash University, Australia, in 2002, all in electrical engineering.

He was with the defense infrastructure industry briefly, before moving to academia, where he has worked for 18

years as an Assistant Professor, a tenured Associate Professor, and then a tenured Full Professor. He is currently with The Department of Electronic Engineering, The Chinese University of Hong Kong (CUHK), Shatin, Hong Kong SAR, China. His research interest includes power converters such as multilevel inverters, converter topological developments, control, and modulation techniques, and their grid-tied applications.

Dr. Loh was the recipient of 5 IEEE paper-related prizes.

Frede Blaabjerg (S'86–M'88–SM'97–F'03) was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. He got the Ph.D. degree in Electrical Engineering at Aalborg University in 1995. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor of power electronics and drives in 1998. From 2017 he became a Villum Investigator. He

is honoris causa at University Politehnica Timisoara (UPT), Romania and Tallinn Technical University (TTU) in Estonia. His current research interests include power electronics and its applications such as in wind turbines, PV systems, reliability, harmonics and adjustable speed drives. He has published more than 600 journal papers in the fields of power electronics and its applications. He is the co-author of four monographs and editor of ten books in power electronics and its applications.

He has received 33 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award 2014, the Villum Kann Rasmussen Research Award 2014, the Global Energy Prize in 2019 and the 2020 IEEE Edison Medal. He was the Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS from 2006 to 2012. He has been Distinguished Lecturer for the IEEE Power Electronics Society from 2005 to 2007 and for the IEEE Industry Applications Society from 2010 to 2011 as well as 2017 to 2018. In 2019-2020 he served as a President of IEEE Power Electronics Society. He has been Vice-President of the Danish Academy of Technical Sciences. He is nominated in 2014-2020 by Thomson Reuters to be between the most 250 cited researchers in Engineering in the world.