## **Aalborg Universitet**

#### Solid State Generator for the Float Zone Process

Aunsborg, Thore Stig

DOI (link to publication from Publisher): 10.54337/aau528183112

Publication date: 2023

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA): Aunsborg, T. S. (2023). Solid State Generator for the Float Zone Process. Aalborg Universitetsforlag. https://doi.org/10.54337/aau528183112

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# SOLID STATE GENERATOR FOR THE FLOAT ZONE PROCESS

# BY THORE STIG AUNSBORG

**DISSERTATION SUBMITTED 2023**

# Solid State Generator for the Float Zone Process

Ph.D. Thesis

Thore Stig Aunsborg

Dissertation submitted: February, 2023

PhD supervisors: Prof. Stig Munk-Nielsen

Aalborg University

R&D manager Sune Bro Duun Topsil GlobalWafers A/S

Assistant PhD supervisor: Assoc. Prof. Christian Uhrenfeldt

Aalborg University

PhD committee: Associate Professor Peter Omand Rasmussen

Aalborg University, Denmark

Associate Professor Ziwei Ouyang

Technical University of Denmark, Denmark

Professor Dimosthenis Peftitsis

Norwegian University of Science and Technology, Norway

PhD Series: Faculty of Engineering and Science, Aalborg University

Department: AAU Energy

ISSN (online): 2446-1636

ISBN (online): 978-87-7573-744-4

Published by:

**Aalborg University Press**

Kroghstræde 3

DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Thore Stig Aunsborg

The thesis is typeset using  $\LaTeX 2_{\varepsilon}$

Printed in Denmark by Stibo Complete, 2023

# **Abstract**

The float zone method is an industrial process for the production of very high purity silicon single crystals. This silicon is an important substrate material for many electronic components and is therefore vital to the modern power electronics industry. The process relies on high frequency (MHz) induction heating, which is an application area where the generator for supplying the high frequency current is typically based on vacuum tube technology with low energy efficiency. The replacement of the vacuum tube system with a solid state generator is now feasible, in part due to the development and maturity of power devices made from new semiconductor materials. The work in this thesis investigates and expands this opportunity.

The thesis initially presents an overview of the float zone process and the requirements for the high frequency generator. An overview of suitable circuit topologies for this application is then presented and the challenges associated with the generator requirements are discussed.

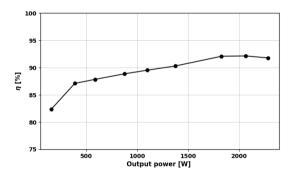

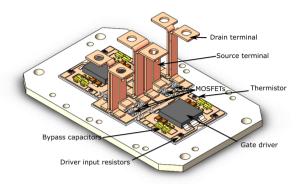

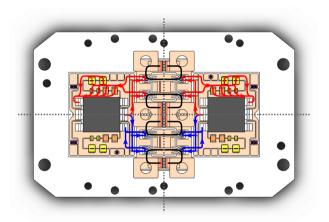

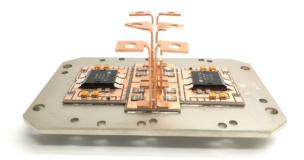

The thesis studies two main approaches to the construction of a generator system for MHz induction heating using a suitable resonant tank. The first approach utilizes a current source resonant inverter system for which a power module structure is presented with paralleled 1700 V SiC MOSFETs driven by integrated gate drivers. The module and inverter system design, manufacturing, and experimental operation is presented, and it is shown that the fabricated power module achieves higher than 90% efficiency for 2.3 kW output power.

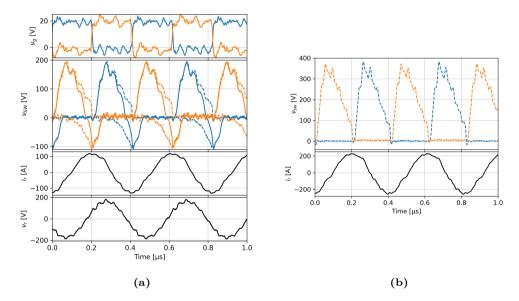

The second approach, which draws on the experiences with development of the first system, utilizes a Class E push-pull resonant inverter topology. The design of the components of the inverter are presented, and the system is experimentally verified for high efficiency operation up to an input power of 5 kW. This approach is argued to be a viable option for the realization of a flexible and efficient inverter system for a full-scale float zone process generator.

# Dansk resumé

Float zone metoden er en industriel proces der bruges til produktion af monokrystallinsk silicium med meget høj renhedsgrad. Dette silicium er et vigtigt substratmateriale til mange elektroniske komponenter, og er derfor af vital betydning for den moderne effektelektronikindustri. Processen udnytter højfrekvent (MHz) induktionsopvarmning, hvilket er et applikationsområde hvor strømgeneratoren typisk er baseret på radiorør som har lav virkningsgrad. Det er nu blevet muliggjort at udskifte radiorørssystemet med en transistorbaseret generator, til dels på grund af udviklingen og modningen af effektkomponenter lavet af nye halvledermaterialer. Arbejdet i denne afhandling undersøger og udvider denne mulighed.

Afhandlingen præsenterer indledningsvist et overblik over float zone processen og kravene der stilles til højfrekvensgeneratoren. Udfordringerne forbundet med disse krav bliver dernæst diskuteret, og særligt egnede kredsløbstopologier til applikationen bliver gennemgået.

Afhandlingen undersøger to hovedtilgange til at konstruere en generator til et MHz induktionsopvarmningssystem der bruger en passende svingningskreds. Den første tilgang anvender en strømkilderesonansvekselretter, hvortil strukturen beskrives for et effektmodul med 1700 V siliciumkarbid halvlederkomponenter drevet af integrerede styrekredsløb. Designet, fremstillingen og den eksperimentelle opførsel for effektmodulet og vekselrettersystemet præsenteres, og det vises at det fremstillede effektmodul opnår højere end 90% virkningsgrad for 2.3 kW udgangseffekt.

Den anden tilgang, som trækker på erfaringerne fra udviklingen af det første system, udnytter en klasse E push-pull vekselsrettertopologi. Udlægningen af komponenterne i vekselretteren præsenteres, og anvendelsen til MHz induktion-sopvarmning verificeres eksperimentelt for højeffektiv drift ved effektniveauer op til 5 kW. Slutteligt argumenteres der for at denne tilgang er en realistisk valgmulighed til realiseringen af et fleksibelt vekselrettersystem med høj virkningsgrad til en fuldskala float zone proces generator.

| A | bstra | ect                                       | $\mathbf{v}$ |

|---|-------|-------------------------------------------|--------------|

| D | ansk  | resumé                                    | vii          |

| P | refac | e                                         | xiii         |

| Ι | Ex    | tended summary                            | 1            |

| 1 | Inti  | roduction                                 | 3            |

|   | 1.1   | State of the art                          | 7            |

|   | 1.2   | Research objectives                       | 8            |

|   | 1.3   | List of publications                      | 9            |

|   | 1.4   | Thesis outline                            | 10           |

| 2 | Ger   | nerator specifications & inverter options | 13           |

|   | 2.1   | Float zone process requirements           | 14           |

|   | 2.2   | Terminology and switching concepts        | 17           |

|   |       | 2.2.1 Wide band gap devices               | 17           |

|   |       | 2.2.2 Switching operation                 | 19           |

|   | 2.3   | Circuit topologies                        | 20           |

|   | 2.4   | Inverter implementation challenges        | 24           |

|   |       | 2.4.1 Switching devices                   | 24           |

|   |       | 2.4.2 Power scaling and paralleling       | 25           |

|   |       | 2.4.3 Switching stage layout              | 27           |

|   | 2.5   | Resonant tank                             | 28           |

| 3 | Cur   | rent source resonant inverter development | 31           |

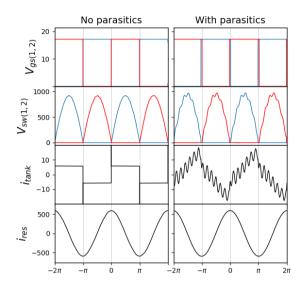

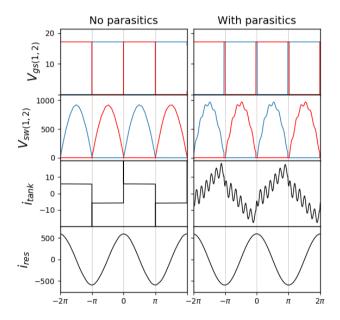

|   | 3.1   | Inverter operation                        | 32           |

|   |       | 3.1.1 Consideration of parasitic elements | 34           |

|   | 3.2   | Power module design                       | 37           |

|   |       | 3.2.1 Parasitic minimization              | 38           |

|    |      | 3.2.2 Thermal management                                     | 38  |

|----|------|--------------------------------------------------------------|-----|

|    | 3.3  | Experimental verification of operation                       | 40  |

|    |      | 3.3.1 Integrated gate driver performance                     | 40  |

|    |      | 3.3.2 Resonant operation                                     | 41  |

|    | 3.4  | Inclusion of series diodes                                   | 47  |

|    |      | 3.4.1 Experimental results                                   | 48  |

|    | 3.5  | Summary                                                      | 50  |

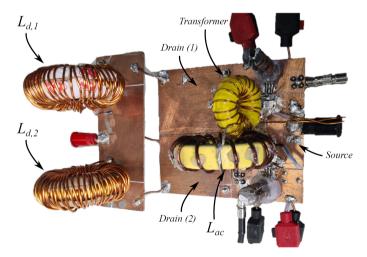

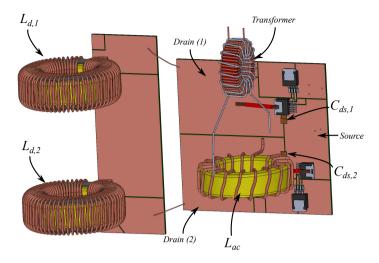

| 4  | Clas | ss E push-pull inverter development                          | 51  |

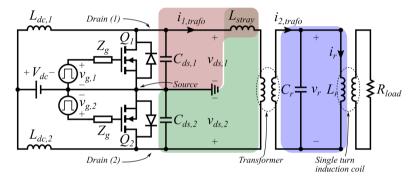

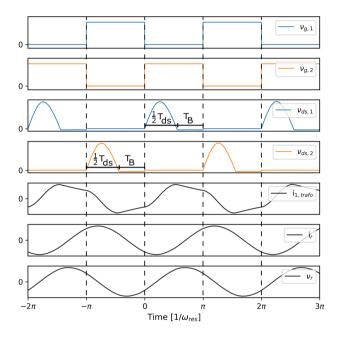

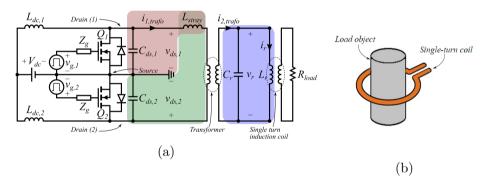

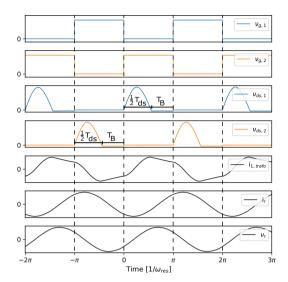

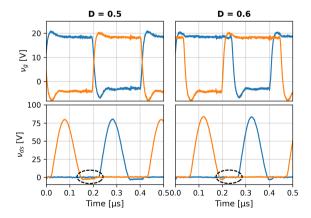

|    | 4.1  | Topology description                                         | 51  |

|    | 4.2  | Inverter component design                                    | 53  |

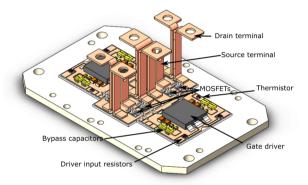

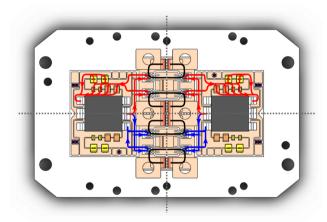

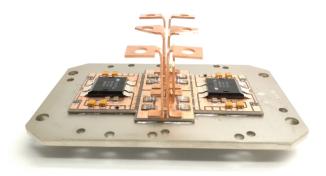

|    |      | 4.2.1 Power module                                           | 54  |

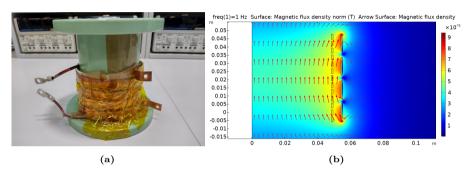

|    |      | 4.2.2 High frequency transformer                             | 55  |

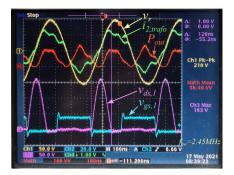

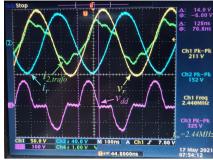

|    | 4.3  | Experimental verification                                    | 56  |

|    |      | 4.3.1 Experimental setup                                     | 57  |

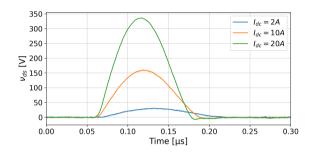

|    |      | 4.3.2 Results and discussion                                 | 58  |

|    | 4.4  | Inverter system scalability                                  | 62  |

|    | 4.5  | Summary                                                      | 63  |

| 5  | Cor  | nclusion & future work                                       | 65  |

|    | 5.1  | Future work                                                  | 66  |

| 6  | Ref  | erences                                                      | 69  |

|    |      |                                                              | ~ - |

| II | A    | ppended papers                                               | 81  |

| A  |      | allenges and opportunities in the utilization of WBG devices |     |

|    |      | efficient MHz power generation                               | 83  |

|    | A.1  | Introduction                                                 | 85  |

|    | A.2  | High frequency power delivery processes                      | 86  |

|    | 4.0  | A.2.1 Efficiency and circuit topologies                      | 86  |

|    | A.3  | Emerging WBG devices                                         | 88  |

|    | A.4  | Challenges in utilization of WBG devices                     | 89  |

|    |      | A.4.1 Gate driving                                           | 90  |

|    |      | A.4.2 Thermal management                                     | 91  |

|    |      | A.4.3 Electrical parasitics                                  | 92  |

|    | A.5  | Current developments in MHz WBG inverters                    | 92  |

|    | A.6  | Conclusion                                                   | 93  |

|    | Kete | erences                                                      | 94  |

| В            | Development of a current source resonant inverter for | high  |   |

|--------------|-------------------------------------------------------|-------|---|

|              | current MHz induction heating                         | 10    | 1 |

|              | B.1 Introduction                                      | 10    | 3 |

|              | B.2 Bidirectional CSRI operation                      | 10    | 5 |

|              | B.3 Design of inverter power module                   | 11    | 1 |

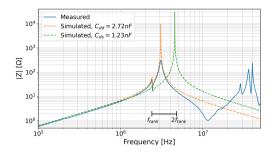

|              | B.4 Resonant tank system                              | 11    | 3 |

|              | B.5 Experimental results                              | 11    | 4 |

|              | B.5.1 Gate driver circuit assessment                  | 11    | 5 |

|              | B.5.2 Resonant operation                              | 11    | 6 |

|              | B.6 Conclusion                                        | 11    | 9 |

|              | References                                            | 12    | 0 |

| $\mathbf{C}$ | Class-E Push-Pull Resonance Converter with Load Varia | ation |   |

|              | Robustness for Industrial Induction Heating           | 12    | 5 |

|              | C.1 Introduction                                      | 12    | 7 |

|              | C.2 Proposed Topology                                 |       | 8 |

|              | C.3 Experimental Verification                         |       | 0 |

|              | C.4 Analysis of Design Robustness                     | 13    | 2 |

|              | C.5 Conclusion                                        |       | 4 |

|              | References                                            |       | 5 |

| D            | Demonstration of a Class E Push-Pull Resonant Inverte | r for |   |

|              | MHz Induction Heating                                 | 13    | 9 |

|              | D.1 Introduction                                      | 14    | 1 |

|              | D.2 Topology description                              | 14    | 2 |

|              | D.3 Design and components                             |       | 4 |

|              | D.4 Experimental results                              |       | 7 |

|              | D.5 Conclusions and future work                       |       | 0 |

|              |                                                       |       |   |

|              | 2.0 Compressions and ravaro norm                      | 10    | ' |

# Preface

This thesis is prepared as partial fulfillment of the PhD degree. The research presented herein was carried out as an Industrial PhD project in collaboration between Topsil GlobalWafers A/S and the Department of Energy, Aalborg University, and was funded by the Innovation Fund Denmark (IFD), Topsil GlobalWafers A/S, and the Department of Energy, Aalborg University.

The work was supervised by Professor Stig Munk-Nielsen, Topsil R&D manager Sune Bro Duun, and Associate Professor Christian Uhrenfeldt. I would like to express my sincere gratitude to each of you for giving me the opportunity to work with and learn from you. Thank you for trusting me with the freedom to develop myself both academically and personally, and for playing a major part in making this thesis happen.

I would also like to thank my colleagues at the R&D team at Topsil for the time we have worked together, the valuable guidance and discussions we have had throughout the project, and for creating a welcoming environment for me to learn from your expertise. The same goes for my colleagues at the Department of Energy - thank you all for both the helpful and the unhelpful discussions, and for making work here a worthwhile and enjoyable experience.

Finally, I wish to extend a special thanks to my amazing partner, family, and friends, whose wonderful company matters more to me than any personal accomplishment.

Thore Stig Aunsborg

Those Aunsland

#### Preface

# Part I Extended summary

# Chapter 1

# Introduction

The conversion and control of electrical energy is an important building block of the modern world. Prior to the advent and commercialization of the transistor and similar technologies in the middle of the 20th century, this task was accomplished using various forms of vacuum tube technology. Today, however, the conversion of electrical energy is nearly completely dominated by semiconductor-based power electronics, wherein solid state switching devices are used to control and modulate the flow of electrical power [1]. At the heart of all power electronic components are the semiconductor devices, most often made from silicon (Si), which control the flow of power from the source to the load. The components are found everywhere in modern society and in all power ranges, from cellular phone charging stations to electric vehicles, from small motor drives to wind turbines, and from toasters to industrial furnaces. The specifications of the devices and the way in which they are controlled is highly application dependent, and the devices are continuously improved to offer lower conversion losses, higher reliability, and lower cost.

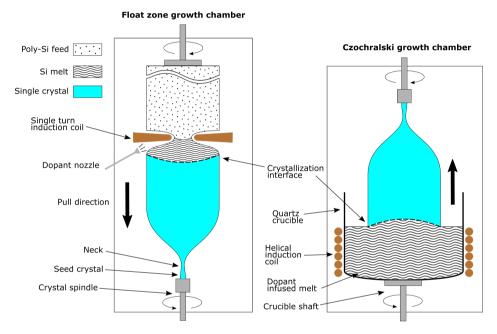

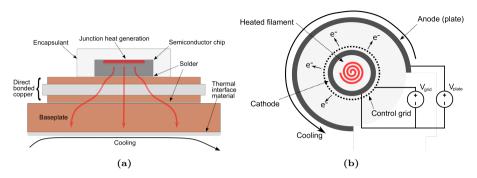

To produce the silicon needed as substrate material for the electronics industries, the two common crystal growth methods applied are shown in Fig. 1.1, which are known as the Float Zone (FZ) process and the Czochralski (CZ) process, respectively [2], [3]. The techniques share quite a few characteristics; in both processes, the aim is to grow a single, monocrystalline ingot of silicon with a low impurity concentration. This is accomplished by melting polycrystalline silicon and allowing the molten silicon to slowly crystallize on a monocrystalline seed crystal in a controlled atmosphere. In CZ growth, the seed is dipped into a melt-containing crucible and then drawn upwards while maintaining a stable crystallization interface, while in FZ growth the bottom part of a feed rod of polycrystalline material is melted while the seed is pulled downwards, resulting in a "floating" molten zone. In order to produce a monocrystalline ingot, the pull rate is high at the initial stages of growth to facilitate the formation of

a *neck* with a diameter of a only few millimeters. Because of the low thermal stress in the thin neck, the propagation and multiplication of dislocations is greatly suppressed, such that a dislocation-free crystal is achieved after a few centimeters of growth [3], [4]. After neck formation, the pull rate is reduced to allow the growth of larger diameter ingots. For both FZ and CZ growth, the crystal is constantly rotated to provide homogeneity and to ensure the production of a cylindrical rod. The desired doping profile can be achieved either by adding dopants to the melt or by post-processing after growth.

Fig. 1.1: Illustration of the basic setup for the two main crystal growth techniques for silicon.

By production volume, the CZ method is by far the most used of the two techniques, as larger diameter rods can be produced at a lower cost than what is possible with the FZ method [3]. However, since the melt is contained in a quartz (SiO<sub>2</sub>) crucible, the produced crystal is inevitably contaminated with the crucible material, primarily oxygen [5]. Some discrete high power silicon components, such as power thyristors and high voltage diodes and IGBTs, have demanding specifications that require a substrate material with very high purity and resistivity, which is impeded by oxygen contamination [6]. The free-standing melt in the FZ method ensures minimal contamination, making the product ideal for higher voltage devices.

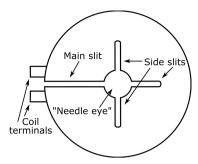

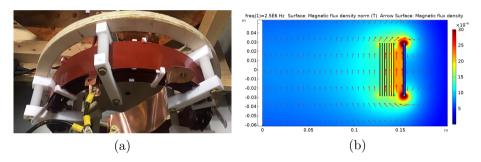

The diameter of the produced ingots is an important parameter, both from a device property standpoint and from an economic perspective. Modern FZ crystals are grown using the "needle eye" technique where the upper part of the molten zone is much narrower than the crystal (see Fig. 1.1) [2], [6]. Using this technique, ingots up to 200 mm in diameter are currently on the market [4]. The power delivery in this process comes from a flat single-turn induction coil surrounding the needle eye in close proximity to the melt. The application of the needle eye FZ technique in seen in the photograph in Fig. 1.2 taken through the viewport of an FZ puller, showing the "pancake" inductor and the hot molten silicon. After the FZ processing the crystal is cut into ingots, which are further cut into thin wafers that are typically polished to a mirror finish. The final product of the process, silicon wafers used for device production, is shown in Fig. 1.3.

Fig. 1.2: Photograph of the FZ process through the view port of an FZ puller [7].

Fig. 1.3: Picture of the product from the silicon FZ process: low-contaminant monocrystalline silicon wafers [7].

The induction heating coil itself is a critical part of the FZ process to allow for contact-free crystal growth, ensure power delivery that results in a suitable heat and force distribution in the melt, and reduce the likeliness of electrical breakdown of the gas causing arcing [2]. By running a high frequency current through the coil an electromagnetic (EM) field is generated, causing eddy currents to flow in the silicon which heat the material through Joule heating. To achieve a smooth melting profile and the required heating profile that facilitates FZ growth, operation frequencies of a few MHz is typically used. This high frequency along with voltage and current requirements result in demanding specifications for the generator system supplying the heating power.

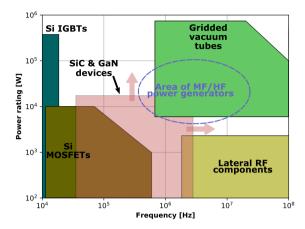

Interestingly, FZ production of silicon is therefore one of the few areas where solid state technology has yet to outmatch vacuum tube systems. As such, it belongs to a set of applications primarily within the field of high frequency/high power amplifier- and oscillator systems, such as e.g. radio frequency (RF) broadcasting amplifiers or industrial MHz heating systems, where tubes are still widely in use [8]–[11]. The FZ process requirements for high quality and large scale crystal growth have made vacuum tubes unparalleled for this type of high frequency heating application. One drawback is, however, that vacuum tubes are typically operated as linear amplifiers with energy efficiencies below 80% [11]–[13] (and generally significantly lower), while solid state based switch-mode circuit topologies can achieve practically realisable efficiencies above 90%, leading to considerable interest in exploiting the advantages of solid state solutions for generators for FZ production and similar processes. The challenge in achieving this goal lies in utilizing the semiconductor devices at the voltage, frequency, and power levels required for the applications.

In order to pursue a solid state generator system suited for FZ and other high frequency processes, researchers are looking toward new material technologies. Historically, power electronics devices were almost exclusively based on silicon due to the availability of high quality substrate material, native oxide properties, and process maturity [14]. While this technology is continually improving, the fundamental material properties of Si means that Si devices are limited in their power- and voltage handling capabilities in the MHz frequency range [15], [16]. In this respect, the material is outclassed by wide band gap (WBG) semiconductors such as gallium nitride (GaN) and silicon carbide (SiC). Recent advances in semiconductor manufacturing have enabled the development of competitive WBG power devices suitable for high frequency application areas [16], [17]. These WBG materials open up the design space for making devices

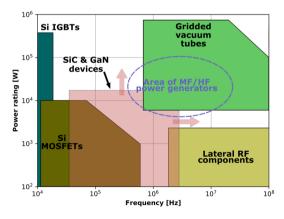

Fig. 1.4: Estimation of the operating ranges of devices used in power generation and conversion. The circled area shows the expanded application area considered here. [Paper A]

with higher breakdown voltage, reduced power losses, and superior switching performance based on the application demands [18]. For the FZ process and similar industry applications, devices with high switching speed and large power handling capability per area are desired, and WBG devices are thus prime candidates for expanding the frequency and power regimes of solid state technology into the demanding application of industrial MHz heating such as FZ production. This opportunity is illustrated in Fig. 1.4, which shows roughly the applicability areas of different device types used in power conversion and indicates the expansion possibilities of WBG devices into the high frequency target area currently dominated by gridded vacuum tubes.

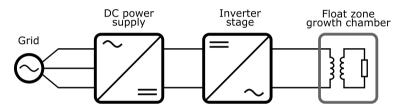

To take advantage of these possibilities, this project revolves around investigations of the utilization of these devices in inverters suitable for a generator system for the FZ process. The basic layout of such a system is shown in Fig. 1.5.

Fig. 1.5: General schematic layout of a generator system for FZ process heating.

#### 1.1 State of the art

Induction heating is a very versatile process with many industrial heating applications, such as boiling, hardening, and welding [19], [20]. While common induction heating generators operate at significantly lower frequencies than the FZ process requires, several applications exist for plasma generators, dielectric heaters, and wireless power transfer which utilize frequencies in the MHz regime and often operate in the ISM frequency bands (6.78 MHz, 13.56 MHz, and multiples) [21]–[23]. Therefore, although the amount of specific literature on generator development for the FZ process is limited, insight may be gained from the considerable research that has been presented by various groups in the fields of MHz inverters for related industrial processes and high frequency resonant inverters in general utilizing WBG devices. An illustrative selection of recent research efforts relevant to the development goals in this project is given in table 1.1 below.

**Table 1.1:** Selected recent research efforts in high frequency power conversion. The table is expanded from Paper A.

| Authors/year                 | Targeted application(s)        | Power switches                               | Package              | Circuit topology                                           | Operating<br>frequency | Output<br>power         | Efficiency                              |

|------------------------------|--------------------------------|----------------------------------------------|----------------------|------------------------------------------------------------|------------------------|-------------------------|-----------------------------------------|

| Haehre et al.<br>(2014) [24] | HF power<br>generators         | 1200 V SiC<br>MOSFET                         | TO-247-3             | Class D (full<br>bridge)                                   | 2.4 MHz                | 2.4 kW                  | 90.6%                                   |

| Ghodke et al.<br>(2016) [25] | Plasma source                  | 900 V SiC<br>MOSFET                          | TO-263-7             | Class D<br>(half-bridge)                                   | $2~\mathrm{MHz}$       | $3.4~\mathrm{kW}$       | N/A                                     |

| Choi et al. (2016) [26]      | Wireless<br>power transfer     | a) 1200 V SiC<br>MOSFET b) 650<br>V GaN HEMT | a) DE150<br>b) GaNpx | a) single ended class $\phi_2$ b) push-pull class $\phi_2$ | 6.78 MHz               | a) 2.2<br>kW b) 2<br>kW | <ul><li>a) 93%</li><li>b) 96%</li></ul> |

| Guo et al.<br>(2016) [27]    | Isolated<br>DC/DC<br>converter | 1200 V SiC<br>MOSFET                         | Bare die             | Full-bridge LLC                                            | $1.2~\mathrm{MHz}$     | 4 kW                    | 97%                                     |

| Nguyen et al.<br>(2017) [28] | Wireless<br>power transfer     | 650 V GaN<br>HEMT                            | GaNpx                | Class DE (5<br>half-bridges)                               | $13.6~\mathrm{MHz}$    | $4~\mathrm{kW}$         | 96.5%                                   |

| Denk et al.<br>(2018) [29]   | HF power<br>generators         | 1200 V SiC<br>MOSFET                         | ISOPLUS-<br>SMPD     | Class DE<br>(full-bridge)                                  | $2.5~\mathrm{MHz}$     | $25~\mathrm{kW}$        | 92.5%                                   |

| Park et al.<br>(2020) [30]   | Plasma<br>generator            | 1200V SiC<br>MOSFET                          | TO-247-3             | Class D<br>(full-bridge)                                   | $3.4~\mathrm{MHz}$     | 10 kW                   | 97%                                     |

| Gu et al.<br>(2021) [31]     | Wireless<br>power transfer     | 650 V GaN<br>HEMT                            | GaNpx                | PPT $\phi_2$                                               | 6.78 MHz               | 1.7 kW                  | 95.7%                                   |

As seen from the table, the application area for MHz inverters is diverse and there are many approaches to high efficiency designs. All of these rely on soft-switching concepts to dramatically reduce the switching losses at high frequency, which is achieved by utilizing circuit topologies with reactive elements to shape the voltages and currents of the switching devices at the switching instant [32]–[34]. Most commonly WBG devices are employed, in particular SiC MOSFETs and GaN HEMTs, and the choice of device is dependent on factors such as switching frequency, voltage requirements, and circuit topology [16], [18], [35]. In order to utilize the fast switching power devices, suitable packaging concepts of the devices must be employed both for discrete devices and power modules [36]–[38]. For MHz frequency operation, driving the switching devices also requires significant consideration [39], [40], as does the development of high efficiency passive components such as transformers and inductors [41], [42].

Within the context of a MHz inverter system for the FZ process, on overview of practical component limitations, circuit topologies, and switching device considerations is given in chapter 2.

# 1.2 Research objectives

The FZ production of silicon currently relies on vacuum tube oscillators due to demanding process requirements, which means the power efficiency of the production is limited. If a solid state generator based on off-the-shelf components could be utilized instead, significant advantages in energy savings, generator supply security, and process control are envisioned. By employing emerging

WBG semiconductor components, the frequency and power ranges of single solid state power modules is continuously increasing. Therefore, to investigate this opportunity for the FZ industry, the first research objective is

To investigate the feasibility of expanding the application range of solid state inverters into the area suitable for FZ production.

To achieve this first research goal, it is necessary to develop a solid understanding of the challenges associated with operation the relevant devices in this frequency range, many of which are characterized by both theoretical and practical elements. Therefore, the second research objective is

To expand the knowledge base on the practical usage of WBG-based devices for MHz inverters through design, development, and verification of operation of relevant power module prototypes.

To reach these goals the deliberate design of the entire inverter system is necessary, such that the specifics of the process requirements are considered in all aspects of the generator system.

# 1.3 List of publications

This thesis is based on the work presented in the following papers, which are also included as part II of the thesis.

- A "Challenges and opportunities in the utilization of WBG devices for efficient MHz power generation", Thore Stig Aunsborg, Sune Bro Duun, Christian Uhrenfeldt and Stig Munk-Nielsen, *Published in "IECON 2019 45th Annual Conference of the IEEE Industrial Electronics Society"*, pp. 5107-5113, 2019.

- B "Development of a current source resonant inverter for high current MHz induction heating", Thore Stig Aunsborg, Sune Bro Duun, Stig Munk-Nielsen and Christian Uhrenfeldt, *Published in "IET Power Electronics"*, 15, pp. 1–10, 2022.

- C "Class-E Push-Pull Resonance Converter with Load Variation Robustness for Industrial Induction Heating", Benjamin Futtrup Kjærsgaard, Janus Dybdahl Meinert, Thore Stig Aunsborg, Sune Bro Duun, Asger Bjørn Jørgensen and Stig Munk-Nielsen, Published in "European Conference on Power Electronics and Applications (EPE'22 ECCE Europe)", pp. 1-8, 2022.

D "Demonstration of a Class E Push-Pull Resonant Inverter for MHz Induction Heating", Thore Stig Aunsborg, Benoît Bidoggia, Sune Bro Duun, Janus Dybdahl Meinert, Benjamin Futtrup Kjærsgaard, Asger Bjørn Jørgensen and Stig Munk-Nielsen, Accepted for publication in "Applied Power Electronics Conference (APEC)", 2023.

In addition to the appended papers which are included in the thesis, the author has participated in the work on the following papers which have been published during the PhD project period.

- 1 "High Frequency Resonant Operation of an Integrated Medium Voltage SiC MOSFET Power Module", Asger Bjørn Jørgensen, Thore Stig Aunsborg, Szymon Beczkowski, Christian Uhrenfeldt and Stig Munk-Nielsen, Published in "IET Power Electronics", 13, pp. 475-482, 2020.

- 2 "Thermal Performance of an Integrated Heat Spreader for GaN HEMT devices", Faheem Ahmad, Thore Stig Aunsborg, Szymon M. Beczkowski, Stig Munk-Nielsen and Asger Bjørn Jørgensen, Published in "12th International Conference on Integrated Power Electronics Systems (CIPS)", pp. 1-6, 2022.

- 3 "Digital design demonstration of 10kV SiC-MOSFET power module to improve wire-bonding layout for power cycle capabilities", Masaki Takahashi, Thore Stig Aunsborg, Christian Uhrenfeldt, Stig Munk-Nielsen and Asger Bjørn Jørgensen, Published in "IEEE International Workshop on Integrated Power Packaging (IWIPP)", pp. 1-6, 2022.

- 4 "Analysis of Nonlinear Conductivity Coating used to Improve Electric Field Distribution in Medium Voltage Power Module", Yuan Gao, Yang Yang, Hongbo Zhao, Thore Stig Aunsborg, Stig Munk-Nielsen and Christian Uhrenfeldt, Published in "IEEE Energy Conversion Congress and Exposition (ECCE)", pp. 1-7, 2022.

# 1.4 Thesis outline

This thesis is structured as follows. Chapter 1 presents the topic of float zone silicon crystal growth from a general perspective, and introduces the state of the art in the field of high frequency inverter structures relevant to the development of an inverter for the float zone process. The research objectives are then presented.

In order to fulfil the research goals, chapter 2 dives deeper into considerations of the float zone process requirements seen from a generator perspective, in order to investigate the feasibility of different approaches to the solid state generator. An overview of directly relevant power electronics concepts is then

#### 1.4. Thesis outline

briefly given, leading into a discussion of suitable circuit topologies for the inverter and the challenges in realizing the physical generator system. Several of the arguments in this and in the introduction chapter were developed and presented in paper A.

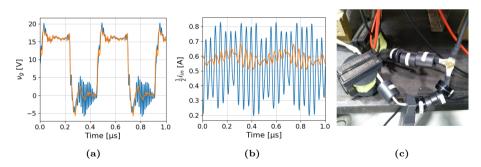

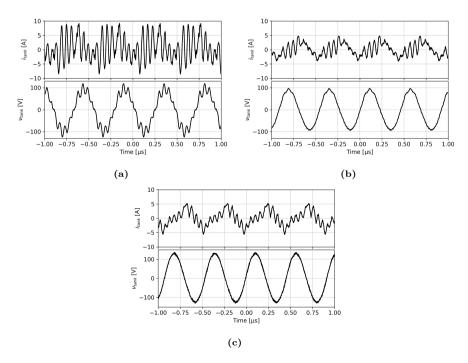

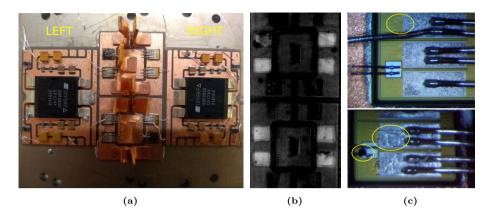

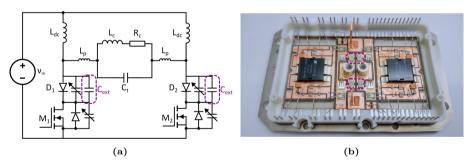

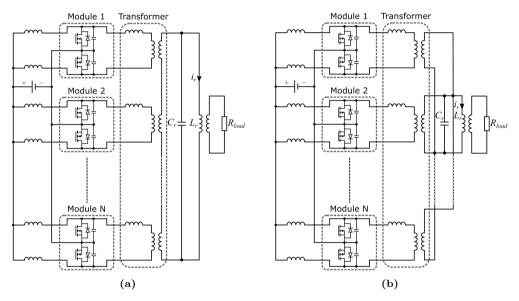

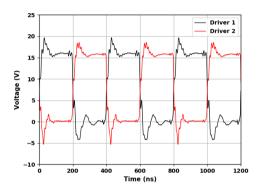

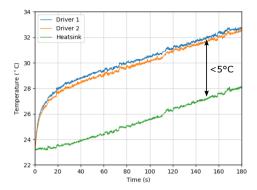

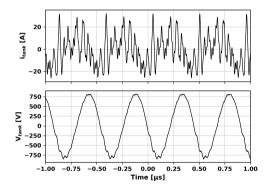

Chapter 3 presents the efforts in the demonstration of a current source resonant inverter for MHz induction heating. The fundamentals of the topology are presented, along with a power module featuring paralleled SiC MOSFETs and integrated gate drivers for transformerless MHz operation of a industrially relevant resonant tank. The design, operation, and discussion of the system is the main content of paper B. In addition, a similar approach with the inclusion of diodes for switch timing variation is briefly presented.

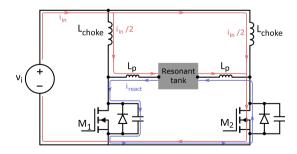

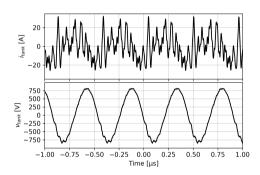

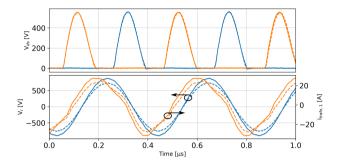

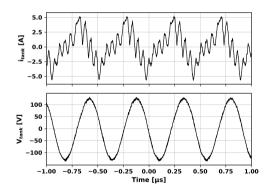

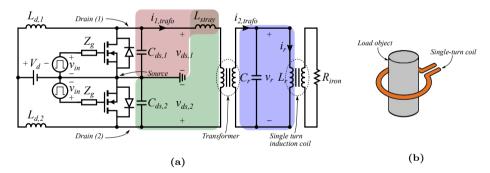

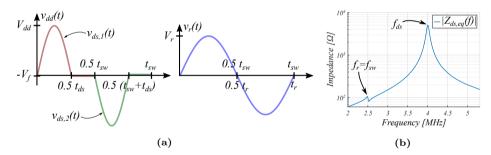

The knowledge and experience in working at MHz frequencies with paralleled WBG components is further developed in chapter 4. Here, a Class E push-pull resonant inverter implementation with load frequency variation robustness is introduced. The basic circuit operating principles of the topology are introduced, along with experimental demonstration and discussion of the operation of the inverter. A low power version of the topology is presented in paper C, while further development of the concept to a higher power implementation is presented in paper D.

Chapter 5 concludes on the findings in the thesis and highlights the main research contributions, ending with a discussion of future work.

# Chapter 1. Introduction

# Chapter 2

# Generator specifications & inverter options

In order to assess the feasibility of developing a generator suitable for the FZ process, the nature of the process demands on the generator system is first overviewed in this chapter.

Successful growth of silicon by the FZ process is governed by the highly nonlinear and complex interplay of many parameters. The process has been studied and continuously improved since its conception in the early 1950s, and thus the geometries of components and operation specifications are finely tuned to allow for production of large diameter crystals. Because of this, a solid state generator must adhere to the specifications from existing technology. As the generator supplies the heating power to the melt through induction heating, one of the most critical components is the work coil, a schematic of which is shown in Fig. 2.1. This coil is commonly made of copper and the influence of the slits is to promote magnetic field strengthening and consequently heating at the outer regions of the melt surface away from the molten neck. Coupled with the rotation of the crystal, a nearly axisymmetric temperature profile can be achieved in the melt by the use of slits [2].

The work coil geometry is determined entirely by the process requirements and small changes to its geometry may result in drastic variation in the electromagnetic pressure and molten Si temperature distribution profile [2]. Since a single turn coil is used and the load is non-ferromagnetic, the coupling efficiency for the induced magnetic field is limited. This results in the necessity of carefully considering the work coil properties in the FZ generator system design.

Chapter 2. Generator specifications & inverter options

Fig. 2.1: Top-down schematic of a work coil used for FZ growth with the needle eye technique.

# 2.1 Float zone process requirements

The developed solid state generator system should be integrable with existing industrial FZ production geometries and process specifications. Therefore, the specifications most relevant to the generator development are outlined below.

**Power level** The power requirement for the FZ generator is self-evidently determined primarily by the need to sustain the zone of molten Si at around 1400°C, and therefore increases for larger crystal diameters. Under the high frequency approximation for the generated electromagnetic (EM) field which assumes, as is typical of the FZ process, that the skin depth is small compared to the inductor and feed rod dimensions [2], [6], the dissipated power density through Joule heating can be written

$$q_{\rm EM} = \frac{i_{\rm ef}^2}{\delta \sigma} \tag{2.1}$$

where  $i_{\rm ef}$  is the effective density of the surface current, which is directly proportional to the coil current. Empirically, because the coupling to the Si load is weak, many hundreds of amperes are normally required in the work coil, increasing with higher power requirements for large diameter crystal growth, such that the transferred power to the silicon ingot may be in the tens of kW for large diameters. Due to the high currents, resistive heating losses of the coil itself may be of similar magnitude, so considering this as well as losses in connectors and auxiliaries, the output power of the envisioned generator must be scalable within the area shown in Fig. 1.4.

Working frequency The induction heating frequency is a critical parameter for successful crystal growth. In order to achieve sufficient melting of the feed rod a low penetration depth is required, often illustrated by the skin depth at which the EM field has decayed to 1/e of its surface value

$$\delta = \sqrt{\frac{\rho}{\pi f \mu_{\rm T} \mu_0}} \tag{2.2}$$

where  $\delta$  is the skin depth,  $\rho$  is the resistivity, f is the frequency,  $\mu_r$  is the relative permeability, and  $\mu_0$  is the vacuum permeability. In the FZ process for larger crystal diameters using the needle eye technique, MHz frequencies are typically required to ensure proper melting of the surface of the silicon. If the frequency is too low, the EM field penetrates deep into the feed rod (see table 2.1), which combined with radiative heat loss leads to the formation of a thin solid layer at the surface, preventing successful growth [43]. However, too high operating frequency increases the risk of arcing and process instability. Therefore the frequencies currently used in industry and which have a proven track record of successful results are between 2.4 MHz and 3 MHz, although successful growth is also possible with slightly lower frequency [2], [44].

Table 2.1: Variation of penetration depth in silicon with coil operating frequency.

|                |                                          | Skin depth, $\delta$ [mm] |                  |                  |                  |

|----------------|------------------------------------------|---------------------------|------------------|------------------|------------------|

| Material phase | Resistivity, $\rho$ [ $\Omega \cdot m$ ] | $500~\mathrm{kHz}$        | $1~\mathrm{MHz}$ | $2~\mathrm{MHz}$ | $3~\mathrm{MHz}$ |

| Solid silicon  | $2 \cdot 10^{-5} \ [45]$                 | 3.2                       | 2.3              | 1.6              | 1.3              |

| Molten silicon | $8.3 \cdot 10^{-7} \ [45]$               | 0.65                      | 0.46             | 0.32             | 0.27             |

In addition, normal variations in the coupling to the load during stable operation and within different phases of the growth process means that the work coil inductance is not fixed. If the coil is part of a resonant circuit, the resonance frequency of this circuit is then also not fixed and the oscillator system is therefore typically allowed to drift in frequency during the process to maintain the desired heating profile and force balance surrounding the molten zone. It is thus an additional requirement from the generator that it is capable of operating with high efficiency in a wide frequency range.

**Coil voltage** The requirement for high coil voltage is an important reason for the usage of vacuum tubes technology in FZ production. From the relations between current, power, and frequency from (2.1) and (2.2) it follows that

$$i_{\rm ef}^2 \propto f^{-1/2} \Longrightarrow I_{\rm coil} \propto i_{\rm ef} \propto f^{-1/4}$$

(2.3)

where  $I_{coil}$  is the current in the work coil. Assuming a small frequency variation, such that the work coil can be represented by simple constant inductance, and a high quality factor of the coil to neglect the coil resistance, the proportionality between frequency and voltage is found from Ohm's law:

$$V_{\text{coil}} = 2\pi f L_{\text{coil}} I_{\text{coil}} \Longrightarrow V_{\text{coil}} \propto f^{3/4}$$

(2.4)

Given that the power requirements, coil geometry, and high operating frequency are entirely specified by the requirements of the melting process it is evident that high voltages must be applied at the coil terminals, and any additional series inductance will result in higher voltage requirements for a given output power. Thus for a common loaded work coil requiring many hundreds of amperes and having an inductance of  $\approx 100$  nH, multiple kV between the coil terminals is required to achieve the required power delivery to the silicon load in industrial FZ processes.

Arcing protection The need for high frequency current in the work coil and consequently high terminal voltage seen from (2.4) is accompanied by the risk of electric breakdown of the atmosphere in the growth chamber causing arcing [43]. This is especially critical in the high electric field area around the main slit in Fig. 2.1. A small amount of nitrogen is commonly added to the argon atmosphere to reduce the risk of arcing, and using high chamber pressure can increase the breakdown strength of the gas [46]. However, the pressure must be balanced with the growth requirements as higher pressure also promotes convective cooling, increasing the thermal stresses of the growing crystal. In general, avoiding arcing is a key challenge in growing large diameter crystals by the FZ process [2], and since arcing is a relatively common occurrence, the developed generator must be tolerant to this type of event.

Load variation and frequency tracking A common element of induction heating processes is that the equivalent resistive load can vary in a wide range [47], [48]. Although dependent on the specific system, the generator must generally be able to supply the required power during all phases of the growth process. Therefore, a closed loop control scheme with fast response to resistive and inductive loading changes is required for efficient generator operation and sufficient process control. While these consideration of process control opportunities are important in the system design, the development of the closed loop control scheme for the generator is outside the scope of this project.

All the features required for the solid state generator for the FZ process are summarized in table 2.2, along with features that are preferred for a commercial system.

Table 2.2: Requirements and preferred features for a generator for the float zone process.

| Parameter             | Requirement                   | Notes                                                   |

|-----------------------|-------------------------------|---------------------------------------------------------|

| Output power level    | Several tens of kW            | Dependent on ingot diameter                             |

| Working frequency     | $2-3~\mathrm{MHz}$            | Variable frequency required                             |

| Coil terminal voltage | Multiple kV                   | Dependent on ingot diameter                             |

| Arcing protection     | Yes                           | Should allow fast restart of process                    |

| Load variation        | Unloaded to full load         | Dependent on chamber<br>preheating system               |

| Frequency tracking    | Yes                           | Fast resonance frequency tracking in closed loop        |

|                       | Preferred feature             | es                                                      |

| Inverter components   | Off-the-shelf<br>devices      | Important for security of supply                        |

| Galvanic isolation    | Low loss<br>transformer       | Low frequency preferred, requires high voltage switches |

| Power regulation      | Fast and flexible variability | Desired for improved process controllability            |

| RF noise robustness   | Control system immunity       | Adherence to EMC regulation                             |

# 2.2 Terminology and switching concepts

In order to provide a discuss the possibilities for a solid state inverter that meets the criteria in the previous section, a few relevant power electronic concepts are briefly revisited below.

# 2.2.1 Wide band gap devices

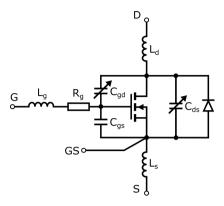

The ideal switching device that is capable blocking infinite voltage in the OFF-state, has zero resistance in the ON-state, and can instantaneously switch between the two states does not exist. Instead, real semiconductor devices have parasitic resistances, capacitances, and inductances, as shown in Fig. 2.2. For enhancement mode FETs the device works as a switch controlled by the gate voltage  $\nu_{\rm gs}$  when operated in the ohmic region. When the gate voltage is larger than the threshold voltage  $\nu_{\rm gs} > V_{\rm th}$  the device is in the ON-state and behaves as a lumped resistor with some nominal value  $R_{\rm ds,on}$ . The gate-drain capacitance  $C_{\rm gd}$  and the drain-source capacitance  $C_{\rm ds}$  are highly non-linear under varying drain-source voltage  $\nu_{\rm ds}$  while  $C_{\rm gs}$  is constant [49]. In device datasheets, these capacitors are commonly represented by the following terminol-

ogy: input capacitance  $C_{\rm iss} = C_{\rm gs} + C_{\rm gd}$ , output capacitance  $C_{\rm oss} = C_{\rm ds} + C_{\rm gd}$ , and reverse-transfer capacitance  $C_{\rm rss} = C_{\rm gd}$ .

Fig. 2.2: Circuit schematic of a switching MOSFET including the parasitic capacitances. The three main terminals of the device are the drain (D), source (S), and gate (G) terminals, and the (GS) terminal is an optional auxiliary source connection for decoupling the gate loop from the power loop. With the exception of the body diode, any FET will have a similar parasitic layout. Here,  $R_{\rm g}$  is the internal device gate resistance, and the inductances from the interconnections shown may be inside the package for discrete devices.

The parasitic elements, and in particular the parasitic capacitances, are highly important to the switching properties of the device, and even more so for high switching frequencies and higher power devices [37], [50]. The possibility for reduction of these device parameters is a major attraction of WBG device technology. The wide band gap results in several beneficial material properties, the most important of which is the higher critical field  $E_{\rm c}$ , which is the maximum field strength the material can withstand before the onset of avalanche breakdown [51]. Some of the advantages resulting from this feature in unipolar WBG devices are illustrated in Baliga's Figure of Merit (BFOM) [52], which is concerned with the drift region resistance, and Baliga's High Frequency Figure of Merit (BHFFOM) [53], in which the product of resistance and input capacitance are assessed

$$R_{\rm on,sp} = \frac{4V_{\rm br}^2}{\epsilon_{\rm r}\mu_{\rm n}E_{\rm c}^3} \Rightarrow {\rm BFOM} = \epsilon_{\rm r}\mu_{\rm n}E_{\rm c}^3$$

(2.5)

$$\frac{1}{R_{\rm on,sp}C_{\rm in,sp}} = \frac{1}{2}\mu_{\rm n}E_{\rm c}^2V_{\rm G}^{1/2}V_{\rm br}^{3/2} \Rightarrow \text{BHFFOM} = \mu_{\rm n}E_{\rm c}^2$$

(2.6)

where  $R_{\rm on,sp}$  is the specific on-state resistance,  $V_{\rm br}$  is the breakdown voltage,  $\epsilon_{\rm r}$  is the relative permittivity,  $\mu_{\rm n}$  is the electron mobility,  $E_{\rm c}$  is the critical electric field,  $V_{\rm G}$  is the gate voltage, and  $C_{\rm in,sp}$  is the specific input capacitance. These FOMs illustrate the tradeoffs between voltage ratings, die area, on-state losses, and switching performance based on ideal material parameters, and are

presented for Si, SiC, and GaN in table 2.3. The higher FOMs for SiC and GaN indicate a larger power handling capability and better high frequency performance for a device of a given die area and voltage rating.

**Table 2.3:** Key material parameters for semiconductors for fast-switching power components [Paper A].

|                                                         | Silicon | 4H-SiC | GaN  |

|---------------------------------------------------------|---------|--------|------|

| Band gap, $E_{\rm g}$ [eV]                              | 1.12    | 3.23   | 3.39 |

| Critical E-field, $E_{\rm c}$ [MV/cm]                   | 0.3     | 2.5    | 3.75 |

| Relative permittivity, $\epsilon_{\rm r}$               | 11.7    | 9.66   | 8.9  |

| Electron mobility, $\mu_{\rm n}  [{\rm cm}^2/{\rm Vs}]$ | 1350    | 900    | 1265 |

| BFOM (rel. to Si)                                       | 1       | 319    | 1392 |

| BHFFOM (rel. to Si)                                     | 1       | 46     | 146  |

## 2.2.2 Switching operation

One of the most important parts of high frequency power conversion is the minimization of switching losses. This is because the losses associated with the switching of semiconductor devices scale linearly with the switching frequency and, neglecting driving losses, can be written as

$$P_{\rm sw} = (E_{\rm on} + E_{\rm off}) f_{\rm sw} \tag{2.7}$$

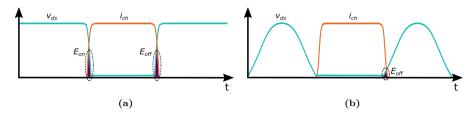

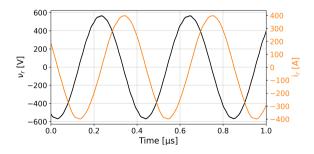

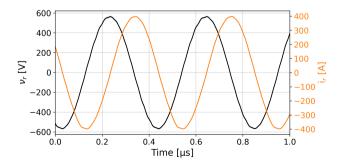

where  $E_{\rm on}$  and  $E_{\rm off}$  are the turn-on and turn-off switching energies, respectively. While the magnitude of these losses is generally dependent on complex interactions between the parasitic elements of the components in the circuit [1], [54], it is in most cases necessary for MHz switching of higher voltage components that the switching losses are mitigated through soft switching methods to avoid the concurrency of switch voltage and current during the switching transitions [29], [41]. This can be achieved either through zero voltage switching (ZVS) or zero current switching (ZCS). ZVS ideally eliminates  $E_{\rm on}$  by ensuring that  $\nu_{\rm ds}=0$  prior to turn-on, while ZCS eliminates  $E_{\rm off}$  by letting the device channel current  $i_{\rm ch}=0$  before and during turn-off. The former is more suitable for high frequency operation of FETs, as generally  $E_{\rm on}>E_{\rm off}$  and ZVS eliminates the losses associated with hard switching of the output capacitance equal to  $\frac{1}{2}f_{\rm sw}C_{\rm oss}\nu_{\rm ds}^2$  [1], [55], [56]. The way in which soft switching is achieved, and the corresponding waveforms, depend on the circuit topology. An illustrative example of hard- and soft switching waveforms is shown in Fig. 2.3.

The turn-off losses under ZVS conditions may be written as [57]

$$E_{\text{off}} = \int_{t_1}^{t_2} \nu_{\text{ds}}(t) i_{\text{ch}}(t) dt$$

(2.8)

Fig. 2.3: Simplified examples of switch voltage and current during switching events. (a) Hard switching, (b) ZVS soft switching.

where  $t_1$  and  $t_2$  are the beginning and end of the overlap time, respectively. In some resonant circuits a low turn-off switch voltage and low  $E_{\text{off}}$  is naturally achieved [58], while in others this loss can be minimized by using fast switching devices such that the time period  $t_2 - t_1$  is very short. The channel current cut-off speed is primarily controlled by the gate driver, meaning that for a compact gate layout and fast WBG devices, very fast turn-off transitions and nearly zero total switching loss can be achieved using low inductive gate loops and gate drivers with high current capability [55], [59]. Using these techniques with suitable switching devices and circuit topologies, MHz inverter systems can therefore be realized.

# 2.3 Circuit topologies

The choice of circuit topology of the inverter for the generator system is highly important to the performance and efficiency of the system. As was mentioned in chapter 1, traditional RF amplifier circuits used for vacuum tube generators such as Class A, B, or C have too low operating efficiencies to be useful solutions for the solid state generator. However, as switch-mode inverters with traditional hard switching power devices are also not feasible circuit topologies, circuits allowing soft switching of the power devices are necessary. This can be achieved using e.g. quasi-resonant inverters where reactive components are used in normally hard-switched converters to achieve ZVS or ZCS at the expense of increased component count, higher device stress, and/or higher conduction losses [1], [58], [60]. For induction heating systems, and in RF power conversion systems, resonant inverters (or, equivalently, switched-mode power amplifiers) are typically used for applications requiring high efficiency. In these circuits, soft switching is achieved by utilizing the load network to shape the switch voltage and current. Implementations of these inverters in recent literature were overviewed in section 1.1 and here a brief overview of the topologies will be given with special attention to aspects relevant to MHz induction heating processes.

The selection of inverter circuit topology is dependent on many criteria

established by the application. One of the important metrics is the utilization factor of the switches, that is, the amount of output power that the amplifier generates for a given transistor stress [61]

$$c_{\rm pmr} = \frac{\eta_{\rm D} V_{\rm dc} I_{\rm dc}}{N V_{\rm ds p} I_{\rm ds rms}} \tag{2.9}$$

where  $\eta_{\rm D}$  is the switch drain efficiency. This equation is useful as a basic benchmark for comparing different resonant inverter topologies since a circuit with higher  $c_{\rm pmr}$  allows higher output power for the same power loss for the utilized switching devices. The switch utilization is compared in table 2.4 for selected resonant inverter topologies.

Table 2.4: Comparison of device stresses for resonant inverter topologies, assuming  $\eta_D=1$ . The 'half bridge' is the standard non-resonant ideal half bridge inverter with square switch voltage and current waveforms.

| Class                        | $V_{ m ds,p}$ | $I_{ m ds,rms}$ | N | $c_{ m pmr}$ |

|------------------------------|---------------|-----------------|---|--------------|

| Half bridge                  | 1             | 1.41            | 2 | 0.35         |

| D, VSRI                      | 1             | 1.57            | 2 | 0.32         |

| DE (D = 0.25)                | 1             | 3.14            | 2 | 0.16         |

| D, CSRI                      | 3.14          | 0.71            | 2 | 0.23         |

| E                            | 3.56          | 1.54            | 1 | 0.18         |

| $\mathrm{EF}_2 \ / \ \Phi_2$ | 2.1           | 1.9             | 1 | 0.25         |

| E, push-pull                 | 3.56          | 0.77            | 2 | 0.18         |

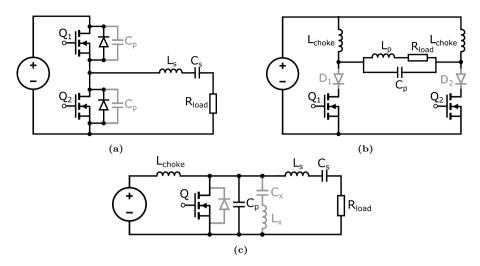

In systems where the semiconductor device cost is a critical factor, the  $c_{\rm pmr}$  may be the highest weighted optimization parameter in the inverter design, whereas in other applications the device cost may be dwarfed by e.g. cost of auxillary components or costs associated with reduced process uptime in the case of inverter failure. In these applications the reliability of the inverter, reduced EMI, or simplicity of the topology may be prioritized over switch utilization, and therefore determining the most suitable topology for a given application is not trivial. The circuit schematics corresponding to the topologies in table 2.4 are shown in Fig. 2.4 with descriptions below.

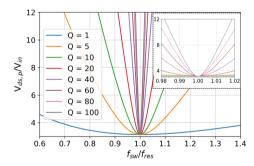

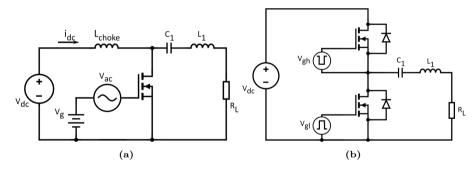

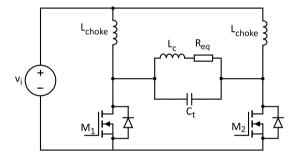

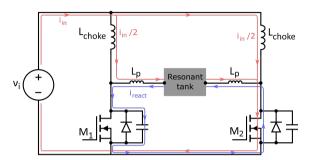

Class D VSRI, Class DE, and LLC The basic Class D voltage source resonant inverter (VSRI) is a standard half bridge circuit connected to a series resonant tank at the output as shown in Fig. 2.4a. The voltage across the switches is a square wave that is filtered by the resonant circuit to produce a sinusoidal output current for high quality factors  $Q = |P_{\rm react}|/P_{\rm real}$ . In this topology high  $c_{\rm pmr}$  is achieved for a duty cycle D = 0.5 (or slightly less to avoid shoot-through), but the energy stored in the switch output capacitance is discharged through the channel each switching cycle, leading to a switching loss that makes high frequency operation unfeasible. By using significant dead

Fig. 2.4: Ideal circuits schematics of load resonant inverters suitable for MHz operation. (a) Class D voltage source resonant inverter (VSRI) with series resonant tank and optional parallel switch capacitance, although in practice some switch capacitance is unavoidable for any inverter. (b) Class D current source resonant inverter (CSRI) with parallel resonant tank and optional series diode. (c) Class E inverter with optional antiparallel diode. The switch utilization in the topology may be improved by additional resonant components in the tank circuit.

time and operation with inductive load, and possibly including external switch capacitance, ZVS can be achieved by charging and discharging  $C_{\rm oss}$  using the load current. This reduces the  $c_{\rm pmr}$  of the circuit, but allows the switches to turn on with ZVS during body diode conduction to achieve high operating efficiency, and by tuning the reactive parameters, specific operating points can be found where the current through the switch is zero at turn on resulting in zero voltage derivative switching (ZVDS), which is the Class DE operating condition [62], [63].

An appealing variation of the VSRI, which is common in induction heating systems, is achieved by modifying the load network into a series-parallel resonant tank such that it becomes an LLC resonant inverter [47], [64]. This variation is attractive due to, compared to the VSRI, load short-circuit handling capability and in particular the current gain of the parallel resonance tank. As argued in section 2.1, the required current level in the induction coil is many hundreds of Amperes, which is much higher than is desirable to switch in a MHz inverter. By employing a parallel resonant tank with a large current gain, the required transistor current is dramatically reduced without using an impedance matching network with large transformation ratio [65].

The drawbacks of the topology for MHz frequencies are mainly related to the switching potential of the source terminal of the high side switch, as it means the driving signal must be level shifted for the high side switch while maintaining synchronization with the low side switch. This can be a challenge at high frequency and voltage levels, and therefore the high side driver must have a large common mode transient immunity [34]. These considerations, along with parasitic inductance in the switching loop and the fact that the required dead time may be a significant fraction of the switching period for high frequencies, can make practical implementations of this topology difficult for multi-MHz inverters [32], [66].

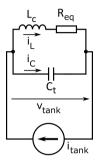

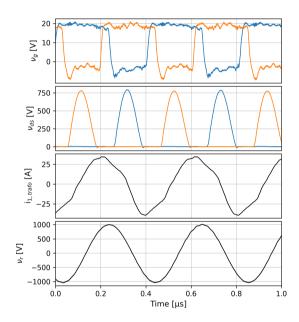

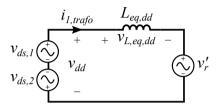

Class D CSRI The circuit of the Class D current source resonant inverter (CSRI) is shown in Fig 2.4b. As the dual of the VSRI, in the CSRI the current input to the tank network is a square wave and the voltage is a half sine. The large choke inductors ensure constant current draw from the source. The series diodes are optional when the switches are operated at the resonance frequency of the tank circuit [58], and the implication of including them in the topology is discussed in chapter 3. Like the VSRI, the CSRI has been extensively used for induction heating systems in the kHz regime. The CSRI naturally incorporates a parallel resonant tank with inherent current gain such that the switches ideally only carry the active current in the circuit. This leads to the conventional wisdom for induction heating systems that voltage source inverters are best suited for high impedance coils, while current source inverters are best suited for low impedance coils with high reactive current requirements [67], [68].

In terms of utilization factor, however, the CSRI is not the dual of the VSRI. This is because, from a device perspective and considering only conduction losses, the inverter power is limited by the *peak* of the transistor voltage, whereas it is mainly limited by the *RMS* of the transistor current through the heat dissipation capacity of the semiconductor devices. In spite of this, the topology is inherently attractive for high efficiency RF amplifiers as it has the important advantage for high frequency operation that any parasitic switch parallel capacitance is naturally absorbed into the resonant tank [69], [70]. In addition, since the gates of the both switching devices are referenced to the same potential, there is no high side switch in this topology, and it therefore requires no level shifting.

Class E and derivatives The Class E amplifier was invented as a high efficiency alterative to linear transistorized amplifiers [71]. The basic circuit is shown in Fig. 2.4c. In nominal operation, the circuit elements are precisely tuned for a specific frequency and load such that the conditions for both ZVS and ZVDS are satisfied:

$$\nu_{\rm ds}(2\pi) = 0,$$

$$\frac{\mathrm{d}\nu_{\rm ds}(\omega t)}{\mathrm{d}\omega t}\bigg|_{\omega t = 2\pi} = 0$$

(2.10)

Because there is no current running through the switch at the switching instant, the ZVDS condition can ensure that device losses are low even for slow or

mistimed gate signals [34]. In this condition, the antiparallel diode is not required.

Like the CSRI, the standard Class E resonant inverter includes a choke inductor and also incorporates the switch  $C_{\rm oss}$  in the resonant network. In addition, parasitic inductance at the input is absorbed by the choke inductor, and parasitic output inductance may be part of the resonant network. The topology includes only a single switch, which avoids problems with timing synchronization at high frequencies, and has the switch gate referenced to ground. Because both the voltage and current are shaped by resonant elements, the Class E inverter has no steep voltage or current flanks which helps to reduce electromagnetic interference (EMI), reduce stress on passive components, and may improve efficiency as steeper voltage transients can increase device operation losses [16], [72].

The largest disadvantage of the Class E topology is the low  $c_{\rm pmr}$ . There are several ways this property may be improved, e.g. by shaping the switch current in the Class E push-pull topology to approach the CSRI square wave current waveforms [61], or through topology modifications to the reactive elements such as Class  $EF_x$  [33], [73], or  $\Phi_2$  [66], [74]. These modifications may be applied to improve the switch utilization at the expense of increased complexity [73].

## 2.4 Inverter implementation challenges

For any choice of circuit topology, the combination of the requirements from table 2.2 results in a challenging inverter system design for this application. A brief overview of some of the most important challenges is given below.

## 2.4.1 Switching devices

The choice of switching device material, device technology, package, and voltage and current rating for high frequency applications is dependent on many factors, including operating frequency and environment, cost, and reliability and power density requirements [35], [41], [75]. Both SiC and GaN devices may be applied to resonant high frequency inverters for induction heating [19], [76], and in general to MHz converters as was shown in table 1.1. However, even without considering practical layouts and operating efficiencies, the maximum theoretical operating frequency of any semiconductor device is limited by its RC-network of  $R_{\rm g}$  and  $C_{\rm iss}$  as

$$f_{\text{max}} = \frac{1}{4R_{\text{g}}C_{\text{iss}}} \tag{2.11}$$

The maximum operating frequency for a device type is thus, in rough terms, inversely proportional to its voltage rating, as can be noted through the similarity between (2.11) and BHFFOM (2.6), but these parameters are highly

dependent on the intended application regime of the designed device. For high frequency and power applications, the device nonidealities therefore become vitally important. These considerations are evident by considering the selected WBG devices with low  $R_{\rm ds,on}$  in table 2.5, which also highlights the inherent challenge in high frequency operation of medium voltage devices.

**Table 2.5:** Characteristics and maximum theoretical operating frequency of selected WBG power devices, each with low on-state resistance for its voltage class. Expanded from Paper A.

| Device                       | Type                                    | $V_{ m br}$       | $R_{ m ds,on}$        | $C_{\mathrm{iss}}$ | $R_{\rm g}$   | $f_{ m max}$        |

|------------------------------|-----------------------------------------|-------------------|-----------------------|--------------------|---------------|---------------------|

| SCT3040KL                    | SiC MOSFET                              | $1200~\mathrm{V}$ | $40~\mathrm{m}\Omega$ | $1337~\mathrm{pF}$ | $7~\Omega$    | $27~\mathrm{MHz}$   |

| C2M0080170P                  | ${\rm SiC~MOSFET}$                      | $1700~\mathrm{V}$ | $80~\mathrm{m}\Omega$ | $2250~\mathrm{pF}$ | $2~\Omega$    | $56~\mathrm{MHz}$   |

| $\rm UJ3N120070K3S$          | $\operatorname{SiC}$ JFET               | $1200~\mathrm{V}$ | $70~\mathrm{m}\Omega$ | $985~\mathrm{pF}$  | $3.3~\Omega$  | $77~\mathrm{MHz}$   |

| GS66508T                     | $\operatorname{GaN}\operatorname{HEMT}$ | $650~\mathrm{V}$  | $50~\mathrm{m}\Omega$ | $260~\mathrm{pF}$  | $1.1~\Omega$  | $874~\mathrm{MHz}$  |

| $\mathrm{GPI65060DDK}$       | $\operatorname{GaN}\operatorname{HEMT}$ | $650~\mathrm{V}$  | $25~\mathrm{m}\Omega$ | $420~\mathrm{pF}$  | $2.18~\Omega$ | $273~\mathrm{MHz}$  |

| ${\rm G2R50MT33\text{-}CAL}$ | ${\rm SiC~MOSFET}$                      | $3300~\mathrm{V}$ | $50~\mathrm{m}\Omega$ | $7301 \mathrm{pF}$ | $1.2~\Omega$  | $29~\mathrm{MHz}$   |

| 10 kV die [77]               | SiC MOSFET                              | 10000 V           | N/A                   | $5800~\mathrm{pF}$ | $3.7~\Omega$  | $11.6~\mathrm{MHz}$ |

For MHz switching frequencies it is important to note the additional challenge that the charging and discharging of  $C_{\rm oss}$  is not lossless [41], [78]. Recent investigations reveal different loss mechanisms for different device types as well as varying scaling factors for frequency and voltage, and that for high efficiency soft switched MHz inverters these losses may cause significantly increased device stresses [16], [35], [79]. These losses are not considered quantitatively for the work in this thesis, but their existence is noted for derating considerations of selected switching devices.

## 2.4.2 Power scaling and paralleling

At the required power and voltage levels the paralleling of multiple switching devices is necessary both for medium voltage devices with low current rating and for a transformer-based solution utilizing lower voltage devices. Generally, barring difference between devices, higher power handling capability means larger total device capacitances, no matter if the power level reached through a few large-area devices or many smaller devices, as is also shown in table 2.5. From (2.11) a higher  $C_{\rm iss}$  limits the maximum switching frequency, but it also increases the required gate drive power and peak current levels to achieve fast switching speed of the power devices [80]. For ZVS resonant inverters, only the gate charge related to ZVS,  $Q_{\rm g,ZVS} \approx C_{\rm iss} \Delta V_{\rm g}$  is relevant [59]. Thus for a hard-switched gate driver controlling a soft switched power device, the required amount of driving power is at least

$$P_{\rm g} = C_{\rm iss} f_{\rm sw} \Delta V_{\rm g}^2 \tag{2.12}$$

Additional driver related losses are present in actual gate driving operation. As is evident from these considerations an increased power level results in a more difficult construction of a high-side driver with low coupling capacitance, particularly for higher operating voltage, since the gate driver power supply needs to supply significant power [81]. Thus from a gate driving point of view, it is therefore important to note the significant difference in driving power requirements for GaN HEMTs and SiC MOSFETs, as GaN devices require significantly less driving power. This is in part due to lower input capacitance, but mainly because these devices are typically operated at levels around 6 V [35]. Compared to the driving voltage of  $\Delta V_{\rm g}=20$  V that it typical for SiC MOSFETs, from (2.12) this alone accounts for more than 11 times higher driving losses for SiC than for GaN. Advanced gate driver structures such as resonant gate drives may be employed to improve the driving performance for high power FETs at MHz frequency [34], [39], [40].

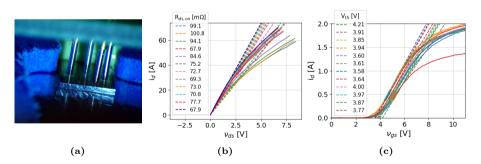

Another inherent challenge associated paralleling is the static and transient current sharing between dies, gate drive and power loop symmetries, and variance between devices. For the CPM2-1700-0080B SiC MOSFET devices used for most of the experimental work in this thesis (the bare die version of the C2M0080170P from table 2.5) [82], 12 dies are compared for output and transfer characteristics in Fig 2.5. In overall terms these measurements confirm the datasheet values, although a significant spread in the values of  $R_{\rm ds,on}$  is observed in Fig. 2.5b. The issue of static current balancing is fortunately largely resolved for devices exhibiting a positive temperature coefficient of the resistance [83]. In contrast to  $R_{\rm ds,on}$  the threshold voltage  $V_{\rm th}$  has a negative

Fig. 2.5: Curve tracing measurements for characterization of MOSFET dies. (a) Photograph of a bare die in the probing station. (b) Output characteristics and fitted  $R_{\rm ds,on}$  at  $\nu_{\rm gs}=20$  V and  $T_{\rm j}=25~{}^{\circ}C$ . As in the datasheet, the fit intersects the curves at  $i_{\rm d}=28$  A. (c) Transfer characteristics and fitted  $V_{\rm th}$  at  $T_{\rm j}=25~{}^{\circ}C$ . The datasheet threshold voltage is defined as the  $\nu_{\rm gs}$  value where the current level is 10 mA, requiring milli-ampere measurement precision. Here, we instead determine  $V_{\rm th}$  from the data in the linear region on the  $i_{\rm d}/\nu_{\rm gs}$  curve for  $\nu_{\rm ds}=1$ .  $V_{\rm th}$  is then the zero-current intercept of the fit of this data under the linear approximation for the drain current  $i_{\rm d}=k\left((\nu_{\rm gs}-V_{\rm th})\nu_{\rm ds}-\frac{\nu_{\rm ds}^2}{2}\right)$  [1], where k is a constant depending on the physical design and parameters of the MOSFET.

temperature coefficient, so the observed spread in Fig. 2.5c can potentially result in imbalance in the dynamic losses, particularly for elevated operation temperatures<sup>1</sup> [84]. A compact gate loop should be employed to avoid false turn on of the MOSFETs due to low threshold voltage [39], which can also reduce transient current sharing imbalance between devices with varying threshold voltage [85], [86].

#### 2.4.3 Switching stage layout

The layout of the switching stage and minimization of parasitic elements are highly relevant for realizing the potential of fast-switching WBG components [87]–[89]. Fast switching can be achieved both for systems using discrete packaged devices and power module designs, but in all cases require careful consideration current loops, coupling paths, and geometrical and device capacitances [36]. For discrete devices this is particularly true as the package may be the limiting factor for the reasonable operating frequency of the device rather than its own characteristics [35], [37], [38]. Different topologies have different inherent sensitivities to each parasitic element depending on inverter operation and application, and the optimization of the layout is therefore aimed at different parasitic parameters. As a relevant example, the VSRI is highly sensitive to inductance between the DC capacitor bank and the switches, while for the CSRI (as will be discussed further in 3.1.1) the output inductance of the switching stage is the parasitic element requiring most consideration [67].

Concerning the driving stage, it is well known that for any hard switched gate driver the circuit layout should be compact to facilitate fast transitions and minimize voltage overshoots on the power device gate. Considering an ideal step input to the gate circuit, the dynamic response of the gate voltage may be estimated from [77], [90]

$$L_{\rm g} = \frac{C_{\rm iss}R_{\rm g}^2}{4\zeta^2} \tag{2.13}$$

where  $R_{\rm g}$  is the gate resistance and  $\zeta$  is the damping factor. For  $\zeta=1$  a critically damped response is achieved, so (2.13) limits the gate loop inductance in relation to the power device parameters. For fast switching devices this consideration competes with (2.11), and as the allowed inductance scales with the square root of  $R_{\rm g}$  which is in parallel for each device, achieving a low enough inductance to avoid voltage overshoot can be a significant challenge for paralleled power devices.

In addition, it is not only the compactness of the loops that is necessary to consider, but for paralleled devices achieving symmetry in gate- and power loops to best utilize the device ratings of each device and promote equal transient

<sup>&</sup>lt;sup>1</sup>The temperature dependence of the bare dies was similarly confirmed by curve tracing, where no significant deviation from the datasheet values was found.

current sharing is also highly important [39], [86]. This is particularly true at high switching frequency where any transient imbalance may be more critical [83].

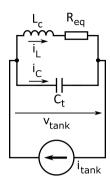

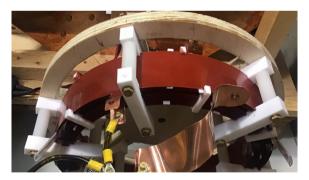

#### 2.5 Resonant tank

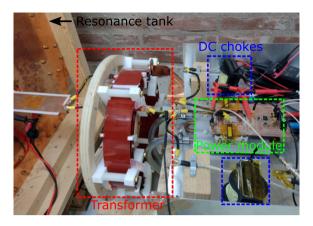

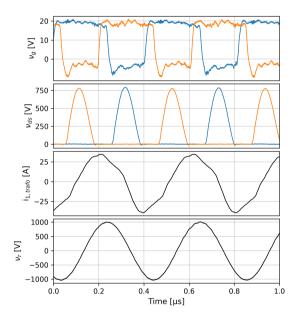

Experimental testing of the developed inverters in a realistic environment is an important part of validating the technology in a relevant setting. Therefore, an experimental setup with high power and voltage capability was constructed to emulate a real FZ process, with a resonant tank system based on similar components to those in vacuum-tube generators in use for FZ processing.

The induction coil is a specialized component that closely mimics an operational FZ coil, and a steel load was used in place of molten Si due to the similar resistivities of these materials. To increase the work coil current a compensating capacitor bank was added to form a parallel resonant tank. Vacuum capacitors were chosen due to their very low ESR and their ability to handle many hundreds of amperes and several kilovolts. The drawback of these components is their large size making compact resonance loops difficult to construct, which due to the high operating frequency can limit the voltage at the coil terminals and thus lower the power delivered to the load at a given capacitor voltage as described in section 2.1.

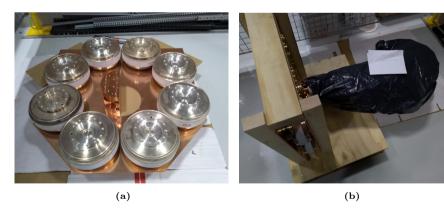

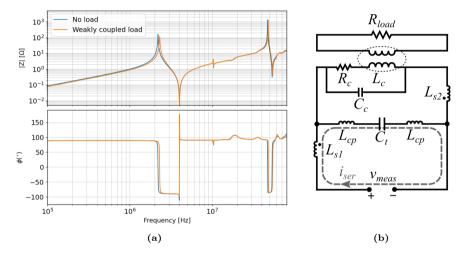

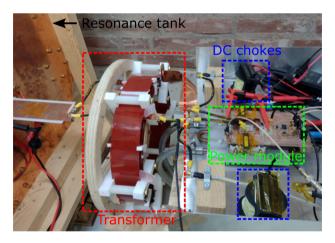

The constructed resonant tank is shown in Fig 2.6. As is shown in Fig. 2.6a the vacuum capacitors are arranged in a circular pattern where the inverter power module output terminals are to be connected on the left side of the capacitor bank in Fig. 2.6b and the induction coil is on the right.

Fig. 2.6: Photographs of the resonant tank, with (a) the capacitor bank with 8 vacuum capacitors in parallel for a total capacitance of 40 nF and (b) the complete resonant tank including proprietary induction coil mounted in a wooden chassis.

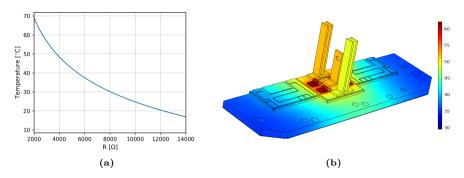

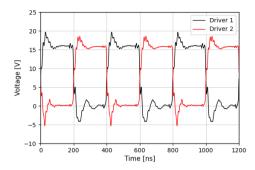

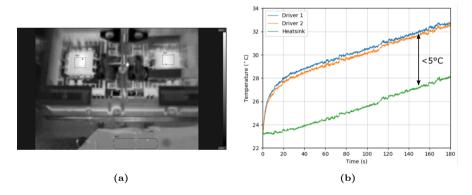

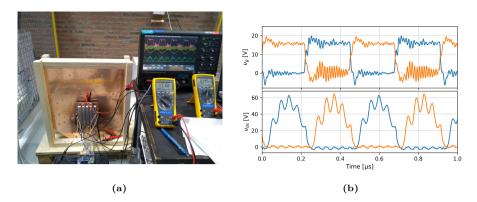

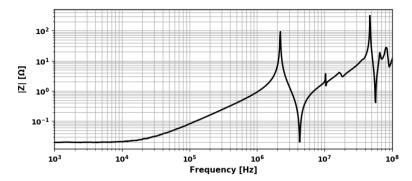

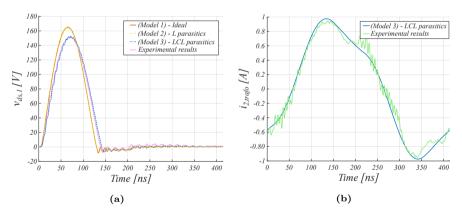

The circular shape is due to the importance of the resonance loop being