### **Aalborg Universitet**

### Multi-Sampled Current Control of Grid-Connected Voltage Source Converters

He, Shan

DOI (link to publication from Publisher): 10.54337/aau/485238703

Publication date: 2022

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

He, S. (2022). *Multi-Sampled Current Control of Grid-Connected Voltage Source Converters*. Aalborg Universitetsforlag. https://doi.org/10.54337/aau/485238703

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

# MULTI-SAMPLED CURRENT CONTROL OF GRID-CONNECTED VOLTAGE SOURCE CONVERTERS

### BY SHAN HE

**DISSERTATION SUBMITTED 2022**

# MULTI-SAMPLED CURRENT CONTROL OF GRID-CONNECTED VOLTAGE SOURCE CONVERTERS

by

Shan He

AAU Energy

Aalborg University, Denmark

Dissertation submitted April, 2022

Dissertation submitted: May 2022

PhD supervisor: Professor Frede Blaabjerg

Aalborg University, Denmark

Assistant PhD supervisor: Associate Professor Dao Zhou

Aalborg University, Denmark

Professor Xiongfei Wang Aalborg University, Denmark

PhD committee: Associate Professor Florin Iov

Professor Yaow-Ming Chen Director Norbert Hanigovszki

Faculty of Engineering and Science, Aalborg University

PhD Series:

AAU Energy

Department:

ISSN (online): 2446-1636

ISBN (online): 978-87-7573-907-3

Published by:

**Aalborg University Press**

Kroghstræde 3

DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Shan He

Printed in Denmark by Stibo Complete, 2022

# **CURRICULUM VITAE**

Shan He received the B.S. degree in Electrical Engineering from Northeast Electric Power University, Jilin, China, in 2015, and the M.S. degree in Electrical Engineering from Zhejiang University, Hangzhou, China, in 2018. He was a visiting researcher with RWTH Aachen, University, Aachen, Germany, from October to December 2021. He is currently pursuing a Ph.D. degree in Power Electronics at Aalborg University, Aalborg, Denmark. His research interests include grid-connected voltage source converters, especially in multi-sampling control.

# **ENGLISH SUMMARY**

Grid-connected voltage source converter (VSC) is the key interface between the renewable energy sources and the power grid, and pulse width modulation (PWM) based digital control has been the most commonly used method due to its flexibility, adaptability, and robustness. Especially, the sampling frequency is usually set to one or two times larger than the switching frequency to acquire the average value of voltage/current in VSCs, which are so-called single-sampling or double-sampling control. As the performance/price ratio of microprocessors increased in the past years, multi-sampling control gradually attracts attention where the sampling rate is higher than two. When using multi-sampling, in addition to the average voltage/current value, the switching ripple can also be sampled, which is the key distinction from regular sampling. Hence, how to fully employ the potential benefits from multi-sampling to achieve robust control of grid-connected converters is of interest.

First, a control delay is introduced in the PWM process of the VSCs, which will limit the control bandwidth design and even the stabilization of the VSCs. Multisampling PWM can effectively reduce the control delay, however, the internal mechanism of multi-sampling PWM is still not fully investigated. Second, with the large-scale integration of renewable energy sources, the grid admittance varies in a wide range, which may threaten the harmonic stability of the VSC-grid system. Because the control delay is critical to the stability, how to apply the multi-sampling PWM to further enhance the stability is worth to be investigated. Third, to get the most out of multi-sampling technology, the multi-sampled switching ripple can be used to estimate some additional states and parameters in the controlled VSCs. Hence, multi-sampling-based condition monitoring is of interest to be studied.

To cope with the aforementioned issues, this Ph.D. project first graphically analyzes the connection between the multi-sampling PWM and the double-sampling PWM, based on which, the grid-side current will be distorted by the aliased low-order harmonics and the multi-sampled switching ripple is the main reason. Then, the related anti-aliasing filters are proposed to remove the sampled switching ripple while the introduced phase lag is low. Further, how to select the sampling rate for the single-phase H-bridge VSCs and the three-phase interleaved VSCs is discussed.

As an extension of the admittance shaping, the passivity-based control is a promising solution to tackle the instability challenges in the VSC-grid system. Specifically, if the VSC output admittance is passive, the stable operation can be secured regardless of the grid admittance. Based on multi-sampling with anti-aliasing filters, the related passivity-based damping strategies are proposed considering inverter-side current control or grid-side current control. To further optimize the control delay, a multi-sampling-based real-time-update current control is proposed where the anti-aliasing filters are not required.

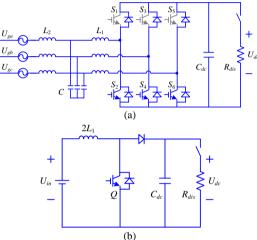

By utilizing the multi-sampled current data, a grid voltage estimator is proposed, which can help to reduce the cost of voltage sensors and also work as a backup under

a voltage sensor fault. To address the transients during start-up, a soft start-up method is proposed where the VSC is controlled as a boost converter. On the other hand, based on the multi-sampled voltage data, a grid impedance estimator is proposed for a three-phase interleaved VSC under an inductive grid.

The findings of this Ph.D. thesis have improved the application of multi-sampling technology on grid-connected VSCs.

### **DANSK RESUME**

Grid-connected voltage source converter (VSC) er nøglegrænsefladen mellem de vedvarende energikilder og elnettet, og pulsbreddemodulation (PWM) baseret digital kontrol har været den mest almindeligt anvendte metode på grund af dens fleksibilitet, tilpasningsevne og robusthed. Specielt er samplingsfrekvensen normalt indstillet til en eller to gange større end omskiftningsfrekvensen for at opnå den gennemsnitlige værdi af spænding/strøm i VSC'er, som er såkaldt single-sampling eller double-sampling kontrol. Efterhånden som mikroprocessorernes ydeevne/pris-forhold steg i de seneste år, tiltrækker multi-sampling-kontrol gradvist opmærksomhed, hvor samplingsraten er højere end to. Ved brug af multi-sampling kan ud over den gennemsnitlige spænding/strømværdi også samples switching ripple, hvilket er den vigtigste forskel fra almindelig sampling. Derfor er det interessant, hvordan man fuldt ud udnytter de potentielle fordele ved multi-sampling for at opnå robust kontrol af nettilsluttede konvertere.

Først introduceres en kontrolforsinkelse i VSC'ernes PWM-proces, som vil begrænse kontrolbåndbreddedesignet og endda stabiliseringen af VSC'erne. Multisampling PWM kan effektivt reducere kontrolforsinkelsen, men den interne mekanisme for multi-sampling PWM er stadig ikke fuldt ud undersøgt. For det andet, med den omfattende integration af vedvarende energikilder, varierer netadgang i et bredt område, hvilket kan true den harmoniske stabilitet af VSC-netsystemet. Fordi kontrolforsinkelsen er kritisk for stabiliteten, er det værd at undersøge, hvordan man anvender multi-sampling PWM for yderligere at forbedre stabiliteten. For det tredje, for at få mest muligt ud af multi-sampling-teknologien, kan den multi-samplede switching ripple bruges til at estimere nogle yderligere tilstande og parametre i de kontrollerede VSC'er. Derfor er multi-sampling-baseret tilstandsovervågning af interesse at blive undersøgt.

For at klare de førnævnte problemstillinger har denne ph.d. Projektet analyserer først grafisk forbindelsen mellem multi-sampling-PWM og dobbelt-sampling-PWM, baseret på hvilken grid-side-strømmen vil blive forvrænget af de aliaserede lavordens harmoniske, og den multi-samplede switching ripple er hovedårsagen. Derefter foreslås de relaterede anti-aliasing-filtre for at fjerne den samplede switch-rippel, mens den indførte faseforsinkelse er lav. Yderligere diskuteres, hvordan man vælger prøvetagningshastigheden for de enkeltfasede H-bro VSC'er og de trefasede interleaved VSC'er.

Som en forlængelse af adgangsudformningen er den passivitetsbaserede kontrol en lovende løsning til at tackle ustabilitetsudfordringerne i VSC-netsystemet. Specifikt, hvis VSC-udgangsadmittansen er passiv, kan den stabile drift sikres uanset netadmittansen. Baseret på multi-sampling med anti-aliasing-filtre foreslås de relaterede passivitetsbaserede dæmpningsstrategier under hensyntagen til strømstyring på invertersiden eller strømstyring på netsiden. For yderligere at optimere kontrolforsinkelsen foreslås en multi-sampling-baseret real-time-opdatering af strømstyring, hvor anti-aliasing-filtre ikke er påkrævet.

Ved at udnytte de multi-samplede strømdata foreslås en netspændingsestimator, som kan hjælpe med at reducere omkostningerne til spændingssensorer og også fungere som backup under en spændingssensorfejl. For at imødegå transienterne under opstart foreslås en blød opstartsmetode, hvor VSC'en styres som en boostkonverter. På den anden side, baseret på de multi-samplede spændingsdata, foreslås en netimpedansestimator for en trefaset interleaved VSC under et induktivt net.

Resultaterne af denne ph.d. afhandling har forbedret anvendelsen af multi-sampling teknologi på nettilsluttede VSC'er.

### **ACKNOWLEDGEMENTS**

The work presented in this thesis is a summary of the Ph.D. project "Multi-Sampled Current Control of Grid-Connected Voltage Source Converters", which was implemented at AAU Energy, Aalborg University. This Ph.D. project is supported by China Scholarship Council, Otto Mønsteds Fund as well as Aalborg University. I would like to appreciate the above-mentioned institutions.

My biggest thanks should go to my main supervisor, Prof. Frede Blaabjerg. During the past three-year Ph.D. study journey, he has provided me with research opportunities, shared the research experience, and guided me step by step to the final goal. His pragmatic and serious attitude toward scientific research and life experiences inspired me, and this will be valuable during my entire life.

At the same time, I would like to thank my co-supervisor, Associate Prof. Dao Zhou and Prof. Xiongfei Wang, for all of their time and energy with my research. I am very grateful to them for tolerating my limitations and encouraging me to keep moving forward at all time.

I would also like to thank Prof. Rik De Doncker from RWTH Aachen University, Germany and Assistant Prof. Zhiqing Yang from Hefei University of Technology, China for providing me with their external cooperation and valuable comments on my research work. I want to take this opportunity to thank my colleagues in E.ON Energy Research Center for their help and support during my study aboard.

I would like to thank the assessment committee for the Ph.D. defense. I would like to further extend my appreciation to all my colleagues at AAU Energy, Aalborg University for their support during my Ph.D. study.

Finally, my sincerest gratitude goes to my family in China for their endless love, continuous support, and full understanding. Most importantly, I would like to acknowledge the efforts of my wife Xin Sui, and I cannot reach this point without her endless patience, companionship, and love in daily life.

Shan He

Aalborg University, April, 2022

# TABLE OF CONTENTS

| Curriculum Vitae                                                   | iii |

|--------------------------------------------------------------------|-----|

| English Summary                                                    | v   |

| Dansk Resume                                                       | vii |

| Acknowledgements                                                   | ix  |

| Table of contents                                                  | xi  |

| Part I. Report                                                     | 1   |

| Chapter 1. Introduction                                            | 3   |

| 1.1. Background                                                    | 3   |

| 1.1.1. Multi-Sampling PWM                                          | 7   |

| 1.1.2. Passivity Based Current Control                             | 8   |

| 1.1.3. Condition Monitoring                                        | 9   |

| 1.2. Project Objectives and LimitatIons                            | 10  |

| 1.2.1. Project Objectives                                          | 10  |

| 1.2.2. Project Limitations                                         | 11  |

| 1.3. Thesis Outline                                                | 12  |

| 1.4. List of Publications                                          | 12  |

| Chapter 2. Multi-Sampling PWM Analysis and Aliasing Suppression    | 15  |

| 2.1. Background                                                    | 15  |

| 2.2. Aliasing Analysis for Multi-Sampling PWM                      | 16  |

| 2.2.1. Four-Sampling PWM                                           | 16  |

| 2.2.2. Eight-Sampling PWM                                          | 17  |

| 2.3. Improved Repetitive Filter                                    | 18  |

| 2.4. Case Studies                                                  | 22  |

| 2.5. Summary                                                       | 25  |

| Chapter 3. Passivity Enhancement With Inverter-Side Current Contro | 127 |

| 3.1. Background                                                    | 27  |

| 3.2. Passivity Analysis of Current Controllers                     | 28  |

| 3.3. Passivity Enhancement                                         | 34  |

| 3.4. Case Studies                                                  | 40  |

| 3.5. Summary                                                                          | 42 |

|---------------------------------------------------------------------------------------|----|

| Chapter 4. Passivity Enhancement With Grid-side Current Control                       | 45 |

| 4.1. Background                                                                       | 45 |

| 4.2. Passivity Analysis of Current Controller                                         | 46 |

| 4.3. Passivity Enhancement                                                            | 49 |

| 4.4. Case Studies                                                                     | 51 |

| 4.5. Summary                                                                          | 53 |

| Chapter 5. Enhanced Real-Time-Update Current Control Using Multi-<br>Sampling Concept | 55 |

| 5.1. Background                                                                       | 55 |

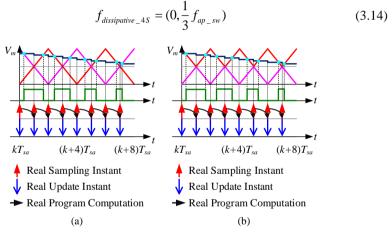

| 5.2. Conventional Real-Time-Update PWM                                                | 56 |

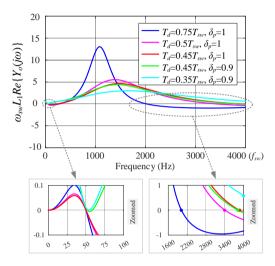

| 5.3. Enhanced Real-Time-Update Current Control                                        | 60 |

| 5.4. Case Studies                                                                     | 62 |

| 5.5. Summary                                                                          | 63 |

| Chapter 6. Control of Interleaved Three-Phase Inverters With Grid Impe                |    |

| 6.1. Background                                                                       | 65 |

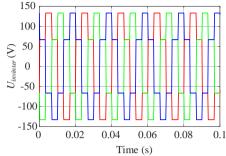

| 6.2. Sampling Rate Selection                                                          | 66 |

| 6.3. Controller Design                                                                | 67 |

| 6.4. Grid Impedance Estimation                                                        | 70 |

| 6.5. Case Studies                                                                     | 72 |

| 6.6. Summary                                                                          | 75 |

| Chapter 7. Grid Voltage Sensorless Control Using Multi-Sampling                       | 77 |

| 7.1. Background                                                                       | 77 |

| 7.2. Grid Voltage Estimation                                                          | 78 |

| 7.3. Controller Design                                                                | 80 |

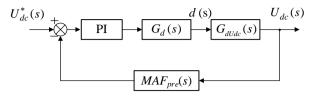

| 7.4. Soft Start-Up                                                                    | 82 |

| 7.5. Case Studies                                                                     | 85 |

| 7.6. Summary                                                                          | 90 |

| Chapter 8. Conclusion and Future Work                                                 | 93 |

| 8.1. Summary                                                                          | 93 |

| 8.2. Main Contributions                                                                                           | 94  |

|-------------------------------------------------------------------------------------------------------------------|-----|

| 8.3. Outlook                                                                                                      | 94  |

| BiblIography                                                                                                      | 97  |

| Part II. Papers                                                                                                   | 103 |

| [J1] A Review of Multi-Sampling Techniques in Power Electronics<br>Applications                                   | 105 |

| [J2] Aliasing Suppression of Multi-Sampled Current Controlled LCL-Fil Inverters                                   |     |

| [J3] Passivity Based Multi-Sampled Current Control of LCL-Filtered Gr<br>Connected Inverters                      |     |

| [J4] Line Voltage Sensorless Control of Grid-Connected Inverters Using Multisampling                              |     |

| [C1] Robust Passivity Enhancement for LCL-Filtered Grid-Following In with Multi-Sampled Grid-Side Current Control |     |

| [C2] Switching harmonics suppression of single-loop multi-sampling congrid-connected inverter                     |     |

| [C3] Enhanced Real-Time-Update Current Control Using Multi-Samplin Concept                                        | _   |

| [C4] Multisampling control of two-cell interleaved three-phase grid-conneconverters                               |     |

| [C5] Multisampling based grid impedance estimation for two-cell interleathree-phase inverters                     |     |

# LIST OF FIGURES

| Fig. 1.1. Applications and demands of VSCs in power system                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.2. Typical control structure of a three-phase VSC. Source: [J1]4                                                                                                                                                                                           |

| Fig. 1.3. Representation of VSC-grid system                                                                                                                                                                                                                       |

| <b>Fig. 1.4.</b> Regular PWM in digital control. (a) Single-sampling, (b) Double-sampling. Source: [J2]                                                                                                                                                           |

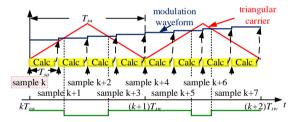

| Fig. 1.5. Multi-sampling PWM. Source: [J2]                                                                                                                                                                                                                        |

| <b>Fig. 1.6.</b> Four-sampling PWM for a single-phase VSC (Blue: modulation signal, Red: carrier). Source: [J1]                                                                                                                                                   |

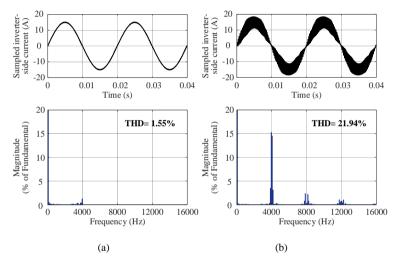

| <b>Fig. 1.7.</b> Sampled inverter-side current for a single-phase VSC ( $f_{sw}$ =2 kHz). (a) Four-sampling ( $f_{sa}$ =8 kHz), (b) Sixteen-sampling ( $f_{sa}$ =32 kHz). Source: [J3] 8                                                                          |

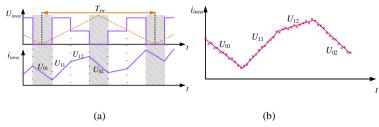

| <b>Fig. 1.8.</b> Voltage vectors and currents for a three-phase PWM. (a) $U_{inv\alpha}$ and $i_{inv\alpha}$ within a switching period, (b) Estimated current slope. Source: [J4] 10                                                                              |

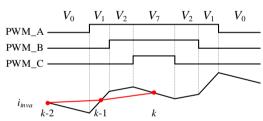

| Fig. 1.9. Measurement instants for grid impedance estimation. Source: [J1] 10                                                                                                                                                                                     |

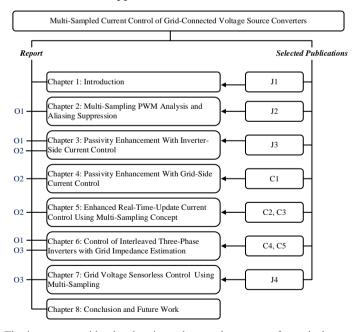

| <b>Fig. 1.10.</b> Thesis structure with related topics and research outcomes for each chapter; where "O" denotes objective, while "J" and "C" refer to a journal or conference publication, respectively.                                                         |

| <b>Fig. 2.1.</b> Single-loop multi-sampling control with inverter-side current feedback (RF: repetitive filter). Source: [J2]                                                                                                                                     |

| <b>Fig. 2.2.</b> Intersection analysis for four-sampling PWM (Blue: modulation signal, Red: carrier). Source: [J2]                                                                                                                                                |

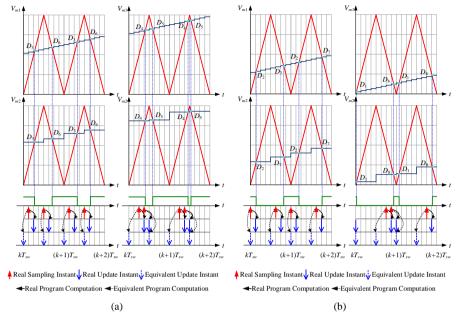

| <b>Fig. 2.3.</b> The mechanism analysis for four-sampling PWM. (a) Positive half cycle of modulation signal, (b) Negative half cycle of modulation signal. Source: [J2].                                                                                          |

| <b>Fig. 2.4.</b> The mechanism analysis for eight-sampling PWM. (a) Positive half cycle of modulation signal, (b) Negative half cycle of modulation signal (Blue: modulation signal, Red: carrier). Source: [J2]                                                  |

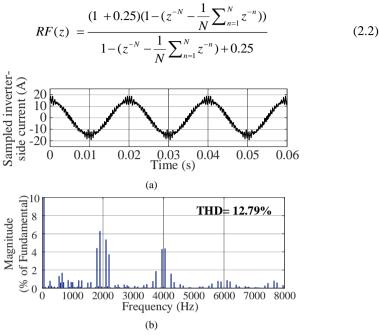

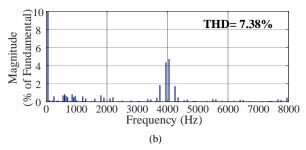

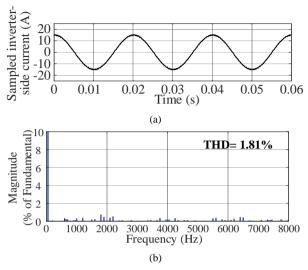

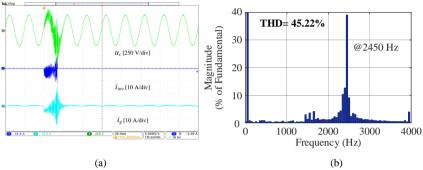

| <b>Fig. 2.5.</b> The eight-sampled inverter-side current without anti-aliasing filters. (a) Sampled inverter-side current waveform, (b) Current spectrum. Source: [J2] 19                                                                                         |

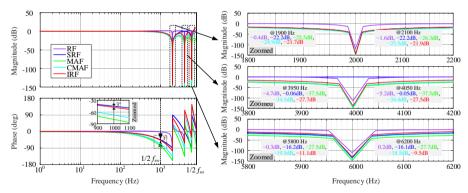

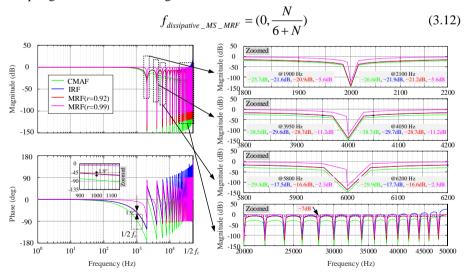

| <b>Fig. 2.6.</b> The bode diagram of the repetitive filters using eight-sampling (RF: repetitive filter, SRF: simplified repetitive filter, MAF: moving average filter, CMAF: compromised moving averaging filter, IRF: improved repetitive filter). Source: [J2] |

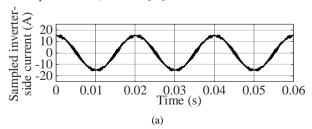

| <b>Fig. 2.7.</b> The eight-sampled inverter-side current with a simplified repetitive filter. (a) Sampled inverter-side current waveform, (b) Current spectrum. Source: [J2]                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Fig. 2.8.</b> The eight-sampled inverter-side current with an improved repetitive filter. (a) Sampled inverter-side current waveform, (b) Current spectrum. Source: [J2]                                                          |

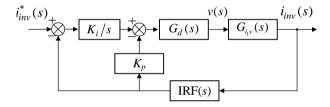

| <b>Fig. 2.9.</b> Model of the single-loop inverter-side current control using multisampling. Source: [J2]                                                                                                                            |

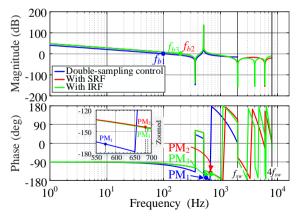

| <b>Fig. 2.10.</b> Bode diagram of the inner loop using double-sampling and eight-sampling (SRF: simplified repetitive filter, IRF: improved repetitive filter). Source: [J2]                                                         |

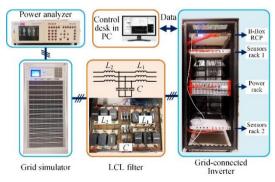

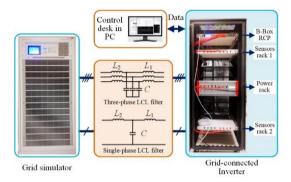

| Fig. 2.11. Three-phase grid-connected VSC prototype. Source: [J2]                                                                                                                                                                    |

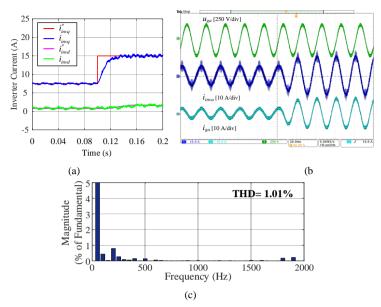

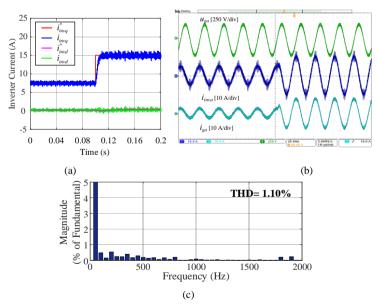

| <b>Fig. 2.12.</b> Experimental results when using double-sampling control. (a) Step response, (b) Analogue inverter-side and grid-side current, (c) THD of analog grid-side current. Source: [J2]                                    |

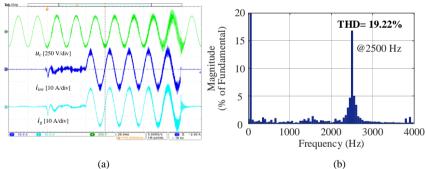

| <b>Fig. 2.13.</b> Experimental results when using eight-sampling control without antialiasing filters. (a) Step response, (b) Analogue inverter-side and grid-side current, (c) THD of analog grid-side current. Source: [J2]        |

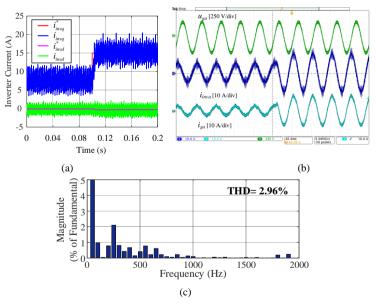

| <b>Fig. 2.14.</b> Experimental results when using eight-sampling control with a simplified repetitive filter. (a) Step response, (b) Analogue inverter-side and grid-side current, (c) THD of analog grid-side current. Source: [J2] |

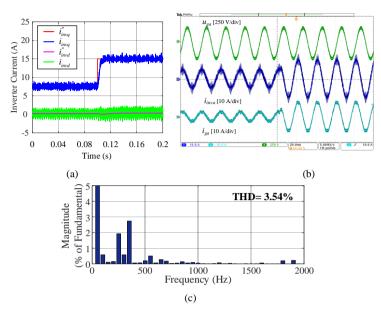

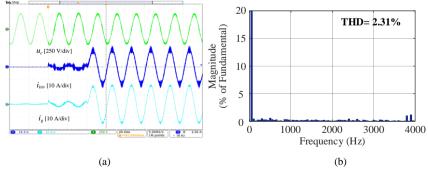

| <b>Fig. 2.15.</b> Experimental results when using eight-sampling control with an improved repetitive filter. (a) Step response, (b) Analogue inverter-side and grid-side current, (c) THD of analog grid-side current. Source: [J2]  |

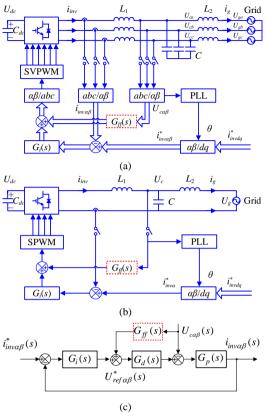

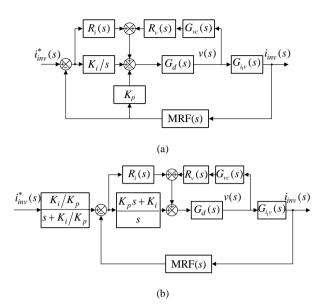

| <b>Fig. 3.1.</b> Current control diagram of a single/three-phase grid-connected VSC. (a) Three-phase control diagram, (b) Single-phase control diagram, (c) General current control model. Source: [J3]                              |

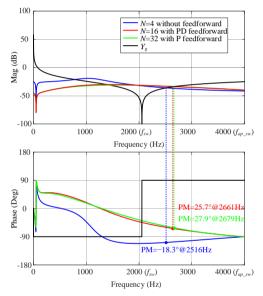

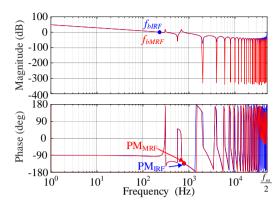

| <b>Fig. 3.2.</b> Bode diagram of repetitive filters with a high sampling rate (CMAF: compromised moving average filter, IRF: improved repetitive filter, MRF: modified repetitive filter). Source: [J4]                              |

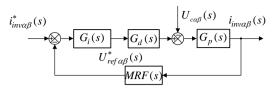

| <b>Fig. 3.3.</b> Single-loop control diagram using multi-sampling (MRF: modified repetitive filter). Source: [J3]                                                                                                                    |

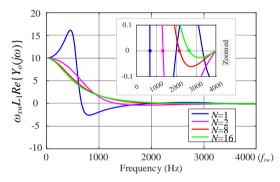

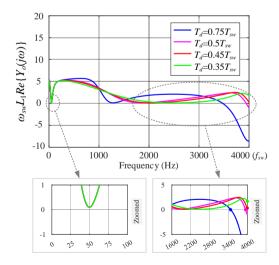

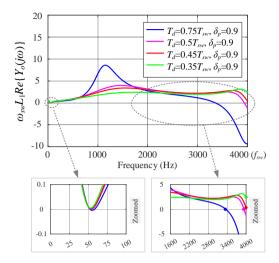

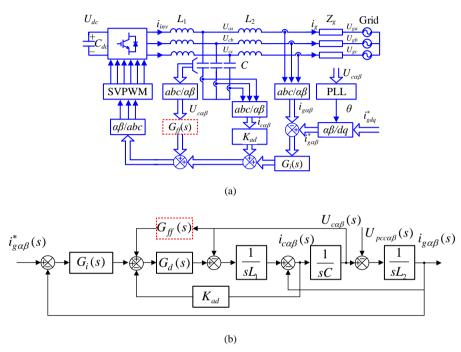

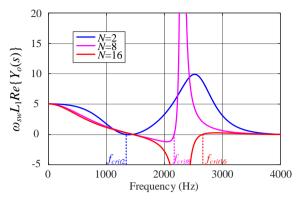

| <b>Fig. 3.4.</b> Real part of VSC output admittance for a single-loop current controller using regular sampling ( $N=1$ , 2), eight-sampling ( $N=8$ ), and sixteen-sampling ( $N=16$ ). Source: [J3]                                |

| <b>Fig. 3.5.</b> Four-sampling PWM for a single-phase VSC. (a) Seen from a preset switching frequency perspective, (b) Seen from an apparent switching frequency perspective. Source: [J3]                                           |

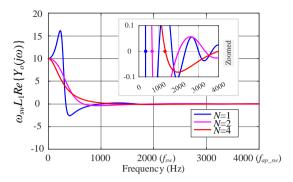

| <b>Fig. 3.6.</b> Real part of VSC output admittance for a single-loop inverter-side current controller using regular sampling ( <i>N</i> =1, 2) and four-sampling ( <i>N</i> =4) for a single-phase inverter. Source: [J3]            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Fig. 3.7.</b> Real part of VSC output admittance with proportional feedforward and different control delays. Source: [J3]                                                                                                          |

| <b>Fig. 3.8.</b> Real part of VSC output admittance with derivative feedforward and different control delays. Source: [J3]                                                                                                            |

| <b>Fig. 3.9.</b> Real part of VSC output admittance with proportional-derivative feedforward and different control delays. Source: [J3]                                                                                               |

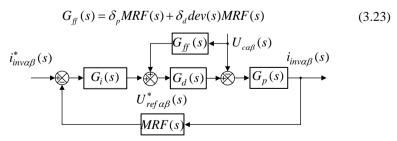

| <b>Fig. 3.10.</b> Multi-sampled inverter-side current control diagram with filter capacitor voltage feedforward (MRF: modified repetitive filter). Source: [J3] 36                                                                    |

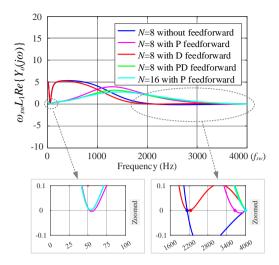

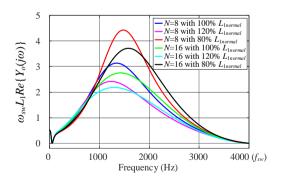

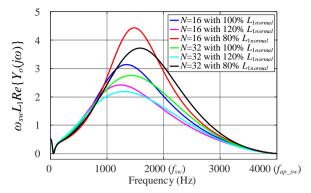

| <b>Fig. 3.11.</b> Real part of VSC output admittance with and without filter capacitor voltage feedforward based on different sampling rates for three-phase inverters. Source: [J3]                                                  |

| <b>Fig. 3.12.</b> Robustness analysis of proposed method against $\pm 20\%$ inverter-side inductance variation ( $N=8$ with PD feedforward or $N=16$ with P feedforward). Source: [J3].                                               |

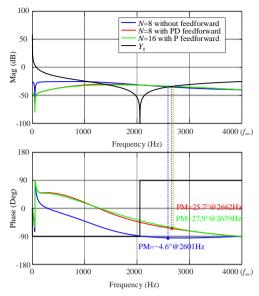

| <b>Fig. 3.13.</b> Output admittance for a multi-sampled three-phase VSC with and without the filter capacitor voltage feedforward. Source: [J3]                                                                                       |

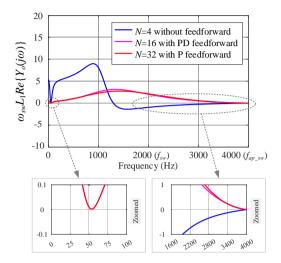

| <b>Fig. 3.14.</b> Real part of output admittance for four-sampling control, sixteen-sampling control with proportional-derivative feedforward, and thirty two-sampling control with proportional voltage feedforward. Source: [J3] 39 |

| <b>Fig. 3.15.</b> Robustness analysis of proposed method against ±20% inverter-side inductance variation (N=16 with PD feedforward or N=32 with P feedforward). Source: [J3]                                                          |

| <b>Fig. 3.16.</b> Output admittance for a multi-sampled single-phase HB inverter with and without the filter capacitor voltage feedforward. Source: [J3]                                                                              |

| Fig. 3.17. Single/three-phase grid-connected VSC prototype. Source: [J3] 41                                                                                                                                                           |

| <b>Fig. 3.18.</b> Experimental results for a three-phase VSC using <i>N</i> =8 without feedforward. (a) Inverter-side current and grid-side current, (b) Grid-side current harmonic spectrum. Source: [J3]                            |

| <b>Fig. 3.19.</b> Experimental results for a three-phase VSC using <i>N</i> =8 with proportional-derivative feedforward. (a) Inverter-side current and grid-side current, (b) Grid-side current harmonic spectrum. Source: [J3]       |

| <b>Fig. 3.20.</b> Experimental results for a single-phase VSC using <i>N</i> =4 without feedforward. (a) Inverter-side current and grid-side current, (b) Grid-side current harmonic spectrum. Source: [J3]                           |

| <b>Fig. 3.21.</b> Experimental results for a single-phase VSC using <i>N</i> =16 with proportional-derivative feedforward. (a) Inverter-side current and grid-side current, (b) Grid-side current harmonic spectrum. Source: [J3]                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

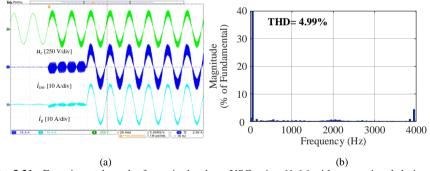

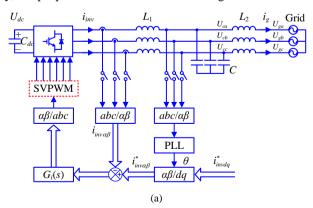

| <b>Fig. 4.1.</b> Diagram of a three-phase VSC with grid-side current feedback. (a) Three-phase control diagram, (b) Mathematic model. Source: [C1]                                                                                                                                                         |

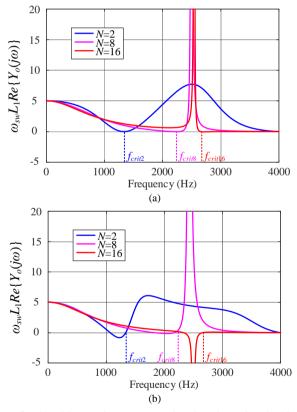

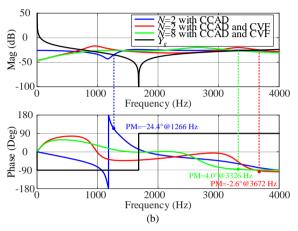

| <b>Fig. 4.2.</b> Passivity of $Y_o(s)$ for a single-loop grid-side current controller using double-sampling ( $N$ =2), eight-sampling ( $N$ =8), and sixteen-sampling ( $N$ =16) for three-phase inverters. Source: [C1]                                                                                   |

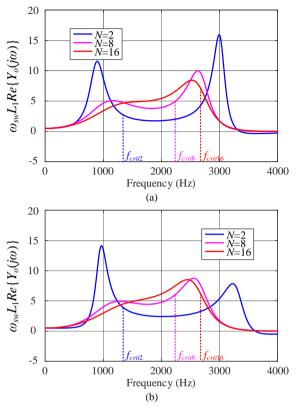

| <b>Fig. 4.3.</b> Passivity of $Y_o(s)$ with capacitor current active damping using double-sampling ( $N$ =2), eight-sampling ( $N$ =8), and sixteen-sampling ( $N$ =16) for three-phase inverters. (a) With nominal values of $L_1$ and $C$ , (b) With +20% unit deviation of $L_1$ and $C$ . Source: [C1] |

| <b>Fig. 4.4.</b> Passivity of $Y_o(s)$ with CCAD and CVF using double-sampling ( $N$ =2), eight-sampling ( $N$ =8), and sixteen-sampling ( $N$ =16) for three-phase inverters. (a) With nominal values of $L_1$ and $C$ , (b) With +20% unit deviation of $L_1$ and $C$ . Source: [C1]                     |

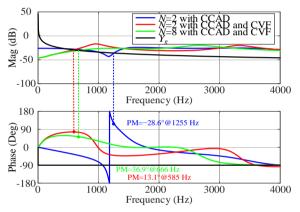

| <b>Fig. 4.5.</b> Bode plot of inverter output admittance with $+20\%$ unit deviation of $L_1$ and $C$ when $L_g$ =8 mH. (CCAD: capacitor current active damping, CVF: capacitor voltage feedforward) Source: [C1]                                                                                          |

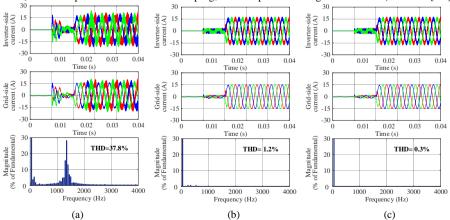

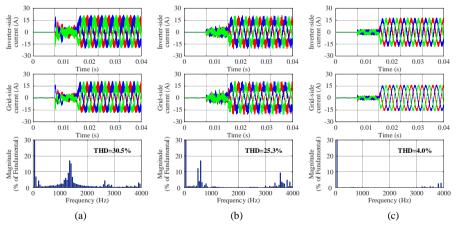

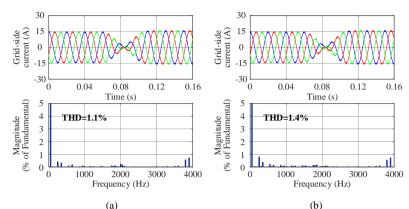

| <b>Fig. 4.6.</b> Simulation results under $+20\%$ deviation of $L_1$ and $C$ when $L_g$ =8 mH. (a) $N$ =2 with CCAD, (b) $N$ =2 with CCAD and CVF, (c) $N$ =8 with CCAD and CVF. (CCAD: capacitor current active damping, CVF: capacitor voltage feedforward) Source: [C1]                                 |

| <b>Fig. 4.7.</b> Bode plot of inverter output admittance with +20% unit deviation of $L_1$ and $C$ when $L_g$ =3 mH and $C_g$ =3 $\mu$ F. (CCAD: capacitor current active damping, CVF: capacitor voltage feedforward) Source: [C1]                                                                        |

| <b>Fig. 4.8.</b> Simulation results under +20% deviation of $L_1$ and $C$ when $L_g$ =3 mH and $C_g$ =3 $\mu$ F. (a) $N$ =2 with CCAD, (b) $N$ =2 with CCAD and CVF, (c) $N$ =8 with CCAD and CVF. (CCAD: capacitor current active damping, CVF: capacitor voltage feedforward) Source: [C1]               |

| <b>Fig. 5.1.</b> Single-loop control diagram of a three-phase VSC using inverter-side current feedback. (a) Diagram of single-loop control, (b) Mathematic model. Source: [C2]                                                                                                                             |

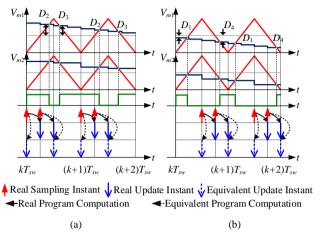

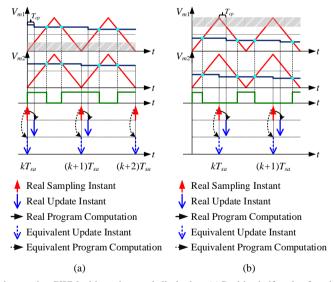

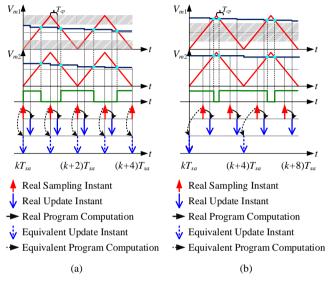

| <b>Fig. 5.2.</b> Single-valley-sampling real-time-upate PWM. (a) Without duty cycle limitation, (b) With duty cycle limitation. Source: [J1]                                                                                                                                                               |

| <b>Fig. 5.3.</b> Single-peak-sampling real-time-update PWM. (a) Without the duty cycle limitation, (b) With the duty cycle limitation. Source: [J1]                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                            |

| <b>Fig. 5.4.</b> Real-time-update PWM without duty cycle limitation. (a) Positive half cycle of modulation signal, (b) Negative half cycle of modulation signal. Source: [J1]                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

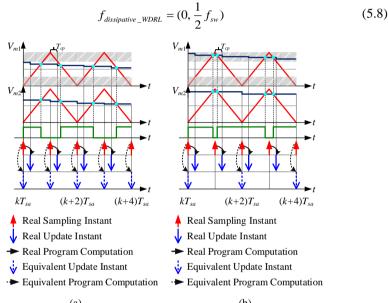

| <b>Fig. 5.5.</b> Double-sampling real-time update PWM. (a) Without the duty cycle limitation, (b) With the duty cycle limitation. Source: [C3]                                                                                                       |

| <b>Fig. 5.6.</b> Enhanced real-time-update PWM with double-sampling. (a) Sampling at Peak/valley point of carrier, (b) Sampling at middle point of carrier. Source: [C3].                                                                            |

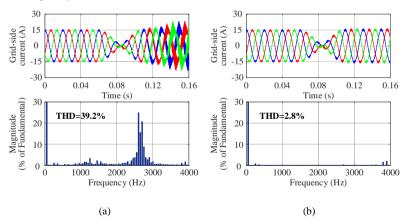

| <b>Fig. 5.7.</b> Simulation results of Case 1 (C=3 $\mu$ F and $f_i$ =2517 Hz). (a) Double-sampling real-time-update PWM, (b) Enhanced real-time-update PWM. Source: [C3].                                                                           |

| <b>Fig. 5.8.</b> Simulation results of Case 2 ( $C=6 \mu F$ and $f$ =1779 Hz). (a) Double-sampling real-time-update PWM, (b) Enhanced real-time-update PWM. Source: [C3]                                                                             |

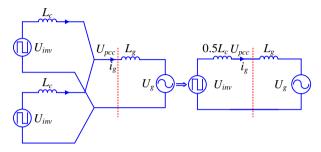

| <b>Fig. 6.1.</b> Current control diagram of an interleaved two-cell three-phase VSC. (a) PCC current control loop, (b) Circulating current control loop. Source: [C4] 66                                                                             |

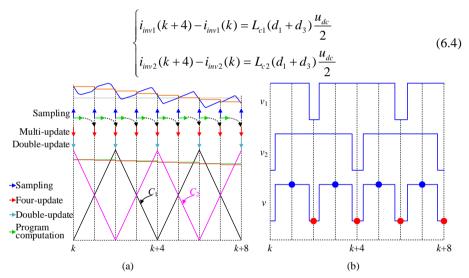

| <b>Fig. 6.2.</b> PWM process and sampling rate selection for two-cell interleaved three-phase VSCs. (a) Sampling and modulation, (b) Pulse pattern. Source: [C4] 67                                                                                  |

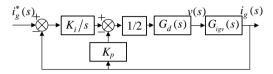

| Fig. 6.3. Model of PCC current control loop. Source: [C4]                                                                                                                                                                                            |

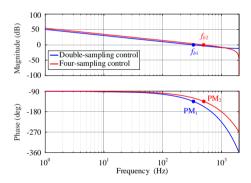

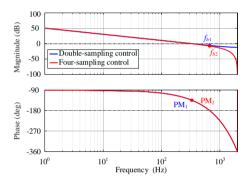

| <b>Fig. 6.4.</b> Bode diagram of the inner loop of PCC current control loop. Source: [C4]                                                                                                                                                            |

| <b>Fig. 6.5.</b> Model of the circulating current control loop. Source: [C4]                                                                                                                                                                         |

| Fig. 6.6. Bode diagram of circulating current control loop. Source: [C4] 69                                                                                                                                                                          |

| Fig. 6.7. Equivalent circuit for a two-cell interleaved VSC. Source: [C5] 70                                                                                                                                                                         |

| Fig. 6.8. Sampled grid voltage bias analysis. Source: [C5]                                                                                                                                                                                           |

| <b>Fig. 6.9.</b> Predicted VSC output voltage at the intersection point of the interleaved carriers. Source: [C5]                                                                                                                                    |

| <b>Fig. 6.10.</b> Grid impedance estimation results. (a) Estimated grid impedance without compensation, (b) Grid phase angle, (c) Estimated grid impedance with compensation. Source: [C5]                                                           |

| Fig. 6.11. Two-cell three-phase interleaved VSC prototype. Source: [C4] 73                                                                                                                                                                           |

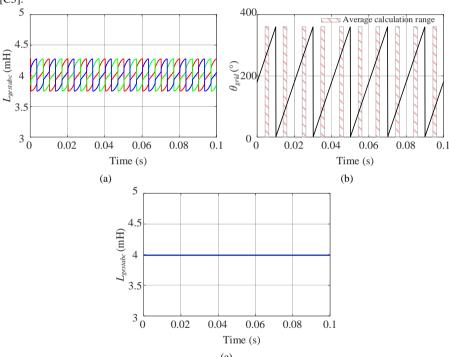

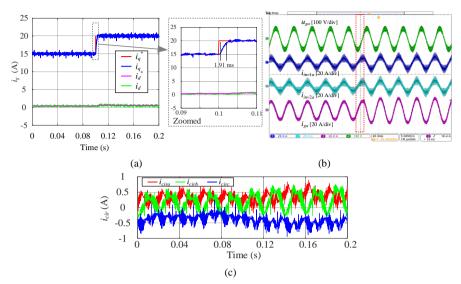

| <b>Fig. 6.12.</b> Experimental results when using double-sampling double-update control with circulating current suppression. (a) Step response, (b) converter-side currents and PCC currents, (c) Low frequency circulating currents. Source: [C4]. |

| <b>Fig. 6.13.</b> Experimental results when using four-sampling four-update control without circulating current suppression. (a) Step response, (b) Converter-side                                                                                   |

| currents and PCC currents, (c) Low frequency circulating currents. Source: [C4].                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                    |

| <b>Fig. 6.14.</b> Experimental results when using four-sampling double-update control with circulating current suppression. (a) Step response, (b) Converter-side currents and PCC currents, (c) Low frequency circulating currents. Source: [C4]                  |

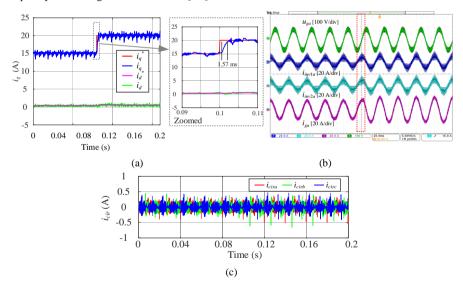

| <b>Fig. 6.15.</b> Grid impedance estimation results under a clear grid condition. (a) Inverter-side current and grid-side current, (b) Sampled PCC voltage and estimated grid impedance. Source: [C5]                                                              |

| <b>Fig. 6.16.</b> Grid impedance estimation results under a distorted grid condition (10% 5 <sup>th</sup> and 7 <sup>th</sup> grid harmonics). (a) Inverter-side current and grid-side current, (b) Sampled PCC voltage and estimated grid impedance. Source: [C5] |

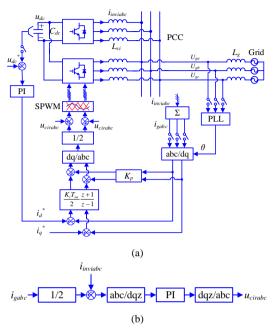

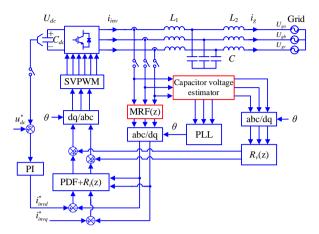

| <b>Fig. 7.1.</b> Diagram of proposed grid voltage sensorless control for three-phase VSCs (MRF: modified repetitive filter, PDF: pseudo-derivative-feedback). Source: [J4]                                                                                         |

| Fig. 7.2. Single-phase equivalent circuit for a three-phase VSC. Source: [J4] 78                                                                                                                                                                                   |

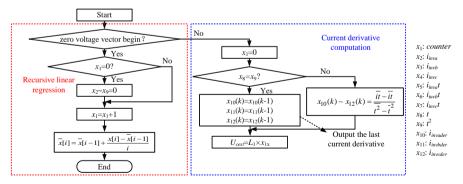

| Fig. 7.3. Proposed filter capacitor voltage estimation flowchart. Source: [J4] 79                                                                                                                                                                                  |

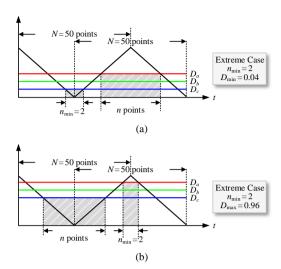

| <b>Fig. 7.4.</b> Duty cycle limitation for the dataset used for linear regression. (a) Minimum duty cycle, (b) Maximum duty cycle. Source: [J4]                                                                                                                    |

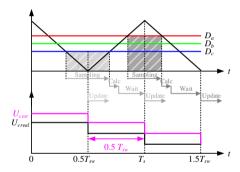

| Fig. 7.5. Update scheme of filter capacitor voltage estimator. Source: [J4] 80                                                                                                                                                                                     |

| <b>Fig. 7.6.</b> Model of the current control loop. (a) PDF controller-based control diagram, (b) Equivalent PI controller-based control diagram. Source: [J4]                                                                                                     |

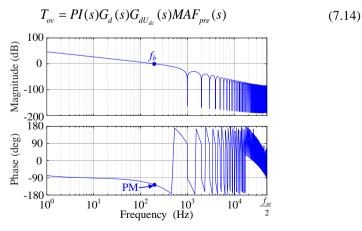

| <b>Fig. 7.7.</b> Bode diagram of the current control loop with IRF and MRF (IRF: improved repetitive filter, MRF: modified repetitive filter). Source: [J4]                                                                                                        |

| <b>Fig. 7.8.</b> Topology deviation when injecting zero voltage vectors. (a) Three-phase VSC with locked three upper arms, (b) Equivalent boost converter. Source: [J4].                                                                                           |

| Fig. 7.9. Block diagram of pre-charging control. Source: [J4]                                                                                                                                                                                                      |

| <b>Fig. 7.10.</b> Bode diagram of dc-link voltage controller during pre-charging. Source: [J4]                                                                                                                                                                     |

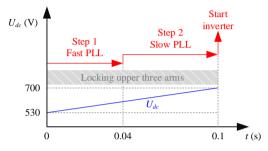

| <b>Fig. 7.11.</b> Switching mechanism of fast and slow PLL during start-up process. Source: [J4]                                                                                                                                                                   |

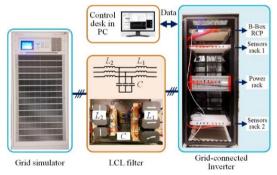

| Fig. 7.12. Three-phase grid-connected VSC prototype. Source: [J4]                                                                                                                                                                                                  |

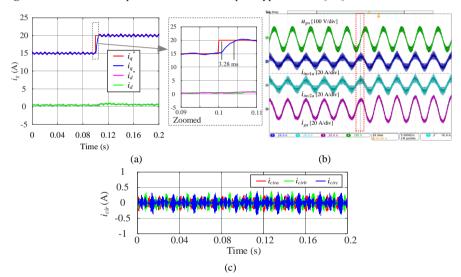

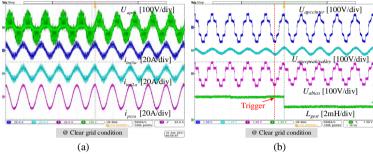

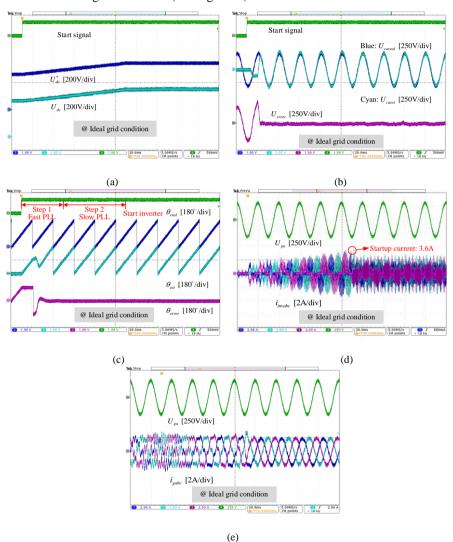

| <b>Fig. 7.13.</b> Experimental results for start-up under an ideal grid condition. (a) Dclink voltage, (b) Estimated filter capacitor voltage, (c) Estimated grid phase angle, (d) Inverter-side currents, (e) Grid-side currents. Source: [J4]                    |

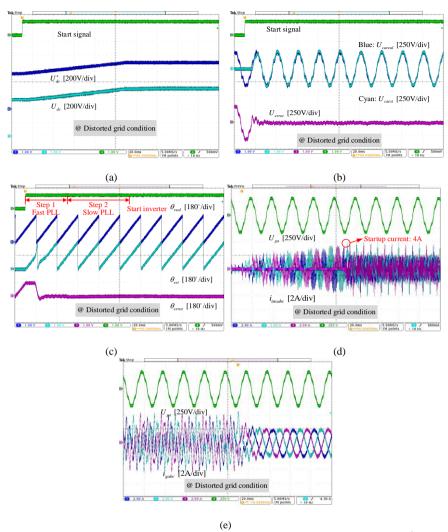

| <b>Fig. 7.14.</b> Experimental results for start-up under a distorted grid condition (10% 5 <sup>th</sup> and 7 <sup>th</sup> harmonics). (a) Dc-link voltage, (b) Estimated filter capacitor voltage,                                                             |

| (c) Estimated grid phase angle, (d) Inverter-side currents, (e) Grid-side currents.  Source: [J4]                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

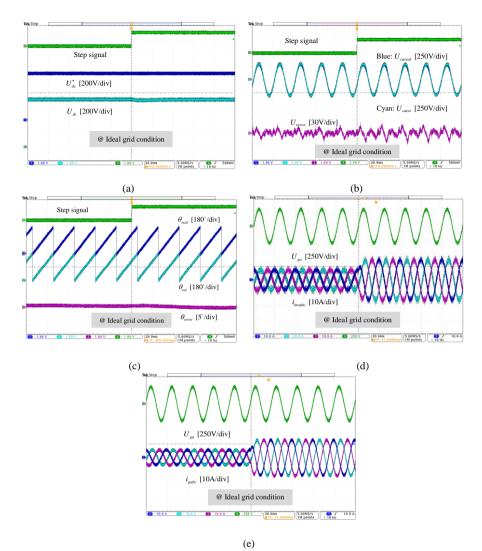

| <b>Fig. 7.15.</b> Reference current step-change performance under an ideal grid condition. (a) Dc-link voltage, (b) Estimated filter capacitor voltage, (c) Estimated grid phase angle, (d) Inverter-side currents, (e) Grid-side currents. Source: [J4]. 88                                                    |

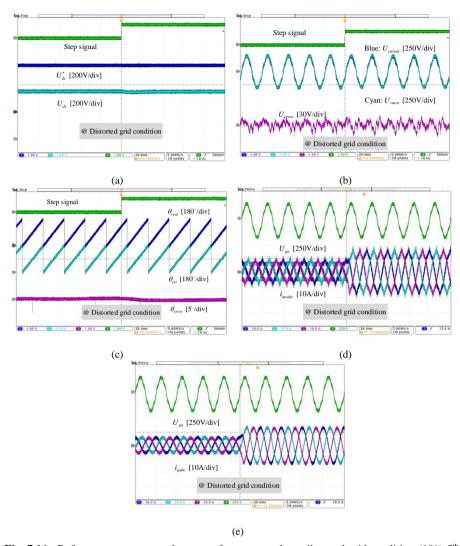

| <b>Fig. 7.16.</b> Reference current step-change performance under a distorted grid condition (10% 5 <sup>th</sup> and 7 <sup>th</sup> harmonics). (a) Dc-link voltage, (b) Estimated filter capacitor voltage, (c) Estimated grid phase angle, (d) Inverter-side currents, (e) Grid-side currents. Source: [J4] |

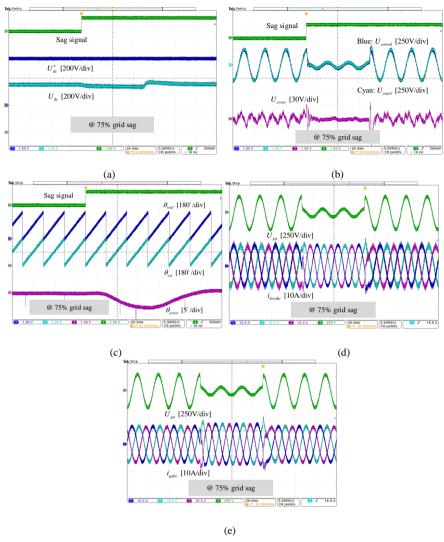

| <b>Fig. 7.17.</b> Experimental results under a 75% grid voltage sag. (a) Dc-link voltage (b) Estimated filter capacitor voltage, (c) Estimated grid phase angle, (d) Inverterside currents, (e) Grid-side currents. Source: [J4]                                                                                |

# LIST OF TABLES

| <b>TABLE 2.1.</b> Main parameters of a grid-connected VSC. Source: [J2]                                   | 22 |

|-----------------------------------------------------------------------------------------------------------|----|

| TABLE 3.1. Main parameters of a three-phase grid-connected VSC. Source:[J3]                               | _  |

| <b>TABLE 3.2.</b> Main parameters of a single-phase grid-connected VSC. Source:[J3]                       | 33 |

| <b>TABLE 4.1.</b> Main parameters of a three-phase grid-connected VSC. Source: [C1].                      | 19 |

| <b>TABLE 5.1.</b> Comparison between real-time-update PWM and multi-sampling PWM. Source: [C3] and [J1]6  | 51 |

| <b>TABLE 5.2.</b> Main parameters of a three-phase grid-connected VSC. Source: [C3].                      | 53 |

| <b>TABLE 6.1.</b> Main parameters of an interleaved three-phase two-cell grid-connected VSC. Source: [C4] | 59 |

| <b>TABLE 7.1.</b> Main parameters of a grid-connected three-phase VSC. Source: [J4                        | _  |

|                                                                                                           |    |

# PART I. REPORT

# **CHAPTER 1. INTRODUCTION**

#### 1.1. BACKGROUND

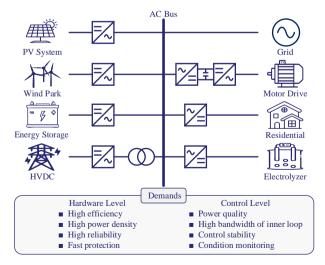

Electric power system is being modernized with the help of power electronics, which can transform voltages and currents from one level and shape to another [1]. Voltage-source converters (VSCs), as an interface between the AC system and the DC system (see Fig. 1.1), are widely used in renewable energy generation [2], battery energy storage [3], high-voltage direct current (HVDC) transmission [4], transportation electrification [5], and low-voltage distribution network [6], etc. Depending on the power demand, the VSC topologies vary. Three-phase two-level VSC is the most commonly used converter, but the allowed output power is limited by the current rating and the voltage rating of the power semiconductors. Multi-level VSCs are mainly used in the medium-voltage and high-voltage level power conversions [7], such as three-level neutral point clamped VSCs, modular multi-level converters, interleaved parallel VSCs, etc.

In terms of the hardware level of VSCs, raising efficiency and power density are always the primary demands to save energy costs and reduce emissions. These two requirements can be achieved in several ways, e.g., by reducing switching losses in power semiconductors, magnetic integration, and advanced thermal management from layout of printed circuit boards to case enclosure [8-9]. In light of the critical applications and harsh operation environments, reliable operation of VSCs is of necessity to ensure long lifetime and low maintenance cost [10]. In addition, the fast protection of semiconductors should be secured in terms of over-current and over-voltage faults.

Fig. 1.1. Applications and demands of VSCs in power system.

In terms of the control level of VSCs, power quality should be normally guaranteed at a satisfactory level when connected to the grid/load [11]. For instance, a total harmonic distortion for the controlled current should be lower than 5%, which can be achieved through the harmonic suppression control or the hard passive filtering [12]. In addition, the VSCs are usually equipped with multiple control loops with different dynamics, and the high bandwidth of the inner control loop is preferred. On the other hand, the dynamics of the outer loops are usually low to decouple the controller design, which, however, leads to frequency coupling with both the load and grid. Consequently, the VSC system may be unstable with wide-band oscillations, based on which, the accurate modeling and careful controller design are emphasized [13]. To further save the cost and enhance the reliability, advanced condition monitoring may be applied such as motor speed estimation, grid voltage estimation, grid impedance estimation, and fault diagnosis [14-16].

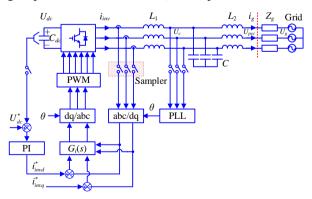

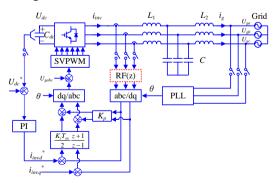

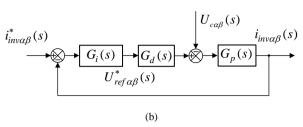

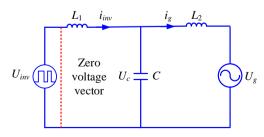

Increasing the integration of renewables has been regarded as a critical pathway to de-carbonize the power system [17-19]. As a bridge between the renewables and the power grid, grid-connected VSCs are of importance to fulfill the above demands. To achieve efficient and reliable power conversion, three basic control loops including the alternating current controller (ACC), dc-link voltage controller (DVC), and phaselocked loop (PLL) are required. Fig. 1.2 shows a typical control structure of a threephase VSC, where  $U_g$  is the grid voltage,  $U_{pcc}$  is the point of common coupling (PCC) voltage,  $U_c$  is the filter capacitor voltage,  $U_{dc}^*$  is the dc-link reference voltage,  $i_{inv}$  is the inverter-side current,  $L_1$  is the converter-side filter inductance,  $L_2$  is the grid-side filter inductance, C is the filter capacitance,  $Z_g$  represents a grid impedance, respectively. The dq-frame proportional-integral (PI) current control is adopted, where the dc-link voltage  $U_{dc}$  is controlled to generate the d-axis current reference  $i_{invd}^*$ . PLL is used for the grid synchronization, where the PCC voltage or the filter capacitor voltage is measured to obtain the phase angle  $\theta$ , which is then used with abc/dq transformations. The outputs of PI current controllers go through a dq/abc transformation, generating the modulation signal. The voltage pulse pattern is produced through a pulse width modulation (PWM) process.

Fig. 1.2. Typical control structure of a three-phase VSC. Source: [J1].

For the controller design, a fast dynamic response is required for ACC, and the bandwidth of ACC is usually set to 1/5 to 1/10 of the switching frequency [20]. In addition, the bandwidth of outer loops such as DVC and PLL should be set to a low value to decouple the dynamics with ACC [21]. Nevertheless, the control delay is inevitable in the PWM process, which limits the bandwidth design of ACC. On the other hand, the passive grid admittance tends to vary in a wide range with the increasing proportion of renewable energy sources, which poses a significant challenge to VSC-grid interactions [22]. Even though the ACC is designed internally stable, the system may still be unstable due to the control delay. According to the impedance-based stability criterion, the VSC control system can be represented as a current source  $i_s(s)$  with an output admittance  $Y_o(s)$  in parallel (see Fig. 1.3). First, the current source  $i_s(s)$  should be stable. Second, the ratio of output admittance to grid admittance should meet the Nyquist criterion. While the first condition can be easily guaranteed through the bandwidth design of ACC, the second is difficult to achieve. Due to the control delay, the phase difference at the intersection point between  $Y_o(s)$ and  $1/Z_g(s)$  can be easily over 180°, then the VSC-grid system will be not stable [23].

Fig. 1.3. Representation of VSC-grid system.

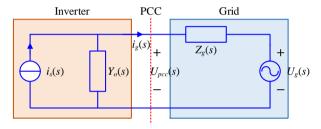

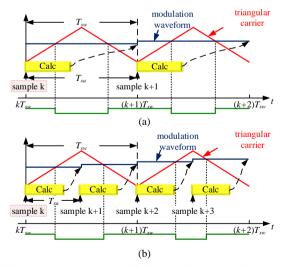

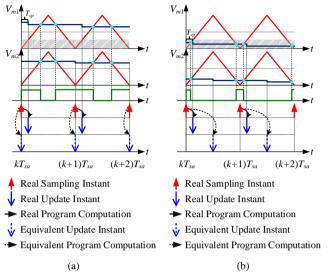

Fig. 1.4. Regular PWM in digital control. (a) Single-sampling, (b) Double-sampling. Source: [J2].

Hence, the control delay is crucial in the bandwidth of ACC and the VSC-grid interactive stability. Moreover, the control delay is determined by the sampling methods. For the digital control of VSC, single-sampling and double-sampling PWM are the most used sampling methods. As shown in Fig. 1.4, the sampling period  $T_{sa}$  is the same as or half of the switching period  $T_{sw}$ . The main advantage of single-sampling and double-sampling is that the average value of current and voltage can be directly obtained without using the anti-aliasing filters [24]. Yet, the control delays for both

of sampling methods are  $1.5T_{sw}$  and  $\frac{1.5T_{sw}}{2}$ , which are far away from the critical delay

$0.25T_{sw}$  according to passivity-based theory [25]. In order to compensate the control delay, a series of digital filters are proposed but their performance in the high-frequency range is restricted [26].

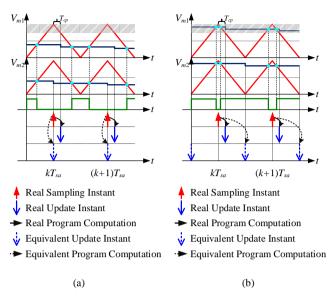

In the past decades, the cost of high-performance microprocessors has significantly decreased, which promotes the utilization of multi-sampling PWM in reducing the control delay [27]. Fig. 1.5 illustrates the diagram of multi-sampling PWM, where the sampling and the calculation are implemented more than twice. Especially, if the sampling rate is infinite, multi-sampling control will become the analog control [28]. Moreover, the control delay inversely relates to the multi-sampling rate, which can help to overcome the bandwidth limit of the ACC design and to enhance the stability considering the effect of grid impedance [29]. In addition, the linear controllers can be easily transplanted, and only the sampling frequency needs to be increased.

Fig. 1.5. Multi-sampling PWM. Source: [J2].

Yet, compared with single-sampling and double-sampling PWM, the switching harmonics (SHs) are introduced besides the average value. Although several digital methods are proposed in the prior art to deal with the multi-sampled SHs, their effect on the control is still not clear [30]. Further, the duty cycle is updated more than twice during one switching period, but an effective voltage pulse can only be produced by two duty cycles. Hence, the internal mechanism of multi-sampling PWM should be further investigated.

In light of the considerable control delay in single-sampling PWM and double-sampling PWM, several passivity-based current control methods are proposed in the prior art. The main principle is to shape the output admittance of VSC to be passive using active damping, then the VSC system can be always stable regardless of grid admittance [31]. However, the current multi-sampling PWM-based control methods mainly focus on the bandwidth improvement of ACC, and how to utilize the multi-sampling PWM with less control delay to further enhance the passivity is still not

widely discussed. Moreover, the design of the passivity-based damping terms should be based on the internal mechanism of multi-sampling PWM.

Besides the bandwidth improvement of ACC and the VSC-grid interactive stability enhancement, the multi-sampled switching ripple can be further used to estimate additional states and parameters in VSCs. Consequently, more information can be acquired to unleash more possibilities for better control performance. However, the current applications of multi-sampling-based estimation mainly focus on the motor drives [32], and few works discuss the grid-connected VSCs.

#### 1.1.1. MULTI-SAMPLING PWM

The control delay  $T_d$  for single-sampling and double-sampling PWM is  $1.5T_{sa}$ , which contains a one-step computation delay and a half-step zero-order-hold delay [33-34]. Note that the expression of control delay for multi-sampling PWM is  $\frac{1.5T_{sw}}{N}$

(*N* is the sampling rate), which can be regarded as an extension of regular sampling PWM [28]. However, the control delay derivation is based on DC-DC converters [35]. For the two-level three-phase VSCs, the internal mechanism of delay reduction remains unclear. Moreover, the effect of the sampled SHs on the control system is still not thoroughly discussed, which makes it difficult to design the related sampled SHs suppression methods.

The four-sampling PWM is recommended in the control of single-phase VSCs [36]. It can be seen in Fig. 1.6 that the apparent switching frequency is twice as large as the carrier frequency with unipolar modulation. Hence, the average current can be sampled at the intersection points and the peak/valley of the carrier. Fig. 1.7 gives a comparison when using different sampling rates. Herein, the carrier frequency is set as 2 kHz, and the apparent switching frequency is 4 kHz. When the sampling rate is larger than four such as sixteen, the SHs around multiple switching frequencies are introduced. More generally, the noise-free sampling rate can be set to 4*M* for the cascaded H-bridge VSCs with *M* cells [37].

It seems that multi-sampling technology is more suitable for multi-level VSCs, and the SHs will not be sampled by setting a proper sampling rate. However, the ability of multi-sampling PWM to control delay reduction will be constrained. Moreover, interleaved VSCs are another kind of commonly used multi-level VSCs, where the switching cells are connected in parallel instead of in series like the cascaded H-bridge VSCs [38]. Unfortunately, the multi-sampling PWM is still not widely applied in interleaved VSCs. Therefore, the selection of multi-sampling rate for multi-level VSCs is of importance to be further studied, and the prerequisite is that the multi-sampling PWM in two-level three-phase VSCs should be fully understood.

Fig. 1.6. Four-sampling PWM for a single-phase VSC (Blue: modulation signal, Red: carrier). Source: [J1].

**Fig. 1.7.** Sampled inverter-side current for a single-phase VSC ( $f_{sw}$ =2 kHz). (a) Four-sampling ( $f_{sa}$ =8 kHz), (b) Sixteen-sampling ( $f_{sa}$ =32 kHz). Source: [J3].

### 1.1.2. PASSIVITY BASED CURRENT CONTROL

As an extension of the admittance shaping, the passivity-based current control is a promising solution to tackle the VSC-grid interactive instability challenges. Similar to the impedance-based criterion, the first condition to achieve passivity is that the ACC should be stable. The second condition is stricter, i.e., the output admittance should be passive for all frequencies. Specifically, the phase characteristic of VSC output admittance  $Y_o(s)$  in Fig. 1.3 will be within  $[-90^{\circ}, 90^{\circ}]$ , which is the same as resistors, inductors, capacitors, or a combination. Consequently, the phase difference can be always below  $180^{\circ}$  at the intersection point between the VSC output admittance and the grid admittance, and the system stable operation can be secured regardless of

the grid admittance [31]. The first condition can be easily guaranteed by setting the bandwidth of ACC. However, the second condition is hard to achieve due to the control delay, and the passivity goal is compromised to Nyquist frequency.

LCL filters are commonly used in grid-connected VSCs to reduce the volume of the required inductors and improve the power quality, which, however, leads to the quite different non-dissipative regions according to the current sampling position. When the control target is converter-side current, the non-dissipative region for the

VSC output admittance is between the critical frequency ( $\frac{1}{4T_d}$ ) and the Nyquist

frequency. Hence, control delay compensation can help to shrink the non-dissipative region and enhance the passivity [25]. Another passivity enhancement route is to add extra damping terms such as filter capacitor current damping, filter capacitor voltage damping, PCC voltage damping, etc [39].

When the control target is grid-side current, the non-dissipative region for the VSC output admittance is between the anti-resonant frequency ( $\frac{1}{2\pi}\sqrt{\frac{1}{L_1C}}$ ) and critical

frequency ( $\frac{1}{4T_d}$ ) [40]. In contrast with the converter-side current control, the

passivity is threatened by control delay reduction, and the extra damping terms are mandatory. Similar to the converter-side current control, several passivity-based current control methods using filter capacitor current damping, filter capacitor voltage damping, and PCC voltage damping have been proposed in [41-44], but only the regular sampling PWM is considered.

The current applications of multi-sampling PWM mainly focus on the bandwidth and the internal stability improvement, and the discussion of VSC-grid interactive stability is rare. Hence, how to utilize multi-sampling PWM with reduced control delay to update the previous passivity-based control methods and further enhance the stability robustness needs to be further explored.

#### 1.1.3. CONDITION MONITORING

The multi-sampling technology not only reduces the control delay, but also additional states and parameters can be predicted using multi-sampled data. Up till now, there are two applications in VSCs including current slope estimation and grid impedance estimation. Fig. 1.8 shows a three-phase PWM, and the current slope can be estimated by utilizing the sampled current data during the active vectors ( $U_{11}$  and  $U_{12}$ ) or the zero vectors ( $U_{01}$  and  $U_{02}$ ) [45-46]. Based on the estimated current slope, several states and parameters in the field of motor drives can be further estimated such as motor speed, motor inductance open-circuit fault detection, and dead-time compensation [47-50].

**Fig. 1.8.** Voltage vectors and currents for a three-phase PWM. (a)  $U_{inv\alpha}$  and  $i_{inv\alpha}$  within a switching period, (b) Estimated current slope. Source: [J4].

As discussed before, the grid impedance plays a key role in the VSC-grid interactive stability. Besides the passivity-based control, grid impedance estimation is also a promising candidate. Then the control parameters can be adjusted online to shape the output admittance and maintain the stable operation of VSCs. By using the four-sampled current and voltage, as shown in Fig. 1.9, the grid impedance is estimated for a two-level three-phase VSC [51]. Similarly, by only using the four-sampled PCC voltage, the grid impedance estimation is achieved for a single-phase VSC [52]. Considering the prior art of multi-sampling-based estimation, there are still a lot of possibilities to estimate more parameters and states and to achieve a better control performance, especially for the grid-connected VSCs.

Fig. 1.9. Measurement instants for grid impedance estimation. Source: [J1].

### 1.2. PROJECT OBJECTIVES AND LIMITATIONS

#### 1.2.1. PROJECT OBJECTIVES

The overall goal of this project is to exploit the multi-sampling technology in grid-connected VSCs. The main hypothesis is summarized as follows:

### Can multi-sampling technique improve the robustness of grid-connected VSCs?

Guided by this hypothesis, the following research questions are pursued:

- Q1: What is the internal mechanism of multi-sampling PWM in VSCs?

- Q2: How to enhance the passivity for VSCs using multi-sampling PWM?

- Q3: How to utilize multi-sampling for condition monitoring in VSCs?

Aiming to address the abovementioned research questions, three research objectives are listed as follows:

O1: Reveal the internal mechanism of multi-sampling PWM for two-level and multi-level VSCs

The effect of different anti-aliasing filters on the sampled SHs and control performance needs to be investigated. Moreover, the control delay reduction for multi-sampling PWM in VSCs needs to be identified, based on which, the detailed implementation in the two-level and multi-level VSCs will be discussed as well.

O2: Develop multi-sampling control strategies to enhance the passivity of the current control of VSCs

The passivity characteristic for the single/double-sampled ACC of VSCs will be investigated first. Based on the reduced control delay, the multi-sampling control strategies will be developed to further enhance the passivity when sampling the VSC-side current or the grid-side current, respectively. In addition, the robustness to the filter parameter fluctuations will be researched as well.

O3: Estimate more states and parameters in VSCs using the multi-sampled current/voltage switching ripple

Based on the equivalent circuit of VSCs, the utilization of multi-sampled switching ripple will be investigated to estimate the crucial states and parameters such as grid voltage estimation, grid impedance estimation, fault diagnosis, passive filter parameters estimation, etc.

#### 1.2.2. PROJECT LIMITATIONS

This Ph.D. project has the following limitations:

- The analysis of multi-sampling PWM is based on the voltage-balance equivalence, which still lacks strict mathematic deduction. Moreover, the nonlinear phenomenon in the multi-sampling PWM such as vertical crossing and multiple switching are ignored.

- In the passivity-based current control, the side band effect close to the switching

frequency is ignored in the PWM model. Additionally, the effect of outer loops

on the stability in the low-frequency range is ignored.

- For the grid-voltage estimation, the effect of sampling noise on the estimation accuracy is not considered. Also, the stability robustness to the VSC-side inductor saturation and grid impedance variation is not considered.

- In the experimental validation, the VSC is connected to a grid emulator instead of the real power grid. In addition, the dc-side is not connected to a real solar panel or a wind turbine. Hence, the feasibility and reliability of the proposed control methods in this Ph.D. project require more field tests.

#### 1.3. THESIS OUTLINE

This Ph.D. project's outcomes are documented in the form of a paper-based Ph.D. thesis, containing a *Report* and a collection of the *Selected Publications* throughout the entire study. The thesis structure is shown in Fig. 1.10 to illustrate how to connect the content in the *Report* to the *Selected Publications*.

There are eight chapters in the *Report*. The research background and motivation of the Ph.D. project are introduced in Chapter 1. Chapter 2 analyzes the mechanism of multi-sampling PWM and aliasing, and an improved repetitive filter is proposed to suppress the aliasing having a small phase lag. To enhance the passivity of ACC, a damping strategy controlling converter-side current is proposed in *Chapter 3*, and the robustness against the filter parameter deviation is also discussed. In addition, the proposed method is extended to the single-phase VSCs. Similarly, a passivity-based damping strategy controlling grid-side current is proposed in *Chapter 4*, where the robustness to the filter parameter deviation and the transient performance during startup are enhanced. To further reduce the control delay, an enhanced real-time-update current control method is developed in *Chapter 5*, and the dissipation below Nyquist switching frequency can be achieved only using single-loop converter-side current control. Chapter 6 focuses on the multi-sampled current control of three-phase interleaved VSCs, and the sampling rate selection and the control parameter design are discussed. Moreover, based on the multi-sampled PCC voltage, the grid impedance is estimated under a pure inductive grid. Chapter 7 proposes a grid voltage estimator while using multi-sampled current control, based on which, the sensor cost might be saved and the voltage sensor fault can be prevented. Finally, Chapter 8 concludes this Ph.D. project and suggests future trends.

## 1.4. LIST OF PUBLICATIONS

The outcomes of during Ph.D. study have been submitted/published in the form of journal papers and conference papers, as indicated below. Parts of these publications are used in the Ph.D. dissertation (*Report*), which are also listed in Fig. 1.10.

#### Journal Papers:

- [J1] S. He, D. Zhou, X. Wang, Z. Zhao, and F. Blaabjerg, "A review of multi-sampling techniques in power electronics applications," *IEEE Trans. Power Electron.*, early access, 2022.

- [J2] S. He, D. Zhou, X. Wang, and F. Blaabjerg, "Aliasing suppression of multi-sampled current controlled LCL-filtered inverters," *IEEE Trans. Journal Emerg. Sel. Topics Power Electron.*, vol. 10, no. 2, pp. 2411-2423, April 2022.

- [J3] **S. He**, D. Zhou, X. Wang, and F. Blaabjerg, "Passivity based multisampled current control of LCL-filtered grid-connected inverters," *IEEE Trans. Power Electron.*, 2022 (Second-round revision).

[J4] **S. He**, D. Zhou, X. Wang, and F. Blaabjerg, "Line voltage sensorless control of grid-connected inverters using multisampling," *IEEE Trans. Power Electron.*, vol. 37, no. 4, pp. 4792-4803, April 2022.

# Conference Papers:

- [C1] **S. He**, Z. Yang, D. Zhou, X. Wang, F. Blaabjerg, and Rik De Doncker, "Robust passivity enhancement for LCL-filtered grid-following inverters with multi-sampled grid-side current control", in *Proc. IEEE ECCE*, 2022 (Accepted).

- [C2] **S. He**, D. Zhou, X. Wang, and F. Blaabjerg, "Switching harmonics suppression of single-loop multi-sampling control of grid-connected inverter", in *Proc. IEEE IECON*, pp. 3259-3264, 2020.

- [C3] **S. He**, D. Zhou, X. Wang, and F. Blaabjerg, "Enhanced real-time-update current control for grid-following inverters," in *Proc. IEEE PEDG.*, 2022 (Accepted).

- [C4] **S. He**, D. Zhou, X. Wang, and F. Blaabjerg, "Multisampling control of two-cell interleaved three-phase grid-connected converters", in *Proc. IEEE APEC*, pp. 590-594, 2021.

- [C5] **S. He**, D. Zhou, X. Wang, and F. Blaabjerg, "Multisampling based grid impedance estimation for two-cell interleaved three-phase inverters", in *Proc. IEEE ECCE*, pp. 1432-1437, 2021.

**Fig. 1.10.** Thesis structure with related topics and research outcomes for each chapter; where "O" denotes objective, while "J" and "C" refer to a journal or conference publication, respectively.

# Other publications not included in the Ph.D. thesis:

- [OP1] **S. He**, X. Sui, Z. Liu, M. Kang, D. Zhou and F. Blaabjerg, "Torque ripple minimization of a five-phase induction motor under open-phase faults using symmetrical components," *IEEE Access*, vol. 8, pp. 114675-114691, June 2020.

- [OP2] **S. He**, D. Zhou, X. Wang, and F. Blaabjerg, "Overview of multisampling techniques in power electronics converters", in *Proc. IEEE IECON*, pp. 1922-1927, 2019.

- [OP3] **S. He**, D. Zhou, X. Wang, and F. Blaabjerg, "Switching harmonics suppression of single-loop multi-sampling control of grid-connected inverter", in *Proc. IEEE IECON*, pp. 3259-3264, 2020.

- [OP4] **S. He**, D. Zhou, X. Wang, and F. Blaabjerg, "Grid voltage sensorless control of three-phase LCL grid-connected inverters using multisampled current", in *Proc. IEEE ECCE Asia*, pp. 2002-2006, 2020.

- [OP5] **S. He**, Y. Pan, D. Zhou, X. Wang, and F. Blaabjerg, "Current harmonic analysis of multisampled LCL type grid-connected inverter", in *Proc. IEEE ECCE*, pp. 4329-4335, 2020.

- [OP6] **S. He**, D. Zhou, X. Wang, and F. Blaabjerg, "Multisampling control of LCL-type grid connected inverter with an improved repetitive filter", in *Proc. IEEE ECCE*, pp. 4336-4341, 2020.

- [OP7] **S. He**, Z. Yang, D. Zhou, X. Wang, F. Blaabjerg, and Rik De Doncker, "Low-frequency stability enhancement for LCL-Type grid-following inverters with multi-sampled current control", in *Proc. IEEE ECCE*, 2022 (Accepted).

- [OP8] **S. He**, X. Sui, and F. Blaabjerg, "Comparative study of different fault-tolerant control strategies for a five-phase concentrated-full-pitch winding induction motor," in *Proc. IEEE ECCE Europe*, pp. P.1-P.10, 2019.

- [OP9] **S. He**, X. Sui, D. Zhou and F. Blaabjerg, "Torque ripple minimization of seven-phase induction motor under more-than-two-phase fault," in *Proc. IEEE ICEM*, pp. 2222-2228, 2020.

- [OP10] **S. He**, X. Sui, D. Zhou, and F. Blaabjerg, "Zero torque ripple operation of seven-phase concentrated-full-pitch winding induction motor under open circuit faults," in *Proc. IEEE ISIE*, pp. 380-385, 2020.

- [OP11] **S. He**, X. Sui, D. Zhou, and F. Blaabjerg, "Torque ripple suppression of a five-phase induction motor under single-phase open", in *Proc. IEEE ECCE Asia*, 2020.

- [OP12] Z. Liu.; P. Zhang, **S. He**, J. Huang, "A review of modeling and diagnostic techniques for eccentricity fault in electric machines," *Energies*, vol. 14, no. 6, pp. 4296, July 2021.

- [OP13] Z. Li, F. Zhao, X. Wang, **S. He**, S.-M. Nielsen, "Multi-sampling with real-time update PWM for time-delay minimization of FPGA-based voltage controlled converters," in *Proc. IEEE APEC*, 2022. (Accepted).

# CHAPTER 2. MULTI-SAMPLING PWM ANALYSIS AND ALIASING SUPPRESSION

#### 2.1. BACKGROUND

In the implementation of multi-sampling PWM, the effect of sampled SHs on the control is still not fully discussed, and the internal mechanism of multi-sampling PWM is also not clear. Prior-art studies mainly focused on the multi-sampled SHs suppression and four strategies have been proposed as follows.

First, by using the first-order hold sampler, the modulation signal has more continuity but the small-signal model needs further analysis [53-54]. Second, the saw-tooth carrier is added to the feedback loop to counteract the switching noise, however, the triangle carrier is more general in DC-AC converters and the compensation method cannot be utilized directly [55-56]. Third, the grid-side current and the filter capacitor voltage are preferred since they contain less switching noise [57-58]. Fourth, Moving average filter (MAF) can effectively suppress the sampled SHs, but the introduced phase lag is large [59-61]. The phase lag for the simplified repetitive filter (SRF) is low, but only the odd-order SHs can be filtered out [30].

In this chapter, the multi-sampling PWM is transformed into a double-sampling PWM based on the voltage-second equivalence. Then, the Nyquist frequency for multi-sampling PWM is the same as the Nyquist frequency of double-sampling control. Then, the aliasing in the grid-side currents can be explained as the non-average value of current is sampled for the control. To suppress the aliasing, as shown in Fig. 2.1, an improved repetitive filter (IRF) is presented to suppress the sampled SHs while the phase lag is low.

Fig. 2.1. Single-loop multi-sampling control with inverter-side current feedback (RF: repetitive filter). Source: [J2].

#### 2.2. ALIASING ANALYSIS FOR MULTI-SAMPLING PWM

#### 2.2.1. FOUR-SAMPLING PWM

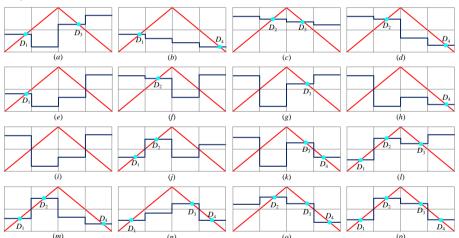

The analysis begins with the most basic multi-sampling PWM, i.e., four-sampling PWM, as seen in Fig. 2.2. According to the probability theory, there are  $2^4$  possible intersection cases, and the amplitude of the duty cycle determines the intersection position. Fig. 2.2(l)-(p) shows one non-linear phenomenon called multi-intersection, where the power semiconductor is triggered more than two times during one switching period and the switching loss will increase. One solution is to restrict the slew rate of the reference to be lower than the carrier [62-63], the "self-lock" logic from the microprocessor can be also utilized to prevent multi-switching [64]. Fig. 2.2(e)-(i) shows the vertical crossing phenomenon, and only one duty cycle or no duty cycles can produce the effective voltage pulse. When the vertical crossing happens, the PWM is forced to output pull-up and pull-down [64]. Similarly, the cases in Fig. 2.2(j)-(k) can be also ignored because they are a combination of multi-switching and vertical crossing. In addition, the cases in Fig. 2.2(a) and (d) should be disregarded since they only occur when the modulation wave crosses 0.5.

Fig. 2.2. Intersection analysis for four-sampling PWM (Blue: modulation signal, Red: carrier). Source: [J2].