### **Aalborg Universitet**

#### Series-Connection of Medium Voltage SIC Mosefets with Self-Powered Design

Wang, Rui

DOI (link to publication from Publisher): 10.54337/aau543669441

Publication date: 2023

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Wang, R. (2023). Series-Connection of Medium Voltage SIC Mosefets with Self-Powered Design. Aalborg Universitetsforlag. https://doi.org/10.54337/aau543669441

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

## SERIES-CONNECTION OF MEDIUM VOLTAGE SIC MOSFETS WITH SELF-POWERED DESIGN

#### BY RUI WANG

**DISSERTATION SUBMITTED 2023**

# SERIES-CONNECTION OF MEDIUM VOLTAGE SIC MOSFETS WITH SELF-POWERED DESIGN

by

Rui Wang

Dissertation submitted

Dissertation submitted: May 2, 2023

PhD supervisor: Prof. Stig Munk-Nielsen,

Aalborg University

Assistant PhD supervisor: Assistant Prof. Asger Bjørn Jørgensen,

Aalborg University

PhD committee: Professor Zhe Chen (chair)

Aalborg University, Denmark

Senior Specialist, PhD Lars Helle Vestas Wind Systems, Denmark

Professor Jacek Rabkowski

Warsaw University of Technology, Poland

PhD Series: Faculty of Engineering and Science, Aalborg University

Department: AAU Energy

ISSN (online): 2446-1636

ISBN (online): 978-87-7573-713-0

Published by:

**Aalborg University Press**

Kroghstræde 3

DK – 9220 Aalborg Ø Phone: +45 99407140

aauf@forlag.aau.dk

forlag.aau.dk

© Copyright: Rui Wang

Printed in Denmark by Stibo Complete, 2023

### CV

Rui Wang obtained the B.S. degree in Electrical Engineering and Automation from Hunan University in Changsha, China, in 2017. He then obtained the M.S. degree in electrical engineering from Huazhong University of Science and Technology in Wuhan, China, in 2020. Currently, he is pursuing the Ph.D. degree in Aalborg University in Aalborg, Denmark.

Rui Wang's research interests involve wide bandgap power semiconductor devices, active gate drivers and series-connection technology for these devices, as well as corresponding medium-voltage converter design.

## **ABSTRACT**

Medium-voltage (MV) high-power power electronics technology, which contributes to less copper cost and loss, becomes significantly promising as the power demand of society increases continuously. Owing to rapid advancement of power semiconductor devices featuring wide bandgap material, the emerging MV silicon carbide (SiC) metal oxide semiconductor field effect transistors (MOSFETs) rated from 3.3 kV to 15 kV can exceptionally simplify the structure and decrease the control complexity level of MV high-power converters. Besides this, it facilitates high frequency, high efficiency, and high-temperature operation. Nevertheless, there still exist some hardware design challenges which hinder this evolution.

To enhance the effectiveness by using MV SiC devices to replace the dominance of silicon (Si) insulated gate bipolar transistors (IGBTs) in MV converter applications, this thesis initially presents the importance and necessity of researching gate driver (GD) design considering the prominent fast-switching characteristic of SiC device. Then it is clarified that, common mode noise and isolation burden are two significant issues encountered in the GD design. Furthermore, series-connection is researched in this thesis, which is categorized into two groups named as direct and indirect series-connections based on intended synchronous and asynchronous switching operations. Maintaining the advantage of fast switching of SiC devices also brings on a significant challenge for the voltage balancing (VB) design of direct series-connection.

On the above basis, for some indirect series-connections of power devices using modular design with large submodule capacitor, targeting the self-powered auxiliary power supply (APS) for powering GDs, etc., a single gate-driven SiC MOSFET stack is suggested to construct it with a flyback topology, where simplified structure and easier control are the prominent advantages. Further, a thorough analysis of the single gate-driven MOSFET stack's short-circuit characteristics is conducted and a hardware improvement is proposed to reinforce its resistance against the short-circuit in the presence of both hard switch fault and fault under load.

For direct series-connection and some other indirect series-connections without large submodule capacitors, a converter-based self-powered GD is suggested for MV SiC device, which integrates the device and GD into a single unit and makes it scalable to series-connection. Most importantly, it eliminates the common mode path from the GD to the ground and reduces the isolation burden from the total bus voltage to the unit voltage. By conducting experiments, the effectiveness of this self-powered GD has been verified in the cases of DC to DC and DC to AC conversions. On this basis, an adaptive impedance optimization for this self-powered GD is proposed to achieve a better tradeoff between snubber loss and VB performance of series-connected SiC MOSFETs in static and dynamic conditions. Finally, in conjunction with an active delay control strategy, the achieved dynamic VB performance is further enhanced.

٧

**Keywords**: medium voltage, SiC MOSFET, auxiliary power supply, gate driver, series-connection, voltage balancing, short-circuit fault, self-powered, common-mode noise.

## **DANSK RESUME**

Teknologien for mellemspænding (MV) effektelektronik, som bidrager til lavere kobberomkostninger og tab, bliver stadig mere betydningsfuld, som samfundets behov for energi fortsætter med at stige. På grund af den hurtige udvikling af nye halvledermaterialer i dag, kan nye MV siliciumcarbid (SiC) metal-oxid-halvlederfelteffekttransistor (MOSFET) med en blokeringsspænding fra 3,3 kV til 15 kV i høj grad forenkle strukturen og reducere styringskompleksiteten af MV effektelektronikkonvertere. De muliggør høj operations-frekvens, høj effektivitet og høj drifttemperatur. Ikke desto mindre er der stadig visse hardware-designudfordringer, der hæmmer denne udvikling.

For at opnå fordelene af at bruge MV SiC-enheder til at erstatte dominansen af silicium (Si) isolerede gate-bipolare transistorer (IGBT) i MV effektelektronik, præsenterer denne afhandling først vigtigheden og nødvendigheden af at undersøge gate-driver (GD) design på grund af den hurtige skiftekarakteristik af SiC-enhederne. Derefter påpeges det, at støj og spændingsisolering er to væsentlige udfordringer, der opstår i gate-driver-designet. Baseret på state-of-the-art kategoriseres serielforbindelse i denne afhandling i to grupper som direkte og indirekte seriel-forbindelse i henhold til den tilsigtede synkrone og asynkrone skiftning. At opretholde fordelene ved hurtig skiftning af SiC-enheder medfører også en betydelig udfordring for spændingsbalancering ved direkte seriel-forbindelse.

Derefter foreslås en enkelt gate-drevet SiC-MOSFET-stak til at konstruere en selv-drevet GD med en flyback-topologi. Den enkelt gate-drevet GD fjerner problemet med støj og høj isoleringsbyrde der ellers findes i de nuværende GD, og derudover er en forenklet struktur og nemmere kontrol de markante fordele. Yderligere analyseres denne enkelt-gate drevne SiC-MOSFET-stak i forhold til kortslutningsfejl, og det identificeres hvordan en tilføjelse af et kredsløb kan gøre en SiC-MOSFET-stak robust imod kortslutning.

For direkte serieforbindelser, samt visse andre indirekte serieforbindelser uden store submodul-kondensatore, foreslås en konverter-baseret selvforsynende GD til MV SiC-enheder, som integrerer enheden og GD i et enkelt modul og gør den skalerbar til serieforbindelse. Vigtigst af alt eliminerer den fælles støj-vej fra GD til jord og reducerer isolationsbelastningen fra den samlede indgangs-spænding ned til enhedsspændingen. Ved at udføre eksperimenter er effektiviteten af denne selvforsynende GD blevet bekræftet i både DC-DC og DC-AC-konverteringer. På denne baggrund, foreslås en adaptiv impedansoptimeret styring af denne selvforsynende GD for at opnå en bedre afvejning mellem tab og spændingsbalancering af serieforbundne SiC MOSFET'er under både statiske og dynamiske tilstande. Endelig kan den dynamiske spændingsbalancering forbedres yderligere ved tilføjelse af aktiv forsinkelseskontrolstrategi.

**Nøgleord**: mellem-spænding, SiC MOSFET, hjælpestrømforsyning, gate-driver, serieforbindelse, spændingsbalancering, kortslutningsfejl, selv-forsynet, fælles tilstandsstøj.

## **ACKNOWLEDGEMENTS**

This thesis makes a summary of the research achievements I have accomplished in the Ph.D. project conducted at AAU Energy, Aalborg University, Denmark. I would like to thank Medium Voltage BASIC & Center of Digitalized Electronics (CoDE) project for partially funding my Ph.D. project. In addition, I would also like to thank the Chinese Scholarship Council for granting me a CSC scholarship and the Otto foundation for supporting my study abroad.

I would like to extend my sincere thanks to Stig Munk-Nielsen, my supervisor, for providing me with the professional and valuable mentorship. I appreciate his support and encouragement, which assisted me in overcoming the research dilemma. This experience, as a precious treasure, would establish my essential confidence in my future research. I would also like to sincerely express the gratitude to my cosupervisor Asger Bjørn Jørgensen for crucial guidance, patient discussion, and kind assistance regarding the research and my writing skill. I would also like to thank my supervisor at KTH Royal institute, Hans-Peter Nee, for the productive discussion during my three-month study abroad in Stockholm, Sweden.

I would like to thank Hongbo Zhao as the Ph.D. mentor of mine, for providing substantial assistance with my research as well as career guidance. I would also like to thank the other co-authors in my appended publications, Wentao Liu, Shaokang Luan, Zhixing Yan, and Dipen Narendra Dalal, for their valuable contributions. I would like to thank my colleagues, Szymon Michal Beczkowski, Jannick Kjær Jørgensen, Yuan Gao, Zhongchao Sun, Faheem Ahmad, Benjamin Futtrup Kjærsgaard, Masaki Takahashi, Pawel Piotr Kubulus and Thore Stig Aunsborg, for the creative discussions. I would like to thank the project coordinator, Bonnie Steffensen, who assisted me with the reimbursing of conferences and travel expenses.

Finally, I would like to deeply express the gratitude to my family. Without your endless support, unconditional trust, significant encouragement, and unselfish love, I could not start and accomplish this journey.

Aalborg, April 2023

Rui Wang

## **TABLE OF CONTENTS**

| Chapter 1. Introduction1                                                             |

|--------------------------------------------------------------------------------------|

| 1.1. State-of-the-art                                                                |

| 1.1.1. Gate driver design of MV SiC MOSFET2                                          |

| 1.1.2. Series-connection design of MV SiC MOSFETs                                    |

| 1.2. Research objectives                                                             |

| 1.3. Original contributions                                                          |

| 1.4. Publications                                                                    |

| Appended publications                                                                |

| Other publications                                                                   |

| 1.5. Thesis outline                                                                  |

| Chapter 2. A single gate-driven stack for self-powered auxiliary power supply        |

| 11                                                                                   |

| 2.1. Single gate driver concept                                                      |

| 2.2. Working principle of the suggested single gate-driven stack                     |

| 2.2.1. Turning-on process                                                            |

| 2.2.2. Turning-off process                                                           |

| 2.2.3. Automatic balancing process and non-ideal factors                             |

| 2.3. Experimental results in self-powered auxiliary power supply application 20      |

| Chapter 3. Anti-short circuit improvement of the single gate-driven stack27          |

| 3.1. Short-circuit characteristic analysis of the single gate-driven stack           |

| 3.2. Anti-short circuit improvement of the stack                                     |

| 3.2.1. Working principle of the improved stack                                       |

| 3.2.2. Simplified model of anti-short circuit fault process                          |

| 3.3. Experimental results of anti-short circuit fault performance                    |

| Chapter 4. A self-powered gate driver with converter-based design41                  |

| 4.1. Common mode noise analysis of gate driver                                       |

| 4.2. Structure of the suggested self-powered gate driver with converter-based design |

| 4.3. Experimental verification of the suggested gate driver                          |

| Chapter 5. Voltage balancing design of series-connected MV SiC Mequipped with self-powered gate drivers |    |

|---------------------------------------------------------------------------------------------------------|----|

| 5.1. The concept of adaptive-impedance snubber                                                          | 56 |

| 5.1.1. Voltage balancing in static condition                                                            | 57 |

| 5.1.2. Voltage balancing in dynamic condition                                                           | 61 |

| 5.2. Design detail and hybrid voltage balancing strategy                                                | 62 |

| 5.3. Experimental verification of voltage balancing                                                     | 67 |

| 5.3.1. Performance of the adaptive-impedance snubber                                                    | 68 |

| 5.3.2. Performance of the hybrid voltage balancing strategy                                             | 71 |

| 5.3.3. Experimental verification in DC to AC conversion                                                 | 73 |

| Chapter 6. Conclusion and future work                                                                   | 77 |

| 6.1. Conclusion                                                                                         | 77 |

| 6.2. Future work                                                                                        | 78 |

| Appendices                                                                                              | 81 |

## TABLE OF FIGURES

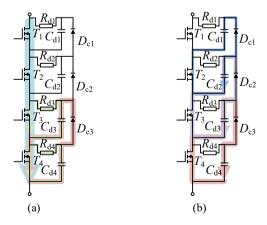

- Figure 1-1. Direct series-connection of MV SiC MOSFETs

- Figure 1-2. Indirect series-connection of MV SiC MOSFETs (a) multi-level converter with flying capacitor (b) modular multi-level converter

- Figure 2-1. MMC hardware with the (a) external-powered (b) self-powered approach

- Figure 2-2. Topology of the improved single gate-driven SiC MOSFET stack

- Figure 2-3. Turning-on process of the proposed stack

- Figure 2-4. Key circuit status in (a) Stage I, (b) Stage II, (c) Stage III, (d) Stage VI

- Figure 2-5. Turning-off process of the proposed stack

- Figure 2-6. Key circuit status in (a) Stage V, (b) Stage VI, (c) Stage VII, (d) Stage VIII

- Figure 2-7. (a) automatic balancing current loops (b) non-ideal reverse current loops

- Figure 2-8. Diagram of medium voltage testing platform

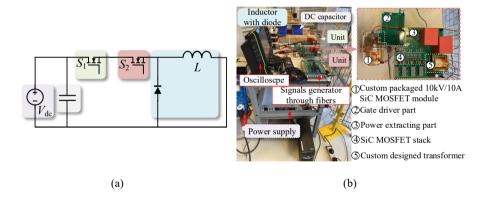

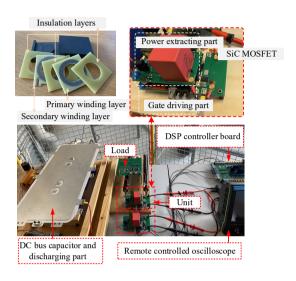

- Figure 2-9. The self-powered auxiliary power supply: (a) schematic (b) photograph

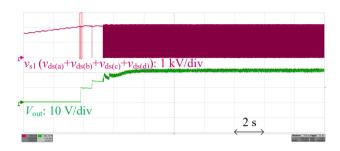

- Figure 2-10. Overall performance of the self-powered auxiliary power supply

- Figure 2-11. Voltage balancing performance of SiC MOSFETs in the proposed stack

- Figure 2-12. Voltage balancing during (a) input voltage transient (b) output load transient

- Figure 2-13. Loss distribution results with (a) the clamping RCD snubber method (b) the active delay control method (c) the proposed method

- Figure 3-1. Simulated waveforms of the single gate-driven stack in the FUL occurrence

- Figure 3-2. Topology of the improved single gate-driven SiC MOSFET stack

- Figure 3-3. Working process of the improved stack in (a) normal (b) FUL (c) HSF conditions

- Figure 3-4. (a) simplified anti-short circuit fault model (b) thermal model

- Figure 3-5. Testing platform of the improved stack: (a) schematic (b) photograph

- Figure 3-6. Performance of the improved stack in the normal condition

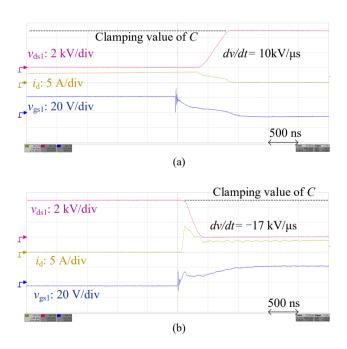

- Figure 3-7. Performance of the improved stack in the (a) fault under load and (b) hard switch fault conditions

- Figure 3-8. (a) measured  $v_{eq}$  (b) measured  $i_{eq}$  (c) I-V characteristic fitting (d) solved  $i_{eq}$

- Figure 3-9. Comparisons between experiment and simplified model in the FUL condition (a)  $i_{SC}$  (b)  $\Delta t_r$ ,  $\Delta t_f$ ,  $\Delta t_r + \Delta t_f$  (c)  $I_{(max)}$

- Figure 3-10. Comparisons between experiment and simplified model in the HSF condition (a)  $i_{SC}$  (b)  $\Delta t_r$ ,  $\Delta t_f$ ,  $\Delta t_r + \Delta t_f$  (c)  $I_{(max)}$

- Figure 4-1. Direct series-connection with the (a) conventional (b) self-powered gate driver

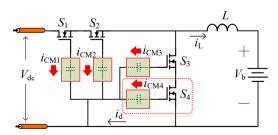

- Figure 4-2. Common mode noises indication of a bidirectional DC to DC converter

- Figure 4-3. Simulation results of common mode noises when running

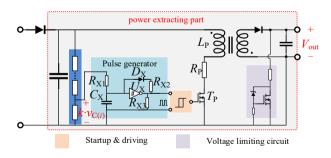

- Figure 4-4. Overall configuration of the self-powered gate driver with converter-based design

- Figure 4-5. Detail of the power extracting part

- Figure 4-6. The designed transformer (a) 3D-CAD model (b) electric field distribution with the aid of ANASYS Maxwell

- Figure 4-7. Testing platform of the self-powered gate driver with converter-based design: (a) schematic (b) photograph

- Figure 4-8. Startup process using the self-powered gate driver with converter-based design

- Figure 4-9. Switching waveforms of a 10 kV SiC MOSFET using the suggested self-powered gate driver with converter-based design (a) turning-off (b) turning-on

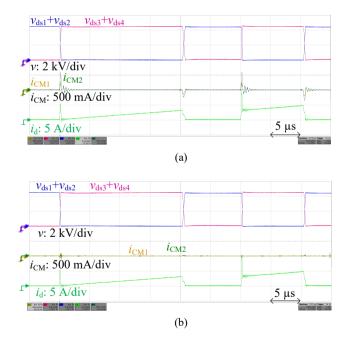

- Figure 4-10. Comparison results of CM currents for  $S_1$  and  $S_2$  with (a) conventional gate drivers (b) suggested self-powered gate drivers with converter-based design

- Figure 4-11. (a) static and (b) dynamic voltage balancing performance of  $S_1$  and  $S_2$  in a double-pulse test with suggested self-powered gate drivers

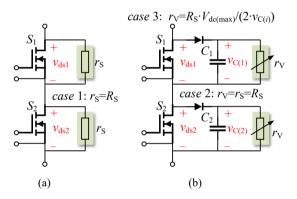

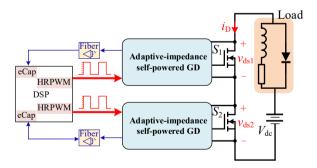

- Figure 5-1. Two direct series-connected MV SiC MOSFETs equipped with the self-powered gate drivers

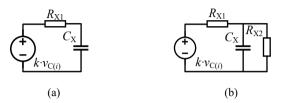

- Figure 5-2. Static voltage balancing (a) by placing resistors in parallel (b) with the adaptive-impedance design

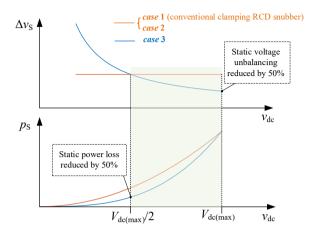

- Figure 5-3.  $\Delta v_S$  and  $p_S$  indication versus  $v_{dc}$  in case 1, case 2, and case 3

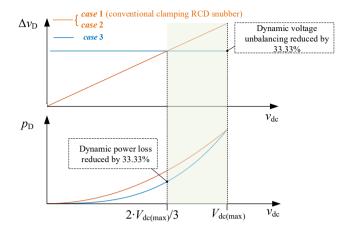

- Figure 5-4.  $\Delta v_D$  and  $p_D$  indication versus  $v_{dc}$  in case 1, case 2, and case 3

- Figure 5-5. Main circuit of the designed power extracting part

- Figure 5-6. Equivalent circuit diagram of the designed pulse generator during (a) OFF and (b) ON duration

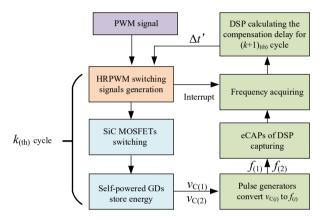

- Figure 5-7. Structure of the suggested hybrid voltage balancing method

- Figure 5-8. Detail of the system flowchart

- Figure 5-9. The corresponding control block diagram

- Figure 5-10. Testing platform photograph of a buck chopper circuit

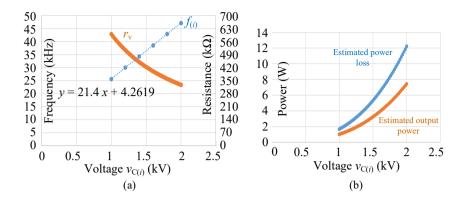

- Figure 5-11. (a) correlation between  $f_{(i)}$  ( $r_V$ ) and  $v_{C(i)}$  (b) estimated power loss and estimated output power versus  $v_{C(i)}$

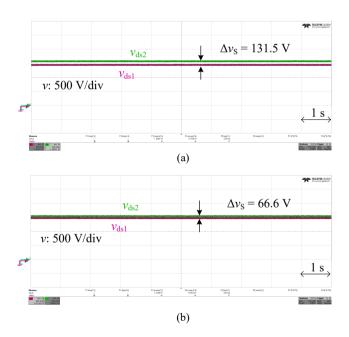

- Figure 5-12. Static voltage balancing performance equipped with (a) the conventional snubber (case 1 & case 2), (b) the proposed adaptive-impedance "snubber" (case 3)

- Figure 5-13. Dynamic voltage balancing performance equipped with the traditional snubber (case 1 & case 2)

- Figure 5-14. Dynamic voltage balancing performance equipped with the proposed adaptive-impedance "snubber" (case 3)

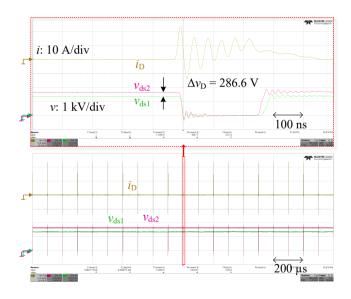

- Figure 5-15. Dynamic voltage balancing performance with the proposed hybrid strategy

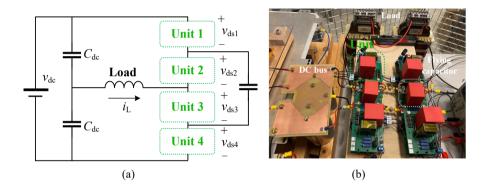

- Figure 5-16. Testing platform of a half-bridge circuit: (a) schematic (b) photograph

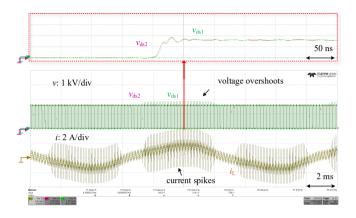

- Figure 5-17. Voltage balancing with sinusoidal pulse width modulation

Figure 5-18. Performance of direct series-connection: (a) turning-on (b) turning-off process

Figure 5-19. Performance of indirect series-connection: (a) turning-on (b) turning-off process

Figure 6-1. Schematic of the intelligent power module

Figure 6-2. Schematic of series-connection-based LLC resonant converter

## **CHAPTER 1. INTRODUCTION**

In recent decades, the advance of power electronics technology has extensively promoted the industry development, and power electronics converters are ubiquitous today, from tiny integrated modules of a few watts to giant converters of tens of megawatts. Among them, high-power converters based on fully-controlled power semiconductor devices play a crucial role in industrial applications for satisfying the requirement of solid power controllability. As the demand for power rating keeps growing, they are developing towards higher voltage for the purpose of saving copper loss and cost, which leads to the widespread use and promising future of medium voltage (MV) (1 kV - 35 kV) converters [1].

In terms of power generation, MV converters plays a crucial role in the utilization of renewable energy such as offshore wind turbines, large photovoltaic plants, etc. In terms of power consumption, MV converters are used to directly obtain power from the MV grid for fast charging of large electric vehicles, power supply of data centers, etc. Additionally, MV converters can also be applied as motor drives in areas like fans in the cement industry, compressors in the chemical industry, pumps in the water industry, etc. [2], which are taken as the example for the following elaboration as the products of some companies are listed in Table 1-1.

| Manufacturer  | Product       | Voltage (AC) | Power        |

|---------------|---------------|--------------|--------------|

| DICETE AM [2] | MV700         | 6.0/6.9 kV   | 1.7-11.1 MW  |

| INGETEAM [3]  | MV100         | 3.3-4.16 kV  | 0.8-12.7 MW  |

| CIEMENO [4]   | GH150         | 4.16-13.8 kV | 4-35 MVA     |

| SIEMENS [4]   | GH180         | 2.3-11 kV    | 0.14-17 MVA  |

|               | ACS2000       | 4.0-6.9 kV   | 0.25-3.68 MW |

| ABB [5]       | ACS5000       | 6.0-13.8 kV  | 2-36 MW      |

|               | MEGADRIVE-LCI | 2.1-2*25 kV  | 2-150 MW     |

| AMTECH [6]    | AXPERT-HIVERT | 3.3-11 kV    | 0.25-12.5 MW |

| DELTA [7]     | MVD3000       | 3.3-11 kV    | 0.25-10.9 MW |

Table 1-1 Industrial MV motor drives

As is widely known, the performance of power devices is of great significance to converters, and the above commercial products are all based on Silicon (Si) devices.

1

For relatively lower voltage, taking Ingeteam MV100 for instance, a back-to-back three-level converter based on Si insulated-gate-bipolar-transistor (IGBT) is qualified [3]. To meet higher voltage requirement such as 13.8 kV AC output voltage, modular multi-level converter need to be adopted as in the design of SIMENS GH150 [4].

Compared with the Si devices, Silicon Carbide (SiC) devices enable operation at higher blocking voltage, temperature and higher switching speed with less power loss [8]. Although till now, Si IGBTs still dominate in the field due to their standardized fabrications, mature designs, and improved performances. Thanks to the development of SiC technology, MV SiC metal-oxide-semiconductor field-effect transistor (MOSFET) rated from 3.3 kV to 15 kV has attracted attention due to its superior switching characteristics and become a promising power device to challenge the hegemony of Si IGBT [9]. Consequently, to prompt this evolution, it is essential to research its reliable gate driver (GD) design and series-connection design to comply with the high voltage standard and faster switching speed.

#### 1.1. STATE-OF-THE-ART

#### 1.1.1. GATE DRIVER DESIGN OF MV SIC MOSFET

Since both SiC MOSFET and Si IGBT have a similar gate structure, their driving mechanisms and corresponding GD designs are also comparable. Referring to the design of Si IGBT, GD of SiC MOSFET also requires adequate positive/negative voltage to assure the reliable turning on/off, reliable over-voltage protection and short-circuit protection to prevent damage to the device, active miller clamping circuit to prevent the device from being falsely turned on caused by crosstalk, etc.

While the difference is that, SiC MOSFET as a wide bandgap device requires a higher positive voltage to reduce the on-state loss and a lower negative voltage to avoid the gate breakdown (recommended as +20 V / -5 V). Besides, the fast switching characteristic of SiC MOSFET requires the response speeds of protection circuits to be faster, and the influences of parasitic parameters should be given greater consideration. Further, when moving towards MV SiC MOSFET from low-voltage SiC MOSFET, the challenge lies in the isolation, where both the signal transmission and power transmission are focused on. In MV cases, optical fibers are generally used in the signal transmission to achieve isolation. By contrast, the methods for isolation of the power transmission are numerous and rather important.

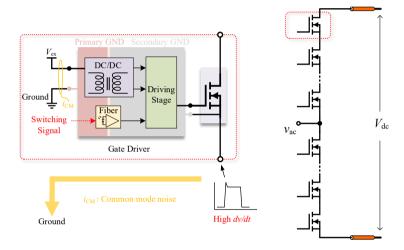

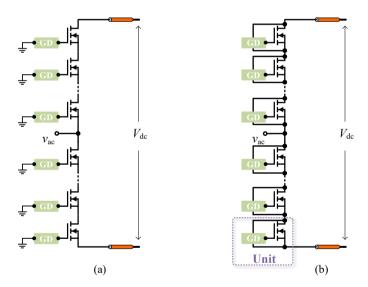

Most of GDs utilize the external-powered design which requires an external grounded power supply to power GD, as shown on the left side of Fig. 1-1. Therefore, considering the above voltage difference between input side and output side of GD, it is necessary to ensure sufficient isolation to prevent high voltage breakdown, and it is vital as well to ensure a sufficiently low coupling capacitance to prevent forming a large common mode current induced by high dv/dt during the switching process of

MV SiC MOSFET, which may cause interference to the driving signal when flowing through the GD. Hence, two ways are suitable for the power transfer design on GD, where one is based on power over fiber, and the other is based on transformer [10]. Since transferred power by the former one is limited and efficiency is low, a lot of research are targeting the latter one. To greatly reduce the coupling capacitance while maintaining high voltage isolation, the material, size and the winding design of magnetic cores are studied [11]-[12]. For further improvement, a method of PCB based planar winding can be adopted [13], and a method of high-density current-transformer can be applied [14]. Nowadays, wireless power transfer is a popular solution for GD design where the magnetic core is removed, which has claimed 120 W output power, 92.78% full-power efficiency, and 27 kV isolation capability [15].

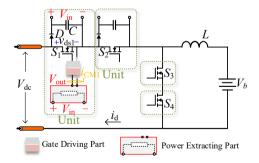

Figure 1-1. Direct series-connection of MV SiC MOSFETs

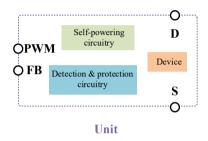

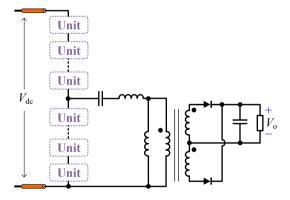

In contrast, self-powered GD design, where GD extracts power from the main loop directly, enables the power device, its GD, and the associated power extracting part to be included in a single unit. It can greatly ease the high voltage isolation burden. Besides this, low coupling capacitance is achieved as well since the common mode current path from the GD to the ground is eliminated. Additionally, since the external power source is not used, it is appropriate for extended design. Nevertheless, this self-powered concept has only yet been realized in a number of methods for thyristors, IGBTs, and lower voltage MOSFETs.

#### 1.1.2. SERIES-CONNECTION DESIGN OF MV SIC MOSFETS

Considering the design margin of using MV SiC MOSFET, a single device limited by its blocking voltage is only suitable for a small number of medium voltage cases. To accommodate the higher voltage application scenarios, series-connection of MV SiC

MOSFETs is called for, which is divided into direct series-connection and indirect series-connection in this thesis.

Direct series-connection is the straightforward method to improve the blocking voltage of device by connecting more devices in series, as shown on the right side of Fig. 1-1, and the working principle is to make the series-connected power devices switch synchronously. However, there exists a well-known challenge that unbalanced voltage distribution occurs among devices. Voltage unbalancing of series-connected devices in a stack can result in devices withstanding higher voltages than their own blocking capabilities when operating at the expected total voltage, and the overvoltage breakdown of one device can further lead to breakdown of the full stack as a severe consequence. Static voltage unbalancing of series-connected devices is induced by the leakage current discrepancy of devices and it is generally solved by placing balancing resistors in parallel. With dynamic voltage unbalancing being the major problem, it is caused by inconsistencies of GDs of devices, devices characteristics, etc., and a significant voltage unbalancing could occur during the switching transients. For lowvoltage devices, literatures have given extensive analysis and provided many valuable solutions [16]. For MV SiC MOSFETs, the direct series-connection is only studied in a few papers [17]-[21], and adding resistor-capacitor snubbers is the common voltage balancing (VB) method, which causes large power loss for good VB performance.

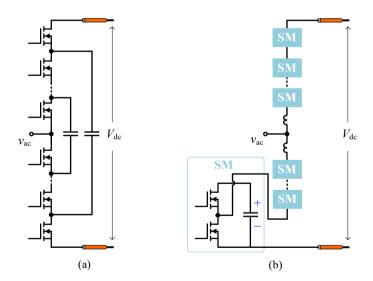

Figure 1-2. Indirect series-connection of MV SiC MOSFETs (a) multi-level converter with flying capacitor (b) modular multi-level converter

In contrast to direct series connection, indirect series-connection manages to avoid the dynamic voltage unbalancing by means of topology modifications of the converters [22], and thus the electromagnetic interference (EMI) issue will be reduced, or the filter requirement will be lower by means of switching seriesconnected power devices asynchronously.

Fig. 1-2(a) presents a prevalent method of using flying capacitors to implement this goal. The transient voltages of devices are clamped by the capacitors to assure safety, and the balancing of charging and discharging of capacitors are controlled by the specific modulation of the converter. With large flying capacitors to clamp voltages temporarily, considerable driving delays of devices in the stack can be set intentionally to realize multi-level modulation, which facilitates reduction of the harmonic content of output voltage and alleviation of EMI issue [23]. However, the large capacitors occupy a large volume of the converter based apparatus and increase the total cost. Therefore, a quasi-two-level modulation becomes attractive with small flying capacitors despite of sacrificing the benefit of low harmonic content [24]-[25]. A similar design by adopting the diode clamping method is also prevalent, and using multi-level modulation for low harmonic content while using quasi-two-level modulation for the lower requirements of diodes [26].

Although the above flying capacitor converter and diode clamping converter are effective in MV design, their topologies become more and more complicated as the series count of devices increases to meet the higher voltage requirement. Instead, the modular multi-level converter (MMC), as another type of indirect series-connection is preferred in the higher voltage cases, as shown in Fig. 1-2(b). Similarly, in order to achieve multi-level output voltage with low harmonic content, the submodule (SM) capacitance needs to be large which increases the size and cost, and using quasi-two-level modulation can be one tradeoff solution [27]-[28].

It is worth noting that, to alleviate the common mode noise and isolation problems as described above, auxiliary power supply (APS) is integrated into the SM to power GDs, which benefits from the modular design and the intrinsic SM capacitor [29]. Since APS extracts the power from the SM capacitor, it also utilizes a self-powered concept, which is known as self-powered APS. Different from the above illustrated self-powered GD which is combined with a single power device to be considered as a unit, as this self-powered APS is combined with a SM as a unit, it will still suffer from the common mode noise to some extent inside the SM, while self-powered GD features the elimination of common mode noise theoretically.

Although using MV SiC MOSFETs can reduce the series count compared with using low-voltage ones and simplify the complexity, the input voltage of the self-powered APS becomes higher and its corresponding design as a high-input-voltage low-output-lower converter needs to be considered. Due to cost saving, low-voltage devices are generally adopted in the design. Therefore, lots of optimization methods have been proposed, including input-series structure [30], multi-cell series-parallel converter [31], high-voltage tapped-inductor buck converter [32], etc. However, they make the topology and control scheme complicated.

#### 1.2. RESEARCH OBJECTIVES

The research aims to identify some potential challenges of the direct and indirect series-connection of MV SiC MOSFETs with self-powered design, and then to provide corresponding analyses and solutions:

- For self-powered auxiliary power supply design in the SM of MMC, an appropriate DC to DC topology with high-input-voltage, simple control and low cost needs to be chosen.

- For self-powered gate driver design, although greatly reduced by using self-powered concept, the high-input-voltage and large *dv/dt* (*di/dt*) still cause potential isolation and interference problems to itself. Besides, a suitable topology for constantly self-powering should be taken into account.

- For direct series-connection design, the fast switching characteristic of MV SiC MOSFET brings more difficulty to the active voltage balancing. Hence, an effective voltage balancing strategy is required.

#### 1.3. ORIGINAL CONTRIBUTIONS

Based on the above research objectives, the novelty in this thesis and the original contributions are as follows:

- To simplify the topology and ease the control burden, a flyback converter is selected to construct the self-powered auxiliary power supply. For satisfying the high-input-voltage requirement, a single gate-driven stack consisting of directly series-connected SiC MOSFETs with low-voltage rating is proposed as the primary switch of this flyback converter, which possesses the capability of automatic voltage balancing [Publication IV, Publication V]. Further, its short-circuit characteristic is studied and analyzed, and the potential for over-current limitation in the single gate-driven stack is firstly pointed out. As a result, the single gate-driven SiC MOSFET stack is improved to increase its ability to resist short-circuit faults, and these enhancements have significantly strengthened the stack's capability of antishort circuit fault [Publication II].

- A scalable self-powered gate driver with converter-based design is suggested, where the SiC MOSFET stack with automatic voltage balancing capability is used to build a high-input-voltage power extracting converter, and it makes commercial gate driver available as its following gate driving part. It works efficiently without the aid of the main loop power device's switching. In addition, the self-powered gate driver is controlled as a clamping resistor-capacitor-diode (RCD) snubber by using the open-loop

design of the power extraction converter, which is scalable to the series-connection of power devices [Publication III].

Adaptive-impedance optimization of the self-powered gate driver with converter-based design is proposed for obtaining a better static and dynamic voltage balancing performance of series-connected SiC MOSFETs. Further, as a passive voltage balancing strategy, it facilitates the small-signal model establishment for combining with an active delay control method, which contributes to a well-balanced voltage distribution [Publication I, Publication VI]. In addition, the startup problem of using self-powered gate drivers is also evaluated, and a potential improvement method is provided and further demonstrated experimentally [Publication VII].

#### 1.4. PUBLICATIONS

#### **APPENDED PUBLICATIONS**

This thesis is prepared as a summary of published papers, and the following papers are appended as part of this thesis.

#### In journals:

- **I. R. Wang**, A. B. Jørgensen, W. Liu, H. Zhao Z. Yan and S. Munk-Nielsen, "Voltage Balancing of Series-connected SiC MOSFETs with Adaptive-impedance Self-powered Gate Drivers," in *IEEE transaction on Industrial Electronics*, doi: 10.1109/TIE.2022.3231281, 2022, Early Access.

- II. R. Wang, A. B. Jørgensen, H. Zhao and S. Munk-Nielsen, "An Improved Single Gate Driven SiC MOSFET Stack with Strong Anti-short Circuit Fault Capabilities," in *IEEE Transactions on Power Electronics*, vol. 37, no. 11, pp. 13577-13586, Nov. 2022.

- III. R. Wang, A. B. Jørgensen, D. N. Dalal, S. Luan, H. Zhao and S. Munk-Nielsen, "Integrating 10kV SiC MOSFET into Battery Energy Storage System with A Scalable Converter-based Self-powered Gate Driver," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 11, no. 1, pp. 351-360, Feb. 2023.

- **IV. R. Wang**, A. B. Jørgensen, and S. Munk-Nielsen, "An Enhanced Single Gate Driven Voltage-balanced SiC MOSFET Stack Topology Suitable for High-voltage Low-power Applications," in *IET Power Electronics*, vol. 15, no. 3, pp. 251-262, Feb. 2022.

#### At conferences:

- V. R. Wang, H. Zhao and S. Munk-Nielsen, "Comparison of Two Types of Single Gate Drivers for SiC MOSFET Stacks in Flyback Converters," in 2021 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia, 2021, pp. 36-40.

- VI. R. Wang, A. B. Jørgensen, H. Zhao and S. Munk-Nielsen, "Design and analysis of a voltage clamping active delay control method for series-connected SiC MOSFETs," in *24th European Conference on Power Electronics and Applications*, 2022, pp. 1-8.

- VII. R. Wang, A. B. Jørgensen, W. Liu, H. Zhao, Z. Yan, D. N. Dalal and S. Munk-Nielsen, "Auxiliary Power Supply Startup Evaluation and Improvement of the Input-series System With Small Submodule Capacitances," in 2023 IEEE Applied Power Electronics Conference and Exposition, 2023, Accepted.

#### OTHER PUBLICATIONS

In addition to the appended papers, a contribution has been made during the Ph.D. project period.

- 1. H. Zhao, S. Luan, Z. Shen, A. J. Hanson, Y. Gao, D. N. Dalal, **R. Wang**, S. Zhou, and S. Munk-Nielsen, "Rethinking Basic Assumptions for Modeling Parasitic Capacitance in Inductors," in *IEEE Transactions on Power Electronics*, vol. 37, no. 7, pp. 8281-8289, July 2022.

- H. Zhao, Z. Yan, S. Luan, D. N. Dalal, J. K. Jørgensen, R. Wang, X. Zhou, S. M. Beczkowski, B. Rannestad and S. Munk-Nielsen, "A Comparative Study on Parasitic Capacitance in Inductors with Series or Parallel Windings," in *IEEE Transactions on Power Electronics*, vol. 37, no. 12, pp. 15140-15151, Dec. 2022.

#### 1.5. THESIS OUTLINE

The thesis is constructed in the following manner:

Chapter 1 introduces the background and illustrates the state-of-the-art within gate driver design and series-connection design of MV SiC MOSFETs, followed by the defined research objectives. Chapter 2 presents detail of the proposed single gate-driven SiC MOSFET stack, which is designed for high-input-voltage low-output-power applications represented by the self-powered auxiliary power supply in MMC. Chapter 3 delves deeper into the short-circuit properties of the single gate-driven stack

and expounds on the specific measures taken to facilitate the automatic resolution of any short-circuit faults.

Chapter 4 presents the designed self-powered gate driver for MV SiC MOSFET and verifies its effectiveness in experiments. Chapter 5 proposes a novel approach called adaptive-impedance optimization for the self-powered gate driver, aimed at improving the voltage balancing performance of MV SiC MOSFETs in both static and dynamic conditions. Based on it, a hybrid voltage balancing strategy is further proposed, followed by the converter performance demonstration.

Chapter 6 marks the conclusion of the thesis, providing a summary of the research conducted and a discussion on possible avenues for future work.

In the final section, the bibliography and the appended publications are included.

## CHAPTER 2. A SINGLE GATE-DRIVEN STACK FOR SELF-POWERED AUXILIARY POWER SUPPLY

The information in this chapter is based on Publication IV and Publication V.

As a typical topology of indirect series-connection of devices, modular multi-level converter (MMC) is selected as an instance for illustration, and Fig. 2-1 presents intuitive comparison between the external-powered approach and the self-powered one for the gate drivers (GDs), protections, etc.

Figure 2-1. MMC hardware with the (a) external-powered (b) self-powered approach

In Fig. 2-1(a), the GD is powered through an external grounded power supply, which necessitates its ability to withstand the high voltage and dv/dt during the switching transient of the device, especially for the top submodule (SM). Instead, in Fig. 2-1(b), a self-powered auxiliary power supply (APS) is integrated as an essential part in the SM hardware design, and the isolation burden of GD is eased from the total bus voltage to the SM bus voltage and the dv/dt immunity requirement is decreased, which also facilitates the modular design. Therefore, the design of self-powered APS is significant. To simplify the topology and control complexity, utilizing the flyback topology is an effective option in this APS design. However, owing to the high-input-

voltage condition when using medium voltage (MV) SiC MOSFET in the SM design, it necessitates the employment of a low-power device with an equivalent voltage rating as the primary switch in the flyback topology, which is unavailable or expensive in some cases, making direct series-connection of low-voltage power devices an appealing solution.

#### 2.1. SINGLE GATE DRIVER CONCEPT

For the direct series-connection, compared with the conventional approach of using individual GD for each device, single GD shows its compactness where the upper devices in the stack can be driven by some simple passive components whereas only the device at the bottom requires a standard GD. However, this approach will lead to inherent delays in the gate driving loops of series-connected devices and result in significant voltage unbalancing [33]-[36]. Therefore, it is widely researched in the field of solid-state circuit breaker where only one-time turning-off is required, and the energy absorbing components such as varistors are deployed for the transient voltage balancing (VB) purpose. For converter design, several VB methods have also been proposed. In [37]-[38], the commonly used resistor-capacitor-diode (RCD) snubbers are utilized for VB, but this method presents the issue of high loss if a balanced voltage distribution is desired. Additionally, each device requires an extra power supply in its gate loop, which raises the overall cost. In [39], two series-connected devices are respectively accompanied by two compensation capacitors that are placed in parallel for VB, however, the performance is highly dependent on the conditions. These parameters must be precisely selected for a particular situation and adjusted as the power loop varies, or else the voltage unbalancing will become unacceptable.

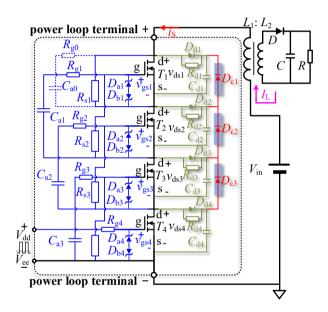

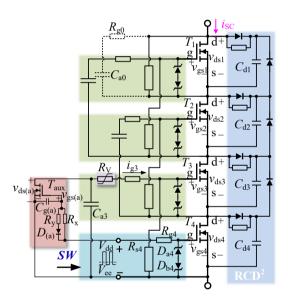

Therefore, the challenge of enhancing the adaptability of a single GD while reducing loss still needs to be addressed. Despite that the authors in [40] managed to achieve the goal by incorporating a controller to regulate the driving speed, this design was complex and only applied to the series-connection case of two SiC MOSFETs. Meanwhile, the authors in [41] utilized a unique snubber topology with good voltage adaptability to balance voltages through automatic balancing loops, but it still used a traditional gate driver design and required a complicated startup circuit. Hence, in this chapter, a novel improved single gate-driven SiC MOSFET stack that integrates the benefits in [40] and [41] is proposed, as depicted in Fig. 2-2. It includes a specifically designed single GD (the blue part), and an optimized RCD snubber (the green and red parts) which is defined as an automatic VB RCD<sup>2</sup> circuit.

#### 2.2. WORKING PRINCIPLE OF THE SUGGESTED SINGLE GATE-DRIVEN STACK

Fig. 2-2 depicts a stack of SiC MOSFETs consisting of four devices  $T_i$  ( $i = 1 \sim 4$ ) connected in series, where the count is chosen when employing 1.7 kV / 5 A devices to satisfy the voltage requirement of 5 kV in the self-powered APS and taking some

design margin into account. It is observed that only the SiC MOSFET at the bottom necessitates a standard GD while the upper devices are driven through additional coupling capacitors  $C_{ai}$  ( $i = 1 \sim 3$ ) which connects the gate electrode of  $T_i$  to the source electrode of its adjacent device. Resistor  $R_{si}$  ( $i = 1 \sim 4$ ) is for static VB, while  $R_{gi}$  ( $i = 1 \sim 4$ ) and  $D_{ai}$  ( $D_{bi}$ ) are respectively utilized as the gate resistor and the gate protection Zener diode. In contrast to the commonly known RCD snubber, the resistance in the automatic VB RCD<sup>2</sup> circuit is selected to be large for saving loss. VB of  $T_i$  ( $i = 1 \sim 4$ ), that is, the balancing of drain-source voltage  $v_{dsi}$ , is improved by placing diodes  $D_{ci}$  ( $i = 1 \sim 3$ ) between snubber capacitors, which takes advantage of the sequential lagging single GD. Next, on the basis of the depicted turning-on and turning-off processes, the working detail will be illustrated as follows.

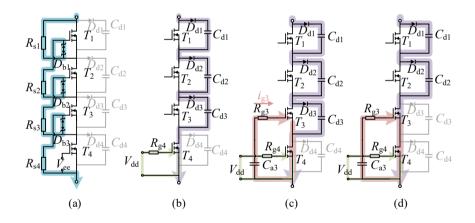

Figure 2-2. Topology of the improved single gate-driven SiC MOSFET stack

#### 2.2.1. TURNING-ON PROCESS

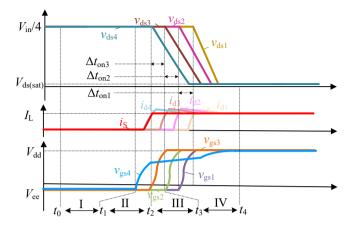

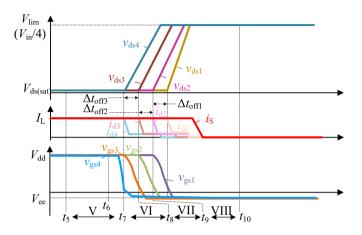

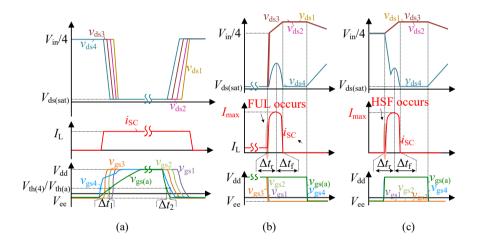

Fig. 2-3 illustrates that the process of turning-on can be segmented into four stages, labeled as Stage I through IV.

**Stage I** [ $t_0 \sim t_1$ ]: during this stage, the gate-source voltage  $v_{gs4}$  of  $T_4$  equals the negative driving voltage  $V_{ee}$ , and there is a key current loop to assure the reliable off-state of this stack as depicted in Fig. 2-4(a). Since the Zener voltage of  $D_{bi}$  and the resistance of  $R_{si}$  can be chosen properly (considering the forward voltage drop of  $D_{ai}$  as well) [42],  $v_{gsi}$  ( $i = 1 \sim 3$ ) of  $T_i$  will also be equivalent to  $V_{ee}$ , and  $v_{dsi}$  will be in static balance.

Figure 2-3. Turning-on process of the proposed stack

Figure 2-4. Key circuit status in (a) Stage I, (b) Stage II, (c) Stage III, (d) Stage VI

**Stage II**  $[t_1 \sim t_2]$ :  $v_{gs4}$  begins to increase from  $V_{ee}$  to the positive driving voltage  $V_{dd}$  when  $T_4$  receives the turning-on signal. When  $T_4$  reaches the saturation region, it triggers the load current  $I_L$  to initiate the commutation process from the secondary side to the stack, and the stack current  $i_S$  will increase from zero. Since  $T_i$  ( $i = 1 \sim 3$ ) remains in its cutoff region, as seen in Fig. 2-4(b),  $i_S$  will instead flow through  $C_{di}$  ( $i = 1 \sim 3$ ) which is relatively large in our approach to avoid voltage unbalancing.

**Stage III** [ $t_2 \sim t_3$ ]: when  $i_S$  approaches the load current  $I_L$  at  $t_2$ ,  $v_{ds4}$  begins to decrease, and it induces the current forming in the gate loop of  $T_3$  as depicted in Fig. 2-4(c). As

a result, there is an increase in the drain current of  $T_4$  ( $i_{d4}$ ) when compared to  $i_S$ , and the following relationship can be established as:

$$i_{M4} = i_{d4} + i_{ds4} + i_{gd4} = I_L + i_{g3} + i_{ds4} + i_{gd4}.$$

(2-1)

where  $i_{M4}$  represents the channel current inside  $T_4$ ,  $i_{g3}$  represents the gate current of  $T_3$  which flows into the gate capacitance  $C_{in3}$  via  $R_{g3}$ , and  $i_{ds4}$  and  $i_{gd4}$  denote the currents across the drain-source capacitance  $C_{gd4}$  and the Miller capacitance  $C_{ds4}$ , respectively.

By incorporating the transconductance parameter  $G_{\rm M}$  and the threshold voltage  $V_{\rm th}$ , the relationships can be obtained as follows:

$$\begin{cases} i_{\text{M4}} = G_{\text{M}}(v_{\text{gs4}} - V_{\text{th}}), & v_{\text{gs4}} > V_{\text{th}} \\ i_{\text{g3}} \approx \frac{-dv_{\text{ds4}}/dt}{(1/C_{\text{a3}} + 1/C_{\text{in3}})} & . \\ i_{\text{gd4}}/C_{\text{gd4}} \approx i_{\text{ds4}}/C_{\text{ds4}} = -dv_{\text{ds4}}/dt \end{cases}$$

(2-2)

Combining Eq. (2-1) and Eq. (2-2),  $dv_{ds4}/dt$  can be solved as:

$$\frac{dv_{\rm ds4}}{dt} \approx -\frac{G_{\rm M}(v_{\rm gs4} - V_{\rm th}) - I_{\rm L}}{C_{\rm ed4} + C_{\rm ds4} + 1/(1/C_{\rm a3} + 1/C_{\rm in3})}.$$

(2-3)

From Eq. (2-2), it is observed that  $i_{g3}$  is highly dependent on  $dv_{ds4}/dt$ , which in turn causes an increase of  $v_{gs3}$ . By adjusting the Zener breakdown voltage of  $D_{ai}$ ,  $v_{gs3}$  will be eventually clamped at  $V_{dd}$ . When  $T_3$  reaches the saturation region as well, the current will be transferred from  $C_{d3}$  to  $T_3$ , and the drain current  $i_{d3}$  of  $T_3$  gets increased.

**Stage IV**  $[t_3 \sim t_4]$ : at  $t_3$ ,  $i_{d3}$  reaches  $I_L$  as well, and the proposed stack switches to the status as depicted in Fig. 2-4(d). Next,  $v_{ds3}$  decreases with the  $\Delta t_{on3}$  lag behind  $v_{ds4}$ . In a similar way, the status changes of gate and power loops of  $T_i$  ( $i=1\sim3$ ) are analogous to those of  $T_4$ . After  $\Delta t_{on2}$ ,  $v_{ds2}$  also decreases, followed by the decrease of  $v_{ds1}$  after  $\Delta t_{on1}$ , and  $dv_{dsi}/dt$  ( $i=1\sim3$ ) is determined as:

$$\begin{cases} \frac{dv_{\text{ds}i}}{dt} \approx -\frac{G_{\text{M}}(v_{\text{gs}i} - V_{\text{th}}) - I_{\text{L}}}{C_{\text{gd}i} + C_{\text{ds}i} + 1/(1/C_{\text{a}(i-1)} + 1/C_{\text{in}(i-1)})}, & i=2, 3\\ \frac{dv_{\text{ds}1}}{dt} \approx -\frac{G_{\text{M}}(v_{\text{gs}1} - V_{\text{th}}) - I_{\text{L}}}{C_{\text{gd}1} + C_{\text{ds}1}} \end{cases}$$

(2-4)

In Eq. (2-4), the  $dv_{ds1}/dt$  of  $T_1$  is steeper since  $T_1$  has one less charging/discharging branch (the resistance-capacitance  $R_{g0}C_{a0}$  branch is not included in this section). In comparison, the voltage fall time in  $v_{dsi}$  ( $i = 2 \sim 4$ ) is relatively similar.

At  $t_4$ , the full flow of  $I_L$  through  $T_i$  ( $i = 1 \sim 4$ ) and the arrival of  $v_{gs4}$  at  $V_{dd}$  signify that the turning-on process of the stack is completed.

#### 2.2.2. TURNING-OFF PROCESS

Figure 2-5. Turning-off process of the proposed stack

Figure 2-6. Key circuit status in (a) Stage V, (b) Stage VI, (c) Stage VII, (d) Stage VIII

Fig. 2-5 illustrates that the process of turning-off can be segmented into four stages as well, labeled as Stage V through Stage VIII.

**Stage V** [ $t_5 \sim t_7$ ]:  $v_{gsi}$  is equal to  $V_{dd}$  and the stack is in on-state during this stage, which is depicted in Fig. 2-6(a). At  $t_6$  when  $T_4$  receives the turning-off signal, its driving voltage is caused to change from  $V_{dd}$  to  $V_{ee}$ . Therefore,  $v_{gs4}$  begins to decrease from  $V_{dd}$  gradually.

**Stage VI** [ $t_7 \sim t_8$ ]: At  $t_7$ ,  $T_4$  reaches the saturation region from linear region as  $v_{\rm gs4}$  is decreasing and  $v_{\rm ds4}$  begins to increase, which induces discharging on the gate side of  $T_3$ , as depicted in Fig. 2-6(b). By setting the Zener breakdown voltage of  $D_{\rm bi}$ ,  $v_{\rm gs3}$  will be finally clamped at  $V_{\rm ee}$ . In the meantime, Eq. (2-3) is still applicable in this situation, and thus  $dv_{\rm ds4}/dt$  can be also estimated.

Stage VII [ $t_8 \sim t_9$ ]: At  $t_8$ ,  $T_3$  also reaches the saturation region, and  $v_{ds3}$  increases  $\Delta t_{off3}$  later than  $v_{ds4}$ . In the same manner, the rising rate of  $v_{ds3}$  can also be determined in accordance with Eq. (2-4), which further results in discharging on the gate side of  $T_2$ . As depicted in Fig. 2-6(c), when  $v_{ds4}$  reaches the limiting value  $V_{lim}$  (approximate to  $V_{in}/4$  in this case),  $i_8$  will flow through  $C_{d4}$  rather than  $T_4$ . Since  $C_{d4}$  is relatively large and the rising of  $v_{ds4}$  will be significantly slower, therefore, the voltage unbalancing is avoided as well.

Stage VIII [ $t_9 \sim t_{10}$ ]: At  $t_9$ ,  $v_{\rm ds2}$  begins to increase and it lags  $\Delta t_{\rm off2}$  behind  $v_{\rm ds3}$ , and the stack is changed to the status as depicted in Fig. 2-6(d). The overvoltage of  $v_{\rm ds3}$  is also prevented as it is clamped to  $V_{\rm lim}$ . After  $\Delta t_{\rm off1}$ ,  $v_{\rm ds1}$  will begin to increase as well, and the rising slopes of  $v_{\rm ds1}$  and  $v_{\rm ds2}$  can be calculated by Eq. (2-4). Similarly,  $dv_{\rm ds1}/dt$  is higher due to the absence of one charging/discharging branch, while both  $v_{\rm ds1}$  and  $v_{\rm ds2}$  will be limited to  $V_{\rm lim}$  as well. Finally, at  $t_{10}$ , the turning-off process of the stack is completed.

#### 2.2.3. AUTOMATIC BALANCING PROCESS AND NON-IDEAL FACTORS

Based on the above analysis, the VB of the stack is realized in both the turning-on and turning-off processes with the aid of the clamping circuit. To make it work effectively under the continuously switching process of the stack, not only should the voltage of  $C_{di}$  ( $i = 1 \sim 4$ ) be balanced, but also the charging of discharging should be balanced. Next, the explanation is given as follows.

As the stack is repeatedly switched on and off in this converter application, the switching delays of  $T_i$  ( $i = 1 \sim 4$ ) will cause the energy accumulation of  $C_{di}$ , and the energy  $\Delta E_i$  accumulated during one switching cycle can be expressed as:

$$\begin{cases} \Delta E_1 = V_{\text{lim}} I_{\text{L(on)}} (\Delta t_{\text{on1}} + \Delta t_{\text{on2}} + \Delta t_{\text{on3}}) \\ \Delta E_2 = V_{\text{lim}} I_{\text{L(on)}} (\Delta t_{\text{on1}} + \Delta t_{\text{on2}}) + V_{\text{lim}} I_{\text{L(off)}} \Delta t_{\text{off3}} \\ \Delta E_3 = V_{\text{lim}} I_{\text{L(on)}} \Delta t_{\text{on1}} + V_{\text{lim}} I_{\text{L(off)}} (\Delta t_{\text{off2}} + \Delta t_{\text{off3}}) \\ \Delta E_4 = V_{\text{lim}} I_{\text{L(off)}} (\Delta t_{\text{off1}} + \Delta t_{\text{off2}} + \Delta t_{\text{off3}}) \end{cases}$$

(2-5)

where the load currents during turning-on and turning-off are distinguished as  $I_{\text{L(on)}}$  and  $I_{\text{L(off)}} > I_{\text{L(on)}}$  (ignoring turning-on current overshoot). Since the self-powered APS is a high-input-voltage and low-output-power application, both  $I_{\text{L(off)}}$  and  $I_{\text{L(on)}}$  are small, and the magnitude of  $dv_{\text{dsi}}/dt$  during turning-on process is larger as compared to that during turning-off process. Further,  $\Delta t_{\text{oni}}$  and  $\Delta t_{\text{offi}}$  ( $i = 1 \sim 3$ ) can be obtained as:

$$\begin{cases} \Delta t_{\text{on}i} \approx \frac{C_{\text{in}i}(V_{\text{dd}} - V_{\text{ee}})}{i_{\text{g}i}} \approx \frac{C_{\text{in}i}(V_{\text{ee}} - V_{\text{dd}})(1/C_{\text{a}i} + 1/C_{\text{in}i})}{dV_{\text{ds}(i+1)}/dt}, i=1 \sim 3 \\ \Delta t_{\text{off}i} \approx \frac{C_{\text{in}i}(V_{\text{ee}} - V_{\text{dd}})}{i_{\text{g}i}} \approx \frac{C_{\text{in}i}(V_{\text{dd}} - V_{\text{ee}})(1/C_{\text{a}i} + 1/C_{\text{in}i})}{dV_{\text{ds}(i+1)}/dt}, i=1 \sim 3 \end{cases}$$

Consequently, it is concluded from Eq. (2-6) that  $\Delta t_{\rm offi}$  is much larger than  $\Delta t_{\rm oni}$ . Further, it is solved from Eq. (2-5) that  $\Delta E_4 > \Delta E_3 > \Delta E_2 > \Delta E_1$ , and it provides the prerequisite of the automatic VB process as illustrated below.

As depicted in Fig. 2-2, the automatic balancing RCD<sup>2</sup> circuit is made up of  $R_{\rm di}$  ( $i = 1 \sim 4$ ),  $C_{\rm di}$ ,  $D_{\rm di}$  and  $D_{\rm ci}$  ( $i = 1 \sim 3$ ). It generates extra current loops during the turning-on process of the stack, as depicted in Fig. 2-7(a). Since  $C_{\rm d4}$  stores the most energy as described above, when the voltage across  $C_{\rm d4}$  ( $v_{\rm cd4}$ ) becomes greater than that across  $C_{\rm ds3}$  ( $v_{\rm cd3}$ ),  $D_{\rm c3}$  will conduct during the on-state of  $T_4$  and bring  $v_{\rm cd4}$  and  $v_{\rm cd3}$  back to equality. Similarly,  $v_{\rm cdi}$  ( $i = 1 \sim 4$ ) across  $C_{\rm di}$  will be equalized during the on-state of the stack, making it easy to select  $R_{\rm di}$  which serves to consume  $\Delta E_i$ . In this way,  $v_{\rm cdi}$  across  $C_{\rm di}$  is kept at  $V_{\rm lim}$  by releasing accumulated  $\Delta E_i$  during each switching cycle. As a result,  $C_{\rm di}$  can be regarded as a constant voltage source, therefore, the proposed stack operates as intended.

Figure 2-7. (a) automatic balancing current loops (b) non-ideal reverse current loops

It has been known that using small resistors in well-known RCD snubbers to control SiC MOSFET switching transients and VB can result in significant additional losses. From this perspective, passive methods are not favored compared to active control methods with complex structure and control strategy. Instead, in the proposed topology, a large  $R_{di}$  is chosen to consume only a small amount energy  $\Delta E_i$  as per Eq. (2-5), and the parameter selection criteria are as follows:

In practical applications, it is not feasible to choose the largest possible value for  $C_{di}$  due to the associated increase in volume. Therefore, after  $v_{ds4}$  reaches  $V_{lim}$ ,  $dv_{ds4}/dt$  could be expressed as:

$$\frac{dv_{\text{ds4}}}{dt} \approx \frac{I_{\text{L(off)}}}{C_{\text{d4}} + C_{\text{od4}} + C_{\text{ds4}} + 1/(1/C_{\text{a3}} + 1/C_{\text{in3}})} \approx \frac{I_{\text{L(off)}}}{C_{\text{d4}}}.$$

(2-7)

Following a duration of  $t_{\text{sum}} = \Delta t_{\text{off3}} + \Delta t_{\text{off2}} + \Delta t_{\text{off1}}$ , it is anticipated that the increment of  $v_{\text{ds4}}$  will be a small value  $\Delta V$ , and it can be solved as:

$$\Delta V = \frac{dv_{\rm ds4}}{dt} t_{\rm sum} \approx \frac{I_{\rm L(off)} t_{\rm sum}}{C_{\rm A4}}$$

(2-8)

In Eq. (2-8), when  $\Delta V$  is defined in advance and  $I_{\text{L(off)}}t_{\text{sum}}$  is estimated,  $C_{\text{d4}}$  along with the same  $C_{\text{di}}$  ( $i = 1 \sim 3$ ) could be selected.

In Fig. 2-7(a), the equivalent discharging model of  $R_{di}C_{di}$  during the on-state can be simplified due to the negligible voltage drop of  $v_{Cdi}$  ( $i=1 \sim 4$ ). Based on the principle that  $v_{Cdi}$  returns to be  $V_{lim}$  after one switching cycle, the relationship exists as:

$$\frac{C_{di}[(\Delta V + V_{\lim})^2 - V_{\lim}^2]}{8} \approx \frac{T_{\text{on}}V_{\lim}^2}{R_{di}}, \quad i = 1 \sim 4.$$

(2-9)

where  $T_{\rm on}$  refers to the duration of the on-state within one switching cycle.

Once  $V_{\text{lim}}$  is defined and other parameters are determined,  $R_{\text{d}i}$  ( $i = 1 \sim 4$ ) can be selected as well using Eq. (2-9).

It is worthy of noting that the above analysis is conducted under ideal conditions. However, practical components used in real-world applications may not be ideal, and thus, necessitating their consideration. In selecting  $R_{di}$ , non-ideal components such as diodes can introduce additional energy consumption paths, making it possible to choose an even larger  $R_{di}$ . Additionally, two main influences must be considered:

(1) Due to the reverse recovery and parasitic capacitance of  $D_{ci}$  ( $i = 1 \sim 3$ ) during the turning-off process, it induces reverse current loops as depicted in Fig. 2-

- 7(b). Hence, it is necessary to include an additional discharging loop during the turning-off process of  $T_i$  ( $i = 2 \sim 4$ ), and Eq. (2-3) and Eq. (2-4) should be amended. As a result,  $v_{\rm dsi}/dt$  ( $i = 2 \sim 4$ ) will be smaller while  $v_{\rm dsl}/dt$  will remain unchanged, which may cause  $v_{\rm dsl}$  to increase to  $V_{\rm lim}$  earlier than  $v_{\rm ds2}$ .

- (2) Since the transformer and the diode D on the secondary side have parasitic capacitances, during the turning-on process of the stack, the high dv/dt will induce an additional current flowing through the stack, which could result in  $I_{L(on)}>I_{L(off)}$ .

According to Eq. (2-6), each of the aforementioned factors could result in a disagreement with the conclusion  $\Delta E_4 > \Delta E_3 > \Delta E_2 > \Delta E_1$  and have a negative impact on the proposed topology's VB. Therefore, a  $R_{g0}C_{a0}$  branch is placed in parallel with  $T_1$  additionally, as indicated by the dash line in Fig. 2-2. By reducing  $v_{ds4}/dt$  in this manner,  $\Delta E_4 > \Delta E_3 > \Delta E_2 > \Delta E_1$  can be assured and effective VB is achieved.

## 2.3. EXPERIMENTAL RESULTS IN SELF-POWERED AUXILARY POWER SUPPLY APPLICATION

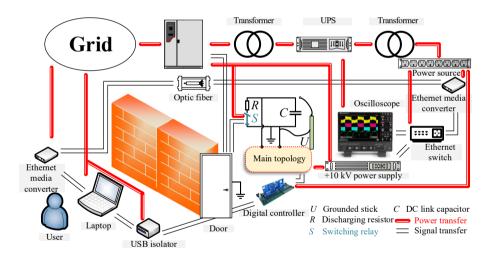

Figure 2-8. Diagram of medium voltage testing platform

The MV testing platform is built based on the diagram depicted in Fig. 2-8. To ensure the safety of conducting MV experiments, the device or circuitry under test is placed inside the cage, and the user is working outside with a laptop and corresponding communication system through optic fiber to realize remote control. The 10 kV adjustable DC power supply gets powered from the grid, and it outputs the expected MV input voltage for test. Since it charges the DC link capacitor C every time and the

remaining energy of C can be large when the test is finished, a discharging resistor R and a MV switching relay S are series-connected and then put in parallel with C to discharge the energy. S is triggered on/off every time when the door is open/close to assure safety of the user's inside operation, besides this, a grounded stick U should be put in physical contact with C to further assure the complete discharge of C before the inside operation. In addition, a digital controller is connected with the laptop through MV isolation to ensure online hardware control. Moreover, high-precision and high-bandwidth oscilloscope, high-voltage probe with differential isolation, low-voltage probe with optical isolation, high-voltage and low-voltage passive probe, current probe, etc. for measuring purposes are put inside the cage and remote recording of experimental data is achieved.

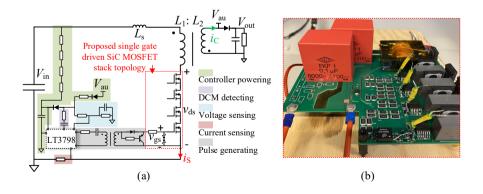

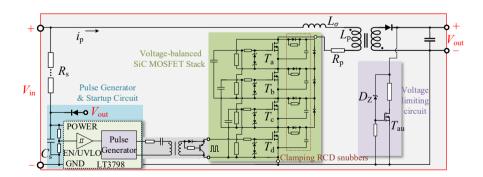

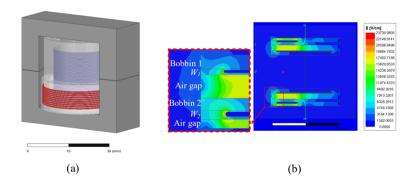

Based on the above, the proposed SiC MOSFET stack's experimental performance is further examined, where the complete self-powered APS schematic and the corresponding hardware photograph are shown in Fig. 2-9. Discontinuous current mode (DCM) is employed in this flyback topology by choosing LT3798 as the offline controller [43], which enables zero current switching (ZCS) of the MOSFETs during turning-on and ZCS of the diode during turning-off, and. It is essential to note that the proposed stack could suffer from temporary gate oscillations of upper devices due to the power loop voltage oscillation under the DCM condition of the flyback converter, and the consideration together with the detailed comparison to another type of single gate driver stack is provided in **Publication V**. Because LT3798 only provides +10 V / 0 V as the output, a circuitry for boosting pulse is added as depicted in the grey part in Fig. 2-9(a), and the driving voltage  $V_{\rm dd}/V_{\rm ee}$  of  $T_4$  becomes  $\pm 20~{\rm V}/0~{\rm V}$  which is suitable for SiC MOSFET. Besides this, the other colored parts in this self-powered APS including controller powering, DCM detecting, voltage sensing, and current sensing are dedicatedly designed for the normal operation, achieving the anticipated closed-loop control.

Figure 2-9. The self-powered auxiliary power supply: (a) schematic (b) photograph

| Name                                               | Parameter                |

|----------------------------------------------------|--------------------------|

| $T_i$ ( $i=1\sim4$ )                               | C2M1000170J (1.7 kV/5 A) |

| $D_{\mathrm{a}i}$ $(i=1\sim4)$                     | PTZ18B (18 V)            |

| $D_{\mathrm{b}i} \left( i = 1 \sim 4 \right)$      | TDZ6_2B (6.2 V)          |

| $D_{ci}$ ( $i=1\sim 3$ ), $D_{di}$ ( $i=1\sim 4$ ) | C5D05170H (1.7 kV/5 A)   |

| $R_{si}$ ( $i=1\sim4$ )                            | 500 kΩ                   |

| $R_{\mathrm{g}i}$ $(i=1\sim4)$                     | 20 Ω                     |

| $C_{ai}$ $(i=1\sim3)$                              | 47 pF                    |

| $C_{\mathrm{d}i}$ ( $i$ =1~4)                      | 50 nF                    |

Table 2-1. Parameters of components in the proposed SiC MOSFET stack

Figure 2-10. Overall performance of the self-powered auxiliary power supply

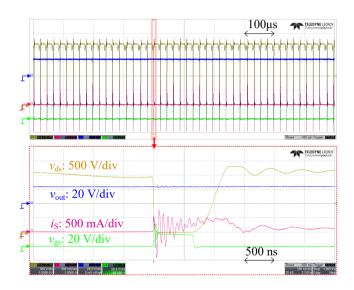

In the experiments, the parameter setting is listed in Table 2-1. With the expected output voltage  $V_{\rm out}$  set as 24 V, the performance of APS under the condition of the input voltage  $V_{\rm in}=2$  kV is shown in Fig. 2-10, and two oscillations of the voltage  $v_{\rm ds}$  across the stack can be observed. Occurrence of the first one is due to devices' output capacitances and the transformer leakage inductance, where the peak value of  $v_{\rm ds}$  is

clamped. Occurrence of the secondary one is due to devices' output capacitances and the transformer magnetizing inductance, as the secondary current  $i_{\rm C}$  approaches zero during every switching cycle. With the aid of the DCM detecting circuitry, when  $v_{\rm ds}$  rings to its valley, LT3798 sends the signal to turn on the stack in order to reduce the energy loss. It can be observed that  $v_{\rm ds}$  abruptly dips to zero from the waveform valley as the gate-source voltage  $v_{\rm gs}$  turns to +20 V and  $i_{\rm S}$  increases gradually from zero. After a while,  $v_{\rm gs}$  turns back to 0 V and  $v_{\rm ds}$  rises to the limiting value.

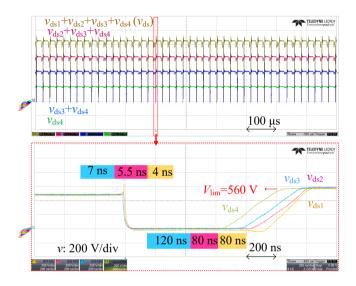

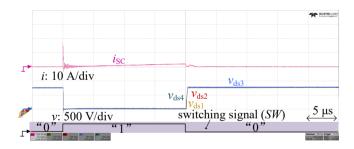

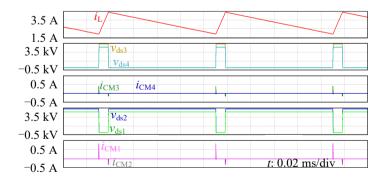

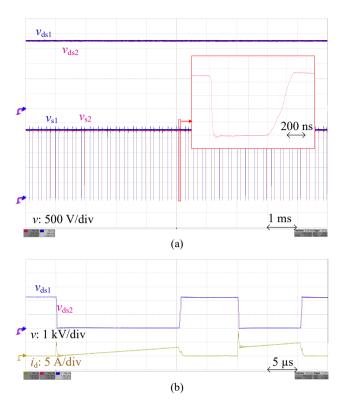

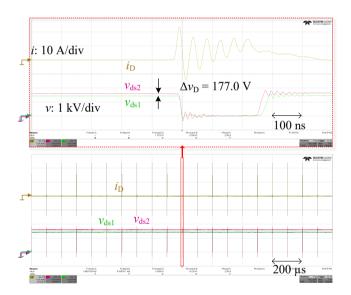

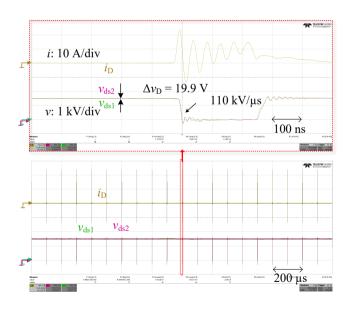

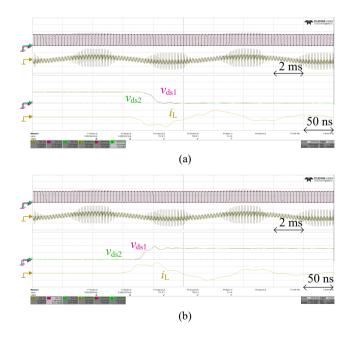

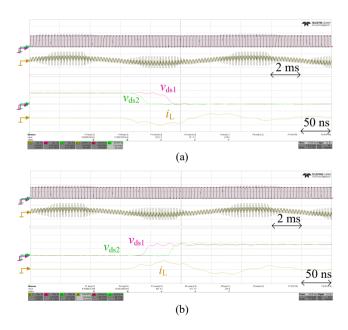

Figure 2-11. Voltage balancing performance of SiC MOSFETs in the proposed stack

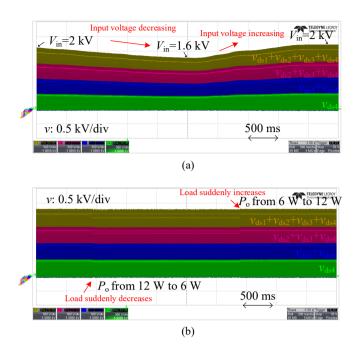

For the VB performance in the stack, the results are displayed in Fig. 2-11. During turning-on process, it is observed that  $v_{ds4}$  drops firstly, then  $v_{ds3}$ ,  $v_{ds2}$  and  $v_{ds1}$  with the sequential delays of 7 ns, 5.5 ns and 4 ns. During turning-off process,  $v_{ds4}$  is the first one to rise, followed by  $v_{ds3}$ ,  $v_{ds2}$  and  $v_{ds1}$  with the sequential delays of 120 ns, 80 ns and 80 ns. Most importantly, the voltages are limited at 560 V and good VB is performed in the stack. Additionally, Fig. 2-12 further presents the VB during the input voltage transient and output load transient to verify its robustness. As  $V_{in}$  is reduced from 2 kV to 1.6 kV and subsequently increased back to 2 kV in Fig. 2-12(a), the voltage across each SiC MOSFET in the stack remains evenly balanced. In Fig. 2-12(b), the output power  $P_0$  is abruptly reduced to 6 W from 12 W, and LT3798 makes the adjustment to decrease the switching frequency as the output power becomes lower. Despite this change, the voltages across the SiC MOSFETs remain well balanced. Following this,  $P_0$  is abruptly increased back to 12 W, and the switching frequency returns to be a higher value with good VB being observed. These results demonstrate the good performance of the stack under different circumstances.

Figure 2-12. Voltage balancing during (a) input voltage transient (b) output load transient

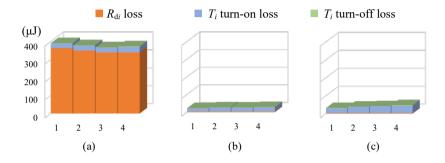

In addition, an experimental comparison is presented to demonstrate the proposed stack' advantages, in comparison to the clamping RCD snubber method and the active delay control method. As previously mentioned, the conventional method for driving  $T_i$  ( $i = 1 \sim 4$ ) in the stack necessities individual pulses for driving, resulting in the need for four sets of driving chips with the optic fiber isolations and four sets of isolated power supplies [44]. Despite delicately designing the gate loops to make them as identical as possible, voltage unbalancing still occurs. Adding clamping RCD snubber is considered as an approach for VB without the scarifying of switching speed of SiC MOSFET, besides this, actively adjusting the switching delay which requires the extra voltage feedback design can achieve the same goal. Comparatively, the proposed single gate-driven stack design is significantly simpler and only one set of driving chip, optic fiber, and isolated power supply is required. Hence, under the same testing condition and with the similar VB performance, the loss distributions of above three approaches are compared as shown in Fig. 2-13, and the detail regarding of parameters setting and switching waveforms are presented in **Publication IV**.

It is concluded that, with the clamping RCD snubber method, the losses of four groups are similar as illustrated in Fig. 2-13(a), including  $T_i$  turning-on loss, turning-off loss, and  $R_{di}$  loss. Importantly, it results in significant  $R_{di}$  ( $i = 1 \sim 4$ ) loss since  $C_{di}$  discharges through  $R_{di}$  during the entire on duration. On the other hand, the active

delay control method significantly reduces the loss comparatively, which is estimated to be 93.07% by adding up, as shown in Fig. 2-13(b). In contrast, the proposed method also significantly reduces the total loss compared to the clamping RCD snubber method as depicted in Fig. 2-13(c), which is estimated to be 89.45%. It should be noticed that, with the proposed method, the turning-on losses of  $T_2$ ,  $T_3$ , and  $T_4$  are similar while larger than  $T_1$  due to the automatic balancing process. Despite that the proposed stack incurs more loss compared to the active delay control method, the loss is not significant, and it is acceptable for high-voltage low-power applications. In return, the proposed stack significantly simplifies the gate driver design as well as the power loop VB design, and it becomes a cost-effective solution.

Figure 2-13. Loss distribution results with (a) the clamping RCD snubber method (b) the active delay control method (c) the proposed method

## CHAPTER 3. ANTI-SHORT CIRCUIT IMPROVEMENT OF THE SINGLE GATE-DRIVEN STACK

The information in this chapter is based on Publication II.

As introduced in Chapter 2, the single gate-driven SiC MOSFET stack offers the merit of being highly compact and low-cost. As a series structure, not only is the normal working principle significant, but also the short-circuit (SC) fault protection is crucial.

For a single SiC MOSFET against SC faults such as fault under load (FUL) and hard switch fault (HSF), extensive research has been conducted on the protection mechanisms. In [45], when SiC MOSFET enters its desaturation region after SC fault occurs, its on-state voltage drop is compared with a threshold to detect the SC fault, and then the protection is actively realized by pulling the driving signal to be "low". Due to the low cost and high robustness of this desaturation strategy, similar designs are commonly seen in various industries, but the requirement of a specific blanking time affects the action timeliness for protection. In [46], inside the SiC MOSFET module, a tunnel magnetoresistance is integrated in the package to directly sense the fault current, which is then regarded as the protection criterion. Additionally, there exist some indirect ways for obtaining the fault current by measuring the change rate of the drain current. For example, in [47], a Rogowski switch-current sensor is designed based on this principle, which is then placed in the power loop as a solution of current measurement. Comparatively, owing to the existence of parasitic inductance between the Kelvin source electrode (if applicable) and the power source electrode of the device, measuring the voltage drop across this inductor is a preferable method to make the estimation. To accomplish the SC fault identification, extra signal processing circuit is further required. In [48]-[49], resistive-capacitive (RC) and resistive-capacitive-diode (RCD) integrator circuits are respectively used to filter this voltage drop, and then the output voltage is compared with a preset threshold voltage. In [50], an additional quantity, the gate-source voltage of device, is further examined to better differentiate between the normal and SC states.

However, implementing the aforementioned SC protection strategies in a SiC MOSFET stack is questionable, since the voltage unbalancing of devices should be taken into consideration when the SC fault occurs [51]. Despite the fact that the short-circuit characteristics and protection of conventional stacks that have separated gate drivers (GDs) have already been studied [52]-[53], there has not been much research on the characteristics and protection in the occurrence of SC faults in single gate-driven stacks. Therefore, it is intensely valuable to fill this gap.

## 3.1. SHORT-CIRCUIT CHARACTERISTIC ANALYSIS OF THE SINGLE GATE-DRIVEN STACK

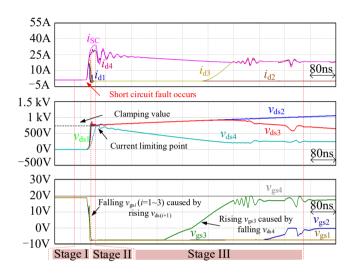

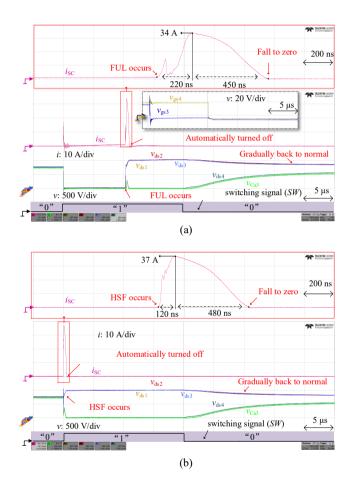

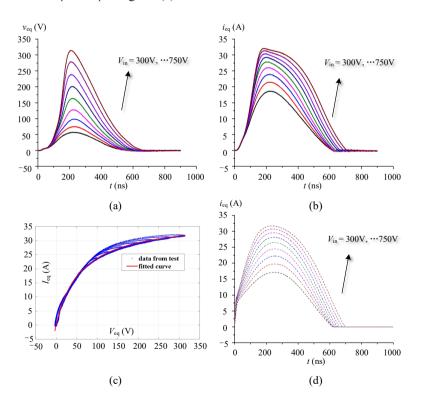

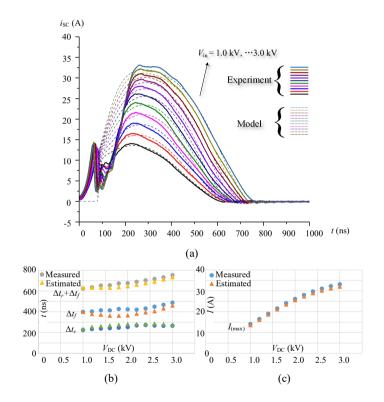

On the basis of the illustrated single gate-driven SiC MOSFET stack with associated clamping VB circuits depicted in Fig. 2-2, the simulated waveforms with the aid of LTspice software are shown to elaborate the SC mechanism of the stack when the FUL occurs. As presented in Fig. 3-1, it includes three working stages as follows.

Figure 3-1. Simulated waveforms of the single gate-driven stack in the FUL occurrence

**Stage I**: The stack functions as usual with a low current  $i_{SC}$  flowing through it in the beginning. However, when a SC fault occurs in the load side of some pulsed power application,  $i_{SC}$  experiences a sudden and significant increase. As  $T_i$  ( $i = 1 \sim 4$ ) enters its saturation region,  $v_{dsi}$  gets increased drastically. This relationship can be expressed as [54]-[56]:

$$i_{SC} = f(v_{gsi}, v_{dsi}, T_j) = f_1(v_{gsi}) \cdot f_2(T_j) \cdot \frac{p(v_{gsi}) \cdot v_{dsi}}{1 + q(v_{gsi}) \cdot v_{dsi}}$$

(3-1)

where  $f_1(v_{gsi})$  stands for the transfer characteristic parameter of device,  $f_2(T_j)$  stands for the parameter which indicates the influence of junction temperature  $T_j$  on  $i_{SC}$ , and  $p(v_{gsi})$  and  $q(v_{gsi})$  stand for the output characteristic parameters of device.

During this interval, the increasing of  $v_{ds(i+1)}$  will lead to the decreasing of  $v_{gsi}$  ( $i = 1 \sim 3$ ), which is similar to the working principle of the stack during the turning-off

process. As a consequence,  $T_4$  will stay in the saturation region to prevent the increase of  $i_{SC}$ , while  $T_i$  ( $i = 1 \sim 3$ ) will enter the cut-off region.

**Stage II:** As  $T_i$  ( $i = 1 \sim 3$ ) is gradually turned off, when  $v_{\rm dsi}$  ( $i = 1 \sim 3$ ) exceeds the voltage of the clamping capacitor  $C_{\rm di}$ ,  $i_{\rm SC}$  will commute to the clamping circuit. Correspondingly, the current  $i_{\rm di}$  ( $i = 1 \sim 3$ ) which flows through  $T_i$  will decrease to zero. Consequently, this feature causes  $T_i$  ( $i = 1 \sim 3$ ) only to tolerate a short time duration of SC (the time span in this simulation is less than 20 ns). Benefiting from the clamping circuit, the voltage unbalancing of  $v_{\rm dsi}$  ( $i = 1 \sim 3$ ) during the dynamic transient can be avoided despite the turning-off inconsistency by using single GD. Therefore,  $v_{\rm dsi}$  ( $i = 1 \sim 3$ ) will increase slowly afterwards, where the increasing rate is determined by  $C_{\rm di}$  the clamping capacitor and it is obtained as:

$$\frac{v_{\text{ds}i}}{dt} = \frac{i_{\text{SC}}}{C_{\text{di}}/3} \tag{3-2}$$

Instead, since  $T_4$  remains in its saturation region,  $v_{ds4}$  increases as  $i_{SC}$  goes up according to Eq. (3-1). At the end of this stage,  $i_{SC}$  reaches its maximum value.

**Stage III:** Despite  $T_4$  is turned on,  $T_i$  (i= 1 $\sim$  3) should be turned off in an automatic way. Since  $T_i$  (i= 1 $\sim$  4) is in a series stack, the SC current will start to decrease, which also represents the start of this stage. Eventually,  $T_1$ ,  $T_2$  and  $T_3$  should be capable to withstand the total bus voltage  $V_{\rm in}$  and cut off the SC current, which illustrates the potential capability of the single gate-driven stack to limit SC current.

However,  $v_{\rm ds4}$  also gets decreased as  $i_{\rm SC}$  decreases since  $T_4$  is still in the saturation region. It will result in the increase of  $v_{\rm gs3}$  again, followed by the turning on of  $T_3$  and increasing of  $i_{\rm d3}$ . After that, the increasing of  $v_{\rm gs2}$  can also occur. As a result of this unstable state,  $v_{\rm dsi}$  ( $i = 1 \sim 4$ ) will oscillate severely, and  $T_1$  could eventually withstand an unacceptably high voltage which violates the reliable functioning.

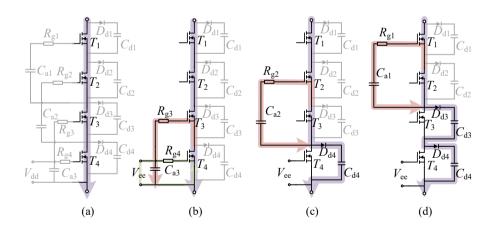

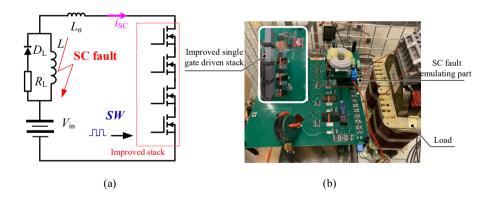

#### 3.2. ANTI-SHORT CIRCUIT IMPROVEMENT OF THE STACK

According to the above conclusion, despite that the single gate-driven stack can limit the overcurrent temporarily, it would be destroyed afterwards if no additional measure is taken. Therefore, an improvement can be made based on the assumption as: if  $v_{gsi}$  ( $i = 1 \sim 3$ ) could remain negative after its state is changed by the SC fault, the stack's advantageous potential of limiting the overcurrent could be fully unlocked.