# **Aalborg Universitet**

## A Novel Common-Ground-Type Nine-Level Dynamic Boost Inverter

Lee, Sze Sing; Siwakoti, Yam P.; Barzegarkhoo, Reza; Blaabjerg, Frede

Published in:

I E E E Journal of Emerging and Selected Topics in Power Electronics

DOI (link to publication from Publisher): 10.1109/JESTPE.2021.3104939

Publication date: 2022

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA): Lee, S. S., Siwakoti, Y. P., Barzegarkhoo, R., & Blaabjerg, F. (2022). A Novel Common-Ground-Type Nine-Level Dynamic Boost Inverter. *I E E E Journal of Emerging and Selected Topics in Power Electronics*, *10*(4), 4435 -4442. Article 9514540. https://doi.org/10.1109/JESTPE.2021.3104939

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

# A Novel Common-Ground-Type Nine-Level Dynamic Boost Inverter

Sze Sing Lee, Senior Member, IEEE, Yam P. Siwakoti, Senior Member, IEEE, Reza Barzegarkhoo, Student Member, IEEE, and Frede Blaabjerg, Fellow, IEEE

Abstract—Recently, inverters with a common ac and dc ground are gaining significant interests due to their zero common-mode voltage that made them particularly attractive for the solar photovoltaic (PV) application. However, the dc source current of the existing topologies is discontinuous, and their voltage gains are limited. This paper proposes a novel common-ground-type boost inverter that achieves continuous dc source current with significantly enhanced dynamic voltage gain. It consists of one boost inductor, four capacitors, nine power MOSFETs and two power diodes. Voltage-boosting and generation of 9-level ac voltage are achieved concurrently within a single-stage operation. The operation of the proposed CGT-9L-BI inverter is analyzed. Simulation and experimental results are presented for validation.

*Index Terms*— Boost inverter, common ground, multilevel inverter, nine level, single-stage.

#### I. INTRODUCTION

H indern power systems expedites the tremendous development of various power electronic converters [1]–[3]. The transformerless inverters, in particular, are steadily rising to become one of the prominent enabling technologies in integrating PV energy into power systems [4], [5]. These transformerless inverters does not require a bulky transformer and thereby enhances their compactness and power conversion efficiency. The absence of transformer in the configurations, however, unfavorably gives rise to insufficient voltage isolation between the PV source and the ac output. The resulting high-frequency common mode voltage (CMV) across the stray capacitor of PV modules will therefore induce the risk of leakage current [6].

The high-frequency CMV issue can be effectively counteracted in a neutral-point-clamped (NPC) inverter configuration. With the ac neutral grounded to the midpoint of dc-link, the stray capacitor of PV modules is clamped across the dc-link capacitor and thus preventing leakage current [7]. Nonetheless, the limited voltage gain and voltage levels are two main downsides of the classical NPC inverter [8]. With the maximum attainable voltage level of only half the dc-link voltage, high dc-link (dc source) voltage of at least twice the ac peak voltage is always mandatory. While high dc voltage requirement is mostly accompanied by an indispensable front-

end boost dc-dc converter, there has been a tendency in reducing the magnitude of dc source voltage in transformerless topologies.

In an attempt to realize a single-stage structure, significant efforts have been devoted on developing topologies based on H-bridge inverter which features unity gain, three levels generation, and a maximum voltage level equal to dc source voltage. As the neutral of ac output in a H-bridge inverter is connected to a half-bridge, some structural modifications are required to provide galvanic isolation between the PV source and ac output. For instance, it might requires the incorporation of either an additional dc-bypass circuit into its dc side or an additional ac-bypass circuit into its ac side, where either circuit consists of power switches and diodes [9]. Noting that high-frequency CMV remains an issue in H-bridge based topologies and therefore the establishment of complex modulation technique is essential [10].

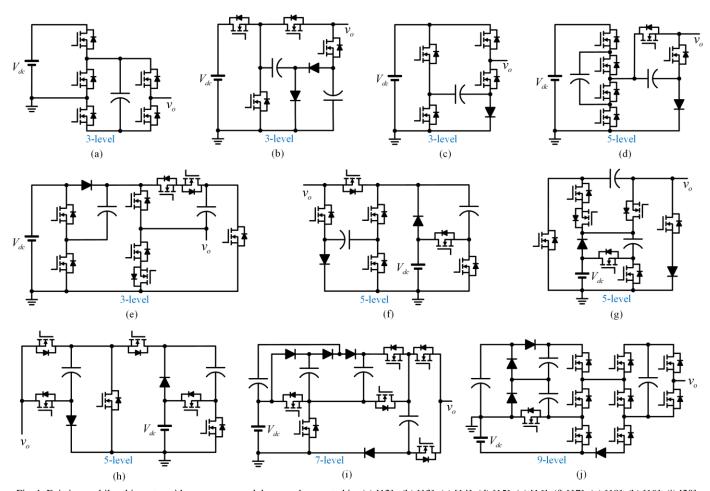

A new class of transformerless inverter with a common ac and dc ground has recently garnered increasing popularity. Effective CMV mitigation is achieved with its ac neutral grounded to the negative terminal of PV source [11]. To make the common ac and dc ground possible, [12] uses an electrolytic capacitor to establish the concept of virtual dc-bus, as shown in Fig. 1(a). The virtual dc-bus is charged to dc source voltage during the positive and zero voltage levels. Negative voltage level can be generated by reversing the polarity of the virtual dc-bus across the ac load. Note that the dc source is not utilized to supply the load during negative voltage level and hence its negative terminal can remain connected to the neutral of ac output. Similar concept is extended in [13] (Fig. 1(b)) where two capacitors are adopted to ensure sufficient energy storage to supply the load during negative voltage level and reduce the magnitude of voltage ripple. The various common-ground-type inverters which are capable of 3-level generation are summarized in [14]. Fig. 1(c) presented in [14] requires only one diode to be inserted into the second leg of an H-bridge that makes it the most compact 3-level topology.

An attempt to increase the number of levels generation from 3 to 5 is made in [15], as depicted in Fig. 1(d). It is a hybrid topology that replaces the first H-bridge leg of Fig. 1(c) with a flying capacitor inverter. In a separate attempt, voltage-

boosting is made possible by utilizing two SCs to realize a twofold voltage gain in Fig. 1(e) [16]. One of the SCs is charged to twice the dc source voltage magnitude so that the maximum voltage level is twice the dc source voltage. However, the number of ac voltage levels remains 3 despite the use of two capacitors.

In recent literature, the common-ground-type inverters have seen evolution in terms of their simultaneous achievement of 5-level voltage generation and double voltage gain [17]–[19]. Further enhancement in the voltage levels generation, such as 7-level and 9-level topology is also presented in [20] (Fig. 1(i)) and [21] (Fig. 1(j)), respectively.

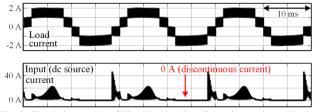

All the aforementioned common-ground-type inverters exhibit a common characteristic such that their dc sources are not fully exploited during some or all the negative voltage levels. A simulation study of Fig. 1(h) is conducted to investigate the consequence of disconnecting the dc source during some voltage levels. As shown in Fig. 2, the dc source current is discontinuous. This is a tradeoff of the common-

ground structure that hinders their application for PV system. Aiming to resolve this drawback, a novel topology is proposed in this paper and its key contributions can be summarized as follows:

- (a) A distinctive topological structure in accomplishing common ac and dc ground to enable leakage current mitigation.

- (b) Capability of nine symmetric voltage level generation with low number of power semiconductor devices.

- (c) Enhanced voltage boost capability for a single-stage dc-ac power conversion.

- (d) The provision of continuous dc source current to accommodate the PV source.

The remainder of this paper is organized as follows. In Section II, the steady-state analysis of the proposed topology is presented. Section III compares the proposed topology with the state-of-the-art common-ground-type inverters. Simulations and experimental results are discussed in Section IV. Finally, Section V concludes the article.

Fig. 1. Existing multilevel inverter with common ac and dc ground presented in: (a) [12], (b) [13], (c) [14], (d) [15], (e) [16], (f) [17], (g) [18], (h) [19], (i) [20], and (j) [21] (the common ac and dc ground is located at dc source positive terminal instead of negative terminal in all other topologies).

Fig. 2. Simulation results of Fig. 1(h) showing discontinuous input (dc source) current.

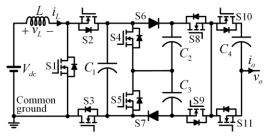

Fig. 3. Proposed common-ground-type nine-level boost inverter (CGT-9L-BI).

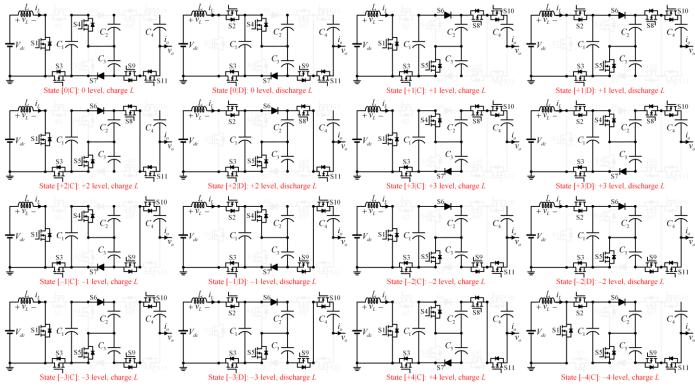

Fig. 4. Switching states of the proposed CGT-9L-BI.

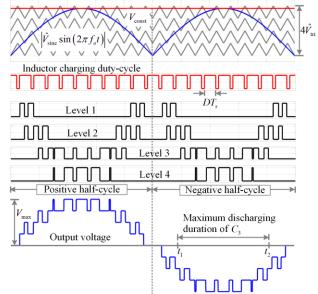

Fig. 5. Multicarrier PWM for the proposed CGT-9L-BI.

TABLE I. SUMMARY OF SWITCHING STATES

| State             | S1 – S11    | Inductor    | Voltage level             |  |

|-------------------|-------------|-------------|---------------------------|--|

| [0 C]             | 10110010101 | charging    | 0                         |  |

| $[0 \mathbf{D}]$  | 01110010101 | discharging | U                         |  |

| [+1 C]            | 10101101010 | charging    | $+0.25V_{\text{max}}$     |  |

| [+1 D]            | 01101101010 | discharging | $\pm 0.23 V_{\text{max}}$ |  |

| [+2 C]            | 10101101001 | charging    | .0.5W                     |  |

| $[+2 \mathbf{D}]$ | 01101101001 | discharging | $+0.5V_{\rm max}$         |  |

| [+3 C]            | 10110011010 | charging    | $+0.75V_{\text{max}}$     |  |

| [+3 D]            | 01110011010 | discharging | $+0.75 V_{\text{max}}$    |  |

| [+4 C]            | 10110011001 | charging    | $+V_{ m max}$             |  |

| [-4 C]            | 11001100101 | charging    | $-V_{ m max}$             |  |

| [-3 C]            | 10101100110 | charging    | 0.751/                    |  |

| [-3 D]            | 01101100110 | discharging | $-0.75V_{\mathrm{max}}$   |  |

| [-2 C]            | 10101100101 | charging    | 0.51/                     |  |

| $[-2 \mathbf{D}]$ | 01101100101 | discharging | $-0.5V_{\mathrm{max}}$    |  |

| [-1 C]            | 10110010110 | charging    | $-0.25V_{\text{max}}$     |  |

| [-1 D]            | 01110010110 | discharging | -0.23 V max               |  |

#### II. PROPOSED CGT-9L-BI

Fig. 3 shows the circuit diagram of the proposed topology that consists of a boost inductor, four capacitors, nine power MOSFETs, and two power diodes. Note that the power diodes can also be replaced with power MOSFETs operating in synchronous rectification mode. This topology is uniquely designed to provide a common ground for dc source and ac output.

### A. Switching States

The equivalent circuit of each switching state is shown in Fig. 4 and summarized in Table I. The proposed CGT-9L-BI is capable of generating nine symmetrical voltage levels. While generating ac voltage, the boost inductor can be simultaneously charged by the dc source to boost the voltages across capacitors  $C_1$ ,  $C_2$  and  $C_3$ . The voltages of all the capacitors are naturally balanced.

#### B. Multicarrier Pulse-Width Modulation (PWM)

Multicarrier PWM as shown in Fig. 5 is developed to control the proposed CGT-9L-BI. By charging the boost inductor L with a constant duty-cycle D, the voltage of capacitors  $C_1 - C_3$  can be boosted to

$$V_{C_1} = V_{C_2} = V_{C_3} = \frac{1}{1 - D} V_{dc}$$

(1)

Compared to these three capacitors, the voltage of  $C_4$  is halved. Referring to Fig. 4, the maximum voltage level  $V_{\text{max}}$  is

$$V_{\text{max}} = \frac{2}{1 - D} V_{dc} \,. \tag{2}$$

The peak of fundamental ac voltage  $\hat{V}_{o,1}$  can be controlled by the modulation index M,

$$\hat{V}_{o,1} = MV_{\text{max}} = \frac{2M}{1 - D} V_{dc} \,. \tag{3}$$

Therefore, the voltage gain of the proposed topology can be written as

$$G = \frac{\hat{V}_{o,1}}{V_{dc}} = \frac{2M}{1 - D} \,. \tag{4}$$

#### C. Design of Passive Components

Passive components can be calculated based on their ripple magnitude. Four capacitors with the same capacitance C are considered. Considering the maximum discharging duration of  $C_3$  depicted in Fig. 5, the capacitor voltage ripple can be derived by solving

$$\left| \int_{t_1}^{t_2} \hat{I}_{o,1} \sin(\omega t) dt \right| = C \Delta V_C \tag{5}$$

that gives

$$\Delta V_C = \left| \frac{2\hat{I}_{o,1}}{\omega C} \cos(\omega t_1) \right| \tag{6}$$

where  $\Delta V_C$  is capacitor voltage ripple and  $\hat{I}_{o,1}$  is the peak of load current at unity power factor.

The current ripple of boost inductor consists of low-frequency and high-frequency components due to the single-phase load and PWM, respectively. Assuming that the capacitor voltage ripple is sinusoidal and the dc source is ideal without low-frequency ripple, the low-frequency voltage across the inductor can be obtained for calculating its current ripple:

$$\Delta I_{L,LF} = \frac{(1-D)\Delta V_C}{\omega L} \tag{7}$$

where  $\Delta I_{L,LF}$  is the low-frequency current ripple of boost inductor. Considering volt-second balance of the inductor for each triangular carrier period, the high-frequency current ripple is

$$\Delta I_{L,HF} = \frac{DV_{dc}}{f.L} \tag{8}$$

where  $f_s$  denotes the frequency of triangular carrier.

# III. COMPARISON WITH EXISTING COMMON-GROUND-TYPE MULTILEVEL INVERTERS

Table II summarizes the comparison of the proposed topology with the state-of-the-art common-ground-type inverters. Observations shows that the proposed CGT-9L-BI outperforms others such that it demonstrates the greatest number of voltage level generation (9 levels) and highest voltage boosting gain. Moreover, it exhibits the highest utilization ratio of power semiconductor devices, as can be seen from its lowest  $(N_{S+D})/N_L$  ratio of only 1.2. This indicates that the proposed topology requires the least number of power semiconductor devices to generate each level. The most noteworthy advantage of the proposed topology is that it has overcome the problem associated with discontinuous input current in the existing common-ground-type inverters. Continuous dc source current is guaranteed in the proposed topology, this implies that it is the best common-ground-type inverter for PV application.

TABLE II

COMPARISON BETWEEN THE PROPOSED CGT-9L-BI AND THE EXISTING

COMMON-GROUND-TYPE INVERTERS

| COMMON-GROUND-TITE INVERTERS |            |            |                  |             |                       |                  |     |

|------------------------------|------------|------------|------------------|-------------|-----------------------|------------------|-----|

| Topology                     | $N_{ m L}$ | $N_{ m S}$ | $N_{\mathrm{D}}$ | $N_{\rm C}$ | $(N_{S+D})/N_{\rm L}$ | $\boldsymbol{G}$ | CIC |

| Fig. 1(a)                    | 3          | 5          | _                | 1           | 1.7                   | M                | No  |

| <b>Fig. 1(b)</b>             | 3          | 4          | 2                | 2           | 2.0                   | M                | No  |

| <b>Fig. 1(c)</b>             | 3          | 4          | 1                | 1           | 1.7                   | M                | No  |

| <b>Fig. 1(d)</b>             | 5          | 6          | 1                | 2           | 1.4                   | M                | No  |

| <b>Fig. 1(e)</b>             | 3          | 8          | 1                | 2           | 3.0                   | 2 <i>M</i>       | No  |

| <b>Fig. 1</b> ( <b>f</b> )   | 5          | 6          | 2                | 2           | 1.6                   | 2 <i>M</i>       | No  |

| <b>Fig. 1(g)</b>             | 5          | 7          | 2                | 2           | 1.8                   | 2 <i>M</i>       | No  |

| <b>Fig. 1(h)</b>             | 5          | 6          | 2                | 2           | 1.6                   | 2 <i>M</i>       | No  |

| Fig. 1(i)                    | 7          | 6          | 4                | 4           | 1.4                   | 3 <i>M</i>       | No  |

| <b>Fig. 1(j)</b>             | 9          | 9          | 4                | 4           | 1.4                   | 4M               | No  |

| CGT-9L-BI                    | 9          | 9          | 2                | 4           | 1.2                   | 2M/(1-D)         | Yes |

$N_{\rm L}$  = number of levels,  $N_{\rm S}$  = number of switches,  $N_{\rm D}$  = number of diodes,  $N_{\rm C}$  = number of capacitors,  $N_{\rm S+D} = N_{\rm s} + N_{\rm D}$  (total number of switches and diodes), G = voltage gain, M = modulation index, D = duty-cycle, CIC = continuous input current.

Fig. 6. Experimental setup.

#### TABLE III.

| PARAMETERS OF THE EXPERIMENTAL SETUP |         |  |  |  |

|--------------------------------------|---------|--|--|--|

| Component                            | Value   |  |  |  |

| DC source $V_{\rm dc}$               | 18 V    |  |  |  |

| Boost inductor L                     | 2 mH    |  |  |  |

| Capacitor C                          | 1000 μF |  |  |  |

| Carrier frequency $f_s$              | 5 kHz   |  |  |  |

| Output frequency $f_0$               | 50 Hz   |  |  |  |

| Load resistor                        | 100 Ω   |  |  |  |

| Load inductor                        | 100 mH  |  |  |  |

|                                      |         |  |  |  |

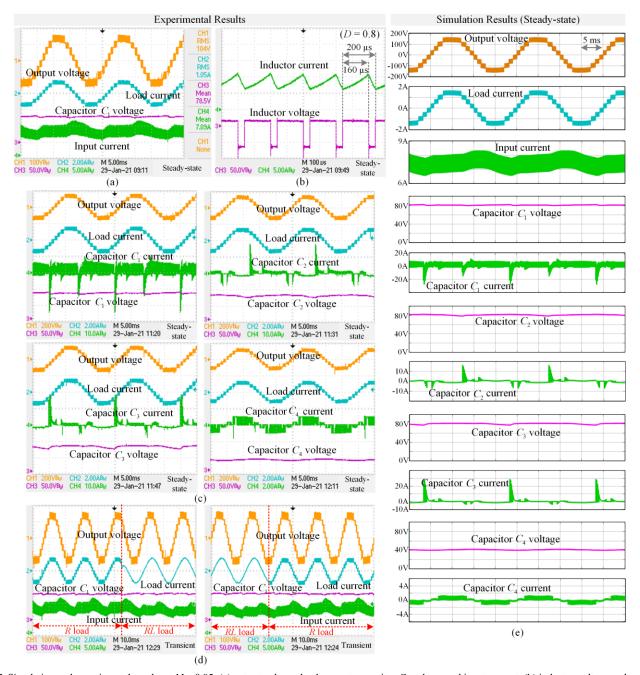

Fig. 7. Simulation and experimental results at M = 0.95: (a) output voltage, load current, capacitor  $C_1$  voltage and input current, (b) inductor voltage and current, (c) voltage and current of each capacitor, (d) output voltage, load current, capacitor  $C_1$  voltage and input current during transient response, and (e) simulation results for comparison with the experimental results.

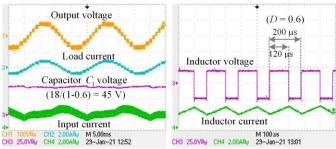

Fig. 8. Experimental results at M = 0.9.

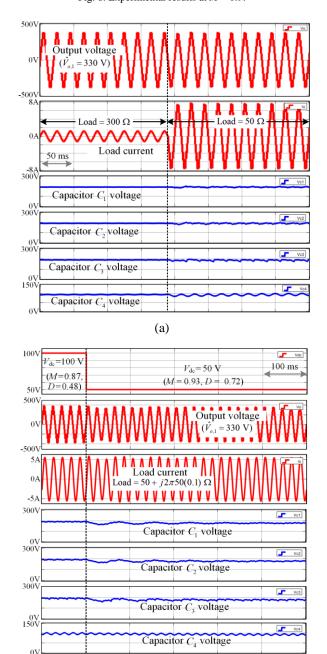

Fig. 9. Dynamic response of the proposed CGT-9L-BI illustrating the self voltage balancing ability of the capacitors: (a) step change in load current, and (b) step change in dc source voltage and modulation index.

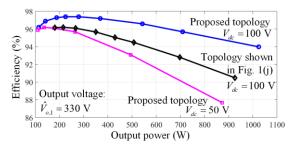

Fig. 10. Simulated efficiency of the proposed topology and comparison with the latest counterpart shown in Fig. 1(j) [21].

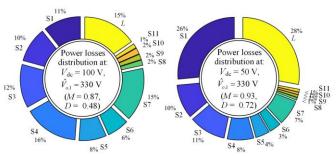

Fig. 11. Power losses distribution of the proposed topology at different input voltage.

#### IV. SIMULATION AND EXPERIMENTAL RESULTS

To validate the operation of the proposed CGT-9L-BI, an experimental prototype as depicted in Fig. 6 was tested. The parameters are summarized in Table III. Practical results measured from experimental tests are compared with simulation results in Fig. 7.

It can be seen that the boost inductor is charged with D = 0.8 and the voltages across capacitors  $C_1$ ,  $C_2$  and  $C_3$  are boosted to approximately 80 V from the 18-V dc source. Nine symmetrical levels are clearly observed between 160 V to - 160 V. Measurement shows that the RMS value of ac voltage is 104 V, which implies that the peak of ac voltage is 147 V. A voltage gain that exceeds 8 confirms the high voltage-boosting capability of the proposed CGT-9L-BI that enables its single-stage dc-ac inversion. All the measured waveforms are in good agreement with the simulated waveforms, thus validating the operation of the proposed topology.

Transient response of the experimental prototype was also tested. As illustrated in Fig. 7(d), the load current changes instantly when the load is switched from purely resistive R to series resistive-inductive RL load and vice-versa. The 9-level waveform of the ac output voltage is maintained without any deterioration during the load transient. Fig. 8 shows the measured waveforms at different modulation index, i.e. M=0.9. It is worth emphasized that continuous dc source current is assured in all modulation indexes because the boost inductor is charged by the dc source with constant duty-cycle. Due to single-phase load, low-frequency current ripple can be observed at the dc source side. Power decoupling control schemes for mitigating this low-frequency ripple can be referred to comprehensive studies presented in [22]–[24].

Although the experimental prototype is tested at low power, the dc source current has reached to the 10 A limit of the dc power supply, as shown in Fig. 7. Therefore, results for higher power level are obtained by simulations. Fig. 9(a) shows the transient response of the proposed topology during step load changes from 300  $\Omega$  to 50  $\Omega$ . At output voltage of approximately 230 V (RMS), the amplitude of load current increases 6 times from 1.28 A to 7.7 A without deteriorating the waveform of ac voltage. When load current is increased, higher voltage ripple is observed in all capacitors. However, their average voltage is naturally balanced. By charging the boost inductor L at a constant duty-cycle of 0.48, the average voltage of each  $C_1$ ,  $C_2$  and  $C_3$  is boosted to approximately 192 V (100/(1-0.48)). The capacitor  $C_4$  is a flying capacitor that achieves naturally balancing for its voltage via load current. Step change in dc source voltage from 100 V to 50 V is also simulated, as shown in Fig. 9(b). To maintain the output voltage at rated value, twofold voltage gain can be achieved by increasing M to 0.93. Therefore, D is increased to 0.72 that generates 179 V across  $C_1$ ,  $C_2$  and  $C_3$ .

Fig. 10 continues to investigate the efficiency of the proposed topology by modeling the experimental prototype in simulation. Considering a peak ac output voltage of 330 V and dc source voltages of 100 V and 50 V, peak efficiency exceeding 96% can be achieved from the proposed topology. To compare the efficiency of the proposed CGT-9L-BI with the latest counterpart, the 9-level topology in the same family of common-ground-type inverters depicted in Fig. 1(j) [21] is also simulated. For fair comparison, power devices with the same characteristic as that used in the proposed topology are considered. As the voltage gain of Fig. 1(j) [21] is limited to 4, it cannot generate 330 V (peak) from a 50-V dc source. Therefore, only 100-V dc source is simulated with M = 0.825(peak ac voltage of Fig. 1(j) =  $4MV_{dc}$  = 330 V). The efficiency comparison at  $V_{dc} = 100 \text{ V}$  in Fig. 10 clearly shows the advantage of the proposed CGT-9L-BI. In addition, the proposed topology also achieves higher voltage gain and continuous dc source current that is more attractive for PV application.

The power losses distribution of the proposed topology is also analyzed, as shown in Fig. 11. At lower dc source voltage, higher voltage gain is achieved by increasing the constant duty-cycle D that charges the boost inductor L. Due to higher dc source current, the power losses of inductor and S1 are more significant at lower dc source voltage.

#### V. CONCLUSION

A novel common-ground-type nine-level boost inverter has been proposed in this paper. As compared to other existing common-ground-type inverters, the proposed topology demonstrates significant improvement from three aspects, i.e. greater voltage level generation (9-level) with minimal power switch count, higher voltage-boosting gain, and continuous input current to cater for PV application. The drawback of discontinuous dc source current in the existing topologies has been resolved. The operation of the proposed topology has

been analyzed and validated through simulations and experimental tests. Good agreement can be found among the theoretical analysis, simulations, and experimental results.

#### REFERENCES

- [1] M. Liserre, T. Sauter, and J. Y. Hung, "Future Energy Systems: Integrating Renewable Energy Sources into the Smart Power Grid Through Industrial Electronics," *IEEE Ind. Electron. Mag.*, vol. 4, no. 1, pp. 18–37, 2010.

- [2] J. M. Carrasco *et al.*, "Power-Electronic Systems for the Grid Integration of Renewable Energy Sources: A Survey," *IEEE Trans. Ind. Electron.*, vol. 53, no. 4, pp. 1002–1016, 2006.

- [3] S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, "A review of single-phase grid-connected inverters for photovoltaic modules," *IEEE Trans. Ind. Appl.*, vol. 41, no. 5, pp. 1292–1306, 2005.

- [4] M. N. H. Khan, M. Forouzesh, Y. P. Siwakoti, L. Li, T. Kerekes, and F. Blaabjerg, "Transformerless Inverter Topologies for Single-Phase Photovoltaic Systems: A Comparative Review," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 8, no. 1, pp. 805–835, 2020.

- [5] H. Xiao, "Overview of Transformerless Photovoltaic Grid-Connected Inverters," *IEEE Trans. Power Electron.*, vol. 36, no. 1, pp. 533–548, 2021.

- [6] G. E. Valderrama, G. V. Guzman, E. I. Pool-Mazún, P. R. Martinez-Rodriguez, M. J. Lopez-Sanchez, and J. M. S. Zuñiga, "A Single-Phase Asymmetrical T-Type Five-Level Transformerless PV Inverter," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 6, no. 1, pp. 140–150, 2018.

- [7] S. Kouro, J. I. Leon, D. Vinnikov, and L. G. Franquelo, "Grid-Connected Photovoltaic Systems: An Overview of Recent Research and Emerging PV Converter Technology," *IEEE Ind. Electron. Mag.*, vol. 9, no. 1, pp. 47–61, 2015.

- [8] S. S. Lee, C. S. Lim, and K.-B. Lee, "Novel Active-Neutral-Point-Clamped Inverters With Improved Voltage-Boosting Capability," *IEEE Trans. Power Electron.*, vol. 35, no. 6, pp. 5978–5986, 2020.

- [9] T. K. S. Freddy, N. A. Rahim, W.-P. Hew, and H. S. Che, "Comparison and Analysis of Single-Phase Transformerless Grid Connected PV Inverters," *IEEE Trans. Power Electron.*, vol. 29, no. 10, pp. 5358– 5369, 2014.

- [10] T. K. S. Freddy, J.-H. Lee, H.-C. Moon, K.-B. Lee, and N. A. Rahim, "Modulation Technique for Single-Phase Transformerless Photovoltaic Inverters With Reactive Power Capability," *IEEE Trans. Ind. Electron.*, vol. 64, no. 9, pp. 6989–6999, 2017.

- [11] S. S. Lee, Y. Yang, and Y. P. Siwakoti, "A Novel Single-Stage Five-Level Common-Ground-Boost-Type Active Neutral-Point-Clamped (5L-CGBT-ANPC) Inverter," *IEEE Trans. Power Electron.*, vol. 36, no. 6, pp. 6192–6196, 2021.

- [12] Y. Gu, W. Li, Y. Zhao, B. Yang, C. Li, and X. He, "Transformerless Inverter With Virtual DC Bus Concept for Cost-Effective Grid Connected PV Power Systems," *IEEE Trans. Power Electron.*, vol. 28, no. 2, pp. 793–805, 2013.

- [13] J. Fallah ardashir, M. Sabahi, S. H. Hosseini, F. Blaabjerg, E. Babaei, and G. B. Gharehpetian, "Transformerless Inverter with Charge Pump Circuit Concept for PV Application," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 64, no. 7, pp. 5403–5415, 2016, doi: 10.1109/JESTPE.2016.2615062.

- [14] Y. P. Siwakoti and F. Blaabjerg, "Common-Ground-Type Transformerless Inverters for Single-Phase Solar Photovoltaic Systems," *IEEE Trans. Ind. Electron.*, vol. 65, no. 3, pp. 2100–2111, 2018.

- [15] F. B. Grigoletto, "Five-Level Transformerless Inverter for Single-Phase Solar Photovoltaic Applications," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 8, no. 4, pp. 3411–3422, 2020.

- [16] N. Vosoughi, S. H. Hosseini, and M. Sabahi, "A New Single Phase Transformerless Grid Connected Inverter with Boosting Ability and Common Ground Feature," *IEEE Trans. Ind. Electron.*, vol. 67, no. 11, pp. 9313–9325, 2020.

- [17] N. Vosoughi, S. H. Hosseini, and M. Sabahi, "A New Transformer-Less Five-Level Grid-Tied Inverter for Photovoltaic Applications," *IEEE Trans. Energy Convers.*, vol. 35, no. 1, pp. 106–118, 2020.

- [18] R. Barzegarkhoo, Y. P. Siwakoti, and F. Blaabjerg, "A New Switched-

- Capacitor Five-Level Inverter Suitable for Transformerless Grid-Connected Applications," *IEEE Trans. Power Electron.*, vol. 35, no. 8, pp. 8140–8153, 2020.

- [19] R. Barzegarkhoo, Y. P. Siwakoti, N. Vosoughi, and F. Blaabjerg, "Six-Switch Step-up Common-Grounded Five-Level Inverter with Switched-Capacitor Cell for Transformerless Grid-Tied PV Applications," *IEEE Trans. Ind. Electron.*, vol. 68, no. 2, pp. 1374–1387, 2021.

- [20] M. Chen, P. C. Loh, Y. Yang, and F. Blaabjerg, "A Six-Switch Seven-Level Triple-Boost Inverter," *IEEE Trans. Power Electron.*, vol. 36, no. 2, pp. 1225–1230, 2021.

- [21] M. Chen, Y. Yang, P. C. Loh, and F. Blaabjerg, "A Single-Source Nine-Level Boost Inverter with A Low Switch Count," *IEEE Trans. Ind. Electron.*, 2021.

- [22] Y. Tang and F. Blaabjerg, "Power decoupling techniques for singlephase power electronics systems — An overview," in 2015 IEEE Energy Conversion Congress and Exposition (ECCE), 2015, pp. 2541–2548.

- [23] L. Zhang and X. Ruan, "Control Schemes for Reducing Second Harmonic Current in Two-Stage Single-Phase Converter: An Overview From DC-Bus Port-Impedance Characteristics," *IEEE Trans. Power Electron.*, vol. 34, no. 10, pp. 10341–10358, 2019.

- [24] L. Zhang, X. Ruan, and X. Ren, "Second-Harmonic Current Reduction for Two-Stage Inverter With Boost-Derived Front-End Converter: Control Schemes and Design Considerations," *IEEE Trans. Power Electron.*, vol. 33, no. 1, pp. 6361–6378, 2018.

Sze Sing Lee (Senior Member, IEEE) received the B.Eng. (Hons.) and Ph.D. degrees in electrical engineering from Universiti Sains Malaysia, Malaysia, in 2010 and 2013, respectively.

He is currently an Assistant Professor with Newcastle University, Singapore. From 2014 to 2019, he was a Lecturer / Assistant Professor with the branch campus of University of Southampton

in Malaysia. From 2018 to 2019, he was a Visiting Research Professor with Ajou University, South Korea. His research interests include power converter / inverter topologies and their control strategies.

Dr. Lee was the recipient of the Outstanding Reviewer Award from the IEEE TRANSACTIONS ON POWER ELECTRONICS in 2020. He is an Associate Editor of the IEEE ACCESS.

Yam P. Siwakoti (S'10–M'14–SM'18) received the B.Tech. degree in electrical engineering from the National Institute of Technology, Hamirpur, India, in 2005, the M.E. degree in electrical power engineering from the Norwegian University of Science and Technology, Trondheim, Norway, and Kathmandu University, Dhulikhel, Nepal, in

2010, and the Ph.D. degree in Electronic Engineering from Macquarie University, Sydney, Australia, in 2014.

He was a postdoctoral fellow at the Department of Energy Technology, Aalborg University, Denmark (2014-2016). He was a visiting scientist at the Fraunhofer Institute for Solar Energy Systems, Freiburg, Germany (2017/2018). He is also a recipient of the prestigious Green Talent Award from the Federal Ministry of Education and Research, Germany in 2016.

Currently he is a Senior Lecturer in the Faculty of Engineering and Information Technology, University of Technology Sydney, Australia. He serves as an Associate Editor of three major journals of IEEE (IEEE Transactions on Power Electronics, IEEE Transactions on Industrial Electronics and IEEE Journal of Emerging and Selected Topics in Power Electronics) and the IET Power Electronics. He is also a peer review college member of Engineering and Physical Science Research Council (EPSRC), UK.

Reza Barzegarkhoo (S'19) received the B.S. degree in Electrical Power Engineering from the University of Guilan, Rasht, Iran, in 2010, and the M.S. degree in Electrical Power Engineering from the Sahand University of Technology (SUT), Tabriz, Iran, in 2012. He is currently working toward the Ph.D. degree in Electrical Power Engineering in the Faculty of Engineering and Information Technology,

University of Technology Sydney (UTS), Sydney, Australia.

His main research interests include the design and control of power electronic converters, multilevel voltage source inverters, charge balancing control, switched-capacitor and switched-boost converters, photovoltaic transformerless grid-tied ac modules, and distributed generation systems.

Mr. Barzegarkhoo has authored/co-authored more than 30 journal/conference peer-review papers in the area of Power Electronics. He also serves as a frequent Reviewer of different IEEE journals. He was selected as Distinguished Reviewer of 2020 by the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS (TIE). He is the winner of IEEE Industrial Electronics Society (IES) Inter Chapter Paper competition with the theme of "Smart Connected Community" in 2021.

Frede Blaabjerg (S'86–M'88–SM'97–F'03) was with ABB-Scandia, Randers, Denmark, from 1987 to 1988. From 1988 to 1992, he got the PhD degree in Electrical Engineering at Aalborg University in 1995. He became an Assistant Professor in 1992, an Associate Professor in 1996, and a Full Professor of power electronics and drives in 1998. From 2017 he became a Villum Investigator. He is honoris causa at University Politehnica Timisoara (UPT), Romania and Tallinn

Technical University (TTU) in Estonia.

His current research interests include power electronics and its applications such as in wind turbines, PV systems, reliability, harmonics and adjustable speed drives. He has published more than 600 journal papers in the fields of power electronics and its applications. He is the co-author of four monographs and editor of ten books in power electronics and its applications.

He has received 33 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award in 2009, the EPE-PEMC Council Award in 2010, the IEEE William E. Newell Power Electronics Award 2014, the Villum Kann Rasmussen Research Award 2014, the Global Energy Prize in 2019 and the 2020 IEEE Edison Medal. He was the Editor-in-Chief of the IEEE TRANSACTIONS ON POWER ELECTRONICS from 2006 to 2012. He has been Distinguished Lecturer for the IEEE Power Electronics Society from 2005 to 2007 and for the IEEE Industry Applications Society from 2010 to 2011 as well as 2017 to 2018. In 2019-2020 he served as a President of IEEE Power Electronics Society. He has been Vice-President of the Danish Academy of Technical Sciences.

He is nominated in 2014-2020 by Thomson Reuters to be between the most 250 cited researchers in Engineering in the world.