### **Aalborg Universitet**

### Model-Based Design for Reactors of the Modular Multilevel Converter

Zhang, Yi; Xu, Yi; Saeedifard, Maryam

Published in: IEEE Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2023.3257087

Publication date: 2023

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Zhang, Y., Xu, Y., & Saeedifard, M. (2023). Model-Based Design for Reactors of the Modular Multilevel Converter. *IEEE Transactions on Power Electronics*, 38(6), 6863-6873. https://doi.org/10.1109/TPEL.2023.3257087

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: December 05, 2025

# Model-Based Design for Reactors of the Modular Multilevel Converter

Yi Zhang (1), Member, IEEE, Yi Xu, and Maryam Saeedifard (1), Fellow, IEEE

Abstract—For complex power electronic converters, typical design approaches divide the system into multiple independent subsystems without sufficiently considering the interactions among them. In this paper, a model-based approach for sizing the reactors of the modular multilevel converter (MMC) is proposed. The proposed method quantitatively considers the interactions between the reactor sizing and other design parameters, such as power ratings, protection schemes, and component-level shortcircuit capabilities. Meanwhile, three deterministic factors are provided in this paper for sizing reactors to ensure enough robustness during extreme situations instead of the heuristic factor in the existing work. The quantified interactions presented in this paper also reveal that a proper over-rating of the active components is able to reduce reactance, increase efficiency, and improve power density. The proposed method not only serves as a quantitative design tool for the MMC, but also emphasizes the significance of the modeling of the interactions in the modelbased design. Finally, the effectiveness of the proposed method is validated by simulations and experiments. This paper is also accompanied by software codes for reproducibility.

Index Terms—Limiting reactor, model-based design, modular multilevel converter (MMC), sizing criteria, short circuit

#### I. INTRODUCTION

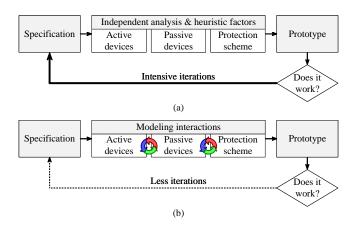

Modular multilevel converters (MMC) are complex systems, composed of many components, and exposed to critical loads [1]. Thereby, a detailed design of its components is of preeminent importance to achieve satisfactory performance with a constraint design margin while ensuring sufficient robustness during extreme situations (e.g., fault transients). Although many efforts have been devoted to achieving a better design of the MMC [2]–[4], most of the existing methods divide the system into multiple independent sub-systems and consider few interactions among them. As shown in Fig. 1, the design based on the independent analysis often ignores these inherent interactions, thereby leading to introducing some empirical factors and intensive trial-and-errors. As such, a better model-based design considering these interactions is preferable to address this challenge.

One specific research gap of the model-based design of the MMC is the reactor sizing considering pole-to-pole (P2P) short-circuit faults. The reactor is significant to limit the fault current and protect the power semiconductor devices

Manuscript received Month xx, 2xxx; revised Month xx, xxxx; accepted Month x, xxxx. This work was supported by Independent Research Fund Denmark with the grant number 1031-00024B. (Corresponding author: *Yi Xu, Yi Zhang*).

Y. Zhang is with AAU Energy, Aalborg University, Denmark. Y. Xu is with Hubei University of Technology, China, and M. Saeedifard is with Georgia Institute of Technology, USA. (e-mail: yiz@ieee.org, xuyi@hbut.edu.cn, maryam@ece.gatech.edu).

Fig. 1. Model-based designs: (a) design based on independent analysis and heuristic experience and (b) design with considering the interactions among different sub-systems.

and other critical components from catastrophic damages [5]. However, the existing design methods of the reactor sizing ignore its inherent interactions with other parameters, such as power ratings, the selection of active components, protection schemes, etc., which leads to using the following heuristic criterion to size reactor [6], [7], namely,

$$L_0 = \frac{U_{\rm dc}}{2\lambda_{\rm emp}},\tag{1}$$

where  $U_{\rm dc}$  is the DC bus voltage,  $L_0$  is the arm inductance, and  $\lambda_{\rm emp}$  is an empirical factor of the pre-set maximum current rise rate which is based on the heuristic experience. For instance, the existing studies provide different values of  $\lambda_{\rm emp}$ , e.g., a wide range of 2-10 kA/ms [6], 100 kA/ms [7], and 1.3 kA/ms [8]. These empirical factors may be applicable for the specific projects, but applying them to different projects are problematic. Moreover, the design criterion of (1) is oversimplified, which ignores that the MMC system typically has multiple reactors and different fault transient stages [9], [10]. Thus, a revisit of the limiting reactor sizing is necessary.

To successfully model the interactions between the reactor sizing and other design parameters, three specific challenges are intertwined from the system-level short-circuit behaviors and component-level robustness. Specifically, the P2P fault transient of the MMC is firstly highly nonlinear and has multiple stages. The previous studies provide dedicated circuit analysis before and after the IGBT blocking [9], [10], but the analysis of sizing the limiting reactors and their interactions with the power semiconductor devices and other design parameters are yet to discuss sufficiently. Moreover, the fault transient of the MMC involves multiple power

| Functions                                  | $L_0$ | $L_{ac}$ | $L_{dc}$ |

|--------------------------------------------|-------|----------|----------|

| Limit the short-circuit current of DC loop | ✓     |          | ✓        |

| Limit the short-circuit current of AC loop | ✓     | ✓        |          |

| Limit circulating current                  | ✓     |          |          |

| Contribute interface to grid               | ✓     | ✓        |          |

| Filter harmonics                           | ✓     | ✓        |          |

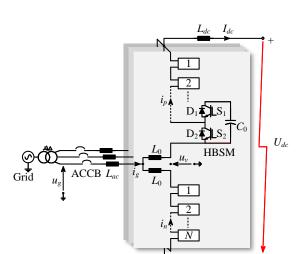

Fig. 2. A half-bridge submodule (HBSM)-based MMC subjected to a pole-to-pole DC fault.

semiconductor devices, such as IGBTs and diodes. These components not only have different time sequences during the fault transient but also have distinct short-circuit capabilities. Page *et al.* [11] propose a simulation-based method to size the limiting reactors considering diodes only. However, an analytical method considering different components is still missing. Finally, multiple reactors are involved in the grid-connected MMC system shown in Fig. 2, which all have different roles. The existing studies often study these functions independently, a comprehensive investigation is missing. Therefore, to address the aforementioned three challenges, the sizing of the limiting reactors should comprehensively bridge the knowledge between the system-level short-circuit behaviors and the capabilities of different components.

This paper bridges the analytical relationship between the system-level reactor sizing and the device-level robustness of power semiconductor devices considering a P2P short-circuit. The established analytical model quantifies the interactions between reactor sizing and other design parameters, such as power ratings, protection schemes, and component-level short-circuit capabilities. Meanwhile, three deterministic factors are provided in this paper to take place the heuristic factor in the existing work. The proposed method not only provides guidelines to better size the hardware parameters and adjusts the protection settings of the MMC, but also emphasizes the modeling of the interactions in the model-based design. This paper is also accompanied by software codes [12].

# II. CONFIGURATION OF AN HBSM-BASED MMC AND TIME SEQUENCE OF POLE-TO-POLE DC FAULT

Fig. 2 shows a typical configuration of an MMC with ACCB protection. The MMC consists of six arms. Each arm is

2

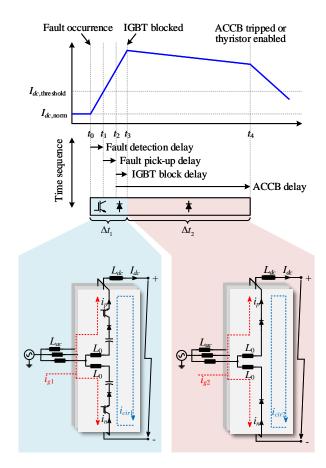

Fig. 3. Time sequence of the P2P short circuit, the conducting power semiconductor devices, and the corresponding equivalent circuits.

comprised of N identical series-connected HBSMs with two different power semiconductor devices (i.e., two IGBTs and two diodes) in each SM and an arm reactor  $L_0$ .

In addition to the arm reactors, the MMC has two other reactors, i.e., the AC reactor  $L_{\rm ac}$ , and the DC reactor  $L_{\rm dc}$  with their functions summarized in Fig. 2. All of these reactors contribute to limiting the short-circuit fault current. The difference is that  $L_0$  and  $L_{\rm dc}$  suppress the DC-loop short-circuit current, while  $L_0$  and  $L_{\rm ac}$  suppress the fault current of the AC loop. To focus on the short-circuit limiting of the reactors, two equivalent inductances in DC and AC loops are given by

$$L_{\text{eqdc}} = \frac{2}{3}L_0 + L_{\text{dc}}, \ L_{\text{eqac}} = \frac{1}{2}L_0 + L_{\text{ac}}.$$

(2)

Moreover, a P2P short-circuit fault interacts with multiple power semiconductors and limiting reactors. To investigate their electrical stresses during different fault transients, this paper is in accordance with the industry report [13] to classify the short-circuit transient into the following stages (see Fig. 3)

- 1) Fault detection delay  $[t_0, t_1)$ : A P2P short-circuit fault occurs at  $t_0$  and is detected till reaching a threshold at  $t_1$ .

- 2) Fault pick-up delay  $[t_1, t_2)$ : Fault pick-up time is necessary in practice to avoid measurement errors. When the measured fault signal exceeds the threshold for a period, the blocking signal is triggered at  $t_2$  and the controller sends

protection commands to IGBTs and ACCBs. This paper selects the fault pick-up delay of 50  $\mu$ s according to [13].

- 3) IGBT blocking delay  $[t_2, t_3)$ : When the blocking signal of the MMC is triggered, with a 20  $\mu$ s delay, the IGBTs are blocked. This time delay considers the multiple control stage of the MMC and the delay of the devices themselves [13].

- 4) Diode conduction only  $[t_3, t_4)$ : The IGBTs are fully blocked at  $t_3$  while the ACCB has not been fully triggered. During this period, diodes conduct the fault current only, which stresses the diode seriously.

- 5) ACCBs are tripped  $[t_4, \infty)$ : The ACCBs are tripped at  $t_4$ , so that the fault is cleared.

Thus, a comprehensive reactor design of the MMC has to consider the interactions of the multiple reactors, different types of power semiconductors, and the aforementioned time sequence of the short circuit transient.

### III. ANALYSIS OF SHORT-CIRCUIT FAULT STRESS ON THE MMC COMPONENTS

This section serves to analytically bridge the system-level short-circuit behaviors and the component-level electrical stresses. By contrast to the previous studies focusing on the short circuit transient on DC grids [14]–[16], this section aims to obtain the electrical stresses of the major power semiconductor devices. Two fault periods are defined as shown in Fig. 3. Fault period  $\Delta t_1$  is related to both IGBTs and diodes, and fault period  $\Delta t_2$  is related to the diodes only. Both of these periods reflect the protection settings of the system.

#### A. Period $\Delta t_1$ : Fault Occurrence to IGBT Blocking $[t_0, t_3)$

At the moment of fault occurrence  $(t_0)$ , the IGBTs have not been blocked yet. As shown in Fig. 3, the fault current consists of a circulating current  $i_{\rm cir1}$  (dominated by SM capacitors discharging) through the DC loop and AC fed-in current  $i_{\rm g1}$ , which are introduced as follows.

1) DC loop: the SM capacitor discharge current can be described as a second-order form in Appendix (A1). Considering the worst case with negligible resistance and short  $\Delta t_1$ , the current is simplified as

$$i_{\text{cirl}}(t) = \frac{1}{3} \left[ \frac{U_{\text{dc}}(t - t_0)}{L_{\text{eqdc}}} + I_{\text{dc}}(t_0) \right],$$

(3)

where  $I_{dc}(t_0)$  is the initial DC current.

2) AC loop: the AC loop stays the same at the moment of the fault occurrence, where the AC voltage  $u_{\rm g}(t)$  and current  $i_{\rm gl}(t)$  are described by

$$u_{\rm g}(t) = \hat{U}_{\rm g} \sin(\omega t + \alpha),$$

(4)

$$i_{g1}(t) = \hat{I}_{g1}\sin(\omega t + \alpha - \varphi_c), \tag{5}$$

where  $\hat{U}_g$  and  $\hat{I}_{g1}$  represent the magnitudes of the grid voltage and current, respectively.  $\omega$  is the synchronous angular frequency,  $\alpha$  is the phase angle at the fault occurrence  $t_0$ , and  $\varphi_c$  is the initial grid phase angle.

3) Electrical stresses of the components: the AC current of (5) is equally split into the upper and the lower arms in this stage. Considering that the variation of  $i_{g1}(t)$  is negligible with a short  $\Delta t_1$ , the arm current in the worst scenario is expressed as

$$i_{\rm p1}(t)_{\rm sim,max} = \frac{1}{3} \left[ \frac{U_{\rm dc} \cdot (t - t_0)}{L_{\rm endc}} + I_{\rm dc}(t_0) \right] + \frac{1}{2} \hat{I}_{\rm g1}.$$

(6)

- B. Period  $\Delta t_2$ : IGBT Blocking to ACCB Tripping  $[t_3, t_4)$

- 1) DC loop: IGBTs are blocked at  $t_3$ . The equivalent circuit is changed as shown in Fig. 3. With a  $\tau_{dc}$  defined in Appendix, the circulating current  $i_{cir2}$  is dominated by a freewheeling current through the DC loop and is expressed as

$$i_{\text{cir2}}(t) = i_{\text{cir1}}(t_3)e^{-\frac{t-t_3}{\tau_{\text{dc}}}}.$$

(7)

3

2) AC loop: the AC voltages are all applied to the AC and arm reactors. Consequently, the AC current is described as the transient circuit, which is

$$i_{g2}(t) = \hat{I}_{g2}\sin[\omega(t - t_3) + \alpha - \varphi] +$$

$$[\hat{I}_{g1}\sin(\alpha - \varphi_c) - \hat{I}_{g2}\sin(\alpha - \varphi)]e^{-\frac{t - t_3}{\tau_{dc}}}, \quad (8)$$

in which  $\varphi=\arctan(\omega L_{\rm eqac}/R_{\rm eqac})$ .  $R_{\rm eqac}$  is the AC-loop equivalent resistance.  $\hat{I}_{\rm g2}$  and  $\tau_{\rm ac}$  are given by

$$\hat{I}_{g2} = \frac{\hat{U}_g}{\sqrt{R_{\text{eqac}}^2 + (\omega L_{\text{eqac}})^2}}, \tau_{\text{ac}} = \frac{L_{\text{eqac}}}{R_{\text{eqac}}}.$$

(9)

3) Electrical stresses of the components: the arm current within the period  $\Delta t_2$  is composed of (7) and half of (8). Considering the worst case, it can be obtained that  $\omega L_{\rm eqac} \gg R_{\rm eqac}$ . The negligible  $R_{\rm eqac}$  and  $R_{\rm eqac}$  cause large  $\tau_{\rm dc}$  and  $\tau_{\rm ac}$ . The maximum arm current is simplified as

$$i_{p2}(t)_{\text{sim\_max}} = \frac{1}{3} \left[ \frac{U_{\text{dc}}(t_3 - t_0)}{L_{\text{eqdc}}} + I_{\text{dc}}(t_0) \right] - \frac{1}{2} \frac{\hat{U}_{\text{g}}}{\omega L_{\text{eqac}}} \cos[\omega(t - t_3)] + \frac{1}{2} (\hat{I}_{\text{g1}} + \frac{\hat{U}_{\text{g}}}{\omega L_{\text{eqac}}}). \quad (10)$$

In summary, the maximum electrical stress on the components is combined with (6) and (10), which is expressed by

$$i(t)_{\text{max}} = \begin{cases} i_{\text{p1}}(t)_{\text{sim,max}}, & t \in [t_0, t_3) \text{ or } \Delta t_1 \\ i_{\text{p2}}(t)_{\text{sim,max}}, & t \in [t_3, t_4) \text{ or } \Delta t_2. \end{cases}$$

(11)

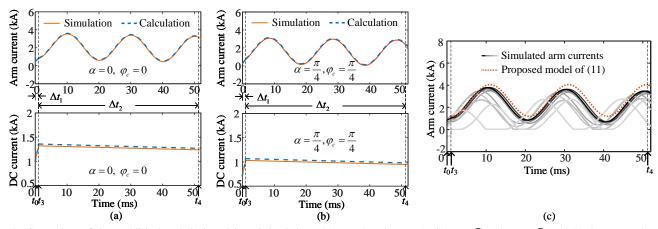

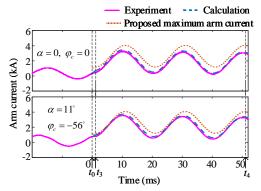

### C. Simulation Verification of the Analytical Models

The aforementioned analytical models are established based upon a certain simplification, e.g., the active power is constant, the resistance is negligible, etc. For the sake of verifications, a 60-MVA MMC-HVDC system with its parameters listed in Table I is used for simulations. As shown in Fig. 4(a), when a P2P DC fault occurs at  $\alpha=0$  and  $\varphi_c=0$ , the simulation results and analytical calculations are closely matched. Meanwhile, Fig. 4(b) has similar results with changed  $\alpha$  and  $\varphi_c$ . These results verify the effectiveness of the established models.

As the fault current is varied with fault occurrence (modeled by  $\alpha$ ) and power factor ( $\varphi_c$ ), a design with sufficient

Fig. 4. Comparison of the established analytical models and simulations: (a)  $\alpha=0$  and  $\varphi_c=0$ , (b)  $\alpha=\frac{\pi}{4}$  and  $\varphi_c=\frac{\pi}{4}$ , and (c) the proposed model described by (11) can represent the envelope of the arm currents under different fault occurrence  $\alpha$  and power factors  $\varphi_c$ .

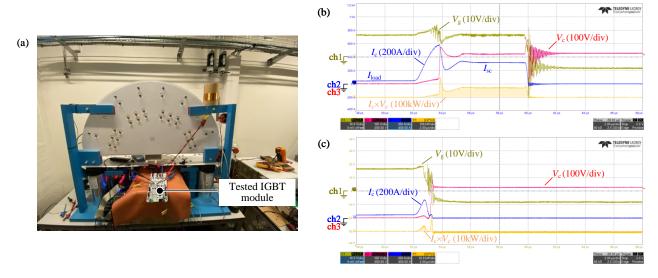

Fig. 5. Type II short-circuit measurements: (a) the photo of the tested platform, (b) waveform of Type II short circuit with de-saturation protection only, and (c) turn off IGBT before reaching the saturation current ( $I_{SC}$ ) ( $V_C$  - collector-emitter voltage,  $I_C$  - collector current,  $V_g$  - gate voltage).

TABLE I

MMC PARAMETERS FOR BOTH SIMULATIONS AND HARDWARE-IN-LOOP

EXPERIMENTS

| Symbol         | Parameter              | Value and Unit |  |

|----------------|------------------------|----------------|--|

| $S_N$          | Power rating           | 60 MVA         |  |

| $\hat{U}_g$    | Grid voltage amplitude | 28.3 kV        |  |

| $\hat{l}_{g1}$ | Grid current amplitude | 1.41 kA        |  |

| f              | Grid frequency         | 50 Hz          |  |

| $U_{dc}$       | DC bus voltage         | 60 kV          |  |

| N              | Number of SMs per arm  | 20             |  |

| $C_0$          | SM capacitance         | 2.65 mF        |  |

| $L_0$          | Arm reactor            | 50 mH          |  |

| $R_0$          | Arm resistance         | 0.02 Ω         |  |

| $L_{dc}$       | DC reactor             | 100 mH         |  |

| $L_{ac}$       | AC reactor             | 6.4 mH         |  |

| $R_{ac}$       | AC filter resistance   | 0.1 Ω          |  |

| $\Delta t_1$   | Fault period 1*        | 1.07 ms        |  |

| $\Delta t_2$   | Fault period 2         | 50 ms          |  |

\*Includes the fault detection time of 1 ms [17], fault pick-up time of 50  $\mu s$  [13], and IGBT block delays of 20  $\mu s$  [13]

robustness must consider the worst-case scenario. By varying both  $\alpha$  and  $\varphi_c$ , the arm currents under different conditions are shown in Fig. 4(c). The proposed model described by (11) can represent the envelope of different cases. Thus, the established maximum arm current can be used to size the

hardware parameters in the next section.

# IV. SHORT-CIRCUIT CAPABILITIES OF POWER SEMICONDUCTORS

To ensure enough robustness for the power devices of the MMC, this section further bridges the above established electrical stresses to the short-circuit capabilities of the power semiconductor devices.

### A. IGBT

A data sheet of the IGBT typically provides the data for the Type-I short-circuit fault only, which has zero current at the moment of fault happening. However, the short circuit in the MMC often occurs when the IGBT is already conducting a large current, which is a more severe Type-II short circuit [18]. Moreover, the short-circuit current of the MMC is generated by N HBSMs in series, which is even more severe than the Tyepe-II short circuit in two-level converters.

In the existing literature, the sizing of the limiting reactors usually does not take the short-circuit capability of the IGBT

into consideration, because their holding a view that the desaturation of the IGBT can protect the device by itself. However, based on the short circuit testing platform [Fig. 5(a)], the waveform of Type II short circuit applying the de-saturation protection has high stresses on the tested device [see Fig. 5(b)]. Specifically, when the de-saturation current is reached, the collector-emitter voltage  $V_{\rm C}$  shows a positive slope (d $v/{\rm d}t$ ) up to and even beyond the DC-link voltage. This positive dv/dt causes a displacement current through the inevitable parasitic Miller capacitance of the IGBT, overcharging the gate and consequently leading a higher  $V_q$  and short-circuit current amplitude. The high overvoltage and overcurrent generate massive peak power, which is around 150 kW at the maximum. Thus, this paper holds a view that an effective sensing and protection to turn the IGBTs off before reaching the saturation current  $(I_{SC})$  is necessary. The case applying this strategy is shown in Fig. 5(c). The peak dissipation is only 10 kW and the period is within 2  $\mu$ s only, which from the perspective of the safe operating area protects the IGBT against the stresses.

Accordingly, a criterion for IGBTs of the MMC is selected as

$$I_{SC} \ge i_{p1}(t_3), \tag{12}$$

where  $I_{SC}$  refers to the IGBT's datasheet. Substituting (11) into (12), the sizing of the DC-loop equivalent inductance has the following criterion

$$L_{\text{eqdc}} \ge \frac{U_{\text{dc}}}{\lambda_{\text{dcl}}},$$

(13)

where

$$\lambda_{\text{dc1}} = \frac{3(I_{\text{SC}} - I_0)}{\Delta t_1} \text{ [A/s]},$$

(14)

$$I_0 = \frac{1}{3}I_{dc}(t_0) + \frac{1}{2}\hat{I}_{g1}.$$

(15)

In (13)-(15), the proposed equivalent current rise rate  $\lambda_{\rm dc1}$  comprehensively consider three aspects, i.e., power rating related  $I_0$ , protection setting  $\Delta t_1$ , and the short-circuit capability of the IGBT  $I_{\rm SC}$ . This addresses the existing study of (1) relies on empirical  $\lambda_{\rm emp}$  without analytical expressions.

#### B. Diodes

By contrast to the IGBTs, diodes are not self-controlled. The short-circuit capability of the diodes is limited by the thermal stress introduced by the surge current. However, many parameters affect the peak junction temperature of the diode during short circuits [19], such as initial diode junction temperature, short circuit duration, forward voltage, thermal impedance, etc. Thus, the standard method [20] introduces the surge current integral  $I^2t$  to quantify the short-circuit capability of the diode, which is expressed as

$$I^{2}t = \int_{0}^{t_{p}} i^{2}(t)dt, \tag{16}$$

where i(t) is the conducting current for the duration  $t_p$ . In other words, if the short-circuit current stresses are kept within

the given limits, the diode will stay within the guaranteed characteristics. Therefore, the MMC needs to fulfill the following condition:

$$I^{2}t_{\text{(diode)}} \ge \int_{t_{0}}^{t_{3}} i_{\text{pl}}^{2}(t)dt + \int_{t_{3}}^{t_{4}} i_{\text{p2}}^{2}(t)dt,$$

(17)

where  $I^2t_{\text{(diode)}}$  refers to the diode's datasheet provided by the manufacturer. Substituting the established diode stresses of (11) into (17), the following two criteria are deduced as

$$L_{\rm eqdc} > \frac{U_{\rm dc}}{\lambda_{\rm dc2}}, \text{ and } L_{\rm eqac} \ge \frac{\hat{U}_{\rm g}}{\lambda_{\rm ac}},$$

(18)

where

$$\lambda_{\text{dc2}} = (\sqrt{a_1 I^2 t_{\text{(diode)}} - a_2 I_0^2} - a_3 I_0) / \Delta t_1,$$

(19)

$$\lambda_{\rm ac} = \omega \left[ \sqrt{b_1 \eta^2 + b_2 \eta I_0 + b_3 I_0^2 + b_4 \omega I^2 t_{\rm (diode)}} - b_5 (I_0 + \frac{1}{3} \eta) \right], \tag{20}$$

where the parameters  $a_1$ ,  $a_2$ ,  $a_3$ ,  $b_1$ ,  $b_2$ ,  $b_3$ ,  $b_4$ ,  $b_5$  and  $\eta$  are related to  $\Delta t_1$  and  $\Delta t_2$  as given in the Appendix. The proposed two additional equivalent current rise rates  $\lambda_{\rm dc2}$  and  $\lambda_{\rm ac}$  consider the ratings of the MMC, the protection settings  $\Delta t_1$  and  $\Delta t_2$ , and short-circuit capability of the diodes  $I^2 t_{\rm (diode)}$  as well.

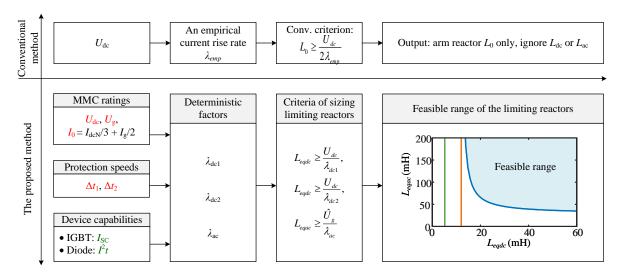

#### C. Summary of the Sizing Criteria of Limiting Reactors

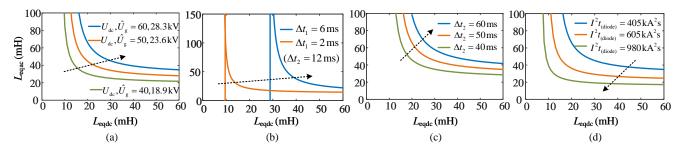

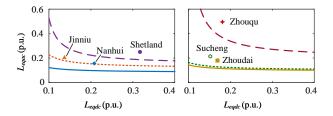

The proposed three sizing criteria of the limiting reactors are summarized in Fig. 6. The proposed method comprehensively considers three aspects, i.e., ratings of the MMC ( $U_{\rm dc}$ ,  $\hat{U}_{\rm g}$ , and  $I_0$ ), the protection speeds ( $\Delta t_1$  and  $\Delta t_2$ ), and short-circuit capabilities of the power semiconductors ( $I_{\rm SC}$  for IGBTs, and  $I^2t$  for diodes). Among them, the limiting reactors are proportional to the ratings of the MMC, while are inversely proportional to the protection speeds and the short-circuit capabilities of the power semiconductors. The three constraints constitute the feasible range of the limiting reactors, which is able to serve the design optimizations. For instance, the boundary of the feasible range indicates the minimum requirements. When  $L_{\rm eqdc}$  is in low area,  $L_{\rm eqac}$  will be dramatically increased and almost flat in large  $L_{\rm eqdc}$  value. That reveals a trade-off between the  $L_{\rm eqdc}$  and  $L_{\rm eqac}$ .

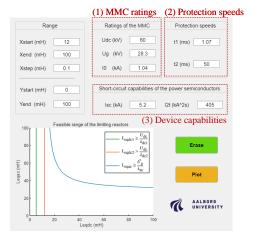

Meanwhile, the impacts of different parameters are shown in Fig. 7. With the increase of the ratings of the MMC (i.e.,  $U_{\rm dc}$ ,  $\hat{U}_{\rm g}$ ) or the protection time (i.e.,  $\Delta t_1$  and  $\Delta t_2$ ), the feasible range of the limiting reactor is squeezed to the right corner. Conversely, the feasible range is enlarged by a large short-circuit capability of the diode. By contrast, the conventional method only relies on the  $U_{\rm dc}$  and an empirical current rise rate  $\lambda_{\rm emp}$ . Its output is a fixed arm inductance  $L_0$  only. Intensive trial-and-errors of the parameter  $\lambda_{\rm emp}$  are inevitable in the conventional method. To let readers utilize the proposed methods easily, an open-access software is also included as shown in Fig. 8.

Fig. 6. Comparison of the proposed sizing criteria and the conventional method for the limiting reactors. The proposed method comprehensively considers three aspects, i.e., the ratings of the MMC, the protection speeds, and the device short-circuit capabilities. The obtained feasible range is able to serve the design optimizations.

Fig. 7. The impact of the parameters on the feasible range of the limiting reactors: (a) increase the ratings of the MMC, (b) increase the protection time  $\Delta t_1$ , (c) increase the protection time  $\Delta t_2$ , and (d) increase the short circuit capability of the diode.

Fig. 8. A software is provided to apply the proposed method.

#### V. VERIFICATION AND COMPARISON

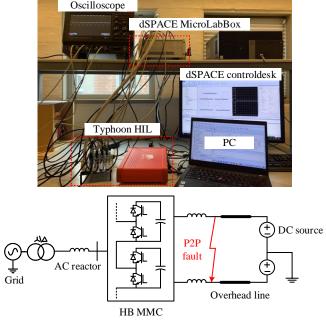

To verify the effectiveness of the proposed method, a hardware-in-the-loop (HIL) experimental platform has been built as shown in Fig. 9. The MMC is emulated using Typhoon HIL-402 and the controller selects dSPACE MicroLabBox. The experimental parameters are listed in Table I. To verify the effects of different power semiconductors, two IGBT modules with different current ratings and short-circuit capabilities are listed in Table II.

Fig. 9. The photo and the configuration of the experimental platform.

#### A. Verification of the Fault Current Estimation

To validate the established fault current estimation method, the comparison of a P2P short-circuit fault and the estimations

Fig. 10. Comparison of the experimental and theoretical results of the proposed maximum arm current under different  $\alpha$  and  $\varphi_c$ .

Fig. 11. The feasible range of the limiting reactors based on IGBT Module 1 and Module 2, respectively, and the corresponding inductance.

AC reactor  $L_{ac}$

14.2

6.2

3

TABLE II

THE DATA OF TWO STUDIED IGBT MODULES, AND THEIR

CORRESPONDINGLY ESTIMATED POWER LOSSES, THERMAL RESISTANCE

OF THE HEAT SINK AND THE CORRESPONDING VOLUME.

|                                 |                                                  | IGBT Module1              |        | IGBT Module2 |        |

|---------------------------------|--------------------------------------------------|---------------------------|--------|--------------|--------|

|                                 |                                                  | IGBT                      | Diode  | IGBT         | Diode  |

|                                 | Voltage [kV]                                     | 4.5                       |        | 4.5          |        |

| Data sheet                      | Current [kA]                                     | 1.2                       |        | 1.5          |        |

| provided                        | $I_{SC}$ [kA]                                    | 5.2                       | -      | 7.8          | -      |

| values                          | $I^2 t_{\text{(diode)}} \text{ [kA}^2 \text{s]}$ | -                         | 405    | -            | 871    |

| [21], [22]                      | $R_{\rm thic}$ [K/kW]                            | 9.5                       | 19     | 9.8          | 16     |

|                                 | $R_{\rm thch}$ [K/kW]                            | 9                         | 18     | 8            | 11     |

|                                 |                                                  | IGBT Module 1 IGBT Module |        | Module 2     |        |

|                                 | S <sub>1</sub> [W]                               | 382                       |        | 357          |        |

| Estimated                       | $D_1$ [W]                                        | 451                       | Total: | 420          | Total: |

| power losses                    | $S_2[W]$                                         | 1542                      | 2477   | 1401         | 2287   |

|                                 | $D_2$ [W]                                        | 102                       |        | 109          |        |

| Thermal resistance of heat sink | R <sub>thhs</sub> [K/kW]                         | 5.4 10.7                  |        | 0.7          |        |

|                                 |                                                  |                           |        |              |        |

Note:  $R_{\rm thjc}$ : junction-to-case thermal resistance,  $R_{\rm thch}$ : case-to-heatsink thermal resistance,  $R_{\rm thbc}$ : heatsink-to-ambient thermal resistance.

are shown in Fig. 10. The experiments are conducted with two different sets of  $\alpha$  and  $\varphi_c$ . The experimental results coincide well with their corresponding theoretical calculations. Meanwhile, the proposed maximum arm current is constant in the two cases, which models the worst-case scenario to design

the limiting reactors. It should be mentioned that the HIL experiment cannot provide dedicated device-level transients. To compensate for this limitation, two short-circuit transients of the device are provided in Figs. 5(b) and (c) where Type-II is more relevant to the MMC.

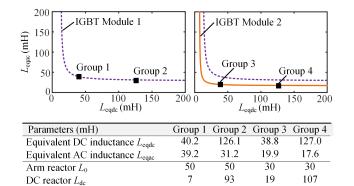

#### B. Verification of the Proposed Criteria with IGBT Module 1

With the selection of IGBT Module 1, the proposed method provides a feasible range of the limiting reactors as shown in Fig. 11. To validate the proposed criteria, two sets of parameters on the boundary are selected, which are denoted as Group 1 and Group 2, respectively. It should be noted that the proposed method considering the P2P fault only determines the relation of  $L_{\rm eqdc}$  and  $L_{\rm eqac}$ . To select the specific values of the three reactors is discussed in Section VI.

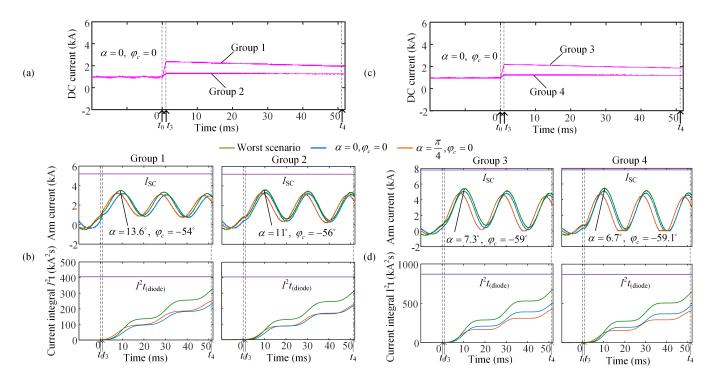

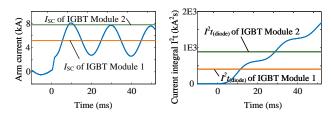

Fig. 12(a) shows the experimental DC currents with parameters of Groups 1 and 2. The case of Group 1 has a large DC current rise rate due to a smaller  $L_{\rm eqdc}$ . Moreover, Fig. 12(b) shows the comparison of the withstanding stresses and the short-circuit capabilities of the IGBTs and diodes, respectively. First, the arm current at  $t_3$  is much smaller than the  $I_{\rm SC}$  of the IGBT, which implies the main limitation of this case is not the short-circuit capability of the IGBT. On the contrary,  $I^2t_{\rm (diode)}$  of two cases are rising from  $t_0$  to  $t_4$ , but the maximum  $I^2t_{\rm (diode)}$  is within the datasheet provided value. Thus, the selected limiting reactors based on the proposed criteria are able to guarantee the operation of the power semiconductors within their safe operating areas.

For the MMC system with identical ratings and power semiconductors, Group 2 has  $L_{\rm eqdc}=126.1$  mH which is approximately three times Group 1. However, both the arm currents and current integral are similar under the two different parameters apart from the different DC current rise rates. Therefore, the parameters of Group 1 near the knee area of the feasible range in Fig. 11 is more cost-effective.

#### C. Verification of the IGBT Module 2 with Larger Capabilities

To further investigate the impact of the short-circuit capability of the power semiconductor devices, IGBT Module 2 with an increased short-circuit capability is selected. The feasible range based on IGBT Module 2 is obtained as shown in Fig. 11 as well. Compared to IGBT Module 1, the feasible range of IGBT Module 2 is enlarged to the lower left corner, which means a smaller inductance can be selected by increasing the short-circuit capability of the power module. Two parameters on the boundary are also selected and denoted as Group 3 and Group 4, respectively.

Similarly, Fig. 11(c) shows the corresponding DC currents, and Fig. 11(d) shows the comparison between the experimental results of the arm currents and the short-circuit capability of power semiconductor devices. Both IGBTs and diodes are within their safe operating areas, which validates the effectiveness of the proposed method. Moreover, Group 3 which has the parameters near the knee area of the feasible range has only 1/4 of  $L_{\rm eqdc}$  compared to the case of Group 4. It reveals that the proposed feasible range is able to explore better parameters with consideration of the P2P fault. Furthermore,  $L_{\rm eqdc}$  and

Fig. 12. Experimental results when using parameters of Groups 1-4: (a) DC currents (Groups 1 and 2). (b) comparison between arm currents and  $I_{\rm SC}$ , and comparison between current integral and  $I^2t_{\rm (diode)}$  (Groups 1 and 2). (c) DC currents (Groups 3 and 4). (b) comparison between arm currents and  $I_{\rm SC}$ , and comparison between current integral and  $I^2t_{\rm (diode)}$  (Groups 3 and 4).

$L_{\rm eqac}$  of Group 3 have reduced by 4% and 50%, respectively, compared to the ones of Group 1. This demonstrates that the demand for the passive device can also be alleviated by upgrading the active devices.

# D. Impacts of Reactor Sizing on Power Losses and Cooling Systems

Sections V-B and V-C have revealed that the reactor sizing is intertwined with the parameters of the power devices. The further impacts on power losses and cooling systems are estimated and listed in Table II. The estimation methods are in accordance with the previous studies of [23] and [24]. First, IGBT Module 2 has slightly reduced power losses. However, due to the reduced thermal resistances of IGBT Module 2, the required thermal resistance of the heat sink changes by a factor of two. The estimated volume of the heat sink of IGBT Module 2 is about half of the one for IGBT Module 1. This reveals that a proper over-rating of the power module not only reduces the reactance, but also increases efficiency and reduce volume. The quantified interactions presented in this paper help to guide to achieve a better trade-off among them.

## E. Comparison of the Proposed Criteria with the Previous Methods

The existing studies use an empirical constant to size the limiting reactor as per (1). In the literature, different values of the  $\lambda_{\rm emp}$ , such as a wide range of 2-10 kA/ms in [6],  $100~{\rm kA/ms}$  [7], or  $1.3~{\rm kA/ms}$  [8], have been reported. Applying  $\lambda_{\rm emp} = 1.3~{\rm kA/ms}$  to the case studies of this paper, the

calculated  $L_0=23$  mH and the corresponding short-circuit waveforms are shown in Fig. 13. Both the selected IGBT modules do not meet the short-circuit requirements considering  $I_{\rm SC}$  or  $I^2t_{\rm (diode)}$ . Moreover, it reveals that the provided  $\lambda_{\rm emp}$  in the literature is problematic to be applied to different cases.

# F. Comparison of the Proposed Criteria to the Installed Projects

To further demonstrate the proposed criteria under various parameters, six installed HBSM-based MMC projects along with their feasible ranges are compared in Fig. 14. The equivalent inductance of these projects is all within the feasible range provided by the proposed method, which verifies the effectiveness of the proposed method.

#### VI. DISCUSSION

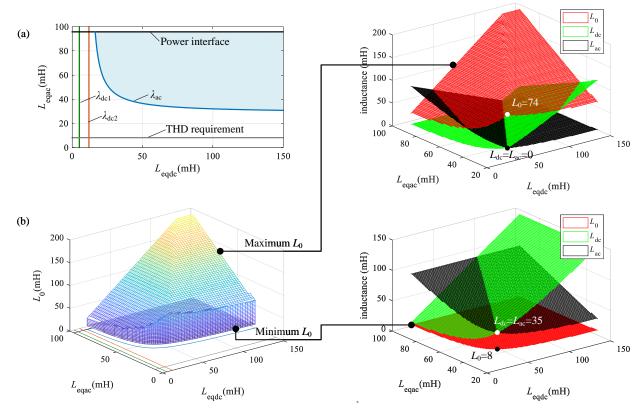

In this paper, the reactors are designed to suppress the DC short-circuit faults and the feasible range of the two equivalent inductances is presented. However, it should be mentioned the reactors of the MMC have different functions, such as suppressing the resonance of the circulating currents, providing an interface to the AC grid, filtering the harmonics, etc. The conversion from the obtained feasible range of  $L_{\rm eqdc}$  and  $L_{\rm eqac}$  into the values of  $L_0$ ,  $L_{\rm ac}$  and  $L_{\rm dc}$  needs to consider these requirements as well. This paper summarizes these requirement related to the arm inductance  $L_0$  directly, others correlate to the equivalent inductance  $L_{\rm eqdc}$  and  $L_{\rm eqac}$ .

To further clarify the trade-offs, a demonstration based on the study case of this paper is shown in Fig. 15. First, with

Fig. 13. Applying the parameter of the existing work  $\lambda_{\rm emp}=1.3$  kA/ms [8] to the case study of this paper. Both IGBT modules do not meet the short-cicuit requirements in terms of  $I_{\rm SC}$  or  $I^2t_{\rm (diode)}$ .

Fig. 14. Comparison of the proposed feasible range (lines) and the parameters of the installed projects (dots). Projects: Nanhui [25], Shetland [26], Jinniu and Sucheng [27], Zhouqu and Zhoudai [28].

| Functions of the reactors        | Criteria                                                                                                                                                                                              | Involved parameters       | Ref.       |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------|

| Limiting short circuit transient | The proposed $\lambda_{dc1}$ , $\lambda_{dc2}$ , $\lambda_{ac}$ in (13) and (18).                                                                                                                     | $L_{ m eqdc},L_{ m eqac}$ | _          |

| Avoid current resonance          | $L_{\rm res,n} = \frac{N}{\omega^2 C_0} \frac{2(h^2-1) + m_a^2 h^2}{8h^2(h^2-1)} \Rightarrow L_0 > \frac{N}{\omega^2 C_0} \frac{3 + 2m_a^2}{48}$                                                      | $L_0$                     | [29], [30] |

| Interface to AC grid             | $m_a = \frac{2}{U_{dc}} \sqrt{ \left( \hat{U}_g - \frac{2S\sin\varphi_c}{3\hat{U}_g} \omega L_{\rm eqac} \right)^2 + \left( \frac{2S\cos\varphi_c}{3\hat{U}_g} \omega L_{\rm eqac} \right)^2} \leq 1$ | $L_{ m eqac}$             | [31]       |

| Filter harmonics                 | $\text{THD}_{\text{pcc}} = \frac{L_s}{L_s + L_{\text{eqac}}} \text{THD}_c = \frac{L_s}{L_s + L_{eqac}} \frac{1}{f(1)} \sqrt{\sum_{h=2k+1}^{\infty} \left[\frac{f(h)}{h}\right]^2}$                    | $L_{ m eqac}$             | [32]–[36]  |

Notes: $m_a$  is the modulation index,  $\text{THD}_{\text{PCC}}$  and  $\text{THD}_c$  are total harmonic distortion at the point of common coupling and the converter side, respectively,  $L_s$  is the equivalent inductance of the AC grid,  $f(h) = \sum_{i=1}^s \cos(h\theta_i)$  with the positive integer k=1,2,3,...,s is the number of switching angles in the first quarter of cycle, and  $\theta_i$  is the *i*-th switching angle.

Fig. 15. The results with considering all constraints in Table III comprehensively: (a) the feasible range of  $L_{\rm eqdc}$  and  $L_{\rm eqac}$  with two more constraints, and (b) the feasible ranges of arm, dc and ac reactors ( $L_0$ ,  $L_{\rm dc}$ , and  $L_{\rm ac}$ ) and their interactions. (Parameters are based on  $L_s=6.37$  mH, THD<sub>PCC</sub>  $\leq 1.5\%$ ,  $\varphi_c \leq \frac{\pi}{4}$ , and Table I)

consideration of the interface to the AC grid and the THD requirements, the feasible region of the AC and DC loop inductance is narrowed slightly as shown in Fig. 15(a). The power interface limits the maximum  $L_{\text{eqac}}$ , but the dominant factor is still related to the short circuit. Next, the feasible region of the arm inductance  $L_0$  is obtained as shown in Fig. 15(b), which consists of a flat minimum surface and a cone shape of the maximum. The minimum  $L_0$  surface is limited by that the arm inductance  $L_0$  needs to be greater than 8 mH to avoid the circulating current resonance. The maximum  $L_0$  surface consists of the upper constraints of  $L_0 \leq 1.5 L_{

m eqdc}$  and  $L_0 \leq 2 L_{

m eqac}$  according to (2). Considering the designs based on the two extreme surfaces, the corresponding  $L_{\rm dc}$  and  $L_{\rm ac}$  are obtained in the right-hand side of Fig. 15(b). For either case, the surfaces of  $L_{\rm dc}$  and  $L_{\rm ac}$ have inverse trends at two ends and have an intersection in the middle. For instance, considering the situation with the maximum  $L_0$ , the intersection has  $L_{dc} = L_{ac} = 0$  mH and  $L_0 = 74$  mH. It represents a design using the arm reactors to fulfill all requirements. On the contrary, for the case on the minimum  $L_0$  plane, the additional  $L_{dc}$  and  $L_{ac}$  are mandatory. The intersection has  $L_{\rm dc}=L_{\rm ac}=35$  mH and  $L_0=8$  mH.

Moreover, it is worth mentioning that this paper is focused on the most typical HBSM MMC and other topologies with full-bridge submodules (SM), clamping double SMs, and/or a hybrid combination of different SMs [37] are not covered. For those topologies, as during the fault, the SM capacitors are in the path of fault current, the limiting reactor sizing need to consider the SM capacitor charging and other factors.

#### VII. CONCLUSION

This paper proposes a model-based design approach for the MMC. It contributes to sizing multiple reactors of the MMC to keep the short-circuit current within the robust limits of power devices and the interactions of different constraints. The following conclusions can be summarized.

- 1) By bridging the system-level short-circuit behaviors and component-level robustness of the MMC, this paper proposes three deterministic factors  $\lambda_{dc1}$ ,  $\lambda_{dc2}$ , and  $\lambda_{ac}$  to take place the empirical  $\lambda_{emp}$  in the existing studies.

- 2) Based on the proposed method, this paper quantitatively points out that the sizing of the limiting reactors depends on three intertwined aspects: a) ratings of the MMC, b) fault protection speeds, and c) short-circuit capabilities of power semiconductors.

- 3) A feasible region of designing the AC-loop and DC-loop inductances is provided. The parameters near the knee area of the feasible range provide better cost-effective solutions, and the demand for the passive devices can be alleviated by upgrading the active devices. These properties reveal that the proposed method with better modeling of the interactions is able to serve to explore design optimization.

- 4) All constraints of the reactor sizing of the MMC are comprehensively considered, including both fault (i.e., short circuit) and normal states. Based on the parameters of the case study, the dominant factor is related to the fault state. It indicates that the optimization of power electronics

converters often depends on fault states instead of often talked normal operations.

The proposed method has been verified by simulations and experiments as well as comparison with the parameters of several installed projects.

#### APPENDIX

The capacitor discharging in the period  $\Delta t_1$  is

$$i_{\text{cir1}}(t) = \frac{1}{3} \frac{e^{-(t-t_0)/2\tau_{\text{dc}}}}{\sqrt{1-\xi^2}} \left\{ \frac{U_{\text{dc}}}{\omega_{\text{dc}}L_{\text{eqdc}}} \sin[\omega_{\text{dc}}\sqrt{1-\xi^2}(t-t_0)] - I_{\text{dc}}(t_0) \sin[\omega_{\text{dc}}\sqrt{1-\xi^2}(t-t_0) - \theta_{\text{dc}}] \right\}, \quad (A1)$$

where  $R_{\rm eqdc}$  is the DC-loop equivalent resistance. The expressions of  $\tau_{\rm dc}$ ,  $\omega_{\rm dc}$ ,  $\xi$  and  $\theta_{\rm dc}$  are given as

$$\begin{split} \tau_{\rm dc} &= \frac{L_{\rm eqdc}}{R_{\rm eqdc}}, \omega_{\rm dc} = \sqrt{\frac{1}{L_{eqdc}C_{\rm eq}}}, \\ \xi &= \frac{R_{\rm eqdc}}{2} \sqrt{\frac{C_{\rm eq}}{L_{\rm eqdc}}}, \theta_{\rm dc} = \arctan\frac{\sqrt{1 - \xi^2}}{\xi}. \end{split} \tag{A2}$$

The detailed parameters in the sizing criteria of DC-loop and AC-loop equivalent inductance for diodes are given as

$$a_{1} = \frac{27}{3\Delta t_{2} + \Delta t_{1}}, a_{2} = \frac{27\Delta t_{1}(4\Delta t_{2} + \Delta t_{1})}{4(3\Delta t_{2} + \Delta t_{1})^{2}},$$

$$a_{3} = \frac{9(2\Delta t_{2} + \Delta t_{1})}{2(3\Delta t_{2} + \Delta t_{1})}.$$

(A3)

$$\begin{split} b_1 &= \frac{64}{9}m^2 - \frac{16\omega(3\Delta t_2 + \Delta t_1)}{27}n, \\ b_2 &= \frac{128}{3}m^2 - \frac{16\omega(2\Delta t_2 + \Delta t_1)}{3}n, \\ b_3 &= 64m^2 - 16\omega(\Delta t_2 + \Delta t_1)n, b_4 = 16n, b_5 = 8m. \ \ (\text{A4}) \end{split}$$

$$\eta = \frac{U_{\rm dc}\Delta t_1}{L_{\rm ende}},\tag{A5}$$

$$m = \frac{\omega \Delta t_2 - \sin(\omega \Delta t_2)}{6\omega \Delta t_2 + \sin(2\omega \Delta t_2) - 8\sin(\omega \Delta t_2)},$$

$$n = \frac{m}{\omega \Delta t_2 - \sin(\omega \Delta t_2)}.$$

(A6)

#### REFERENCES

- [1] T. H. Nguyen, K. A. Hosani, M. E. Moursi, and F. Blaabjerg, "An overview of modular multilevel converters in HVDC transmission systems with STATCOM operation during pole-to-pole DC short circuits," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4137–4160, May 2019.

- [2] J. V. M. Farias, A. F. Cupertino, V. de Nazareth Ferreira, H. A. Pereira, S. I. Seleme, and R. Teodorescu, "Reliability-oriented design of modular multilevel converters for medium-voltage STATCOM," *IEEE Trans. Ind. Electron.*, vol. 67, no. 8, pp. 6206–6214, Aug. 2019.

- [3] J. E. Huber and J. W. Kolar, "Optimum number of cascaded cells for high-power medium-voltage ac-dc converters," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 5, no. 1, pp. 213–232, Mar. 2017.

- [4] T. Nakanishi and J.-I. Itoh, "High power density design for a modular multilevel converter with an h-bridge cell based on a volume evaluation of each component," *IEEE Trans. Ind. Electron.*, vol. 33, no. 3, pp. 1967–1984, Mar. 2018.

- [5] H. Iman-Eini and M. Liserre, "DC fault current blocking with the coordination of half-bridge MMC and the hybrid DC breaker," *IEEE Trans. Ind. Electron.*, vol. 67, no. 7, pp. 5503–5514, July 2020.

- [6] Q. Tu, Z. Xu, H. Huang, and J. Zhang, "Parameter design principle of the arm inductor in modular multilevel converter based HVDC," in *Int. Conf. Power System Technology*, December 2010, pp. 1–6.

- [7] Z. Xu, H. Xiao, and Z. Zhang, "Selection methods of main circuit parameters for modular multilevel converters," *IET Renew. Power Gener.*, vol. 10, no. 6, pp. 788–797, February 2016.

- [8] G. Tang, Z. He, K. Zha, X. Luo, Y. Wu, C. Gao, and H. Wang, "Type tests on mmc-based hvdc valve section with synthetic test circuits," *International Transactions on Electrical Energy Systems*, vol. 26, no. 9, pp. 1983–1998, 2016.

- [9] K. Liu, Q. Huai, L. Qin, S. Zhu, X. Liao, Y. Li, and H. Ding, "Enhanced fault current-limiting circuit design for a DC fault in a modular multilevel converter-based high-voltage direct current system," *Appl. Sci.*, vol. 9, no. 8, p. 1661, April 2019.

- [10] Z. Xu, H. Xiao, and et al, "DC fault analysis and clearance solutions of MMC-HVDC systems," *Energies*, vol. 11, no. 4, p. 941, April 2018.

- [11] F. Page, G. Adam, S. Finney, and et al, "DC fault parameter sensitivity analysis," in *IET Int. Conf. Dev. Power Syst. Prot.*, January 2014, pp. 1–6.

- [12] Y. Zhang, Y. Xu, and M. Saeedifard, "GitHub," https://github.com/ smartPEC/MOD\_MMCinductor.git.

- [13] N. Belda, C. Plet, C. Spallarossa, T. Kazuyori, and et al, "D5.1 HVDC Network Fault Analysis," Eur. Union's Horiz. 2020 Proj. Rep. - Prog. Meshed HVDC Offshore Transm. Networks, 2016.

- [14] R. Li, L. Xu, D. Holliday, F. Page, and et al, "Continuous operation of radial multiterminal HVDC systems under DC fault," *IEEE Trans. Power Del.*, vol. 31, no. 1, pp. 351–361, February 2016.

- [15] E. Kontos, S. Rodrigues, and et al, "Optimization of limiting reactors design for DC fault protection of multi-terminal HVDC networks," in IEEE Energy Convers. Congr. Expo., September 2014, pp. 5347–5354.

- [16] Y. Wang, W. Wen, C. Zhang, Z. Chen, and C. Wang, "Reactor sizing criterion for the continuous operation of meshed HB-MMC-based MTDC system under DC faults," *IEEE Trans. Ind. Appl.*, vol. 54, no. 5, pp. 5408–5416, September 2018.

- [17] Q. Huai, K. Liu, H. Ding, and L. Qin, "Protection scheme for multi-terminal HVDC system based on wavelet transform modulus maxima," *IEEJ T. Electr. Electr.*, vol. 15, pp. 1147–1159, March 2020.

- [18] J. Lutz, H. Schlangenotto, U. Scheuermann, and et al, Semiconductor Power Devices. Springer-Verlag Berlin Heidelberg, August 2010.

- [19] A. Baschnagel and U. Schlapbach, "Surge current capability of fast recovery diodes," *Power Electron. Eur.*, no. 8, 2007.

- [20] IEC-60747-2, "Semiconductor Devices Part 2: Discrete devices-Rectifier diodes," 2016.

- [21] "5SNA1200G450350 HiPak IGBT module datasheet," ABB Semi.

- [22] "5SNA1500G450350 HiPak IGBT module datasheet," ABB Semi.

- [23] Y. Zhang, H. Wang, Z. Wang, F. Blaabjerg, and M. Saeedifard, "Mission profile-based system-level reliability prediction method for modular multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 35, no. 7, pp. 6916–6930, Jul. 2020.

- [24] —, "System-level power loss evaluation of modular multilevel converters," in *Proc. Energy Convers. Congr. Expos (ECCE)*, 2019, pp. 6797–6804.

- [25] Z. Xu, Flexible DC transmission system, 2nd ed. China: China Machine Press, November 2016.

- [26] Z. He, L. Tu, Y. Yang, W. Xu, L. Ji, and H. Li, "System design of shetland VSC-HVDC transmission project," *Journal of Global Energy Interconnection*, vol. 1, no. 1, pp. 296–302, May 2018.

- [27] K. Ou, H. Rao, Z. Cai, H. Guo, X. Lin, L. Guan, T. Maguire, and et al, "MMC-HVDC simulation and testing based on real-time digital simulator and physical control system," *IEEE Trans. Emerg. Sel. Topics Power Electron.*, vol. 2, no. 4, pp. 1109–1116, December 2014.

- [28] B. Jiang and Z. Wang, "The key technologies of VSC-MTDC and its application in china," *Renew. Sust. Energ. Rev.*, vol. 62, pp. 297–304, September 2016.

- [29] A. Marzoughi, R. Burgos, D. Boroyevich, and Y. Xue, "Investigation and design of modular multilevel converter in AFE mode with minimized passive elements," in *Proc. IEEE Energy Conver. Congr. Expo. (ECCE)*, 2015, pp. 6770–6776.

- [30] K. Ilves, A. Antonopoulos, S. Norrga, and H.-P. Nee, "Steady-state analysis of interaction between harmonic components of arm and

- [31] P. Liu, Y. Wang, W. Lei, and W. Yao, "Parameter designing of arm reactor for modular multilevel converter," *Power Syst. Tech.*, vol. 39, pp. 1665–1671, Jun. 2015.

- line quantities of modular multilevel converters," *IEEE Trans Power Electron.*, vol. 27, no. 1, pp. 57–68, Jan. 2011.

- [32] IEC/TR62001-5, "High-voltage direct current (HVDC) systems- Guidance to the specification and design evaluation of AC filters Part 5: AC side harmonics and appropriate harmonic limits for HVDC systems with voltage sourced converters (VSC)," 2021.

- [33] IEEE Std 519-2014, "IEEE recommended practice and requirements for harmonic control in electric power systems," 2014.

- [34] B. Xu, S. Zhou, W. Lin, J. Wen, and G. Zhou, "Analysis of harmonics on the AC side of MMC based on harmonic equivalent circuit and fast simulation model," *Smart Grid*, vol. 4, pp. 279–284, March 2016.

- [35] S. Sirisukprasert, J. S. Lai, and T. H. Liu, "Optimum harmonic reduction with a wide range of modulation indexes for multilevel converters," in *IEEE Ind. Appl. Conf.*, 2000, pp. 2094–2099.

- [36] M. Guan, Z. Xu, Q. Tu, and W. Pan, "Nearest level modulation for modular multilevel converters in HVDC transmission," *Automation Electr. Power Syst.*, vol. 34, pp. 48–51, Jan. 2010.

- [37] J. Qin, M. Saeedifard, A. Rockhill, and R. Zhou, "Hybrid design of modular multilevel converters for hvdc systems based on various submodule circuits," *IEEE Trans. Power Delivery*, vol. 30, no. 1, pp. 385–394, Feb. 2014.

Yi Zhang (Member, IEEE) received the B.S. and M.S. degrees in electrical engineering from Harbin Institute of Technology, China, in 2014 and 2016, respectively, and the Ph.D. degree in power electronics from Aalborg University, Denmark, in 2020. He is currently a visiting researcher with RWTH-Aachen University, Germany. He was a visiting postdoctoral researcher with Swiss Federal Institute of Technology Lausanne (EPFL), Switzerland, 7.2022-1.2023. He was a DFF International Postdoc affiliated with both Aalborg

University and Massachusetts Institute of Technology, 2021-2022. He was a visiting scholar with Georgia Institute of Technology, USA, 11.2018-3.2019. His research interests includes reliability of power electronics.

Dr. Zhang received the First Place Prize Paper Award of the IEEE Transactions on Power Electronics in 2021, and the IEEE Power Electronics Society Ph.D. Thesis Talk Award Winner in 2020.

Yi Xu received the B.S. and Ph.D. degrees in Electrical Engineering from Wuhan University, Wuhan, China, in 2016 and 2022, respectively. From 2020 to 2021, she was a guest PhD student in AAU Energy, Aalborg University. She is currently a lecturer in the School of Electrical and Electronic Engineering, Hubei University of Technology. Her research interests include modeling and design of power converters, and fault analysis and current limiting technique of MMC-HVDC system.

Maryam Saeedifard (Fellow, IEEE) received the Ph.D. degree in electrical engineering from the University of Toronto, Toronto, Canada, in 2008. She is currently a professor in the School of Electrical and Computer Engineering at Georgia Institute of Technology, Atlanta, GA, USA, where she holds a Dean's Professorship. Her research interests include power electronics and applications of power electronics in power systems.