# **Aalborg Universitet**

# Single-Carrier Modulation for Neutral-Point-Clamped Inverters in Three-Phase **Transformerless Photovoltaic Systems**

Guo, Xiaoqiang; Cavalcanti, Marcelo C.: Farias, Alexandre M.: Guerrero, Josep M.

Published in: I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2012.2224138

Publication date: 2013

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Guo, X., Cavalcanti, M. C., Farias, A. M., & Guerrero, J. M. (2013). Single-Carrier Modulation for Neutral-Point-Clamped Inverters in Three-Phase Transformerless Photovoltaic Systems. *I E E Transactions on Power* Electronics, 28(6), 2635-2637. https://doi.org/10.1109/TPEL.2012.2224138

### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: June 18, 2025

# Single-carrier Modulation for Neutral-Point-Clamped Inverters in Three-Phase Transformerless Photovoltaic Systems

Xiaoqiang Guo, Member, IEEE, Marcelo C. Cavalcanti, Member, IEEE, Alexandre M. Farias, Student Member, IEEE, and Josep M. Guerrero, Senior Member, IEEE

Abstract—Modulation strategy is one of the most important issues for three-level neutral-point-clamped inverters in three-phase transformerless photovoltaic systems. A challenge for modulation is how to keep the common-mode voltages constant to reduce the leakage currents. A single-carrier modulation strategy is proposed. It has a very simple structure, and the common-mode voltages can be kept constant with no need of complex space vector modulation or multicarrier pulsewidth modulation. Experimental results verify the theoretical analysis and the effectiveness of the presented method.

Index Terms — Modulation, neutral-point-clamped inverter, common-mode voltage, transformerless photovoltaic system

X. Guo is with the Key Lab of Power Electronics for Energy Conservation and Motor drive of Hebei province,

Department of Electrical Engineering, Yanshan University, Qinhuangdao 066004, China (e-mail: guoxq@ieee.org)

M. C. Cavalcanti and A. M. Farias are with the Electrical Engineering and Power Systems Department, Federal

University of Pernambuco, 50730-540 Recife, Brazil (e-mail: marcelo.cavalcanti@ufpe.br; alexandre.farias@

J. M. Guerrero is with the Department of Energy Technology, Aalborg University, Aalborg DK-9220, Denmark (e-mail: joz@et.aau.dk).

rocketmail.com)

#### I. INTRODUCTION

Transformerless photovoltaic (PV) inverters have been received more and more attention due to cost and size reduction, as well as efficiency improvement, compared with the conventional transformer ones [1-11]. A number of technical challenges may arise with increased grid-connected transformerless PV systems. One of the most important issues is how to reduce or eliminate the leakage currents through the parasitic capacitor between the PV array and the ground. For three-phase neutral-point-clamped (NPC) transformerless PV systems, the modulation strategy should be carefully designed to retain the constant common mode voltages (CMV) to eliminate the leakage currents [3]. In general, there are two typical modulation strategies for three-phase NPC inverters. One is space vector modulation (SVM), and the other is the multicarrier pulsewidth modulation (PWM). SVM is more favorable from the viewpoint of the switching pulse pattern study, but it requires complex implementation such as switching vector selection, duty cycles calculation and vector sequence arrangement [12]. On the other hand, the multicarrier PWM is more attractive for implementation because it only needs to compare the reference and carrier signal to generate the switching gating signals. Cavalcanti, et al [3] has presented an interesting SVM method to keep CMV constant by using only the medium vectors and the zero vector to comprise the reference vector. In practice, however, its implementation is not an easy task as discussed before. For the multicarrier PWM solution, the common voltage problems can be mitigated by rearranging the multicarrier according to the vector region [13], which increases the computational burden. In order to overcome the abovementioned limitation, a single-carrier modulation strategy is proposed. It has a very simple structure, and the constant CMV can be achieved, with no need of complex SVM or multicarrier PWM.

#### II. PROPOSED METHOD

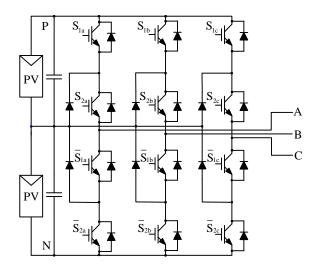

The schematic diagram of the three-phase NPC inverter is shown in Fig.1, where the system common mode voltage  $V_{\text{CM}}$  is defined as [3]

$$V_{\rm CM} = \frac{V_{\rm AN} + V_{\rm BN} + V_{\rm CN}}{3} \tag{1}$$

Fig. 1. Diode-clamped three-level inverter.

According to [3],  $V_{\rm CM}$  should be kept constant as  $V_{\rm PN}$  /2 to eliminate the leakage current. Considering that  $V_{\rm iN}$  (i=A, B, C) has three possible values ( $V_{\rm PN}$ ,  $V_{\rm PN}$  /2, 0), there are two ways to achieve the constant CMV, as listed in Table I.

# Case I: Switching strategy A

When the outer switches of  $S_{1a}$ ,  $\bar{S}_{2a}$ ,  $S_{1b}$ ,  $\bar{S}_{2b}$ ,  $S_{1c}$ ,  $\bar{S}_{2c}$  are off, and other inner switches are on,  $V_{AN} = V_{BN} = V_{CN} = V_{PN} / 2$ . Therefore, the CMV defined by (1) is constant as  $V_{PN} / 2$  [3].

## Case II: Switching strategy B

For the constant CMV of  $(V_{AN} + V_{BN} + V_{CN})/3 = V_{PN}/2$  [3], another switching strategy is presented. Considering that three possible values of  $(V_{PN}, V_{PN}/2, 0)$  of  $V_{iN}$  (i=A, B, C), the switch states should be configured to ensure that three possible values are evenly distributed among  $V_{AN}$ ,  $V_{BN}$ , and  $V_{CN}$ , as listed in Table I. For example, When the switches of  $\bar{S}_{1a}$ ,  $\bar{S}_{2a}$ ,  $S_{1b}$ ,  $\bar{S}_{2b}$ ,  $S_{1c}$ ,  $S_{2c}$  are off, and other switches are on,  $V_{AN} = V_{PN}$ ,  $V_{BN} = V_{PN}/2$  and  $V_{CN} = 0$ , as shown in line 3 of Table I. Therefore, the constant CMV of (1) can be achieved. In the same way, the other five switching states listed in Table I can achieve the constant CMV as well.

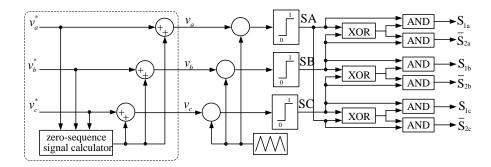

In order to achieve the abovementioned switching strategy A and B, a new single-carrier modulation strategy is presented in Fig.2, where the zero sequence signal is added to the reference signals to increase the voltage utilization.

Detailed information about zero sequence signal calculator can be found in [14] (See Part D of Section IV). The modulation signals of  $v_a$ ,  $v_a$  and  $v_c$  are compared with the carrier to generate the logic (0 or 1) signals of SA, SB and SC. The simple logic circuits behind three comparators are used to generate the specified gating signals to keep the constant CMV, regardless of output logic (0 or 1) of three comparators.

Note that there are eight possible states for SA, SB and SC, as listed in Table I. Take the line 2 for example, when SA=SB=SC=0, the switching states after the simple logic circuits in Fig.2 will be determined as follows:  $S_{1a}$ ,  $\overline{S}_{2a}$ ,  $S_{1b}$ ,  $\overline{S}_{2b}$ ,  $S_{1c}$ ,  $\overline{S}_{2c}$  are off, and other inner switches are on. This switching state is in good agreement with Case I (Switching strategy A). Therefore, the CMV is kept constant as  $V_{PN}/2$ . In the similar manner, the CMV can be achieved by other seven switching states, as listed in Table I.

In summary, it is clear that the constant common mode voltage can be achieved with the proposed single-carrier modulation strategy.

Fig. 2. Proposed single-carrier modulation strategy.

TABLE I

DEVELOPMENT OF SINGLE-CARRIER MODULATION FOR CONSTANT COMMON VOLTAGE

| SA | SB | SC | $S_{1a}$ | $\overline{S}_{2a}$ | $S_{1b}$ | $\overline{S}_{2b}$ | $S_{1c}$ | $\overline{S}_{2c}$ | $V_{ m AN}$                          | $V_{\scriptscriptstyle  m BN}$ | $V_{_{ m CN}}$       | $V_{_{\mathrm{CM}}}$ |

|----|----|----|----------|---------------------|----------|---------------------|----------|---------------------|--------------------------------------|--------------------------------|----------------------|----------------------|

| 0  | 0  | 0  | 0        | 0                   | 0        | 0                   | 0        | 0                   | V <sub>PN</sub> / 2                  | $V_{\rm PN}$ / 2               | $V_{\rm PN}$ / 2     | $V_{\rm PN}$ / 2     |

| 1  | 0  | 0  | 1        | 0                   | 0        | 0                   | 0        | 1                   | $V_{_{\mathrm{PN}}}$                 | $V_{\rm PN}$ / 2               | 0                    | $V_{\rm PN}$ / 2     |

| 1  | 1  | 0  | 0        | 0                   | 1        | 0                   | 0        | 1                   | $V_{\rm PN}$ / 2                     | $V_{_{\mathrm{PN}}}$           | 0                    | V <sub>PN</sub> / 2  |

| 0  | 1  | 0  | 0        | 1                   | 1        | 0                   | 0        | 0                   | 0                                    | $V_{_{\mathrm{PN}}}$           | $V_{\rm PN}$ / 2     | $V_{\rm PN}/2$       |

| 0  | 1  | 1  | 0        | 1                   | 0        | 0                   | 1        | 0                   | 0                                    | $V_{\rm PN}$ / 2               | $V_{_{\mathrm{PN}}}$ | $V_{\rm PN}/2$       |

| 0  | 0  | 1  | 0        | 0                   | 0        | 1                   | 1        | 0                   | V <sub>PN</sub> / 2                  | 0                              | $V_{_{\mathrm{PN}}}$ | V <sub>PN</sub> / 2  |

| 1  | 0  | 1  | 1        | 0                   | 0        | 1                   | 0        | 0                   | $V_{\scriptscriptstyle \mathrm{PN}}$ | 0                              | $V_{\rm PN}$ / 2     | $V_{\rm PN}$ / 2     |

| 1  | 1  | 1  | 0        | 0                   | 0        | 0                   | 0        | 0                   | V <sub>PN</sub> / 2                  | $V_{\rm PN}$ / 2               | V <sub>PN</sub> / 2  | V <sub>PN</sub> / 2  |

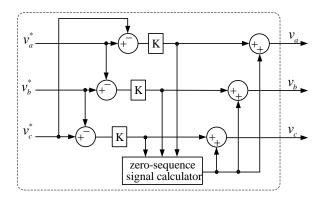

Note that the switching signals of each phase, e.g.  $S_{1i}$  and  $\overline{S}_{2i}$  (i=a, b, c), have the relationship with the other phase due to the logic circuits in Fig.2. This will lead to 30-degree phase shift from the modulation signal. A simple solution is to replace the previous modulation signals with the line-to-line reference signals, as shown in Fig.3, where the coefficient 'K' is used to avoid overmodulation (e.g. K=1/ $\sqrt{3}$ ).

Fig. 3. 30-degree phase shift compensation strategy.

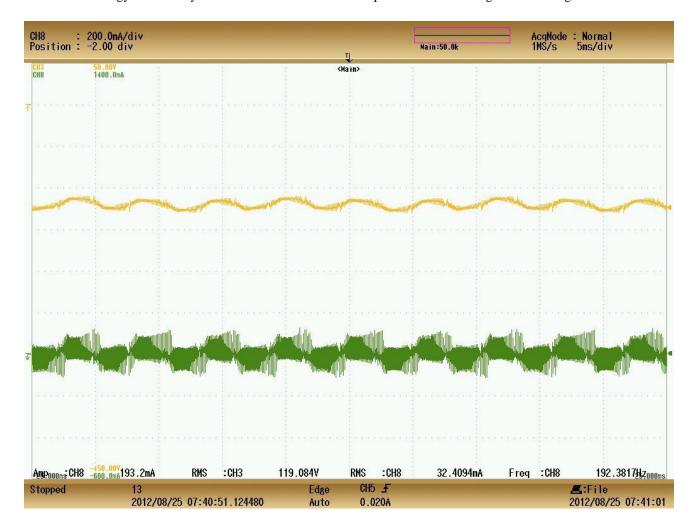

To evaluate the performance of the proposed modulation method, the experimental tests are carried out. The system parameters are switching period is 200us, dead time is 3.54us, load inductance is 5mH, load resistance is  $17\Omega$ , dc link voltage is 240V, modulation index is 0.9, parasitic capacitance is 220 nF, and ground resistance is  $15\Omega$ . The simple logic circuits in Fig.2 are implemented with analogy circuits (SN7486 for XOR and SN7408 for AND). Note that this letter focused on the switching strategy. Other issues such as the grid synchronization [15] and anti-islanding protection [16]

are beyond the scope of this paper.

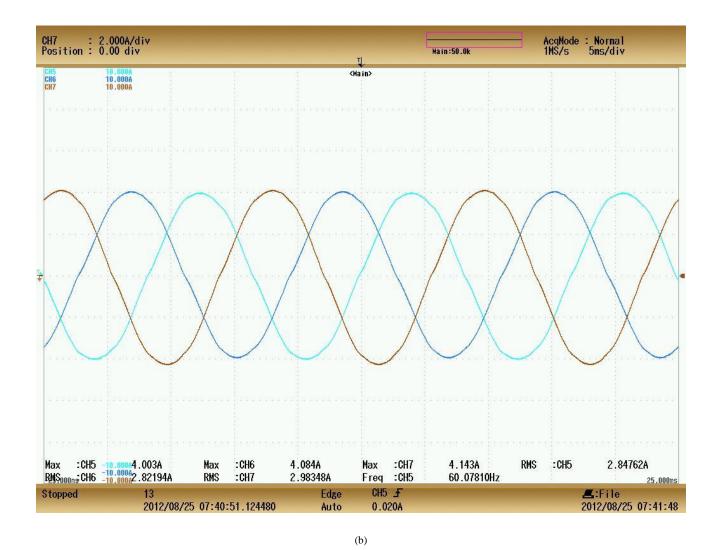

The experimental results are shown in Fig.4. From Fig.4 (a), it can be observed that the common mode voltage is kept almost constant with the value (119.084V) approximate equal to  $V_{PN}/2$ , which is in good agreement with the above theoretical analysis. The rms value of the leakage current is about 32.41mA, which is well below the VDE 0126-01-01 standard requirement of 300 mA. Fig. 4(b) shows the inverter output current waveform. In summary, the proposed modulation strategy will be very attractive for both sinusoidal output current and leakage current mitigation

Fig. 4. Experimental Results, (a) Common mode voltage and leakage current; (b) Inverter output currents

# IV. CONCULSION

A single-carrier modulation strategy has been presented for three-level neutral-point-clamped inverters in three-phase transformerless PV systems. It has the interesting feature that, with no need of complex space vector modulation or multicarrier pulsewidth modulation, the system common mode voltage can be kept constant, which is beneficial to the leakage current elimination. It also has a very simple structure, which is easy to implement by digital signal processors or analog circuits.

#### **REFERENCES**

- [1] R. Gonzalez, J. Lopez, P. Sanchis, and L. Marroyo, "Transformerless inverter for single-phase photovoltaic systems," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 693–697, Mar. 2007.

- [2] R. Gonzalez, E. Gubia, J. Lopez, and L. Marroyo, "Transformerless single-phase multilevel-based photovoltaic inverter," *IEEE Trans. Ind. Electron.*, vol. 55, no. 7, pp. 2694–2702, Jul. 2008.

- [3] Cavalcanti M.C., Oliveira K.C., Farias A.M., Neves F.A.S., Azevedo G.M., and Camboim F.C., 'Modulation techniques to eliminate leakage currents in transformerless three-phase photovoltaic systems', *IEEE Trans. Ind. Electron*, vol. 57, no. 4, pp. 1360-1368, Apr. 2010.

- [4] Araujo, S.V.; Zacharias, P.; Mallwitz, R.; "Highly efficient single-phase transformerless inverters for grid-connected photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 57, no. 9, pp. 3118–3128, Sep. 2010.

- [5] O. Lopez, F. D. Freijedo, A. G. Yepes, P. Fernandez-Comesaa, J. Malvar, R. Teodorescu, and J. Doval-Gandoy, "Eliminating ground current in a transformerless photovoltaic application," *IEEE Trans. Energy Convers.*, vol. 25, no. 1, pp. 140–147, Mar. 2010.

- [6] Kerekes, T.; Teodorescu, R.; Rodríguez, P.; Vázquez, G.; Aldabas, E., "A new high-efficiency single-phase transformerless pv inverter topology," *IEEE Trans. Ind. Electron.*, vol. 58, no. 1, pp.184–191, Jan. 2011.

- [7] W. Yu, J.-S Lai, H Qian and C. Hutchens "High-efficiency MOSFET inverter with H6-type configuration for photovoltaic nonisolated ac module applications," *IEEE Trans. on Power Electronics*, vol.26, no.4, pp.1253-1260, April 2011.

- [8] Huafeng Xiao; Shaojun Xie; Yang Chen; Ruhai Huang; "An optimized transformerless photovoltaic grid-connected inverter," *IEEE Trans. Ind. Electron.*, vol. 58, no. 5, pp. 1887–1895, May. 2011.

- [9] Bradaschia, F.; Cavalcanti, M.C.; Ferraz, P.E.P.; Neves, F.A.S.; dos Santos, E.C.; da Silva, J.H.G.M., "Modulation for three-phase transformerless z-source inverter to reduce leakage currents in photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 58, no. 12, pp. 5385–5395, Dec. 2011.

- [10] B. Yang, W. Li, Y. Gu, W. Cui, and X. He, "Improved transformerless inverter with common-mode leakage current elimination for a photovoltaic grid-connected power system"," *IEEE Trans. Power Electron.*, vol. 27, no. 2, pp. 752–762, Feb. 2012.

- [11] J.-M. Shen, H.-L. Jou, and J-C Wu, "Novel transformerless grid-connected power converter with negative grounding for photovoltaic generation system," *IEEE Trans. Power Electron.*, vol. 27, no. 4, pp. 1818–1829, Apr. 2012.

- [12] J. Rodriguez, L. G. Franquelo, S. Kouro, J. I. Leon, R. C. Portillo, M. A. M. Prats, and M. A. Perez, "Multilevel converters: An enabling technology for high-power applications," *Proc. IEEE*, vol. 97, no. 11, pp. 1786–1817, Nov. 2009.

- [13] Nguyen Van Nho; Hong-Hee Lee, "Analysis of carrier PWM method for common mode elimination in multilevel inverters," *EPE*, pp. 1–10, 2007.

- [14] Zhou K., and Wang D., 'Relationship between space-vector modulation and three-phase carrier-based PWM: A comprehensive analysis', *IEEE Trans. Ind. Electron*, vol. 49, no. 1, pp. 186–196, Jan. 2002.

- [15] D. Yazdani, A. Bakhshai, G. Joos, and M. Mojiri, "A nonlinear adaptive synchronization technique for grid-connected distributed energy sources," *IEEE Trans. Power Electron.*, vol. 23, no. 4, pp. 2181–2186, Jul. 2008.

- [16] M. Ciobotaru, V.G. Agelidis, R. Teodorescu, and F. Blaabjerg, "Accurate and less-disturbing active anti-islanding method based on PLL for grid- connected converters," *IEEE Trans. Power Electron.*, vol. 25, no. 6, pp. 1576-1584, Jun. 2010.