AALBORG

UNIVERSITY

Aalborg Universitet

## Modeling of Physical Unclonable Functions (PUF)

*A Systematic Literature Review*

Ferens, Mieszko; Dushku, Edlira; Kosta, Sokol

*Publication date:*

2025

*Document Version*

Early version, also known as pre-print

[Link to publication from Aalborg University](#)

### *Citation for published version (APA):*

Ferens, M., Dushku, E., & Kosta, S. (2025). *Modeling of Physical Unclonable Functions (PUF): A Systematic Literature Review*.

### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal -

### **Take down policy**

If you believe that this document breaches copyright please contact us at [vbn@aub.aau.dk](mailto:vbn@aub.aau.dk) providing details, and we will remove access to the work immediately and investigate your claim.

# Modeling of Physical Unclonable Functions (PUF): A Systematic Literature Review

Mieszko Ferens, Edlira Dushku, Sokol Kosta

**Abstract**—Hardware fingerprinting technologies are an integral part for security of interconnected devices, for which the Physical Unclonable Function (PUF) has attracted attention in industry and academia for over 20 years. PUFs exploit uncontrollable manufacturing variations to provide hardware-intrinsic secrets that are highly sensitive to physical tampering. However, many questions remain on the applicability of PUFs given the prominent existence of modeling techniques that allow to predict or manipulate these secret fingerprints. In this survey, we analyze the trends and state-of-the-art in PUF modeling from 222 papers obtained from a systematic search and screening process. Our results provide an extensive list of PUF designs and protocols, which we classify based on three main perspectives: application, operational, and defensive. Similarly, we list and classify modeling techniques based on the defined PUF models and learning algorithms. Most of the surveyed papers consider modeling techniques purely as a vulnerability. However, we also include the perspective of modeling as an enabler for lightweight sharing of PUF secrets. Finally, we provide an exhaustive knowledge base and identify gaps and promising directions for future work in the field.

**Index Terms**—physical unclonable function, modeling, machine learning, authentication, hardware security.

## I. INTRODUCTION

**I**N hardware security, a key goal is the development of effective primitives that enable secure supply chains, support a root-of-trust, and support cryptographic operations. Starting from the Integrated Circuit (IC) manufacturing, the manufacturer should not illegally use the design and Intellectual Property (IP) to, e.g., overproduce and sell ICs. It is also important to guarantee that the final device has not been tampered by, e.g., a hardware trojan. Moving to the operation of the final device, it should run on a root-of-trust which ensures a controlled hardware and software platform. Finally, the device should also be capable of cryptographic functions allowing it to authenticate and encrypt its communications.

In this landscape, Physical Unclonable Function (PUF) is a promising hardware fingerprinting technology that serves as a building block for the solutions that tackle these aforementioned problems [1]. PUFs exploit random manufacturing variations to create a hardware-intrinsic fingerprint, similar to how biometrics can be used in humans. The generated fingerprint is essentially a secret that may be used for identification and hardware validation. A standout feature of PUFs is the abundance of lightweight designs targeting low-cost devices [2]. Additionally, PUFs are inherently tamper-evident

Mieszko Ferens (corresponding author), Edlira Dushku and Sokol Kosta are with the Department of Electronic Systems, Aalborg University, Denmark (emails: mjfm@es.aau.dk, edu@es.aau.dk, sok@es.aau.dk, address: A. C. Meyers Vænge 15, 2450 København)

due to their sensitivity to hardware variations which are inevitably affected by invasive or probing techniques [3].

However, a large portion of PUF research has focused on modeling techniques for PUFs, which has become a significant point of controversy for the technology. Modeling techniques are required to support PUF applications in a few cases (e.g., for sharing a large PUF secret at a low memory cost) [4], but generally they are a liability due to the vulnerabilities they introduce [5]. PUF modeling is based on the prediction or manipulation of the PUF fingerprint, for which many different algorithms and threat models have been proposed [6]–[9]. As a result, in the last decade, the field of PUFs has sparked an arms race between secure PUF designs and algorithms capable of cloning them, which deserves an in-depth analysis.

In this paper, we perform a systematic literature review of PUF modeling starting from 2013 until the end of 2024, where most of the works in this domain have been published. The goal is to provide a comprehensive evolution of modeling techniques and PUF designs until the current state-of-the-art. Additionally, the scale of this study enables us to identify clear trends and gaps that we make apparent to the research community. We aim to aid any researcher or developer in selecting the direction of future work on PUFs by providing a comprehensive overview of PUF modeling. As such, the contributions of this paper are as follows:

- We systematically survey the literature on PUF modeling corresponding to more than 400 papers, and we classify different PUF architectures and protocols in regard to their main security features, implementation, and performance metrics.

- We identify the different types of modeling attacks and defensive measures proposed in the literature.

- We present a thorough analysis of modeling attempts (successful and unsuccessful) against different types of PUFs with and without different defensive measures.

- Based on the literature analysis, we discuss the trends and gaps in current PUF research and conclude with recommendations for future directions in both PUF system designs and modeling techniques.

### A. Related surveys and motivation

The systematic literature review of this paper (described in the next subsection) provides a list of surveys related to PUF modeling, and through a broader search, a larger list is obtained. As can be seen in Table I, previous surveys have focused on various aspects of PUF research, including general overview [11], [15], [17], [20], [22], protocols [10], [21], implementation [16], and recently, IoT applications [7],

TABLE I

RELEVANT SURVEYS ON PUF IN THE LAST DECADE.

| Survey                   | Year        | Focus                    | Security analysis | Modeling attacks |

|--------------------------|-------------|--------------------------|-------------------|------------------|

| Delvaux et al. [10]      | 2014        | PUF protocols            | Yes               | Yes              |

| Herder et al. [11]       | 2014        | PUF overview             | Yes               | Yes              |

| Ruhmair et al. [12]      | 2014        | PUF modeling attacks     | Yes               | Yes              |

| Zhang et al. [13]        | 2014        | Silicon PUFs and RO PUF  | Yes               | Yes              |

| Adames et al. [14]       | 2016        | Emerging PUF designs     | No                | No               |

| Halak et al. [15]        | 2016        | PUF overview             | No                | No               |

| Alkathieeri et al. [16]  | 2017        | FPGA implementations     | No                | No               |

| Chang et al. [17]        | 2017        | PUF overview             | Yes               | Yes              |

| Babaei et al. [18]       | 2019        | IoT applications         | Yes               | No               |

| Shamsoshoara et al. [19] | 2020        | IoT applications         | Yes               | No               |

| Ruhmair et al. [9]       | 2020        | PUF side-channel attacks | Yes               | Yes              |

| Yehoshuva et al. [8]     | 2021        | PUF invasive attacks     | Yes               | Yes              |

| Lokhande et al. [20]     | 2021        | PUF overview             | No                | No               |

| Mall et al. [21]         | 2022        | PUF protocols            | Yes               | No               |

| Khalfalla et al. [22]    | 2022        | PUF overview             | Yes               | Yes              |

| Al-Meer et al. [7]       | 2023        | IoT applications         | Yes               | Yes              |

| Santikellur et al. [6]   | 2023        | PUF modeling attacks     | Yes               | Yes              |

| Ferens et al. [23]       | 2023        | PUF modeling attacks     | No                | Yes              |

| Alhamarneh et al. [24]   | 2024        | IoT applications         | Yes               | No               |

| <b>This work</b>         | <b>2025</b> | <b>PUF modeling</b>      | <b>Yes</b>        | <b>Yes</b>       |

[24]. While most of these surveys include some remarks or summary of modeling attacks, they do not provide a depth that is proportional to the amount of research currently available on PUF modeling. Some recent surveys focus on PUF modeling attacks [6], [23], however, they do not provide a complete overview, choosing to focus on a limited set of PUF designs. Similarly, there are some surveys on specialized PUF attacks [8], [9], although they lack some recent developments in the field. Moreover, the beneficial perspective of modeling techniques is missing. Thus, there is a noticeable gap in the literature for a survey that provides a complete and updated overview.

### B. Methodology

To systematically search the literature, we focus on the Web of Science and Scopus databases. These databases index all the major scientific databases where PUF literature is published, including but not limited to IEEE, ACM, ScienceDirect, Springer, and Wiley. To identify relevant works to PUF modeling, we defined a set of keywords which encompass the PUF topic while including mentions of modeling or attacks:

((“physical unclonable function” OR “PUF”) AND (“modeling” OR “modelling” OR “attack”))

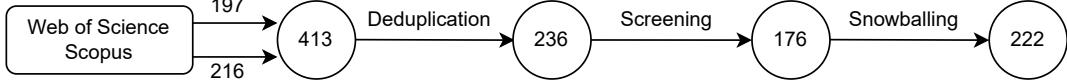

We also limited the search criteria to only include papers from 2013 until the end of 2024. Initially, we attempted to search the databases on a topic basis, where the set of keywords can appear in the title, abstract or keywords of the documents. This search provided us with 2055 and 1950 results in Web of Science and Scopus, respectively, showing that the query was too broad. Thus, we limited the appearance of the keyword set to only the document title for our second query, which provided 197 and 216 results, respectively.

After combining these results into 413 papers, we **removed all duplicates** without excluding similar or extended papers,

leaving 236. Then, we **screened all remaining papers** for relevancy in our study. Our criteria for inclusion in this paper were the following:

- 1) Proposing a novel PUF design, protocol or defensive mechanism that may tackle modeling attacks.

- 2) Evaluating some modeling technique on some PUF design, protocol or defensive mechanism.

While rare, not all papers approach the PUF modeling from a security perspective. These papers are included in our study as, fundamentally, they fit the topic. Additionally, some papers focus on other aspects, e.g., PUF performance, without considering modeling. These papers are also included in our study, as long as their contents somehow align with the inclusion criteria, even if it was not the intention of the authors. On the other hand, we exclude papers that:

- 1) Are not about PUFs.

- 2) Propose PUF applications, design extensions, or protocols that do not affect the modeling in any manner.

- 3) Are the original and more limited works of other extended papers included in this study.

- 4) Are not in English language.

- 5) Are not accessible to us<sup>1</sup>.

The screening process left us with 176 papers, to which we added 46 papers from a **snowballing process** performed in parallel, for a total of 222 papers. This total includes 6 of the survey papers<sup>2</sup> included in Table I. Our methodology is illustrated in Fig. 1.

### C. Organization

The rest of this paper is organized as follows. Section II presents the necessary background on PUFs and modeling

<sup>1</sup>We have access to all major publishers including IEEE, ACM, ScienceDirect, Springer and Wiley, as well as many others. In some rare cases, we are not able to access papers published in less known venues.

<sup>2</sup>The rest of the surveys from Table I were found through a general search on the topic of PUFs without following the described methodology.

Fig. 1. Systematic literature review methodology with deduplication, screening, and snowballing steps. The numbers indicate the number of papers after each step.

techniques. In Section III, the applications of PUFs are introduced, including the problems and solutions that arise from modeling techniques. Section IV presents the classification of PUF designs and shows the trends that have developed. Following, Section V complements the previous section on PUF designs by considering protocols that extend their functionality. Then, in Section VI the types of currently available modeling techniques and their details are provided. Section VII discusses the challenges that remain unsolved and provides a discussion with remarks towards the future goals of research in the field of PUFs. Finally, Section VIII concludes the paper.

## II. PRELIMINARIES

This section presents the necessary background on PUFs to understand the proposed designs and protocols up to date. It also serves to better understand the modeling of PUFs discussed later in the paper.

### A. Definition and basic operation

PUF is based on the idea that it is not possible to manufacture two exact replicas of the same hardware. Random manufacturing variations occur due to many factors such as physical impurities, temperature or pressure difference, among many others. Given that a manufacturer is not able to control these variations with current manufacturing technologies, it is widely accepted that PUFs are physically unclonable. Additionally, since a PUF implementation depends on its hardware, any physical tampering or probing inevitably changes the PUF, proving resilience against such attacks. Note that, we discuss some works that challenge this assumption in Section VI.

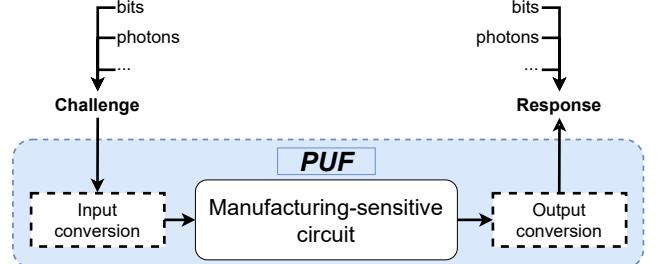

At a high level, a PUF module is expected to function by providing responses to challenges, as shown in Fig. 2. A challenge can be any type of stimuli applied to the PUF, ranging from a binary input to other physical stimuli, such as photons, depending on the PUF type. Similarly, the response of a PUF can also take any of the formats the challenge does. For many applications, it is convenient to provide both challenges and responses in binary form, thus, if required, some conversion circuitry can be included in the PUF system (optional input and output conversion in Fig. 2).

Ultimately, a commonly used term is the Challenge-Response Pair (CRP), which describes a single input challenge to the PUF, and its corresponding response. Based on their CRPs, PUF are evaluated according to a set of properties. While different works consider different sets of properties, we choose to present the fundamental properties that are always considered in PUF literature in one way or another, and that are essential to all PUF applications.

- **Reliability:** The ability of a PUF to provide the same responses to the same challenges, i.e., the consistency of

Fig. 2. Generic PUF module.

the CRPs. Since the CRPs are used to identify the device that possesses a PUF, or as inputs to other cryptographic functions, they are expected to be consistent. Given the correct response  $r$  to a challenge, the reliability of a PUF is calculated by obtaining  $t$  samples of the same response  $r'_i$  in different environmental conditions. These environmental conditions can be a difference in temperature, supply voltage, time (due to aging), among others. Assuming that the responses are converted to bits, and that each response is of  $m$  bits:

$$\text{Reliability} = \left(1 - \frac{1}{t} \sum_{i=1}^t \frac{HD(r, r'_i)}{m}\right) * 100\% \quad (1)$$

with  $HD(\cdot, \cdot)$  being the Hamming Distance of two binary strings. The ideal value for this metric is 100%.

- **Uniformity:** Assuming responses in binary form, the uniformity is the ratio of 1s to 0s in the responses of a PUF. It can be calculated from a set of responses  $r_i$  obtained from  $l$  different challenges:

$$\text{Uniformity} = \left(\frac{1}{l} \sum_{i=1}^l r_i\right) * 100\% \quad (2)$$

To ensure that the responses are hard to predict, uniformity has an ideal value of 50%.

- **Uniqueness:** The ability of a PUF to identify two devices, each with their own instance of the PUF, when responding to the same challenge. For  $d$  devices, each with their own response  $r_c$  of  $m$  bits, it can be calculated as the average Hamming Distance of the responses from the  $d$  PUFs, averaged over  $t$  different challenges:

$$\text{Uniqueness} = \frac{1}{t} \sum_{c=1}^t \left( \frac{2}{d * (d + 1)} \sum_{i=1}^{d-1} \sum_{j=i+1}^d \frac{HD(r_c^i, r_c^j)}{m} \right) * 100\% \quad (3)$$

The ideal value for this metric is 50%.

### B. Basics of modeling PUFs

A well-researched problem of PUFs is their clonability [6], [12], [23]. In essence, while a PUF is designed to provide unpredictable outputs to specific inputs (i.e., CRPs), it is possible to predict them through different methods. This is the fundamental idea of modeling PUFs and is the basis of modeling attacks. Note that PUF modeling can also be done in a trusted manner to, e.g., create a software copy of the PUF for a server that can then authenticate the PUF. The main difference between modeling attacks and the latter is that the restrictions on an attacker are usually considered to be stricter due to limited access to information on the PUF itself [25]. For example, an attacker may collect CRPs passively by eavesdropping on a PUF communication channel or actively by directly communicating with a PUF [26]. Meanwhile, a manufacturer could have access to measurements that are internal to the PUF circuit [27].

Regardless of the case, there are two main components for PUF modeling: (i) the model of the PUF and (ii) the learning algorithm. The model is a general representation of a specific PUF design that possesses some parameters that, when randomized, can perfectly define the behavior of a physical instance of the respective PUF design. On the other hand, the learning algorithm is the component responsible for approximating these parameters for a specific PUF instance. This process obviously requires data on the PUF instance (CRPs or side-channel information), e.g., fitting a model with a Machine Learning (ML) algorithm. With a good fit, the resulting fitted model can approximate the physical PUF instance so closely that other CRPs not present in the training data can also be predicted.

The success of PUF modeling depends on the accuracy of the model, the use of an adequate learning algorithm, and the availability of sufficient training data. For example, a popular model for the so-called Arbiter PUF [28] and XOR PUF [29] designs is the additive delay model [30], [31] (these PUFs and models are explained in more detail in Sections IV-B1 and VI-A1). However, while this model is linear with the former design, it is nonlinear with the latter. This means that one of the most popular ML modeling techniques, namely Logistic Regression (LR) [32], becomes ineffective in the nonlinear case despite it being the best modeling approach to date against the Arbiter PUF [33]. Instead, another popular approach is to use the Multi-Layer Perceptron (MLP) algorithm which adapts better to nonlinear models [29], [34], [35], but requires more data [36].

## III. KEY CONSEQUENCES OF PUF MODELING ON PUF APPLICATIONS

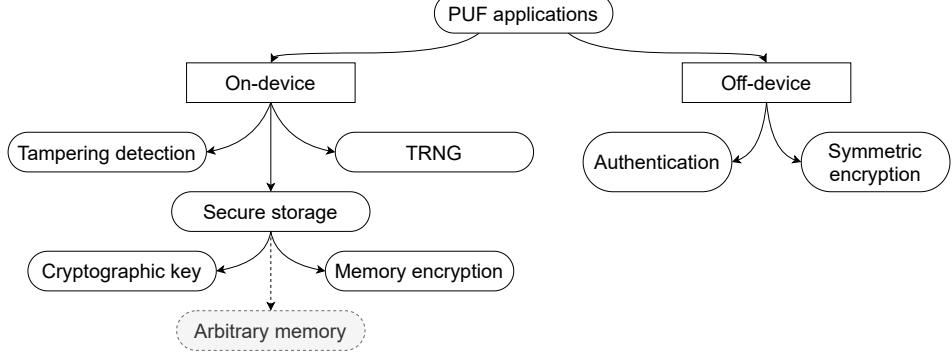

Looking back at the fundamental operation of PUFs from Section II-A, the core concept of a PUF is to provide a unique output to a specific input in the form of a CRP. A CRP functions as a unique token that only the device in possession of the corresponding PUF should be able to generate. This observation shows that a PUF is essentially a tamper-proof storage, which is widely applicable for different security applications. Fig. 3 shows a taxonomy of PUF applications

with examples for each. The first division in PUF applications separates the functional environment in which a PUF (more specifically its CRPs) operates: (i) internal or "on-device", and (ii) external or "off-device". Following, both categories and their specific subcategories (applications) are described.

### A. On-device applications

In the case of on-device applications the focus is on physical security and anti-tampering properties, with CRPs used only internally in the device that holds the PUF. Recall that a PUF acts as a secure storage on the device. However, the contents of the storage are randomized through the manufacturing process and cannot be controlled. Nevertheless, randomized tamper-proof memory is a valuable resource for the following applications.

- **Cryptographic key storage:** An obvious use case for tamper-proof memory is the storage of cryptographic keys [3]. The key could be used as a pre-shared secret (assuming a copy is distributed to other communication nodes) or to initialize a public-key cryptographic scheme. The main advantage of using PUF in this use case, is that adversaries cannot easily obtain this key from the device by invasive methods. This is especially relevant when dealing with memory readout attacks on powered-off devices, as the key is not stored in persistent memory and the PUF needs to generate it instead [25], [37].

- **Tamper-proof memory encryption:** Encrypting the data in a device's memory is an effective method to minimize the risk of adversaries obtaining some information, such as Intellectual Property (IP) [38]. To do so, a device would normally need an encryption key that should not be physically vulnerable on the same device. This proves challenging in absence of secure storage, but PUFs can solve the issue by generating the key on demand.

- **Detection of physical tampering:** Taking a step back and generalizing, a PUF can simply be used as a physical detection layer on an IC that measures its integrity [25]. An example can be found in [27], where a PUF measuring capacitance forms a cage that envelopes a circuit. Such a cage makes it exceedingly difficult to physically breach the circuit without affecting the PUF, which would then output different CRPs, allowing for tamper detection.

- **True Random Number Generation:** Granted a sufficiently large number of CRPs, they can be used as random numbers [39], [40]. The main advantage of PUFs as Random Number Generators (RNGs) is that they implement this function as a lightweight True RNG (TRNG) instead of a Pseudo RNG (PRNG).

Overall, on-device PUF applications can be a building block toward secure supply chain and early-stage integrity validation in a root-of-trust mechanism. Additionally, over-building and the sale of ICs on the black market can be prevented through identification of the generated unique PUFs [41]. Moreover, cryptographic functions can be supported with secure storage modules with guarantees on the randomness of the keys. Finally, PUFs have great flexibility due to the overwhelmingly large number of use cases for RNGs.

Fig. 3. PUF application taxonomy.

The assumption for the uncontrollable randomness of the CRPs of on-device PUFs is important for the previous applications. However, recent work has shown that this assumption may not always hold, when the CRPs of a Static Random Access Memory (SRAM) PUF were manipulated through a process called BTI aging [42]. Such a vulnerability would allow a manufacturer to maliciously control the contents of a PUF, although the authors of [42] proposed an anti-invasive countermeasure which fixed the vulnerability. As will be seen later, anti-invasive techniques form a small portion of the overall modeling techniques in PUF literature, showing the lack of knowledge in this regard. A positive note is that when not performed maliciously, the technique presented by [42] can be used to implement nonrandom secure and tamper-proof memory, enabling other potential applications that have not been explored to date.

#### B. Off-device applications

An arguably much more challenging scenario is when CRPs are exchanged and leave the tamper-proof premises of a device. When CRPs leave a device, one cannot guarantee that they do not fall into the hands of an adversary. Generally, this would not be a problem if CRPs were fully independent; however, many off-device applications only make sense in the presence of a large number of unique CRPs. As we will explain in Section IV-A, a Strong PUF can provide an exponential number of CRPs for its size at the cost of a correlation between them. Combine this with a malicious adversary and you get the majority of modeling attacks (see Section VI). Even so, many works have attempted to push through this limitation to provide the following applications.

- **Authentication:** An obvious use for the PUF's device-unique secret is to identify devices by checking the values of known CRPs [39], [43].

- **Pre-shared key symmetric encryption:** Extending the use of secure storage for cryptographic keys in on-device applications, a device could use a pre-shared symmetric key stored in a PUF for encrypted communications [21].

The main challenge of off-device applications is their susceptibility to modeling attacks due to exposed CRPs. The unified response from the research community to this problem has been to develop obfuscation techniques that prevent CRPs

from being sent in the clear (despite the potential lack of encrypted communications). Obfuscation applies especially to authentication applications, since authentication tends to precede encryption. However, for symmetric encryption schemes, the CRPs are not easily exploitable since they are not sent in the clear by default.

The remaining challenge is then to deploy a single unique PUF in a shared manner, since any communication requires both endpoints to share the CRPs provided by the PUF. The secure deployment of a PUF clone remains an open challenge, with previous work assuming that it is possible through the manufacturing process. One major concern is the memory complexity of storing millions or even billions of CRPs without a physical PUF. Ironically, a good solution to this problem comes from modeling techniques, as software PUF clones can be distributed instead [4]. However, for additional security the controlled physical manipulation of PUFs (as demonstrated by [42] on SRAM PUF) could be employed as well.

## IV. PUF CLASSIFICATION

The idea to use unique and intrinsic characteristics of materials has existed for many decades [44]. However, the term “Physical Unclonable Function” was not introduced until the early 2000s, when the use of intrinsic delays of wires and electronic components to identify ICs was proposed [30]. Since then, a plethora of ideas to uniquely identify electronic devices (typically involving ICs) have emerged [7], accompanied by a variety of applications.

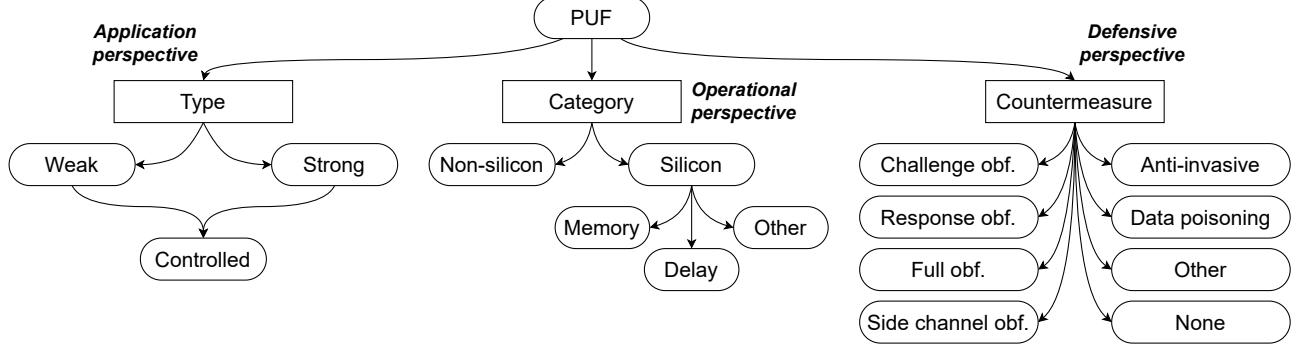

Due to the large number of PUF designs that have been proposed in the literature, it becomes necessary to classify them into groups. The classification process is not straight forward, as no standardized method exists. However, based on the large volume of literature surveyed in this paper, three dimensions to the classification have been identified: (i) **type** of PUFs based on their CRPs (application perspective), (ii) **category** of PUFs based on their operational principles (operational perspective), and (iii) **countermeasures** (if any) implemented into PUFs designs (defensive perspective). Fig. 4 shows a taxonomy for the classification with each perspective having subcategories that are explained in the following subsections.

Fig. 4. PUF classification taxonomy.

Additionally, Table II provides a list of PUF designs organized primarily based on their operational principle, with the other perspectives included as standard columns. Due to the large number of implementations (281 in total), Table II is limited to a single page, prioritizing designs that (i) appear in multiple studies, (ii) include complete performance data, and lastly (iii) are among the most recent. Note that this means that PUFs that appear multiple times in the literature have only one entry in Table II to save space. The full list is available in the appendices of this survey (see Appendix A).

#### A. Application perspective

Depending on the number of unique CRPs that can be extracted from a PUF, they are classified into Weak or Strong PUFs. Moreover, originating from these two classes, Controlled PUF can be defined.

- **Weak PUFs:** Weak PUFs are those that possess a number of unique CRPs linearly proportional to the number of basic components of the PUF. The advantage of a Weak PUF is that its CRPs have low correlation and may even be considered independent [102]. This makes it challenging to model the unknown CRPs based on known ones. However, note that a Weak PUF does not guarantee uncorrelated CRPs [103], [104]. Moreover, due to the limited number of CRPs, an attacker could clone the PUF in linear time by exhaustively recording all CRPs. Thus, the CRPs cannot be exchanged in the clear through an untrusted channel and are normally reserved for on-chip applications such as key generation [11], [13].

- **Strong PUFs:** Strong PUFs are those that possess a number of unique CRPs exponentially proportional to the number of basic components of the PUF. This characteristic prevents PUF cloning in linear time by exhaustively recording all CRPs, making Strong PUFs practical for off-chip applications where CRPs are sent in the clear over an untrusted channel, e.g., authentication. However, since different unique CRPs are generated from the same components of the PUF, they are correlated and exhibit limited entropy [2], [105]. The consequence is that Strong PUFs can become vulnerable to modeling attacks in which unknown CRPs are predicted based on previously known CRPs [102].

- **Controlled PUFs:** Controlled PUFs are those that use either a Weak or (typically) Strong PUF as their core. In addition to this, they implement control logic, e.g., a Random Number Generator (RNG) [106], Linear Feedback Shift Register (LFSR) [107], hash function [108], or fuzzy extractors [109]. Overall, a Controlled PUF enables complex modes of operation that allow for increased security (by implementing countermeasures) and reliable applications. It is worth noting that the definition of Controlled PUF is not consistent throughout the literature. For instance, some PUFs with additional modules might be called Strong PUFs instead [70], [72]. In this paper, we choose to consider as a Controlled PUF any PUF that, besides a single core PUF, incorporates additional elements that increase the difficulty of modeling. However, additional modules that do not affect the modeling do not classify the PUF as a Controlled PUF (e.g., only for increasing reliability [38], [110], [111] or uniqueness [112], [113]).

Looking at the types of PUFs that are addressed in the literature, the largest volume goes to Controlled PUFs with 65.1% of designs. Meanwhile, only 26% and 8.9% are purely Strong and Weak PUFs, respectively. As a security primitive, PUFs are expected to be unclonable and tamper-proof. However, repeated vulnerabilities have necessitated additional security mechanisms, leading mainly to the development of Controlled PUFs. Additionally, the extensive number of CRPs in Strong PUFs provides greater versatility, justifying their popularity in the literature over Weak PUFs. This popularity is reinforced by Weak PUFs already showing good resilience to attacks due to their low correlation CRPs. Since only a handful of recent studies successfully compromise them [42], [114], [115], researchers typically focus on the more challenging security problem of Strong PUFs.

#### B. Operational perspective

Based on their manufacturing, PUFs can be classified as:

- **Non-silicon PUFs:** Non-silicon PUFs are those that are based on the manufacturing variations of non-electrical components. The most common example are optical structures that modify light patterns that pass through them [99], [116], [117], although microscopic randomly

TABLE II

SHORT OVERVIEW OF PUF IMPLEMENTATIONS (SEE APPENDIX A FOR FULL VERSION). THE DISPLAYED AND TOTAL NUMBER OF ENTRIES ARE SHOWN AS (X / Y). PERFORMANCE VALUES ARE SELECTED BASED ON A REPRESENTATIVE WORST CASE SCENARIO. A '∞' SYMBOL INDICATES THAT THE VALUES ARE TAKEN FROM A VISUAL GRAPH AND ARE NOT EXACT. BLANK SPACES ARE INFORMATION THAT WAS NOT OBTAINABLE FROM THE REFERENCE. A '-' SYMBOL INDICATES NO COUNTERMEASURE.

generated structures in certain materials can also be used as a fingerprint [101]. Finally, an emerging idea is to fingerprint the components of quantum computers [100], [118].

- **Silicon PUFs:** Silicon PUFs are those that are based on the manufacturing variations in the fabrication of electrical components, mainly in ICs [81]. Typically, two subcategories are defined for Silicon PUFs: (i) memory-based PUFs and (ii) delay-based PUFs. Memory-based PUFs exploit the stabilization bias of memory components (memory cells) towards either 0 or 1 when left in an unstable state. Meanwhile, delay-based PUFs utilize the variation in latency of the propagation of electrical signals through electrical components and wires. Other subcategories could be defined, but previous work has not naturally converged towards further definitions. Thus, we consider a third general subcategory for “other” designs, as shown in Fig 4.

Comparing silicon and non-silicon PUFs shows a big difference in the ease of implementation. While a few proposals that could support optical systems have appeared [99], [116], they do not come close to the number of silicon PUFs which account for 98.1% of designs (observed in this survey). Even with the new emerging ideas to use PUFs as “quantum” primitives [100], [117], [118], the reliability and particularly specific use cases of non-silicon PUFs are a major challenge that holds them back. Meanwhile, the potential of a few practical silicon PUFs (mainly Arbiter PUF and SRAM PUF) has largely driven most PUF research over the past decade.

1) *The Arbiter PUF:* First, the Arbiter PUF [30] is the first and most promising Strong delay-based PUF to appear in the literature. It uses a chain of switch elements to generate an exponential number of CRPs at a low hardware cost. However, two problems have consistently persisted for Arbiter PUFs: the difficulty of implementing balanced delay paths in hardware, especially Field-Programmable Gate Arrays (FPGA) [49], and the correlation between CRPs viewed as a vulnerability. The implementation challenge is out of scope for this paper, but note that many works have successfully manufactured PUFs in a variety of FPGA platforms [55], [119]–[124] and even some Application-Specific Integrated Circuits (ASIC) [80], [125], [126].

More importantly, the correlation between CRPs is a problem that has been shown to be more challenging than could initially appear. This challenge alone has motivated an enormous number of Controlled PUF designs stemming from the Arbiter PUF. Firstly, designs such as FF-PUF [127], XOR PUF [128], [129], IPUF [56], [128], [130], LSPUF [128], [131], MPUF [62], [128], [132], Dual-mode PUF [51], and CT-PUF [48] (just to name a few), all extend the Arbiter PUF and have one thing in common: they increase the complexity of the model through more complicated wiring and additional basic components. This design strategy attempted to retain the main idea of the Arbiter PUF, that is, lightweight hardware identity with exponential CRPs. However, due to the escalating effectiveness of modeling attacks, most of the previous designs were shown to be vulnerable as well. Thus, a different approach which incorporates other modules was also strongly

argued in many papers leading to designs such as CRC-PUF [133], DFM-APUF [134], FLAM-PUF [54], RPUF [68], PUF-FSM [135], SRPUF [71], DCH PUF [50], etc. This approach (similarly to protocols in Section V) was more effective against modeling attacks, but certain vulnerabilities were still exposed (see Section VI).

2) *The SRAM PUF:* Aside from delay-based PUFs, memory-based are an important class. The earliest PUF of this type is the SRAM PUF [42], [136], which exploits the stabilization bias of SRAM memory cells towards a certain value. Based on this principle, the use of other memory technologies can also be exploited, e.g., with DRAM [137], [138], MRAM [79], [139], or flash memory [81]. The use of memory cells provides an important advantage to security as the bits generated by the memory cells bias is uncorrelated between them. However, the limited number of cells leads to a lower number of CRPs. To combat this limitation, other designs such as the BR PUF [140]–[142] and TBR PUF [140], [141] take inspiration from the Arbiter PUF and create a chain of memory cells, but this can obviously lead to some security concerns due to correlation between cells.

That said, overall, the amount of research into memory-based PUFs is lower than for delay-based. Fundamentally, this is because the best designs are the simple ones such as SRAM PUF that provide clear use cases for on-device applications with few security concerns regarding physical aspects [42].

3) *Other PUF designs:* As can be expected, there are efforts to improve PUFs by providing fundamentally new designs. Aside from delays and memory stabilization bias, capacitance has been exploited [27], [111], [143]. Similarly, voltage, current, or resistance (basically Ohm’s law) through electronic components can be applied to PUFs [110], [144].

Additionally, emerging technologies such as memristors can be leveraged to create PUFs [3], [145]. Another interesting example is the use of CMOS image sensors [146]. Finally, non-silicon materials have also been proposed to fabricate specialized PUFs [101]. Interestingly, many new designs share a striking similarity to the structure of an Arbiter PUF [147], [148].

### C. Defensive perspective

Given the existence of different attacks against PUF, many papers have proposed protocols, schemes, and techniques to mitigate them. The large-scale literature review conducted in this paper has allowed for the identification of common techniques. Thus, in this subsection, we provide a classification of the types of countermeasures that can be found in the literature, with explanations for each class. There are four fundamental countermeasures to modeling techniques: challenge obfuscation, response obfuscation, full obfuscation, and data poisoning. Additionally, special countermeasures to prevent side-channel and invasive attacks have also been proposed. Finally, certain countermeasures that cannot be grouped with the rest have also been proposed.

- **Challenge obfuscation:** Most modeling attacks on PUFs rely on the use of clear CRPs for training of an ML model (see Section VI). For this reason, a popular approach in PUF protocols as well as many Controlled

PUFs is to hide the challenge fully or partially from the attacker [149]–[153]. This obfuscation is typically done with some common control logic on both the verifier and the prover, so that they can generate matching challenges without the need to publicly exchange them through an insecure communication channel [154]. For example, a common PRNG can be used on both endpoints to generate the same challenges [155]. Note that there can be vulnerabilities associated with the added control logic.

- **Response obfuscation:** Similar to challenge obfuscation, response obfuscation is based on the idea that if an attacker does not possess clear CRPs, they cannot perform a modeling attack. In this case, instead of hiding the challenge information from the attacker, the response information is hidden [156]–[159]. This can be done by, e.g., hashing the response value with some other public information through some common hash function [160], or sending decoy responses so that the attacker does not know which corresponds to which challenge [161].

- **Full obfuscation:** As the name implies, full obfuscation combines both challenge and response obfuscation. By hiding both challenge and response information from the attacker, creating a sufficiently accurate CRP training set becomes even more challenging [80], [162]–[165]. It is important to mention that the more complex the PUF additional control logic becomes, the larger the possibility of other vulnerabilities. Additionally, the hardware and the protocol overhead of the design increases, which is an undesirable side effect.

- **Data poisoning:** Different from the previous approaches, data poisoning is based on the idea that the verifier and prover can control the CRPs that are used for the PUF application [26], [166]. The ability to control CRPs can be exploited to perform, e.g., adversarial counterattacks against the modeling attacks. The key characteristic of these countermeasures is that they do not limit the attacker’s ability to obtain CRPs in any way, but regardless, the modeling difficulty increases.

- **Side-channel obfuscation:** Not all modeling attacks, and attacks in general, are designed with CRPs in mind. A common idea to extract information from a PUF is to use side-channel information such as power traces [167], [168], Electromagnetic (EM) radiation [169], or reliability [119]. Side-channel information can be a grave threat to PUF security; thus, countermeasures that hide these traces have been proposed [170], [171].

- **Anti-invasive:** While widely considered to be physically unclonable, in rare cases PUFs have been successfully exploited through physical tampering [42], [115]. In response to this, specific anti-invasive countermeasures have been developed. Specifically, tampering is detected through capacitive cages [27], [111], [143], hardware trojans are prevented through an integrated state machine [172], and memory bit modification through Focused Ion Beam (FIB) aging is handled with specialized pre-charge [42] or transistor test circuits [115].

- **Other:** There exist a handful of countermeasures which do not fit into any of the previous groups [90], [173].

We specify these countermeasures as “Other” in Tables II, III, and IV.

- **None:** Obviously, many designs do not incorporate any specific countermeasure against modeling. We specify these cases as “-” in Tables II, III, and IV.

The need for resilience against modeling attacks has clearly motivated the implementation of countermeasures, since looking at the papers included in this survey only 28.5% do not include any countermeasures. Meanwhile, obfuscation techniques are extremely popular, with 29.4%, 23.4%, and 10.6% of PUFs implementing challenge, response, and full obfuscation, respectively. The lower proportion of full obfuscation techniques can be attached to the larger and undesirable hardware cost. In contrast, data poisoning techniques providing extremely low cost are very scarce with a 2.6%, arguably do the fact that they do not fundamentally prevent modeling attacks and only make them harder. Additionally, although side-channel and invasive techniques are a serious threat, their countermeasures are also rarely seen in literature with 2.1% and 3%, respectively. Finally, other not categorized countermeasures make up the remaining 0.4% of papers.

It is obvious that a popular trend has been to tackle modeling attacks with obfuscation [39]. However, the appearance of advanced attacks that break some of these methods can argue against their use. It is worth noting that some obfuscation techniques have not been broken or have had some initial vulnerability fixed by the same authors that proved them vulnerable. Thus, further research into this direction is not advisable. Instead, the lighter data poisoning solutions that may be more practical in low-cost applications deserve more attention. Moreover, side-channel and invasive vulnerabilities are also a mostly unexplored avenue.

## V. PROTOCOLS

The use of PUFs requires protocols depending on the application. Typically, these protocols are tied to functionality rather than security. However, in the topic of modeling of PUFs we can find papers that propose a PUF protocol as a countermeasure to modeling. These cases are different from a Controlled PUF because it is the way in which the PUFs are used that changes, not its operation. As such, protocols deserve their own section, but we will consider a similar classification to PUFs. This can be seen in Table III.

The first observation we can make is that all protocols that we found use an Arbiter PUF or derivative (except for two where it is unclear) for testing. Note that these protocols tend to be agnostic to the PUF (although they might require a Strong PUF) so this is just a choice by the authors. The second important observation is that when classifying the type of countermeasure they provide, almost all give some form of obfuscation to the CRPs. These observations make sense based on our previous statistics showing that Arbiter-based PUFs and obfuscation techniques have been by far the most researched. The only exceptions to this are an exchangeless key protocol [185] providing Weak PUF functionality, and a data poisoning technique [26] based on selective use of CRPs. Based on these data, our conclusions for the state of research

TABLE III

FULL OVERVIEW OF PUF PROTOCOLS. PERFORMANCE VALUES ARE SELECTED BASED ON A REPRESENTATIVE WORST CASE SCENARIO. A '∞' SYMBOL INDICATES THAT THE VALUES ARE TAKEN FROM A VISUAL GRAPH AND ARE NOT EXACT. BLANK SPACES ARE INFORMATION THAT WAS NOT OBTAINABLE FROM THE REFERENCE. A '-' SYMBOL INDICATES NO COUNTERMEASURE.

| Protocol                | Test target | Ref ID | Type       | Platform        | Reliability | Uniformity | Uniqueness | Countermeasure |

|-------------------------|-------------|--------|------------|-----------------|-------------|------------|------------|----------------|

| Selective CRPs          | Arbiter PUF | [26]   | Strong     | Simulation      | 97%         | 54%        | 50%        | Data poisoning |

|                         | FF-PUF      | [26]   | Controlled | Simulation      |             |            |            | Data poisoning |

|                         | IPUF        | [26]   | Controlled | Simulation      |             |            |            | Data poisoning |

|                         | LSPUF       | [26]   | Controlled | Simulation      |             |            |            | Data poisoning |

|                         | XOR PUF     | [26]   | Controlled | Simulation      | 86%         | 51%        | 50%        | Data poisoning |

| Deception               | Arbiter PUF | [108]  | Controlled | Xilinx Artix-7  | 93.90%      | ~47%       | ~40%       | Full obf.      |

|                         | FF-PUF      | [108]  | Controlled | Simulated       |             |            |            | Full obf.      |

|                         | XOR PUF     | [108]  | Controlled | Simulated       |             |            |            | Full obf.      |

| AES                     | XOR PUF     | [174]  | Controlled | Simulated       |             |            |            | Challenge obf. |

|                         | XOR PUF     | [160]  | Controlled | Simulated       |             |            |            | Challenge obf. |

| DES                     | XOR PUF     | [174]  | Controlled | Simulated       |             |            |            | Challenge obf. |

|                         | XOR PUF     | [160]  | Controlled | Simulated       |             |            |            | Challenge obf. |

| Lockdown                | Arbiter PUF | [155]  | Controlled | 0.18um CMOS     |             |            |            | Challenge obf. |

|                         | XOR PUF     | [75]   | Controlled | Simulated       |             |            |            | Challenge obf. |

| Noise bifurcation       | XOR PUF     | [161]  | Controlled | Simulated       |             |            |            | Challenge obf. |

|                         | XOR PUF     | [175]  | Controlled | Simulated       |             |            |            | Challenge obf. |

| Permutation Interface   | Arbiter PUF | [176]  | Controlled | Simulated       |             |            |            | Challenge obf. |

|                         | XOR PUF     | [176]  | Controlled | Simulated       |             |            |            | Challenge obf. |

| Response inversion      | Arbiter PUF | [177]  | Controlled | Xilinx Artix-7  |             |            |            | Response obf.  |

|                         | XOR PUF     | [178]  | Controlled | Simulated       |             |            |            | Response obf.  |

| Slender PUF             | LSPUF       | [109]  | Controlled | Simulated       |             |            |            | Full obf.      |

|                         | XOR PUF     | [179]  | Controlled | Xilinx Virtex-5 | 75.3%       |            |            | Full obf.      |

| Reverse Fuzzy Extractor | Arbiter PUF | [109]  | Controlled | Simulated       |             |            |            | Response obf.  |

| Challenge Splitting     | Arbiter PUF | [180]  | Controlled | Xilinx Artix-7  |             |            |            | Challenge obf. |

| Challenge Permutation   | Arbiter PUF | [181]  | Controlled | Xilinx Artix-7  | 99.99%      | 61.00%     |            | Challenge obf. |

| CoLAC                   | Arbiter PUF | [182]  | Controlled | Xilinx Artix-7  | 98.22%      |            |            | Response obf.  |

| DAUP                    | Arbiter PUF | [183]  | Controlled | Xilinx Artix-7  |             |            |            | Challenge obf. |

| ECC                     | XOR PUF     | [184]  | Controlled | Simulated       |             |            |            | Response obf.  |

| Exchangeless Key        |             | [185]  | Weak       |                 |             |            |            | -              |

| Noise Injection         | Arbiter PUF | [186]  | Strong     | Simulated       |             |            |            | Data poisoning |

| RFID Auth               |             | [187]  | Controlled |                 |             |            |            | Full obf.      |

**AES:** Advanced Encryption Standard, **DES:** Data Encryption Standard, **CoLAC:** Coordinated and Lightweight Adversarial Machine Learning-based Countermeasure, **DAUP:** Distributed Authentication Using PUFs, **ECC:** Error Correction Code, **RFID:** Radio Frequency Identification

of protocols are the same as for PUF designs in the previous section.

## VI. MODELING TECHNIQUES

This section describes the types of PUF models that have been applied to date. We also classify the modeling techniques that have been presented in the literature. The result of this study highlights which research directions in PUF modeling are successful and which are not. Additionally, we identify the research gaps in the literature.

Table IV lists the modeling attempts on different PUF designs and protocols. Due to the large scale of this study and the fact that many papers perform modeling attempts on the same PUF implementation but with varying parameters, we choose to include in Table IV only one modeling attempt from each paper. Regarding cases where a PUF implementation is tested with and without a countermeasure, we include both. However, if many countermeasures are considered and evaluated in different combinations, we only include the most challenging countermeasure combination for modeling. Our decision for including a modeling instance is based on the following priority order: (i) the largest (and most complex) parameters for implementation where the accuracy shows a successful modeling attack (above 90%), (ii) the largest (and

most complex) parameters for implementation where the accuracy show improvement from random guessing (not close to 50%), and (iii) the smallest (and least complex) parameters for implementation where the accuracy shows a failed modeling attack (around 50%). Even with the previous criteria, the total number of entries scales to 275 modeling attempts, so Table IV is cut to one page with priority for the more popular techniques and successful attempts. We again refer readers interested in the full table to the appendices (see Appendix B).

### A. Types of PUF models

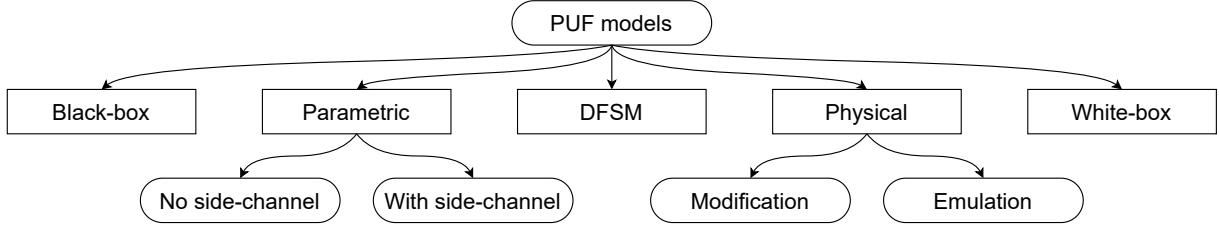

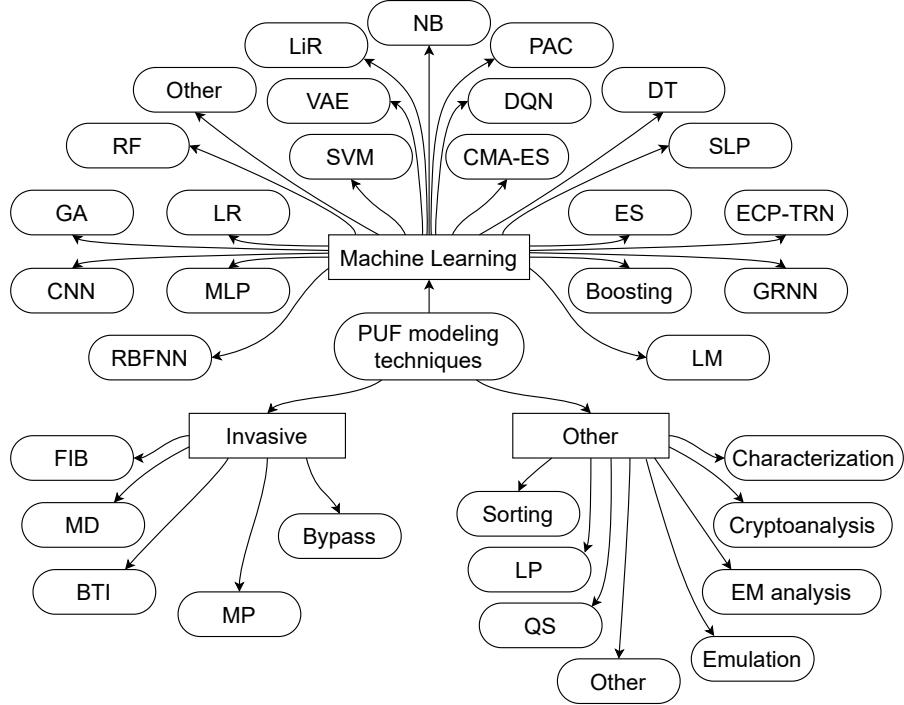

An essential element for effectively modeling a PUF is the use of a model. From analyzing the literature, in this survey, we identify five main model types: (i) parametric, (ii) Deterministic Finite-State Machine, (iii) black-box, (iv) white-box, and (v) physical. Fig. 5 shows the taxonomy for these models, also used in Table IV for each entry.

- **Parametric model:** This model is based on the idea that certain PUFs can be defined as mathematical functions with a set of randomly generated parameters. These parameters are randomized by the manufacturing process of the PUF and considered to be unknown. Thus, the modeling problem becomes a problem of approximating

TABLE IV

SHORT OVERVIEW OF PUF MODELING TECHNIQUES (SEE APPENDIX B FOR FULL VERSION). THE DISPLAYED AND TOTAL NUMBER OF ENTRIES ARE SHOWN AS (X / Y). PERFORMANCE VALUES ARE SELECTED BASED ON A REPRESENTATIVE WORST CASE SCENARIO. A '≈' SYMBOL INDICATES THAT THE VALUES ARE TAKEN FROM A VISUAL GRAPH AND ARE NOT EXACT. BLANK SPACES ARE INFORMATION THAT WAS NOT OBTAINABLE FROM THE REFERENCE. A '-' SYMBOL INDICATES NO COUNTERMEASURES.

| Attack                      | Ref ID                 | PUF/protocol       | Countermeasure     | Model           | CRPs            | Time†        | Accuracy |

|-----------------------------|------------------------|--------------------|--------------------|-----------------|-----------------|--------------|----------|

| MLP (7 / 88)                | [188]                  | DEPUF              | -                  | Parametric      | $6*10^4$        |              | ~94%     |

|                             | [189]                  | FF-IPUF            | Challenge obf.     | Parametric + SC | $10^6$          |              | 96.85%   |

|                             | [128]                  | MPUF               | Challenge obf.     | Black-box       | $3.2*10^5$      | 0:15:23.0    | 96.54%   |

|                             | [177]                  | Response inversion | Response obf.      | Black-box       | $5*10^3$        |              | 95.70%   |

|                             | [190]                  | RF-PUF             | -                  | White-box       |                 |              | 99.99%   |

|                             | [191]                  | SCA PUF            | -                  | Parametric      | $3.5*10^2$      |              | 97%      |

|                             | [26]                   | Selective CRPs     | Data poisoning     | Black-box       | $9*10^4$        |              | ~95%     |

| LR (5 / 54)                 | [31]                   | Arbiter PUF        | -                  | Parametric      | $6.5*10^3$      | 0:0:0.76     | 99%      |

|                             | [192]                  | CRO XMPUF          | -                  | Parametric + SC | $10^4$          |              | ~98%     |

|                             | [60]                   | LP-PUF             | Full obf.          | Parametric      | $5*10^5$        |              | ~100%    |

|                             | [161]                  | Noise bifurcation  | Challenge obf.     | Parametric      | $5*10^5$        | 05:00:00     | 92%      |

|                             | [193]                  | XbarPUF            | -                  | Black-box       | $5*10^3$        |              | 99.0%    |

| SVM (3 / 30)                | [194]                  | FF-PUF             | Challenge obf.     | Parametric + SC | $10^3$          |              | ~91%     |

|                             | [195]                  | STT-MRAM PUF       | -                  | Black-box       | $10^5$          |              | ~95%     |

|                             | [141]                  | XOR BR PUF         | Response obf.      | Parametric      | $7.2*10^3$      | 0:0:24.0     | 95%      |

| CMA-ES (2 / 25)             | [108]                  | Deception PUF-FSM  | Full obf.          | Parametric + SC | $2*10^6$        | 228 years    | 99%      |

|                             | [196]                  |                    | Response obf.      | Parametric      | $10^2$          |              | ~100%    |

| Machine Learning (33 / 246) | ES (1 / 9)             | [179]              | Slender PUF        | Full obf.       | Black-box       | $6.4*10^4$   | ~93%     |

|                             | RF (1 / 7)             | [58]               | LBIST-PUF          | Challenge obf.  | Black-box       | $6*10^4$     | ~93%     |

|                             | Boosting (1 / 4)       | [197]              | MRO-PUF            | Response obf.   | Black-box       | $5*10^4$     | ~98%     |

|                             | CNN (1 / 4)            | [198]              | RO PUF             | -               | Parametric + SC | $2*10^5$     | 92.8%    |

|                             | VAE (1 / 4)            | [174]              | AES                | Challenge obf.  | Black-box       | $2.5*10^2$   | 63.9%    |

|                             | DQN (1 / 3)            | [199]              | Arbiter PUF        | -               | DFSM            | $10^4$       | 94.98%   |

|                             | DT (1 / 3)             | [88]               | HP mem-PUF         | -               | Black-box       | $1.2*10^5$   | ~85%     |

|                             | ECP-TRN (1 / 3)        | [75]               | Lockdown           | Challenge obf.  | Black-box       | $4.8*10^6$   | 00:48:12 |

|                             | GA (1 / 3)             | [200]              | Current Mirror PUF | -               | Parametric      | $5*10^4$     | 26:18:00 |

|                             | SLP (1 / 2)            | [140]              | TBR PUF            | -               | Black-box       | $5*10^4$     | ~95%     |

|                             | GRNN                   | [201]              | XOR PUF            | Response obf.   | Parametric      | $7*10^4$     | 99.64%   |

|                             | LM                     | [202]              | RNN SCA-PUF        | Challenge obf.  | Parametric      | $2*10^6$     | ~54%     |

|                             | LiR                    | [196]              | RPUF               | Challenge obf.  | Parametric      | $1.024*10^3$ | ~90%     |

|                             | NB                     | [52]               | DyAdv PUF          | Response obf.   | Black-box       | $7*10^4$     | ~52%     |

|                             | PAC                    | [203]              | Arbiter PUF        | -               | DFSM            |              |          |

|                             | RBFNN                  | [46]               | CBDC-PUF           | -               | Parametric      | $10^4$       | 50.9%    |

|                             | ...                    | ...                | ...                | ...             | ...             | ...          | ...      |

| Invasive (5 / 8)            | FIB (1 / 3)            | [204]              | SRAM PUF           | -               | Physical        | $1.6*10$     | 00:05:00 |

|                             | BTI (1 / 2)            | [42]               | SRAM PUF           | -               | Physical        |              | Success  |

|                             | Bypass                 | [27]               | Capacitive PUF     | Anti-invasive   | Physical        |              | 98.64%   |

|                             | MD                     | [27]               | Capacitive PUF     | Anti-invasive   | Physical        |              |          |

|                             | MP                     | [27]               | Capacitive PUF     | Anti-invasive   | Physical        |              |          |

|                             | ...                    | ...                | ...                | ...             | ...             | ...          | ...      |

| Other (10 / 21)             | Sorting (1 / 3)        | [205]              | CIS PUF            | -               | Parametric      | ~20          | ~90%     |

|                             | LP (1 / 3)             | [206]              | Xbar PUF           | -               | Parametric + SC | $1.288*10^3$ | 00:12:48 |

|                             | Cryptoanalysis (1 / 2) | [207]              | RO PUF             | Response obf.   | Parametric + SC |              | ~100%    |

|                             | Characterization       | [208]              | Arbiter PUF        | -               | Parametric      | $10^6$       | 83.7%    |

|                             | EM analysis            | [67]               | RO PUF             | -               | Parametric + SC | 0            | 94.2%    |

|                             | Emulation              | [208]              | Arbiter PUF        | -               | Physical        |              | 75.5%    |

|                             | QS                     | [31]               | RO PUF             | -               | Parametric      | $8.39*10^4$  | 99%      |

|                             | -                      | [63]               | NoPUF              | Challenge obf.  | Parametric      |              | ~92%     |

|                             | -                      | [99]               | NOS PUF            | -               | Physical        |              | ~100%    |

|                             | -                      | [209]              | XMPUF              | Challenge obf.  | Black-box       | $10^4$       | 94%      |

|                             | ...                    | ...                | ...                | ...             | ...             | ...          | ...      |

†Format is "hours : minutes : seconds" (hh:mm:ss), unless directly specified with other units in the case of times longer than 48 hours.

**BTI:** Bias Temperature Instability, **CMA-ES:** Covariance Matrix Adaptation Evolutionary Strategies, **CNN:** Convolutional Neural Network, **DQN:** Deep Q-Network, **DT:** Decision Tree, **ECP-TRN:** Efficient CANDECOM/PARAFAC-Tensor Regression Network, **ES:** Evolutionary Strategies, **FIB:** Focused Ion Beam, **GA:** Genetic Algorithm, **GRNN:** General Regression Neural Network, **LM:** Lagrange Multiplier, **LiR:** Linear Regression, **LP:** Linear Programming, **LR:** Logistic Regression, **MD:** Micro-drilling, **MLP:** Multi-Layer Perceptron, **MP:** Magnetic Probing, **NB:** Naive Bayes, **PAC:** Probably Approximately Correct, **QS:** Quick Sort, **RBFNN:** Radial Basis Function Neural Network, **RF:** Random Forest, **SLP:** Single-Layer Perceptron, **SVM:** Support Vector Machine, **VAE:** Variational Auto-Encoder

Fig. 5. PUF model type taxonomy.

the values of these parameters until full emulation of the PUF is achieved. An important note is that certain parametric models utilize side-channel information [168], [210]–[212], which is specified in Table IV as "+ SC". Many different parametric models have been defined, although the specifics of all parametric models that are used in the literature surveyed by this paper are too broad (and not included in Table IV). However, we do provide an explanation of the most popular option in Section VI-A1 - the so-called additive delay model [30], [213].

- **Deterministic Finite-State Machine (DFSM) model:** As the name suggests, this model is based on the idea that a PUF's operation for generating an output can be modeled by states and transitions. Similarly to the parametric model, the challenge is to define a state machine that adequately conveys the inner working of the PUF in question. This is hard for a PUF such as the SRAM PUF [214], since you would require an independent state machine for each bit where the state transitions are dependent on factors internal to the physical components of the SRAM module. Instead, for, e.g., an Arbiter PUF, a DFSM representation makes far more sense as the transitions will be dependent on the input challenge. Despite many candidates for such a model existing (see Table II), very few works make such attempts. However, we were able to find two examples [199], [203].

- **Black-box model:** When no known mathematical model can be applied to a PUF (or even if one exists), a different option is simply treating the PUF as a black-box. As a black-box, the PUF turns into an unknown function which must be approximated using an adequate technique [215]–[217]. This modeling is enabled by the advances in ML techniques, and especially Neural Networks (NNs) capable of theoretically approximating any function given enough data [218], [219]. However, this form of modeling is generally less effective than when a pre-defined model is available, since a larger amount of input-output data is required and there is no guarantee of successfully approximating the unknown function [220], [221]. That said, this black-box approximation remains a realistic threat to PUF that is enhanced by further advances in the field of ML [5], [35]. It is important to note that some papers describe an existing model for their target PUF but proceed to perform an attack using a black-box model. In this paper we consider any modeling technique that does not explicitly define a model and

tailored technique as black-box.

- **White-box model:** In complete opposition to the black-box approach, the white-box model assumes that modeling is performed with complete access and design information for the PUF. The main argument for this approach is to create a PUF clone legally to support the applications of PUFs. On the other hand, it is obvious that white-box modeling is unrealistic for adversaries (aside from a single party charged with all steps of PUF manufacturing and supply).

- **Physical model:** These methods differ from the previous approaches as they use the physical design and characteristics of the PUF instead of defining mathematical models. The methods to physically model a PUF are either through emulation of physical characteristics [208] or by physically modifying a PUF [42], [115].

When looking at the presence of the previous models in the literature, black-box modeling overshadows the rest with 52.8% of cases. It is easy to conclude that the ease of use and availability of advanced ML techniques influences this statistic. Meanwhile, parametric modeling is a strong second choice with 29.2%, to which we should add another 12% when including side-channel information. The popularity in this case is explained with the undeniable effectiveness of the techniques when properly applied. On the other hand, the use of DFSM was only shown to be theoretically possible in [203], and further simplified and experimentally proven in [199]. The lack of research in this direction puts it at a very low 0.4%. Similarly, white-box modeling is only seen 0.8% of the time, because the threat model is less realistic for adversaries. Finally, physical cloning shows promise with 4.8% but moderated by the stricter entry barrier for researchers. Following, we describe some representative examples of each model type, excluding black-box as all such models are inherently unknown internally.

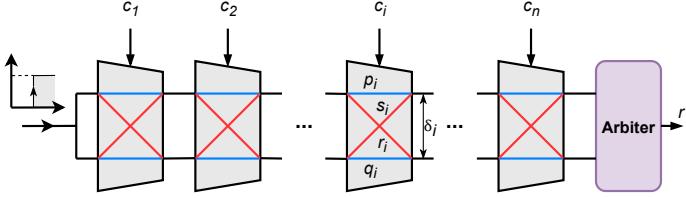

1) *(Parametric) additive delay model:* Starting with parametric models, the most well-known PUF model is the additive delay model, initially proposed for the Arbiter PUF [30], [213]. Its importance comes from the fact that the Arbiter PUF, as shown in Fig. 6, is the building block for most other delay-based PUF designs (see Section IV-B1).

In the context of the Arbiter PUF, the additive delay model considers each stage as an individual switch element (e.g., multiplexer). Consider the  $i$ -th stage. The delay between both inputs to their corresponding outputs is determined by four critical delay parameters:  $p_i$ ,  $q_i$ ,  $r_i$ ,  $s_i$ . The key idea of the model is that each stage adds a delay between its outputs

Fig. 6. Schematic view of  $n$ -bit Arbiter PUF.

without interference from the other stages (hence the term "additive" model). Following the previous example, the  $i$ -th stage's delay can be expressed as  $\delta_i$ . Based on the input to the Arbiter PUF, i.e., the challenge  $\vec{C} = [c_1, \dots, c_n]$ , this delay can take two values:

$$\delta_i^{c_i} = \begin{cases} p_i - q_i, & c_i = 0 \\ r_i - s_i, & c_i = 1 \end{cases} \quad (4)$$

Using both these values, one can define each stage based on the difference between these delays, while adding the common delays that all paths have from the previous stage. The only exception is the first stage, since it does not have any stages prior to it. Thus, we can define the Arbiter PUF as  $\vec{w} = [w_1, \dots, w_{n+1}]$ , with each parameter defined as:

$$w_i = \begin{cases} \frac{\delta_1^0 - \delta_1^1}{2}, & i = 1 \\ \frac{\delta_{i-1}^0 + \delta_{i-1}^1 + \delta_i^0 - \delta_i^1}{2}, & \forall i \in [2, n] \\ \frac{\delta_n^0 + \delta_n^1}{2}, & i = n+1 \end{cases} \quad (5)$$

Notice that there are  $n+1$  elements instead of  $n$ . This is because the common delay from previous stages must be considered for all stages except the first, however the term  $w$  is defined including only the previous stage. Thus, we need the additional  $w_{n+1}$  term to include the common delay of the  $n$ -th stage. For additional information regarding the additive delay model, including the details for how to define  $w_i$ , we refer the reader to [213].

Finally, given the Arbiter PUF parameters ( $\vec{w}$ ), the output  $r$  can be calculated as:

$$r = \text{sign}(\vec{w}^T \vec{\Phi}) \quad (6)$$

where  $\Phi$  represents the input challenge  $\vec{C}$  transformed from its binary form<sup>3</sup>:

$$\vec{\Phi}(\vec{C}) = [\Phi_1(\vec{C}), \dots, \Phi_n(\vec{C}), 1] \quad (7)$$

$$\Phi_i(\vec{C}) = \prod_{i=1}^n (-1)^{c_i} \quad (8)$$

The additive delay model can obviously be extended to delay-based PUF designs that incorporate Arbiter PUFs. Clear examples are the FF-PUF [222], XOR PUF [223], LSPUF [61], MPUF [132], IPUF [224] or DAPUF [225]. We note that many other delay-based designs from Table II use Arbiter PUFs, although in many cases they include modules (Controlled PUFs) which make it challenging to adapt the

<sup>3</sup>By binary form we refer to the fact that the challenge bits  $c_i = \{0, 1\}$ . Some authors convert this to  $c_i = \{-1, 1\}$ , respectively. In that case, the definition of  $\Phi_i(\vec{C})$  in (8) should be adjusted accordingly.

additive delay model. Apart from this, delay-based PUFs that are not based on the Arbiter PUF can also have an additive delay model defined for them. We can find obvious examples of this in the BR PUF [141], TBR PUF [141], and Current Mirror PUF [200], all of which had mathematical models defined for them in a similar fashion to the Arbiter PUF.

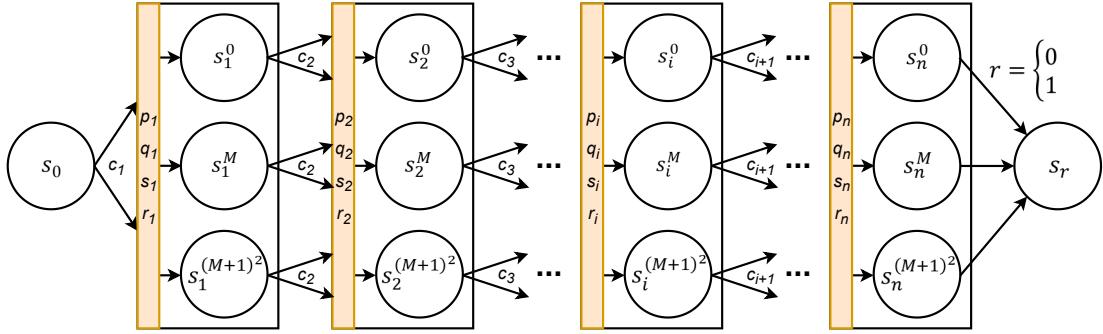

2) *DFSM model*: This approach for modeling the Arbiter PUF from Fig. 6 is taken in [203]. The model begins by following the same approach as the additive delay model, where the total delay at the two outputs of each stage can be described as  $\delta_i^t$  and  $\delta_i^b$ , for the top and bottom paths respectively. These values are the sum of the delays of each path until the  $i$ -th stage, and their difference marks the delay difference  $\delta_i = \delta_i^t - \delta_i^b$  (Fig. 4).

However, the authors realize that the four key wire delays of each stage ( $p_i, q_i, s_i$ , and  $r_i$ ) follow a Gaussian distribution  $N(\mu_i, \sigma_i)$ . Assuming that all stages have the same mean and standard deviation (which is reasonable since they are manufactured together in close proximity), for an  $n$ -bit Arbiter PUF,  $\mu = \mu_1 = \dots = \mu_n$  and  $\sigma = \sigma_1 = \dots = \sigma_n$ . By utilizing this assumption, the distribution of the total delay of all stages must follow the Gaussian distribution  $N(n\mu, \sqrt{n}\sigma)$ . Additionally, we can also consider that the Arbiter at the end of the chain has a limited precision threshold  $\gamma$  for differentiating the final path delays. Therefore, the final output of the Arbiter PUF is given by (9).

$$r = \begin{cases} 1, & \delta_n^t - \delta_n^b > \gamma \\ 0, & \delta_n^t - \delta_n^b < \gamma \\ X, & |\delta_n^t - \delta_n^b| \leq \gamma \end{cases} \quad (9)$$

Notice that there exists a metastable state for the Arbiter if the delay difference is too low. This is simply an unreliable response, and the lower the value of  $\gamma$  is, the more reliable the Arbiter PUF will be. Moreover, due to the limited precision of the Arbiter and the fact that 99.7% of a Gaussian distribution values fall into an interval of  $6\sigma$ , the real values of the delays at the outputs of the stages can be mapped to integer values by  $f : \mathbb{R} \rightarrow \mathbb{Z}$  as shown by (10).

$$f(\delta) = \left\lceil \frac{\delta - n\mu + 3\sigma\sqrt{n}}{\gamma} \right\rceil \quad (10)$$

This mapping means that  $\delta_i \in \{0, M\}$  for all delay values that are in the interval  $[n\mu - 3\sigma\sqrt{n}, n\mu + 3\sigma\sqrt{n}]$  (99.7% of values), and that  $M$  can be expressed by (11).

$$M = \left\lceil \frac{6\sqrt{n}\sigma}{\gamma} \right\rceil \quad (11)$$

With the previous observations it is possible to construct a DFSM representing an Arbiter PUF. Note that it was always possible to represent an Arbiter PUF as a DFSM by simply starting from an initial state, and then for each state transition the DFSM grows by twice as many states as it already has. Basically, this representation considers each state as all the possible combinations of previous stages, where at each stage the paths are either straight or crossed, and the resulting delay difference  $\delta_i$  is either lower or higher than 0. However, such a DFSM grow exponentially with  $n$  (number of stages). That is why the DFSM constructed in [203] is an improvement,

Fig. 7. Polynomial size DFSM representation of a  $n$ -bit Arbiter PUF.

as it is of polynomial size in  $n$ , as shown in Fig 7. This DFSM has an initial and terminal state, and for each stage of the Arbiter PUF a total of  $(M + 1)^2 + 1$  states. Each of these states represents a unique differentiable pair of  $\delta_i^t$  and  $\delta_i^b$ , i.e., the granularity of  $\delta_i$  that the Arbiter can differentiate due to its precision of  $\gamma$ . Note that each state has two possible transitions depending on the challenge bit  $c_i$  for that stage, and the state to which this transition connects is determined by the delay parameters  $p_i$ ,  $q_i$ ,  $r_i$ , and  $s_i$ . In other words, each Arbiter PUF instance transitions are determined by the random manufacturing variations.

To model an Arbiter PUF with the polynomial DFSM representation, one would have to learn the state transitions. Such a problem is solvable with different algorithms and as such is a valid Arbiter PUF model. Additionally, it is possible to extend the DFSM to other PUF architectures, although it may come at the cost of a significant increase in complexity. On the other hand, it is also possible to reduce the number of states per stage further for easier learnability, such as in [199], at the cost of a lower fidelity towards the real PUF model.

3) *White-box PUF probing*: In this literature review, a few works that assume unrestricted access to certain PUF parameters can be found [33], [190]. Generally, this approach is only interesting for developing functional PUF clones for applications, not as an attack method. There exist obvious and simple examples of white-box modeling (not seen in any papers in this review), namely, exhaustive modeling. For example, we can model an SRAM PUF by recording all output bits with privileged access during manufacturing. Another example would be to probe the delays of each connection on an Arbiter PUF.

4) *Physical modification and emulation of PUFs*: There are two alternatives when physically modeling a PUF. The first is to physically modify a PUF to manipulate its output values in a predictable manner. An excellent work for such a technique was presented in [42], where the authors managed to modify the outputs of an SRAM PUF via a process called Bias Temperature Instability (BTI) aging. Using this technique, any SRAM PUF could be configured to have a specific set of CRPs, which means that a supplier could maliciously control, e.g., a cryptographic key embedded in a device. Alternatively, a supplier could also create legitimate clones of SRAM PUFs for symmetric cryptography purposes. The second option for physical modeling of PUFs is emulation [208]. This method is

similar to parametric modeling, but involves modeling the PUF characteristics at a physical level, instead of mathematical.

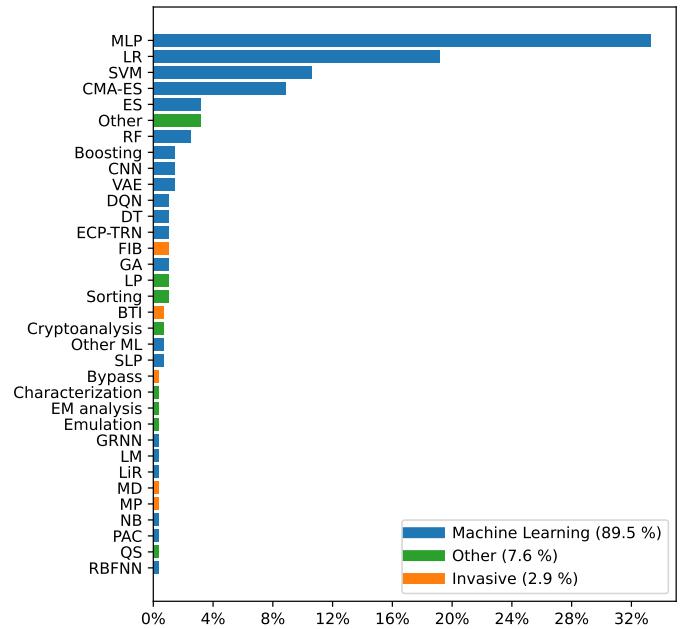

### B. PUF modeling techniques