# **Aalborg Universitet**

# Schedulability Analysis of Distributed Multi-core Avionics Systems with UPPAAL

Han, Pujie; Zhai, Zhengjun; Nielsen, Brian; Nyman, Ulrik; Kristjansen, Martin

Published in: Journal of Aerospace Information Systems

DOI (link to publication from Publisher): 10.2514/1.1010715

Creative Commons License Unspecified

Publication date: 2019

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Han, P., Zhai, Z., Nielsen, B., Nyman, U., & Kristjansen, M. (2019). Schedulability Analysis of Distributed Multicore Avionics Systems with UPPAAL. *Journal of Aerospace Information Systems*, *16*(11). https://doi.org/10.2514/1.I010715

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

## Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: July 04, 2025

# Schedulability Analysis of Distributed Multi-core Avionics Systems with UPPAAL

Pujie Han\* and Zhengjun Zhai<sup>†</sup> Northwestern Polytechnical University, Xi'an, 710072, China

Brian Nielsen<sup>‡</sup>, Ulrik Nyman<sup>§</sup>, and Martin Kristjansen<sup>¶</sup> *Aalborg University, Aalborg, 9220, Denmark*

This paper presents an approach for schedulability analysis of Distributed Integrated Modular Avionics (DIMA) systems that consist of spatially distributed ARINC-653 multi-core modules connected by a unified Avionics Full Duplex Switched Ethernet (AFDX) network. We model a multi-core DIMA system as a set of stopwatch automata in Uppaal to verify its schedulability by model checking. However, direct verification is infeasible due to the large state space. Therefore, we combine global analysis based on Statistical Model Checking (SMC) and compositional analysis based on classical model checking, thereby mitigating the state space explosion problem. Even though the nature of SMC testing cannot prove schedulability, the model of a DIMA system first undergoes quick schedulability falsification using global SMC analysis. Thereafter, we use a compositional approach to check each partition including its communication environment individually. By using assume-guarantee reasoning, we ensure that each real-time task meets the deadline and that communication constraints are also fulfilled globally. The approach is finally applied to the schedulability analysis of a concrete multi-core DIMA system.

### I. Introduction

As the cost of avionics systems rapidly increases in the aviation industry, there is a growing trend towards providing a more generalized airborne computation environment for Commercial Off-The-Shelf (COTS) products. The architecture of Distributed Integrated Modular Avionics (DIMA) [1] is proposed for this purpose. It installs standardized computer modules in spatially distributed locations [2] that are connected by a unified deterministic bus system [3] such as an Avionics Full Duplex Switched Ethernet (AFDX) network [4]. To keep a balance between the performance and the Size, Weight and Power (SWaP) consumption of avionics systems, COTS multi-core processors have been

<sup>\*</sup>Ph.D. Candidate, School of Computer Science and Engineering, West Youyi Road 127.

<sup>&</sup>lt;sup>†</sup>Professor, School of Computer Science and Engineering, West Youyi Road 127.

<sup>&</sup>lt;sup>‡</sup>Associate Professor, Department of Computer Science, Selma Lagerløfs Vej 300.

<sup>§</sup> Associate Professor, Department of Computer Science, Selma Lagerløfs Vej 300.

<sup>¶</sup>Ph.D. Student, Department of Computer Science, Selma Lagerløfs Vej 300.

widely applied to airborne computer modules, where avionics applications run in ARINC-653 [5] partitioned operating systems.

Enabled by the continued improvement of semiconductor technology (Moore's law), the current approach to increasing the processor performance at low cost is mainly through the integration of multiple cores in a single processor. This direction is driven by the so-called power-wall that prevents processors from being clocked at an increased rate, and by the very high complexity of designing processors that continues to improve performance through ever increasing levels of implicit instruction level parallelism.

However, multi-core processors also create new challenges at different levels. Applications must be designed with explicit thread level parallelism, often leading to massively concurrent applications, which again makes it more challenging to ensure correct behavior in terms of functionality, timing, and absence of concurrency bugs like race-conditions and deadlocks. For safety- and time-critical avionics system, this specifically increase the challenge of creating and mapping many application partitions (possibly with non-trivial inter- and intra-partition dependencies) on multiple cores (or even networked processors), and being able to perform the required schedulability analysis to guarantee correct timing. At the operating system level, challenges are providing new effective mechanisms for predictable management, scheduling, synchronization, and partitioning of the underlying processing and memory resources, such that schedulability and worst-case execution time analysis are feasible. At a hardware level, challenges concern creating core-interconnects and memory bus systems to allow sufficiently fast data- and instruction transfer to the multiple cores, and providing memory coherency across them and the different memory types found in multi-core systems. As a further consequence, the development cost of safety critical systems is increased by the need for certifying the safe operation of the system.

Multi-core hardware and distributed applications thus lead to increasingly complex systems whose schedulability has been becoming difficult to validate. This paper addresses this challenge by proposing a new method and tool for analyzing the schedulability of complex avionics systems.

A schedulable DIMA system should fulfil not only the temporal requirements of each real-time task on multiple processor cores but also communication constraints among the distributed nodes. The development of model checking based approaches has currently become an attractive topic for the schedulability analysis of complex real-time systems due to the sufficient expressiveness of formal models. The techniques of classical model checking (MC) describe schedulability as temporal logic properties and verify the properties via state space exploration. There have been works using model-checking to analyze the temporal behavior of individual avionics modules in various formal models such as Coloured Petri Nets (CPN) [6], preemptive Time Petri Nets (pTPN) [7], Linear Hybrid Automata (LHA) [8], Timed Automata (TA) [9], and StopWatch Automata (SWA) [10]. Unfortunately, when being applied to a complete avionics system, they suffer from an inevitable problem of state space explosion, which makes the exact model checking practically infeasible.

Compositional approaches are widely adopted to alleviate the state space explosion problem. Some studies [11–13] exploit the inherent isolation of temporal partitioning by analyzing each partition separately and concluding system properties at a global level, but they ignore the behavior of the underlying network or the interactions among partitions. Thus these methods are not applicable to DIMA environments in which multiple distributed ARINC-653 partitions communicate through a shared network to perform an avionics function together.

Statistical Model Checking (SMC) [14] is also proposed as a promising technique that has the powerful facilities of formal modeling as well as avoids the state space explosion of classical model checking. An SMC engine runs and monitors a number of simulation processes in order to quickly estimate the statistical results of the satisfaction or violation of certain properties. However, the SMC cannot provide any guarantee of schedulability but quick falsification owing to its nature of statistical testing. Therefore, it is reasonable to apply both classical and statistical model checking to the schedulability analysis of avionics systems.

In this paper, we present an approach to schedulability analysis of multi-core DIMA systems that are modeled as a set of StopWatch Automata (SWA) in UPPAAL. The approach combines compositional and global analysis by classical and statistical model checking. The paper is a combination and extension of the two workshop papers [15] and [16]. The rest of the paper is organized as follows. Section II presents related work and contributions. Section III describes the structure of DIMA systems, providing the modeling requirements for a DIMA system. The UPPAAL models and their schedulability analysis are presented in section IV. In section V we detail the compositional analysis approach. In section VI we present a case study and its experimental results, and section VIII discusses those same results along with their applicability to related schedulability problems. Finally, section VIII concludes the paper.

## **II. Related Work and Contributions**

The structure of DIMA systems has been fully discussed in [1–3, 17]. The current research into the schedulability of DIMA systems focuses on two of their major constituent parts: ARINC-653 modules and the underlying AFDX network.

A multitude of analytical methods [18–23] can be used to analyze the schedulability of ARINC-653 modules, which belong to two-level hierarchical scheduling systems. However, the worst-case assumptions in these analytical methods are more pessimistic than real situations. By contrast, the model checking based approaches are more expressive and can be used to perform exact schedulability analyses on the basis of various formal models such as Coloured Petri Nets (CPN) [6], preemptive Time Petri Nets (pTPN) [7], Linear Hybrid Automata (LHA) [8], Timed Automata (TA) [9], and Stopwatch Automata [10].

The authors of [6] construct a CPN model to describe real-time task scheduling in a generic avionics mission computer, deriving task response times from the model to determine the feasibility of five different scheduling protocols. Nevertheless, the modeling method does not cover any ARINC-653 features and is only applicable to

federated avionics. In [24], the theory of pTPN is introduced to support exact schedulability analysis of two-level hierarchical scheduling systems. This approach is extended in [11] with a concept of required interface that models the environment of each application to enable compositional analysis of hierarchical scheduling systems encompassing inter-application communications between periodic tasks. However, the communication latency of the underlying bus system and the features of ARINC-653 ports are not taken into account. The authors of [12] employ the formalism of LHA to model a hierarchical scheduling system where there is no communication among tasks. They adopt a dynamic server algorithm, separating each server from the rest of the system, and thereby enabling component-based scheduling analysis. This method is subsequently applied to a multi-core global scheduling system and extended with a weak simulation in [25] to reduce the state space of complex models. The approaches of [26, 27] use TA to describe a hierarchical scheduling system, while both of them are limited to periodic tasks isolated from each other. The formal modeling of pTPN and the verification of SWA are combined in [28], which allows for inter-task communication but no temporal partitioning mechanism. The authors of [13] introduce their compositional frameworks using SWA for analyzing the schedulability of hierarchical scheduling systems. The modeling is covering concrete task actions and intra-partition synchronization and therefore allows for more features of avionics systems, but the compositional analysis does not support the communication among partitions. They also apply a similar modeling method to the evaluation of multi-core platforms in [29, 30]. Obviously, all of the aforementioned approaches lack the capability to model and analyze network communication in DIMA systems from a global viewpoint.

Up to now, several approaches have been introduced for calculating end-to-end delays in an AFDX network, including a simulation approach [31, 32], response time analysis [33, 34], network calculus [35, 36], trajectory approach [37], forward end-to-end delays analysis [38, 39] and model checking approach [40–42]. Although the model checking approach can obtain more exact results than the rest that compute the upper bounds of worst-case end-to-end delays, it is confronted with the state space explosion problem for realistic networks [41].

The objective of this paper is to help apply model checking to the schedulability analysis of a multi-core DIMA system. From a global perspective of DIMA systems, we employ the combination of SMC and a compositional approach to cope with the state space explosion problem of classical model checking. The main contributions of this paper are summarized as follows:

- Comprehensive Modeling of multi-core DIMA systems that covers the features of two-level ARINC-653 compliant

multi-core schedulers, periodic/sporadic tasks, intra-partition synchronization, and inter-partition communications through an AFDX network.

- A method for global analysis using statistical model checking allows users to quickly falsify non-schedulable configurations by SMC hypothesis testing, which can handle a complete system model and avoid an exhaustive exploration of the state space.

- A method for compositional analysis using classical model checking verifies the model of each ARINC-653

partition including its environment individually and then assembles the local results together to derive conclusions about the schedulability of an entire system. A compositional approach performs assume-guarantee reasoning [43] to reduce the complexity of symbolic model-checking.

- An abstraction relation, timed selection simulation relation, which allows users to create a set of abstract models

that collectively describe the external behavior of a concrete model, thereby simplifying the abstraction in

assume-guarantee reasoning.

- A notion of *message interfaces* that decouples the communication dependencies between partitions. By composing any partition with its related message interfaces and verifying safety properties of the composition, we can conclude that these properties are still preserved at the global level.

- · Application of the approach to an avionics case study, thus validating the feasibility of the approach.

This paper is a combination and extension of the two workshop papers [15] and [16]. These previous papers each focused on one aspect of the approach, namely the models [15] and compositionality [16].

On top of combining the two papers this journal paper also adds several completely new elements and joins it all to a coherent approach:

- Multi-core aspects

- Section III with added description of the ARINC-653 multi-core modes

- Experiments using a symmetric multi-processor scheduler

- Detailed description of all UPPAAL models

- New AFDX models that are able to describe a network topology, giving a more precise latency analysis for the communication between nodes in the network

# **III. Avionics System Description**

This section presents the structure and the main parts of a DIMA system. Thereafter, the two types of ARINC-653 multi-core systems are presented and described. Based on the structure of such systems and the multi-core aspects, formal terms are defined in order to use the properties of a DIMA system in a schedulability analysis.

# A. Distributed Integrated Modular Avionics System

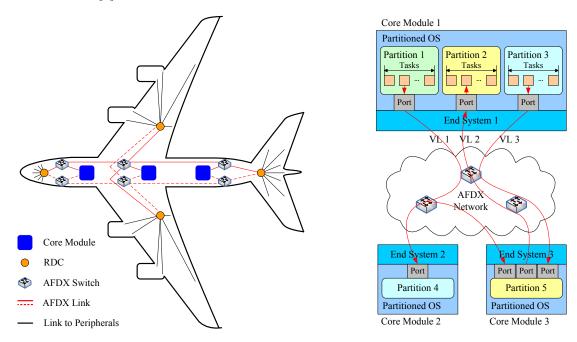

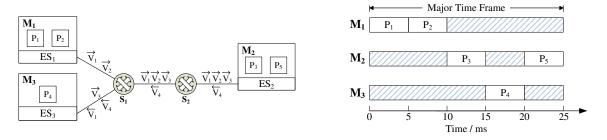

In DIMA systems, a unified AFDX network connects standardized computer devices and thousands of peripherals (sensors and actuators), which are linked by Remote Data Concentrators (RDC) to the AFDX network [3]. Fig. 1 shows a simplified example of a DIMA system, where physically distributed DIMA core modules [5] execute application tasks simultaneously to fulfill avionics functions cooperatively.

In the aviation industry, ARINC-653 series standards define a general-purpose APEX (APplication/EXecutive) interface between the operating system and the application software, providing a space and time partitioning mechanism

for avionics applications [5]. Thus the tasks resident on each DIMA core module run in an ARINC-653 partitioned operating system which realizes a two-level scheduling mechanism and achieves temporal isolation between ARINC-653 partitions. In such a scheduling system, partitions are scheduled by a Time Division Multiplexing (TDM) global scheduler and each partition also has its local scheduling policy based on preemptive Fixed Priority (FP) to manage the internal tasks [5].

Fig. 1 An example of a DIMA system

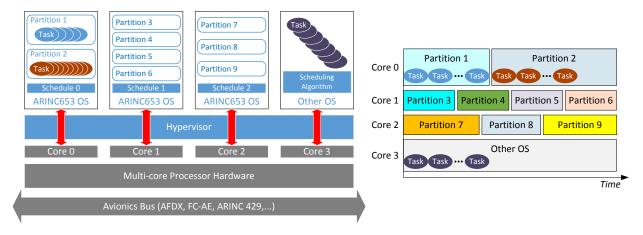

Fig. 2 A DIMA core system

The distributed nature of DIMA systems lead to frequent inter-partition communication not only within core modules but also between them through the underlying AFDX network. According to the ARINC-653 standard [5], all inter-partition communication is conducted using a message passing system. Messages originating from partitions are only allowed to be communicated via an ARINC-653 port and transmitted through a logical channel from a single source partition to one or more destination partitions. Each port and its logical channel are associated with one of the modes of transfer: sampling mode or queuing mode. A sampling port can accommodate at most a single message that remains in the buffer until it is either transmitted by the channel from a source port or overwritten by a new message in a source or destination port. Moreover, a refresh period is defined as an attribute of each sampling port. This attribute provides a correct arrival rate to determine the validity of received messages, regardless of the rate of receiving requests from application tasks. In contrast, a queuing port, which only supports unicast connections, is allowed to buffer multiple messages in a message queue with a fixed capacity. However, the operating system is not responsible for handling overflow after the message queue is full. We consider three schedulability properties that a system has to satisfy: task deadlines, refresh periods of sampling ports and non-overflow of queuing ports. These properties are detailed in Section IV.B.

In this paper, we consider the DIMA core system as shown in Fig. 2 where an AFDX network connects all the core modules through their End Systems (ES), each of which provides a hardware implementation of the AFDX protocol stack [4]. ARINC-664 part 7 [4] prescribes that an AFDX ES should provide ARINC-653 port services for the operating system. A message sent from a source port is expanded by the UDP and IP header at the UDP/IP layer and then forwarded to a Virtual Link (VL), which defines a logical connection from one source ES to one or more destination ESs. Unlike the Internet, routing in AFDX network is based on VLs instead of IP address. What is more, ESs provide each VL with a dedicated maximum bandwidth to ensure an upper bound on end-to-end delay. The message flows belonging to the same VL share the bandwidth. In transmitting between ESs, a scheduler regulates and multiplexes the flows from different VLs. This single multiplex flow is sent across two independent switched networks and both of them will arrive at the destination ES(s) under normal operation. The underlying network redundancy is transparent to the upper protocols because of the function of redundancy management in each ES. Throughout this paper, we assume that there is no unmasked fault in our AFDX network.

#### B. Implementation of ARINC-653 Multi-core systems

Although multi-core processors have been widely applied across various application domains, ARINC-653 series standards did not cover the features of multi-core processors until the ARINC-653 Part 1 Supplement 4 (ARINC653P1-4) was published in 2015. The leading software vendors of ARINC-653 compliant systems thus implement multi-core aspects using different strategies. According to the level of parallelism, two types of software architecture are commonly utilized to implement an ARINC-653 compliant system on multi-core platforms: Asymmetrical Multi-Processing (AMP) and Symmetrical Multi-Processing (SMP) [44].

An AMP deployment enables inter-partition parallelism in one processor, where each core is managed by a separate instance of an operating system that provides airborne software application with the ARINC-653 partitioning mechanism [45]. In such a configuration, each partition is executed on a single core in parallel with the partitions running on the other cores, and thus independent partition schedules are assigned to different cores [46]. Since the operation of each partition is similar to that on a single core processor, the AMP architecture especially suits the compatibility requirements for legacy applications.

However, ARINC653P1-4 did not define inter-partition parallelism within an operating system [5]. When applying an AMP architecture, it requires more effort from the platform providers to handle the contention and co-operation of individual operating systems on different cores. As shown in Fig. 3, the practical AMP implementation, such as the VxWorks 653 Multi-core Edition developed by Wind River [47], introduce a hypervisor layer running across all the cores, thereby ensuring robust partitioning on the operating system level and concerted access to shared resources of the processor's multiple cores.

By contrast, an SMP deployment realizes task parallelism inside one partition that is activated on all cores

Fig. 3 AMP architecture and its multi-core scheduling examples

Fig. 4 SMP architecture and its multi-core scheduling examples

synchronously, which means the tasks belonging to a common partition can run in parallel on different cores. In the SMP mode, as depicted in Fig. 4, all the cores are managed by a single instance of an operating system where only one partition schedule is required. The SMP configuration applies to a substantial number of emerging airborne software applications, such as radar, sonar and image processing, due to their inherent parallelism [48]. Nevertheless, the versions earlier than ARINC653P1-4 did not consider such use of multi-core processors. The legacy applications developed under these widely-used versions may depend on sequential execution and fail inside a parallel partition. By adopting an SMP configuration, function suppliers can benefit from the use of multi-core processors to improve the performance of specific airborne software applications, but have to put more effort into parallel programming schedulability analysis.

The SMP architecture is compatible with ARINC653P1-4 in the scope of an operating system. There are two attributes that control the mappings between partitions or tasks and processor cores in ARINC653P1-4. The fixed attribute *Assigned Processor Core(s)* assigns a particular set of processor cores to a partition. Each task is further associated with an attribute *Processor Core Affinity*, which specifies the processor core or cores the task can run on. A

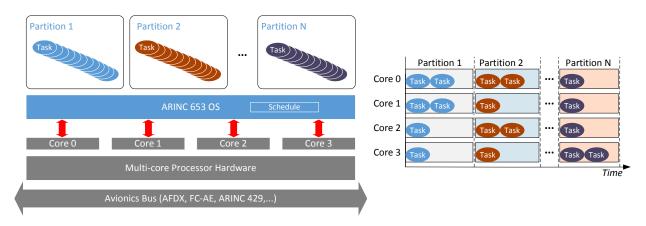

Fig. 5 Layered structure of DIMA core systems

task can only be assigned an affinity for one of the processor cores allocated to the partition to which the task belongs. Therefore, each processor core assigned to the partition will execute a different fixed set of tasks simultaneously [5].

## C. Layered Model of an Avionics System

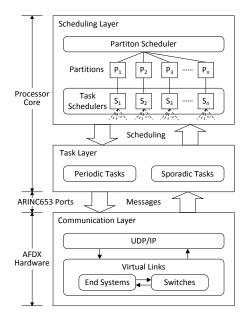

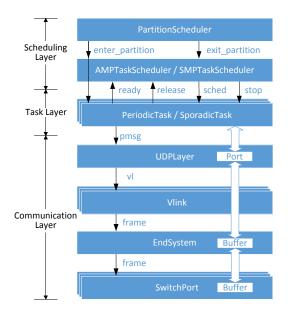

Fig. 5 shows a three-layer model of a DIMA core systems consisting of scheduling layer, task layer, and communication layer. The constituent elements are detailed as follows.

The *scheduling layer* comprises the hierarchical scheduling facilities of an ARINC-653 module. The multi-core architecture AMP and SMP differ in the constitution of this scheduling layer.

• In an AMP configuration, each processor core has an independent TDM partition scheduler  $\langle Core, MF, Sch \rangle$ , where Core is an identifier of the processor core, MF is a major time frame and Sch is a partition schedule. Since partitions are scheduled on a fixed cyclic basis, the partition-scheduling behavior is periodically repeated every MF [5]. Sch contains a set of partition windows, i.e. time slots, each of which is defined as  $\langle P, Off, Dur \rangle$  where P identifies a partition, Off denotes the offset from the start of MF and Dur is the expected duration / budget. Partitions are only activated within their corresponding partition windows [5].

The SMP configuration equips all the processor cores of a module with a common TDM partition scheduler  $\langle MF, Sch, Assi \rangle$  where MF and Sch have the same definitions as those of the AMP partition scheduler. In addition, the set Assi indicates the processor core(s) assigned to partitions. Its elements are defined as  $\langle P, Cores \rangle$  where P identifies a partition and Cores is a set of processor cores.

• The AMP configuration assigns each partition a preemptive FP *task scheduler*, which always selects the task with the highest priority in the ready state within the partition to run.

The SMP task scheduler uses a partitioned preemptive FP scheduling policy [49]. When a partition is assigned multiple processor cores, a set of tasks in the ready state may be selected based on both priority and core affinity to run concurrently on the assigned processor cores [5].

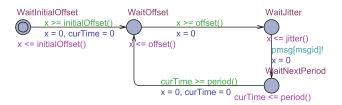

All the application tasks executing avionics functions constitute the *task layer*. We consider a task as the smallest scheduling unit, each of which can be executed concurrently with other tasks in the same partition. A task is indicated by the tuple  $\langle I, \mathcal{P}_{min}, \mathcal{P}_{max}, O, \mathcal{J}, \mathcal{D}, C, \mathcal{R}, \mathcal{L} \rangle$  where I is initial offset determining the first release point of the task,  $\mathcal{P}_{min}$  and  $\mathcal{P}_{max}$  are the minimum period and the maximum period respectively, O is offset,  $\mathcal{J}$  is jitter,  $\mathcal{D} \leq \mathcal{P}_{min}$  is the deadline, C denotes processor core affinity,  $\mathcal{R}$  denotes task priority, and  $\mathcal{L}$  is a sequential list of abstract instructions. In the task model, jobs of each task are scheduled repeatedly and a task releases the kth job ( $k \in \mathbb{N}$ ) in the time interval  $[I + k\mathcal{P}_{min} + O, I + k\mathcal{P}_{max} + O + \mathcal{J}]$ . Let  $t_k$  be the time when the kth job is released. For any task in a partition  $P_i$ , we define the following two task types:

- A periodic task has the kth release time  $t_k \in [I + kP + O, I + kP + O + \mathcal{J}]$  where  $P = P_{min} = P_{max} < +\infty$  is a fixed period.

- A *sporadic task* characterized by a minimum separation  $S = \mathcal{P}_{min} \mathcal{J}$  between consecutive jobs releases its (k+1)th job at  $t_{k+1} \in [t_k + S, +\infty)$ , and its first release time  $t_0$  is in the interval  $[I + O, +\infty)$ .

An element of the sequential list  $\mathcal{L}$  represents the operation of an abstract instruction  $\langle Cmd, Res, T_{BCET}, T_{WCET} \rangle$ . Cmd is the type of abstract instructions belonging to the command set  $\{Compute, Lock, Unlock, Delay, Send, Receive, End\}$ . Res is an identifier encoding one of the resources such as CPU, mutual exclusion locks, messages, and ports.  $T_{BCET}$  and  $T_{WCET}$  are the execution time in the best and the worst case, respectively. In the command set, Compute represents a general computation step, Lock and Unlock handle mutual exclusion locks, Delay allows the current task to stop running for a certain time, Send and Receive are utilized in inter-partition communications, and End is the symbol of job termination. Since the direct application of mutual exclusion locks can cause an unpredictable duration of priority inversion, we adopt the priority ceiling protocol [50] to deal with intra-partition synchronization.

The *communication layer* interacts with the task layer through ARINC-653 ports and provides the services of inter-partition communication between different modules. We focus on the transfer latency in the communication layer. According to the structure of the AFDX protocol stack, the communication layer is further divided into an UDP/IP layer and virtual links.

- The latency of delivery through the *UDP/IP layer* in each ES is commonly implementation dependent but can be measured and bounded on an interval [ $Tu_{min}$ ,  $Tu_{max}$ ], which indicates the delay in forwarding a message from an ARINC-653 port (Transmission) or an Ethernet frame from a VL (Reception) to its destination buffer.

- A *virtual link* is characterized as the tuple  $\langle L_{max}, BAG, N, Conn \rangle$  where  $L_{max}$  is the maximum frame length and BAG is the bandwidth allocation gap, i.e. the minimum interval between the first bits of two consecutive frames [4]. Thus, the maximum available bandwidth of the VL is  $L_{max}/BAG$ . N denotes the speed of the

physical link. Given a frame length L in bytes, the frame delay is  $(8 \times L)/N$ , i.e. the time taken to deliver the frame to a physical link [4]. Let H and W be the set of ESs and switches respectively.  $Conn \subseteq (H \cup W) \times (H \cup W)$  defines the set of VL's physical links, representing a logical connection from one source ES to one or more destination ESs. The ESs in a VL are connected by switches. In order to model the latency through a VL, we consider the accumulated value of the technological latency (independent of traffic load) and configuration latency (depending on configuration and traffic load) [4] along the logical path.

Additionally, two *message patterns* are provided for inter-partition messages between the task and communication layer. Since message-sending actions and the release of their source tasks have similar temporal features, we define two patterns of periodic and sporadic messages that are generated by periodic and sporadic tasks respectively. For any message type  $msg_k$ , we associate a time stamp  $t_l^k$ ,  $l \in \mathbb{N}$ , which is the accumulated time since the initial instant, with each message-sending action. Time stamps  $t_l^k$  identify two message patterns:

- periodic messages with the time stamps  $t_l^k \in [I^k + l\mathcal{P}^k + O^k, I^k + l\mathcal{P}^k + O^k + \mathcal{J}^k]$ , and

- sporadic messages having the (l+1)th time stamp  $t_{l+1}^k \in [t_l^k + \mathcal{P}^k \mathcal{J}^k, +\infty)$  after its first time stamp  $t_0^k \in [\mathcal{I}^k + \mathcal{O}^k, +\infty)$ ,

where  $I^k$  is initial offset,  $\mathcal{P}^k$  is period,  $O^k$  is offset, and  $\mathcal{J}^k$  is jitter. By instantiating the parameters of a pattern, one can describe the message-sending behavior of a specific task.

The above coupled elements represent the parallel components of a DIMA core system, which can be modeled as a network of SWA. In the following sections, we use  $\Omega$  to denote the set of SWA in system models.

# IV. Modeling Framework

This sections is divided into four parts. The necessary preliminaries for this paper are presented followed by an overview of the modelling framework. The framework presents what kind of TA templates are needed in order to represent the behaviour of a DIMA system. Thereafter, the model-based analysis method is presented. Here it is described how classical MC and SMC are combined in order to mitigate state space explosion. Lastly, the TA templates in UPPAAL are presented in detail.

## A. Preliminaries

We present formal definitions including SWA with an input/output extension and its semantic object Timed I/O Transition Systems (TIOTSs) [51].

Suppose that C is a finite set of clocks and V is a finite set of integer variables. A valuation u(x) with  $x \in C \cup V$  denotes a mapping from C to  $\mathbf{R}_{\geq 0}$  and from V to  $\mathbf{N}$ . Let LC(C,V) be the set of linear constraints. A guard  $g \in LC(C,V)$  is a linear constraint which is defined as a finite conjunction of atomic formulae in the form of  $c \sim n$ ,  $c - c' \sim n$  or  $v \sim n$  with  $c, c' \in C$ ,  $v \in V$ ,  $n \in \mathbf{N}$ , and  $v \in \{<, \leq, =, \geq, >\}$ . Given any valuation u, we change the values of clocks and

integer variables using an *update* operation  $r(u) \in 2^R$  in the form of c = 0 or v = n where  $c \in C$ ,  $v \in V$  and  $n \in \mathbb{N}$ , and R is the universal set of update operations. In addition, we define an *action* set  $\Sigma$  used for synchronization, an internal action  $\tau \notin \Sigma$ , and their universal set  $\Sigma^{\tau} = \Sigma \cup \{\tau\}$ .

**Definition 1** (Stopwatch Automaton [10]) A stopwatch automaton is a tuple  $\langle Loc, l_0, C, V, E, \Sigma, Inv, drv \rangle$  where Loc is a finite set of locations,  $l_0 \in Loc$  is the initial location, C is a finite set of clocks, V is a finite set of integer variables,  $E \subseteq Loc \times LC(C, V) \times \Sigma^{\tau} \times 2^{R} \times Loc$  is a set of edges,  $\Sigma = I \oplus O, I \cap O = \emptyset$  is a finite set of actions divided into inputs(I) and outputs(O), Inv is a mapping  $Loc \to LC(C, V)$ , and drv is a mapping  $Loc \times C \to \{0, 1\}$ .

From a syntactic viewpoint, SWA belongs to the class of TA extended with drv, which can prevent part of the clocks called stopwatches from changing in specified locations semantically. We now shift the focus to the semantic object TIOTS of SWA.

In a TIOTS, there are two types of transitions: delay and action transitions. We use the set  $D = \{\epsilon(d) | d \in \mathbf{R}_{\geq 0}\}$  to denote the delay, and refer to the 0-delay  $\epsilon(0)$  as  $\mathbf{0}$ .

**Definition 2 (Timed I/O Transition System)** A timed I/O transition system is a tuple  $\mathcal{T} = \langle S, s_0, \Sigma, \rightarrow \rangle$  where S is an infinite set of states,  $s_0$  is the initial state,  $\Sigma = I \oplus O, I \cap O = \emptyset$  is a finite set of actions divided into inputs(I) and outputs(O), and  $\rightarrow \subseteq S \times \Sigma^{\tau} \cup D \times S$  is a transition relation.  $s \xrightarrow{a} s'$  represents  $(s, a, s') \in \rightarrow$ , which has the properties of time determinism, time reflexivity, and time additivity [51].

For any SWA, a state is defined as a pair  $\langle l, u \rangle$  where l is a location and u is a valuation over clocks and integer variables. On the basis of TIOTSs, the operational semantics of SWA is defined as follows.

**Definition 3 (Semantics of SWA)** The operational semantics of a stopwatch automaton  $A = \langle Loc, l_0, C, V, E, \Sigma, Inv, drv \rangle$  is a timed I/O transition system  $\mathcal{T}^A = \langle S, s_0, \Sigma, \rightarrow \rangle$  where S is the set of states of A,  $s_0 = \langle l_0, u_0 \rangle$  is the initial state of A,  $\Sigma$  is the same set of actions as A, and  $\rightarrow$  is the transition relation defined by

- $\bullet \ \langle l,u\rangle \xrightarrow{a} \langle l',u'\rangle \ iff \ \exists \langle l,g,a,r,l'\rangle \in E \ \ (u\models g \ \land \ u'=r(u) \ \land \ u'\models Inv(l'))$

- $\bullet \ \langle l,u \rangle \xrightarrow{\epsilon(d)} \langle l',u' \rangle \ iff \ l = l' \land (\forall v \in V \ u'(v) = u(v)) \land \ (\forall c \in C \ (drv(l,c) = 0 \Rightarrow u'(c) = u(c))) \land \ (\forall c \in C \ (drv(l,c) = 1 \Rightarrow u'(c) = u(c) + d)) \land \ u' \models Inv(l').$

For any transition  $s \xrightarrow{a} s'$ , two symbols a? and a! denote the action a belonging to input I and output O respectively. Given  $a \in \Sigma$ ,  $s \xrightarrow{a}$  iff  $\exists s' \in S$ , s.t.  $s \xrightarrow{a} s'$ .  $\xrightarrow{\tau} {}^*$  or  $\Longrightarrow$  denotes the reflexive and transitive closure of  $\xrightarrow{\tau}$ .  $s \xrightarrow{\epsilon(d)} s'$  iff  $s \xrightarrow{\epsilon(d)} s'$ , or  $\exists s_1, s_2, \ldots, s_n \in S$ , s.t.  $s \xrightarrow{\alpha_0} s_1 \xrightarrow{\alpha_1} s_2 \xrightarrow{\alpha_2} \cdots \xrightarrow{\alpha_{n-1}} s_n \xrightarrow{\alpha_n} s'$  and  $\forall i \in \{0, \ldots, n\}$ , s.t.  $\alpha_i = \tau$  or  $\alpha_i \in D$  and  $d = \sum \{d_i | \alpha_i = \epsilon(d_i) \}$ .

The definition of parallel composition  $\parallel$  of TIOTSs is similar to that in [51]. Given two TIOTSs  $\mathcal{T}_i = \langle S_i, s_{i,0}, \Sigma_i, \rightarrow_i \rangle$ ,  $i \in \{1, 2\}$ , they are *compatible* iff they satisfy the following conditions:

Fig. 6 Uppaal modeling framework

- (Unique output)  $O_1 \cap O_2 = \emptyset$ .

- (Nonblocking input)  $\forall s \in S_i \ \forall a \in I_i \ s \xrightarrow{a}$ .

Note that the nonblocking input actions are realized as broadcast channels in UPPAAL.

**Definition 4 (Parallel Composition)** Suppose two timed I/O transition systems  $\mathcal{T}_1 = \langle S_1, s_{1,0}, \Sigma_1, \rightarrow_1 \rangle$  and  $\mathcal{T}_2 = \langle S_2, s_{2,0}, \Sigma_2, \rightarrow_2 \rangle$  are compatible. The parallel composition  $\mathcal{T}_1 || \mathcal{T}_2$  is the timed I/O transition system  $\langle S, s_0, \Sigma, \rightarrow \rangle$  where  $S = S_1 \times S_2$ ,  $s_0 = \langle s_{1,0}, s_{2,0} \rangle$ ,  $\Sigma = I_{1||2} \oplus O_{1||2}$ ,  $I_{1||2} = (I_1 \setminus O_2) \cup (I_2 \setminus O_1)$ ,  $O_{1||2} = O_1 \cup O_2$ , and  $\rightarrow$  is the largest relation generated by the following rules:

• INDEP-L:

$$\frac{s_1 \xrightarrow{a} s_1' \quad a \in \{\tau\} \cup \Sigma_1 \setminus \Sigma_2}{\langle s_1, s_2 \rangle \xrightarrow{a} \langle s_1', s_2 \rangle} \qquad \text{INDEP-R:} \quad \frac{s_2 \xrightarrow{a} s_2' \quad a \in \{\tau\} \cup \Sigma_2 \setminus \Sigma_1}{\langle s_1, s_2 \rangle \xrightarrow{a} \langle s_1, s_2' \rangle}$$

• DELAY:

$$\frac{s_1 \xrightarrow{\epsilon(d)} s_1' \quad s_2 \xrightarrow{\epsilon(d)} s_2' \quad d \in \mathbf{R}_{\geq 0}}{\langle s_1, s_2 \rangle \xrightarrow{\epsilon(d)} \langle s_1', s_2' \rangle}$$

• SYNC-IN:

$$\frac{s_1 \xrightarrow{a} s_1' \quad s_2 \xrightarrow{a} s_2' \quad a \in I_{1||2}}{\langle s_1, s_2 \rangle \xrightarrow{a} \langle s_1', s_2' \rangle}$$

• SYNC-IO:

$$\frac{s_1 \xrightarrow{a} s_1' \quad s_2 \xrightarrow{a} s_2' \quad a \in (I_1 \cap O_2) \cup (O_1 \cap I_2)}{\langle s_1, s_2 \rangle \xrightarrow{a} \langle s_1', s_2' \rangle}$$

For any SWA  $A_1, A_2 \in \Omega$ , we define the composite model  $A = A_1 \| A_2$  iff their TIOTSs satisfy  $\mathcal{T}^A = \mathcal{T}^{A_1} || \mathcal{T}^{A_2}$ .

# B. An Overview of the Modeling Framework

The modeling framework is organized as a set of UPPAAL templates with a layered structure. Fig. 6 shows an overview of these templates together with the channels between them.

The scheduling layer consists of three TA templates each responsible for a different scheduling concept: a PartitionScheduler and the two task schedulers AMPTaskScheduler and SMPTaskScheduler. PartitionScheduler provides the service of TDM scheduling for partitions. AMPTaskScheduler and SMPTaskScheduler implement the task scheduling of a particular partition in AMP and SMP multi-core configuration, respectively. The model of a task scheduler allocates processor time to the task layer only when the partition is active. Hence the model of PartitionScheduler sends notification on the channels enter\_partition and exit\_partition to task schedulers when entering and leaving its partition, respectively.

The task layer contains a set of task models which are instantiated from two SWA templates PeriodicTask and SporadicTask. A task model describes an execution unit of airborne software. Since the tasks belonging to a partition are scheduled by its task scheduler, we define four channels ready, release, sched and stop as a set of scheduling commands to communicate between task templates and TaskScheduler. Moreover, the priority ceiling protocol is implemented by mutexes in task models to deal with intra-partition synchronization.

The communication layer comprises four TA templates: UDPLayer, VLink, EndSystem and SwitchPort in accordance with the structure of AFDX protocol stack. They jointly calculate the end-to-end delay of inter-partition communication through an AFDX network. When sending a message to an ARINC-653 port, the source task notifies the model of UDPLayer via a channel pmsg. UDPLayer transfers messages from the task layer to their corresponding VLs. In the link layer, two templates VLink and EndSystem model the latency of delivery through a transmitting ES. VLink realizes a traffic shaping function and shapes the flow of a VL to send no more than one frame in each interval of BAG. The EndSystem multiplexes the regulated flows coming from different VLs within a common end system. The channel vl synchronizes the execution of UDPLayer and VLink. Along the logical path of a VL, SwitchPort calculates the latency of queuing and forwarding frames at an output port of switches. The channel frame notifies the destination end system or switch port of the arrival of a frame. Additionally, two types of shared variables *Port* and *Buffer* model the counters of ARINC-653 ports and the queues at switches' ports, respectively.

In this framework, we verify the three following schedulability properties of DIMA systems:

- All the tasks meet their deadlines in each partition.

- The refresh period of any sampling port is guaranteed.

- The overflow from any queuing ports is avoided.

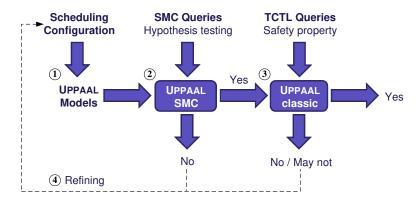

#### C. Model-based Analysis Method

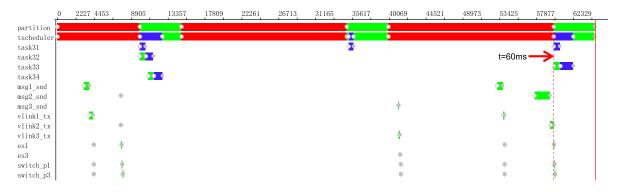

On the basis of the <del>above</del> models described in the next section, we present the procedure for our schedulability analysis, which combines symbolic and statistical model checking. Fig. 7 shows the four steps in the procedure:

- 1) Scheduling configuration is encoded into the UPPAAL model as constant structure arrays.

- 2) We perform hypothesis testing of SMC for the model to falsify non-schedulable configuration rapidly.

Fig. 7 Procedure for schedulability analysis

- 3) If the model goes through the SMC test, its schedulability should be verified by symbolic model checking.

- 4) We refine the configuration that fails in steps 2) or 3) and restart with the new configuration in step 1).

When we apply symbolic model checking to the analysis of a DIMA system, the schedulability constraints are expressed and verified as a safety property of SWA models. We add a set of *error locations* and a boolean variable error with the initial value False to Uppaal templates for this purpose. Once the schedulability is violated, the related model will transfer to one of the error locations and assign the value True to error immediately. Thus, the schedulability is replaced with this safety property  $\varphi$ :

$$A[]$$

not error,  $(1)$

which belongs to a simplified subset of TCTL (Timed Computation Tree Logic) [14] used in UPPAAL.

According to the size of state space, we choose either a global or compositional analysis. The system models with small size can be handled by the *global analysis* where all the constituent elements of a complete system are instantiated and checked directly. Nevertheless, most concrete systems have larger state space, thereby making the global analysis infeasible. To reduce the state space in this case, we perform a *compositional analysis* which check each partition including its environment individually. A set of message interface automata is built to model the environment for a partition.

The schedulability can be obtained from the satisfaction of  $\varphi$ , i.e. the result "Yes" from Uppaal Classic in Fig. 7. However, since the symbolic model checking of Uppaal for SWA introduces a slight over-approximation [10], we cannot conclude non-schedulability from the other results "No" or "May not" with certainty. Therefore, we derive non-schedulability from SMC testing rather than from the verification of  $\varphi$ .

Considering the scalability of SMC, we only use a global analysis in UPPAAL SMC. The schedulability of a complete

Fig. 8 PartitionScheduler model

avionics system is described as following queries of hypothesis testing:

$$Pr[<= M] (<> error) <= \theta, \tag{2}$$

where M is the time bound on the simulations and  $\theta$  is a very low probability. Since UPPAAL SMC approximates the answer using simulation-based tests, we can falsify non-schedulable configuration (i.e. the SMC result "No" in Fig. 7) rapidly by finding counter-examples but identify schedulable ones only with high probability  $(1 - \theta)$  (i.e. the SMC result "Yes" in Fig. 7). Hence, the configuration that goes through the SMC tests should be validated by symbolic model checking to ensure the schedulability of the corresponding system.

## **D. UPPAAL Models**

In this section we present the UPPAAL templates used to perform the analysis. A zip file containing all the models can be downloaded from http://people.cs.aau.dk/~ulrik/submissions/091437/models.zip. The section is divided into three parts each representing a layer of the system as in Fig. 6. The parts then go into details of the UPPAAL templates used in that particular layer.

# 1. Scheduling Layer Models

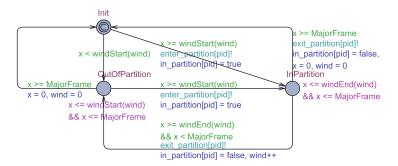

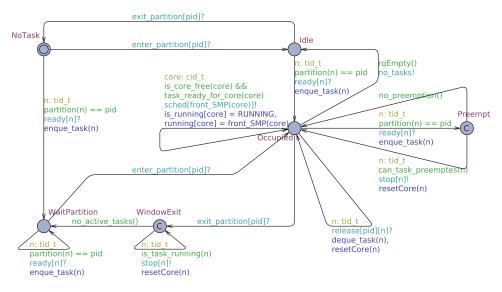

**PartitionScheduler template:** In the scheduling layer, a partition is activated only during its partition windows within every major time frame. We build a TA model PartitionScheduler(See Fig. 8) to provide the description of temporal resources for a particular partition.

The template declarations in UPPAAL support the execution of a PartitionScheduler model. The parameter pid of PartitionScheduler is the identifier of its partition and the partition schedule is recorded in an array of structures PartitionWindows. Each element in the array contains two integer fields offset and duration, where offset is the start time of a partition window and duration denotes the duration of this window. By reading PartitionWindows Table from the declarations, the functions winStart and winEnd with the same integer parameter wind return the

Fig. 9 AMPTaskScheduler model

start time and the end time of the *wind*th partition window, respectively. The integer constant MajorFrame stands for the major time frame, and the clock x measures time within every MajorFrame. In the template, all the guards and invariants use x to control the transitions between locations.

There are three locations in a PartitionScheduler model. The initial location Init represents a conditional control structure that determines the next location at the start of a major time frame. If a partition window and the major time frame start simultaneously, the model will move to the location InPartition. Otherwise, it will enter the location OutOfPartition. Within a major time frame, the model keeps traveling between InPartition and OutOfPartition according to whether or not the current time is in a partition window. For any time from the initial instant, if the PartitionScheduler model of pid enters a new partition window, it will move to the location InPartition, and notify the unique task scheduler model in pid through the output channel enter\_partition. On the contrary, if the PartitionScheduler leaves its current partition window, it will move to the location OutOfPartition, and send notification to the task scheduler model through the output channel exit\_partition.

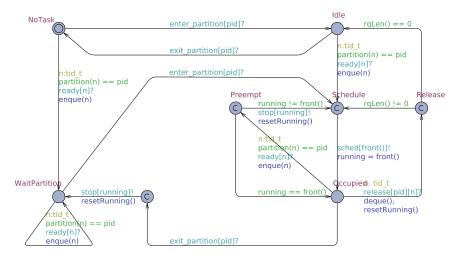

**AMPTaskScheduler template:** For any partition in AMP configuration, there is a preemptive FP task scheduler that runs on a particular processor core while the partition is active. The behavior of the task scheduler is depicted in the TA template AMPTaskScheduler (See Fig. 9). Its partition is identified by the only template parameter pid.

The model of AMPTaskScheduler receives notification from the PartitionScheduler model through two channels enter\_partition and exit\_partition, and uses the channels ready, release, sched and stop as scheduling commands to manage the tasks in the partition pid. If there is a task becoming ready to run or relinquishing the processor, the task model will send its AMPTaskScheduler model a ready or release command, respectively. AMPTaskScheduler maintains a ready queue that keeps all the tasks ready and waiting to run, and always allocates the processor to the first task with the highest priority in the ready queue. If a new task having a higher priority than any tasks in the ready

Table 1 Major locations in task scheduler

| Location      | Partition    | Ready tasks  |              |           |

|---------------|--------------|--------------|--------------|-----------|

| Document      | Outside      | Inside       | 0            | > 0       |

| NoTask        | √            |              | <b>√</b>     |           |

| Idle          |              | $\checkmark$ | $\checkmark$ |           |

| WaitPartition | $\checkmark$ |              |              |           |

| Occupied      |              | $\checkmark$ |              | $\sqrt{}$ |

queue is ready, AMPTaskScheduler will insert the task into the ready queue, interrupt the currently running task via the channel stop and schedule the new selected task via the channel sched. The task identifier is delivered by the offset of channel arrays in the synchronization between AMPTaskScheduler and the task layer.

The ready queue is implemented by the integer array rq which contains a sorted set of task identifiers in priority order. The tasks with identical priority are served in order of readiness. The function rqLen returns the number of the tasks in rq. We use the function enque to insert an identifier of a new task into the ready queue rq and reorder the tasks in the queue. The function deque removes the first element from the ready queue. The first element in rq, i.e. the currently running task, is returned from the function front and recorded in the integer variable running.

According to whether the current time is in the partition windows as well as to the number of the tasks in the ready queue, we create four major locations listed in Table 1. These four locations cover all situations, where the model must be at one of these locations for any time from the initial instant. In contrast, all the other locations of the template are committed and utilized to realize conditional branches or atomic action sequences.

The template AMPTaskScheduler is an event-driven model. It always stays at one of the major locations and reacts to a particular set of input channels, each of which represents a type of external event. The event-handling functionality of those these four major locations is below: listed as follows:

- NoTask reacts to the set of input channels {enter\_partition, ready}. At the location NoTask, the partition pid is not active and the ready queue rq is empty. Entering the partition pid will lead AMPTaskScheduler to the location Idle via the channel enter\_partition. When a new task becomes ready, the scheduler will add the task to the ready queue and move to the location WaitPartition.

- Idle reacts to the set {exit\_partition, ready}. Although the partition pid is active at the location Idle, there is no task being executed because of the empty ready queue rq. Leaving the partition leads to the input of exit\_partition, which makes the model return to the location NoTask. However, once a task is ready to run at Idle, the model will insert the task into rq and then schedule the first task in rq via the output channel sched.

- WaitPartition reacts to the set {enter\_partition, ready}. At the location WaitPartition, there is no task being executed despite the existence of tasks being ready in rq, because for the time is out of the partition pid is inactive.

Fig. 10 SMPTaskScheduler model

Each of the tasks going to ready state must be recorded in rq. After entering the next partition window of pid, the model schedules the first task in rq to run.

• Occupied reacts to the set {exit\_partition, ready, release}. At the location Occupied, the time is in a partition window of pid and there is at least one task in the ready queue rq. First, AMPTaskScheduler will react immediately to the input channel exit\_partition and stop the execution of tasks when leaving the current partition window. Second, when a new task is ready, AMPTaskScheduler will handle the input action ready and thus add the task to rq. After that, if the running task recorded in running is not the first element in rq returned from front, the model will promptly emit the output stop[running]! and sched[front()]! to perform preemption. Third, when the running task relinquishes the processor, AMPTaskScheduler will receive notification from the input channel release and remove the task from rq. At the that moment, if the ready queue is not empty, the highest-priority task will be rescheduled via the channel sched[front()].

SMPTaskScheduler template: For the SMP configuration, we need a second task scheduler that can manage a multi-core partition. Consequently, SMPTaskScheduler must be able to manage multiple running tasks running on different cores. The idea of this scheduler is very similar to the AMPTaskScheduler, but there are some elementary differences between the two templates. The SMPTaskScheduler is shown in Fig. 10, and its main difference is that the location Occupied contains a lot of behavior which was originally divined divided between several locations in AMPTaskScheduler. This location's outgoing edges each represent one of the following: (1) Schedule a task, (2) release a task, (3) ready a task, (4) entering Idle if no active tasks exits, and (5) exit partition.

Scheduling a task is done as soon as possible since sched is defined as an urgent channel. Therefore, a synchronization happens without delay if the guards evaluate to true. Part of the guard is to make sure that there is a task ready

for the core in question. The edge with release just removes the given task from the ready queue. For each core there is a corresponding ready queue, such that all active tasks are grouped by their affinity. The queues are arranged by decreasing priority such that the highest priority task is at the front. Whenever a task synchronize over ready, there is a possibility that a task is preempted. We know the affinity of the new ready task, and we therefore know on which core a preemption might occur. Since the tasks are grouped by affinity we just compare the running task with the front of the given core's ready queue. No preemption occurs if the front task is the same as the running task but is otherwise preempted in order for the core to be free for the new task.

If there are no active tasks in any ready queue the location Idle is entered by the use of no\_tasks. This urgent channel is not used to synchronize with any other process but is a way to force the process to enter Idle when possible. The last edge from Occupied uses the channel exit\_partition. As there might be several active tasks, we need to make sure that all tasks are preempted. In WindowExit all active tasks are preempted and only when that is completed the process enters WaitPartition. The main locations in SMPTaskScheduler are in the end the same as in AMPTaskScheduler which means that Table 1 applies for SMPTaskScheduler as well. Even the four major locations of SMPTaskScheduler react to the same sets of channels as in AMPTaskScheduler, and it is therefore following the same event-driven structure pattern.

## 2. Task Layer Models

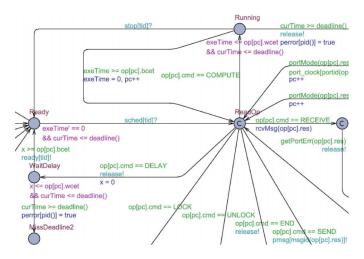

We build two SWA templates PeriodicTask and SporadicTask in UPPAAL. Both templates share the same skeleton, so we take PeriodicTask as an example to sketch out the structure of a task model.

In the template, we define two normal clocks x and curTime and a stopwatch exeTime. The clock x measures the delays prescribed by the task type to calculate the release points of the task. The clock curTime is used to determine the start of the next task period and check if the deadline is missed. By contrast, the stopwatch exeTime measures the processing time during the execution of an abstract instruction that describes concrete task behavior, and will thus progresses only progress when the model is at the location Running.

Once the task is scheduled by TaskScheduler through the channel sched, it will start execution on the processor and move from the location Ready to ReadOp. For any task in the system, a sequential list of abstract instructions is implemented as the structure array op. By using an integer variable pc as a program counter, the task can fetch the next abstract instruction from op[pc] at the location ReadOp (See Fig. 11\*).

According to the command in the abstract instruction currently read from op, the task model performs a conditional branch and moves from the location ReadOp to one of the locations that represent different operations. Therefore, the command set containing the following seven elements divides the rest of the template into seven corresponding parts.

• COMPUTE Command: If the model reads a COMPUTE command, it will (re)start the stopwatch exeTime and enter

<sup>\*</sup>Due to the large size, the complete template is presented in Appendix C.

Fig. 11 Main structure of a task model

the location Running, which means that the processor is being occupied by the task and executing a computation instruction.

- LOCK Command: By reading a LOCK command, the task attempts to acquire the mutual exclusion lock that is specified by the res field of the instruction. The availability of a mutual exclusion lock depends on the priority ceiling protocol. If the lock is available, the task will acquire the lock and return to the location ReadOp immediately. Otherwise, the task will block itself and wait for the lock at the location WaitResource.

- UNLOCK Command: When fetching an UNLOCK command from op, the task releases the lock in the instruction and wakes up one of the tasks blocked on this lock. The woken task will leave the location WaitResource and enter the location Ready to wait for the next scheduling command.

- **DELAY Command:** The instruction with a DELAY command makes a task suspended at the location **WaitDelay** for a specified period of time. Thereafter, the task returns to **Ready**, waiting for its next scheduling command.

- **SEND Command:** The commands SEND and RECEIVE represent non-blocking message I/O operations among different partitions. When the task reads a SEND command with a resource identifier op [pc].res, the corresponding UDP/IP layer model will be notified of the message-sending operation through an output channel pmsg[msgid(op[pc].res)]!, where the offset msgid(op[pc].res) returns the identifier of the message type.

- RECEIVE Command: According to the transfer mode of the source port, there are two ways of processing a RECEIVE command. If the task receives a message from a queuing port, the model will call the function rcvMsg that decreases the counter of the source port. By contrast, the counter of a sampling port does not be isn't changed, but the task checks the source port's clock in the global clock array port\_clock to ensure that the validity of received messages is consistent with the required refresh period of the source port. The clock of a sampling port is reset by the communication layer only when a new message arrives in the port.

- END Command: The command END denotes the accomplishment of the current job in this task period. The task

will relinquish the processor through the channel release and stay at the location WaitNextRelease until the next period starts.

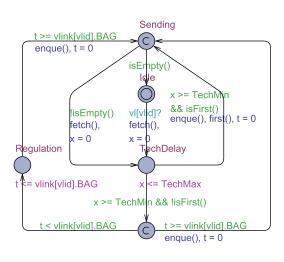

## 3. Communication Layer Models

The communication layer consists of four TA templates: UDPLayer receives message sending requests from the task layer and transfers messages from ARINC-653 ports to their target VLs through the UDP/IP layer. VLink regulates transmitted flows to ensure a BAG (bandwidth allocation gap) interval between two consecutive frames. EndSystem using a First-In-First-Serve (FIFO) scheduler multiplexes the different flows coming from the VLink. SwitchPort acting as the queue inside a switch output port, forwards frames according to a forwarding table. We first detail the template VLink and then briefly describe the other three templates due to their similar skeleton.

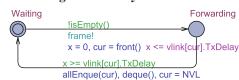

VLink template We create one VLink instance per VL. Its unique template parameter vlid is the identifier of a VL. The VLink models read their configuration from the array vlink, which contains a source port src, an array dst of destination ports, a forwarding table ft, an identifier es of the VL's transmitting ES, an integer field BAG that stands for the bandwidth allocation gap [4], an integer field TxDelay denoting the frame delay [4], etc.

The total delay through a VL is divided into technological and configuration latency. Technological latency is independent of traffic load, whereas configuration latency depends on system configuration and traffic load [4].

The technological latency is bounded on the interval [TechMin, TechMax] where TechMin and TechMax are declared as two integer constants. A clock x measures the nondeterministic technological latency at a location TechDelay. The configuration latency through a transmitting ES is divided into three parts: (1) the floating delay in waiting for the interval of BAG, (2) the jitter within each BAG, and (3) a fixed frame delay. The first delay arises from the traffic regulation of VLink. A clock t measures the first delay since the last output to EndSystem. The second jitter is caused by the interference from other VLs in the same transmitting ES [4]. Hence the jitter will be calculated by the model of EndSystem. The frame delay is finally added to cover the time taken to deliver a frame to the physical link.

As is depicted in Fig. 12, VLink obtains notification of packet-receiving on the input channel vl. At the initial location Idle, VLink waits for the first packet to arrive at the source port. On receiving this first packet, the model fetches it from the port and goes through the technological latency at the location TechDelay. Subsequently, the model sends a new frame by entering the location Sending and resets the clock t to start the latency calculation for a new BAG. Meanwhile, the VL identifier is added to the FIFO queue of the corresponding end system. Leaving the location Sending means VLink has sent a regulated frame to EndSystem.

According to the number of packets in the source port, VLink may wait for the next BAG or the next incoming packet after finishing a sending operation. First, if the model still has at least one packet in the source port to transmit, it will start the next sending procedure by entering TechDelay again. Since there is at least a BAG interval between two consecutive frames, VLink should wait for the start of the next BAG at location Regulation before entering Sending.

Fig. 13 UDP layer model

Fig. 14 End system model

Fig. 12 VLink model

Fig. 15 Switch port model

Second, if the source port is empty, the model will stay at Idle until the next incoming packet arrives.

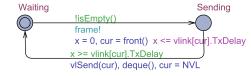

The other templates As shown in Fig. 13-15, the other three templates share the a similar structure. All of them have a Waiting location at which they wait for the next incoming packet from their upper layer. Once they are notified via an input channel or an increment of shared variables, they will enter another "Transmission" location and transfer the packet from the upper to the lower. The model returns to Waiting and repeats this process after finishing the transit operation. In addition, EndSystem and SwitchPort use an urgent channel frame to check their own FIFO buffers in time. They choose destination buffer(s) on the basis of the forwarding table ft of VLs. The function enque adds the VL identifer of a frame to the next buffer, while deque removes the front from the its own buffer.

# V. Compositional Analysis

This section focuses on the compositional schedulability analysis, which verifies local properties of individual partitions by symbolic model checking, infers that they still hold in the complete system, and finally deduces global properties of the system.

We adopt the paradigm of assume-guarantee reasoning [43] to implement the compositional analysis. The basic element of this paradigm is normally expressed as a triple  $\langle \phi \rangle M \langle \varphi \rangle$ , where  $\phi$  and  $\varphi$  are logic formulas and M is a model. The triple is true if whenever M is a constituent of a system satisfying  $\phi$ , the system is guaranteed to satisfy  $\varphi$ . Consider the system consisting of two components M and M'. A typical assume-guarantee rule is defined as

$$\frac{\langle true \rangle M' \langle \phi \rangle \quad \langle \phi \rangle M \langle \varphi \rangle}{\langle true \rangle M || M' \langle \varphi \rangle} \tag{3}$$

where the environment M' of the component M guarantees the assumption  $\phi$  of M. It concludes that the complete system satisfies  $\varphi$ .

A classic way [52] to realize such a paradigm is to provide a preorder  $\leq$  on the finite-state models that captures the notion of "more behaviors" and to use a logic whose semantics is consistent with the preorder. The preorder should not only preserve satisfaction of the logic formulas but also hold in composition operations of models. For example, if a formula is true for a model, it will also be true for any model that is smaller in the preorder. Additionally, satisfaction of a formula corresponds to being smaller than a tableau model of the formula in the preorder. Hence assumptions can be defined either as logic formulas or directly as finite-state models. Let A be the tableau of the assumption  $\phi$ . The above assume-guarantee rule can be expressed as

$$\frac{M' \le A \quad M || A \models \varphi}{M || M' \models \varphi} \tag{4}$$

Considering the conciseness and convenience, we describe assumptions of each component as SWA models directly and implement assume-guarantee reasoning as the rule of Eq. (4).

In this section, we first define a preorder, timed selection simulation relation on SWA models. On the basis of its properties, we present the procedure for compositional analysis in the paradigm of assume-guarantee reasoning. A simplified avionics system exemplifies the use of our compositional analysis.

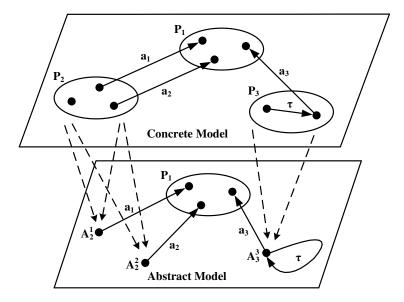

## A. Timed Selection Simulation

We propose a notion of timed selection simulation relation to support assume-guarantee reasoning. Compared with some other abstraction relations like timed simulation [53] and timed ready simulation [54], timed selection simulation only abstracts a selected subset of actions from the concrete model. Applying timed selection simulation to the abstraction of a concrete system, one can pay attention to part of the system, individually model the behavior of each component, and thereby obtain a composite abstract model rather than a monolithic one.

Considering the semantic object  $\mathcal{T}^A$  of an automaton  $A \in \Omega$ , we denote the *error states* of  $\mathcal{T}^A$  by the set  $\mathcal{E} = \{\langle l, u \rangle | l \in Err \}$  where Err is the error-location set of A. Thus, for any TIOTS  $\mathcal{T} = \langle S, s_0, \Sigma, \rightarrow \rangle$ , its error states are defined as a set  $\mathcal{E} \subseteq S$ , and the following function  $g: S \to \{true, false\}$  indicates whether a state  $s \in S$  has violated schedulability properties:

$$g(s) = \begin{cases} true & \text{if } s \in \mathcal{E} \\ false & \text{if } s \notin \mathcal{E}. \end{cases}$$

(5)

Given two compatible TIOTSs  $\mathcal{T}_i$ ,  $i \in \{1, 2\}$  with the error-state set  $\mathcal{E}_i$ , their composition  $\mathcal{T}_1 \| \mathcal{T}_2$  has the error-state set  $\mathcal{E}_{\mathcal{T}_1 \| \mathcal{T}_2} = \{ \langle s_1, s_2 \rangle | s_1 \in \mathcal{E}_1 \lor s_2 \in \mathcal{E}_2 \}$  and the function  $g(\langle s_1, s_2 \rangle) = g(s_1) \lor g(s_2)$ .

Based on the function g(s), the formal definition of timed selection simulation is given as follows.

**Definition 5 (Timed Selection Simulation)** Let  $\mathcal{T}_1 = \langle S_1, s_{1,0}, \Sigma_1, \rightarrow_1 \rangle$  and  $\mathcal{T}_2 = \langle S_2, s_{2,0}, \Sigma_2, \rightarrow_2 \rangle$  be two timed I/O transition systems with  $\Sigma_2 \subseteq \Sigma_1$ . Let R be a relation from  $S_1$  to  $S_2$ . We call R a timed selection simulation from  $\mathcal{T}_1$  to  $\mathcal{T}_2$ , written  $\mathcal{T}_1 \leq \mathcal{T}_2$  via R, provided  $(s_{1,0}, s_{2,0}) \in R$  and for all  $(s_1, s_2) \in R$ ,  $g(s_1) = g(s_2)$  and

- 1) if  $s_1 \xrightarrow{a?} s_1'$  for some  $s_1' \in S_1$ ,  $a \in \Sigma_2$ , then  $\exists s_2' \in S_2$  such that  $s_2 \stackrel{a?}{\Longrightarrow} s_2'$  and  $(s_1', s_2') \in R$

- 2) if  $s_1 \xrightarrow{a!} s_1'$  for some  $s_1' \in S_1$ ,  $a \in \Sigma_2$ , then  $\exists s_2' \in S_2$  such that  $s_2 \stackrel{a!}{\Longrightarrow} s_2'$  and  $(s_1', s_2') \in R$

- 3) if  $s_1 \xrightarrow{a} s_1'$  for some  $s_1' \in S_1$ ,  $a \in (\Sigma_1 \setminus \Sigma_2) \cup \{\tau\}$ , then  $\exists s_2' \in S_2 \text{ such that } s_2 \xrightarrow{\bullet} s_2' \text{ and } (s_1', s_2') \in R$

- 4) if  $s_1 \xrightarrow{\epsilon(d)} s_1'$  for some  $s_1' \in S_1$ , d > 0, then  $\exists s_2' \in S_2$  such that  $s_2 \xrightarrow{\epsilon(d)} s_2'$  and  $(s_1', s_2') \in R$ .

**Definition 6 (Timed Selection Simulation between SWA)** *Let*  $A_i$ ,  $i \in \{1, 2\}$  *be stopwatch automata. We say that*  $A_1 \le A_2$ , *if and only if their corresponding timed I/O transition systems*  $\mathcal{T}_i$  *satisfy*  $\mathcal{T}_1 \le \mathcal{T}_2$ .

We now give some necessary properties of timed selection simulation.

**Theorem 1 (Preorder)** *Timed selection simulation*  $\leq$  *is a preorder.*

For any automaton  $A \in \Omega$ , by construction, the reachability of its error locations is equivalent to that of the error states in the corresponding TIOTS  $\mathcal{T}^A$ . Hence the following theorem shows that timed selection simulation can preserve the satisfaction of the safety properties in the form of Eq.(1).

**Theorem 2 (Property preservation)** Let  $\mathcal{T}_i$ ,  $i \in \{1,2\}$  be timed I/O transition systems and  $\mathcal{E}_i$  be the set of error states of  $\mathcal{T}_i$ . Given a safety property  $\varphi : \forall \neg reach(\mathcal{E}_i)$  that any error states are not reachable, if  $\mathcal{T}_1 \leq \mathcal{T}_2$  and  $\mathcal{T}_2 \models \varphi$ , then  $\mathcal{T}_1 \models \varphi$ .

**Theorem 3 (Abstraction compositionality)** *Let*  $\mathcal{T}_i$ ,  $i \in \{1, 2, 3\}$  *be timed I/O transition systems. If*  $\mathcal{T}_1 \leq \mathcal{T}_2$ ,  $\mathcal{T}_1 \leq \mathcal{T}_3$ , and  $\mathcal{T}_2$  and  $\mathcal{T}_3$  are compatible, then  $\mathcal{T}_1 \leq \mathcal{T}_2 \| \mathcal{T}_3$ .

**Theorem 4 (Compositionality)** Let  $\mathcal{T}_i = \langle S_i, s_{i,0}, \Sigma_i, \rightarrow_i \rangle$ ,  $i \in \{1, 2, 3, 4\}$  be timed I/O transition systems. Suppose  $\mathcal{T}_1 \| \mathcal{T}_3$  and  $\mathcal{T}_2 \| \mathcal{T}_4$  are the parallel compositions of compatible timed I/O transition systems. If  $(1) \mathcal{T}_1 \leq \mathcal{T}_2, \mathcal{T}_3 \leq \mathcal{T}_4$ , and  $(2) O_1 \cap I_4 \subseteq \Sigma_2, I_2 \cap O_3 \subseteq \Sigma_4$ , then  $\mathcal{T}_1 \| \mathcal{T}_3 \leq \mathcal{T}_2 \| \mathcal{T}_4$ .

## **B. Procedure for Compositional Analysis**

Our compositional analysis exemplifies the paradigm of assume-guarantee reasoning. Compared to the existing assume-guarantee approaches, our approach is based on the timed selection simulation relation that has the novel feature of abstraction compositionality. This property helps engineers generate the abstract model of a component automatically by combining a set of simple message interface automata. When a partition  $P_i$  is checked independently, these message interface automata describe the external behavior of the other partitions, serving as the assumptions of  $P_i$  in assume-guarantee reasoning.

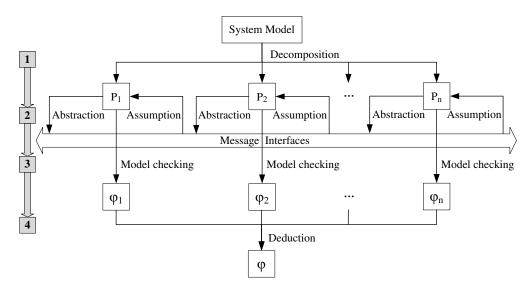

Fig. 16 Compositional analysis procedure

We apply the assume-guarantee rules like Eq. (4) to our compositional analysis, and describe the schedulability goal as the safety property  $\varphi$  of Eq. (1). As shown in Fig. 16, our compositional analysis is comprised of the following four steps:

- 1) *Decomposition:* The system is first decomposed into a set of communicating partitions modeled by TA and SWA. The global property  $\varphi$  is also divided into several local properties, each of which belongs to one partition.

- 2) Construction of message interfaces: We define message interfaces as the assumption and abstraction of the communication environment for each partition. In general, the templates of message interfaces should be built manually by the engineers.

- 3) *Model checking*: The local properties under the assumptions and the abstraction relations are verified by model checking.

- 4) *Deduction:* From the assume-guarantee rules, we finally derive the global property by combining all the local results.

The procedure can be performed automatically except for the first construction of message interfaces. We assume that a task never blocks while communicating with other partitions, which is commonly used in avionics systems [11, 22]. Otherwise a loop of communication dependency will cause circular reasoning, because the assumptions of a partition might be based on its own state recursively.

## 1. Decomposition

We first instantiate the templates of the UPPAAL modeling framework to construct the SWA model of a complete avionics system  $\Lambda$ . Given a template name Template, we define the set of its SWA instances in the system as {Template} and the composition of all the elements in {Template} as [Template]. Let  $\Phi(A)$  be the set of SWA instances for any

model A.  $\Phi(\Lambda)$  contains nine disjoint sets, each of which corresponds to one template in the modeling framework:

$$\begin{split} \Phi(\Lambda) = & \big\{ \{ \text{PartitionScheduler} \} \cup \{ \text{AMPTaskScheduler} \} \cup \{ \text{PeriodicTask} \} \\ & \cup \{ \text{SporadicTask} \} \cup \{ \text{UDPLayer} \} \cup \{ \text{VLink} \} \cup \{ \text{EndSystem} \} \cup \{ \text{SwitchPort} \} \big\}. \end{split}$$

Hence the system  $\Lambda$  is described as a composite SWA model

$$\Lambda = [PartitionScheduler] \| [AMPTaskScheduler] \| [SMPTaskScheduler] \| [PeriodicTask] \\ \| [SporadicTask] \| [UDPLayer] \| [VLink] \| [EndSystem] \| [SwitchPort].$$

(7)

Assume that there are n constituent partitions in a system. Let  $P_i$ ,  $i \in \{1, 2, ..., n\}$  be the SWA composite model of the ith partition. We also refer to this partition as  $P_i$  if its meaning is not ambiguous.  $P_i$  consists of all the SWA instances of the scheduling and task layer within the partition:

$$P_i = [PartitionScheduler]_i || [AMPTaskScheduler]_i || [SMPTaskScheduler]_i || [PeriodicTask]_i || [SporadicTask]_i (8)$$

where the constituent models belong exclusively to  $P_i$ . Thus the scheduling and task layer of the system are divided into n disjoint composite model of partitions  $P_i, i \in \{1, 2, ..., n\}$ , and  $\bigcap_{i \in \{1, 2, ..., n\}} \Phi(P_i) = \emptyset$ .

By contrast, all the partitions share the same model F of the AFDX network facilities in the communication layer:

$$F = [UDPLayer] ||[VLink]||[EndSystem]||[SwitchPort]$$

(9)

which cannot be decomposed like the above layers. However, when only considering the communication environment of one partition  $P_i$ , we traverse the forwarding table ft of VLs and recursively extract models of the network facilities that affect the message transmission to  $P_i$  directly or indirectly. In doing so, F is decomposed into n intersecting composite model  $F_i$ ,  $i \in \{1, 2, ..., n\}$ :

$$F_i = [\mathsf{UDPLayer}]_i ||[\mathsf{VLink}]_i||[\mathsf{EndSystem}]_i||[\mathsf{SwitchPort}]_i$$

(10)

where it is possible that  $\bigcap_{i \in \{1,2,...,n\}} \Phi(F_i) \neq \emptyset$ . We define the composite model of the partition  $P_i$  with its network facilities  $F_i$  as  $P_i^* = P_i || F_i$ .

Let  $Err_i$  be the error-location set of  $P_i$ . The safety property  $\varphi_i$ : A[]  $\neg(\bigvee_{loc \in Err_i} loc)$  denotes the schedulability of  $P_i$ . The global property  $\varphi$  is therefore written as  $\varphi_1 \wedge \varphi_2 \wedge \cdots \wedge \varphi_n$ , and the goal of our schedulability analysis is

expressed as the verification problem:

$$\Lambda \models \varphi. \tag{11}$$

Since the error-location set  $Err_i$  is only allowed to be manipulated by  $P_i$ , the problem can be further divided into n satisfaction relations:

$$P_i^* \parallel ( \Big\|_{i=1, i \neq i}^n P_j ) \models \varphi_i, \ i \in \{1, 2, \dots, n\}.$$

(12)

When handling the property  $\varphi_i$ , we also write  $P_i$  instead of  $P_i^*$  without ambiguity. These n subproblems are thus written as

$$P_1 || P_2 || \cdots || P_n \models \varphi_i, \ i \in \{1, 2, \dots, n\}.$$

(13)