Aalborg Universitet

#### Mission Profile Based Control and Reliability Improvement Strategies of Modular **Multilevel Converters**

Wang, Zhongxu

Publication date: 2019

**Document Version** Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA): Wang, Z. (2019). Mission Profile Based Control and Reliability Improvement Strategies of Modular Multilevel Converters. Aalborg Universitetsforlag.

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## MISSION PROFILE BASED CONTROL AND RELIABILITY IMPROVEMENT STRATEGIES OF MODULAR MULTILEVEL CONVERTERS

BY ZHONGXU WANG

**DISSERTATION SUBMITTED 2019**

AALBORG UNIVERSITY DENMARK

## Mission Profile Based Control and Reliability Improvement Strategies of Modular Multilevel Converters

Ph.D. Dissertation Zhongxu Wang

Dissertation submitted October, 2019

| Dissertation submitted:   | October, 2019                                                                                                             |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------|

| PhD supervisor:           | Prof. Huai Wang<br>Aalborg University                                                                                     |

| Assistant PhD supervisor: | Prof. Frede Blaabjerg<br>Aalborg University                                                                               |

| PhD committee:            | Associate Professor Sanjay Kumar Chaudhary (chair.)<br>Department of Energy Technology<br>Aalborg University              |

|                           | Associate Professor Maryam Saeedifard<br>School of Electrical and Computer Engineering<br>Georgia Institute of Technology |

|                           | Principal Scientist Nan Chen<br>ABB Corporate Research<br>Vasteras                                                        |

| PhD Series:               | Faculty of Engineering and Science, Aalborg University                                                                    |

| Department:               | Department of Energy Technology                                                                                           |

| ISSN (online): 2446-1636  |                                                                                                                           |

ISBN (online): 978-87-7210-520-8

Published by: Aalborg University Press Langagervej 2 DK – 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Zhongxu Wang

Printed in Denmark by Rosendahls, 2019

## Abstract

Modular multilevel converters (MMCs) are typically composed of hundreds of power devices and capacitors. Its fast-growing application and complexity call for much more attention and research need on its reliability performance. Given its different topology from conventional two- or three-level converters, how to effectively improve the reliability of the MMC has not been sufficiently studied. In order to cope with these issues, this thesis firstly studies a sub-module (SM) based reliability testing scheme of the MMC and then proposes reliability improvement strategies from a control perspective. Two condition monitoring strategies for SM capacitors are also introduced and validated experimentally.

In order to illustrate the limitations of existing SM based testing schemes, an overview of existing testing emulators is given. Based on the challenges, this Ph.D. project proposes a mission profile emulator for power modules in the MMC. By integrating an auxiliary SM based voltage stabilizer, the testing scheme is applicable to mimic practical current profiles and switching profiles. Meanwhile, due to the decoupling between the voltage of DC power supply and the high voltage of SM capacitors, the power rating and voltage rating of the used power supply in the current source are both significantly reduced. In order to facilitate the implementation of this setup, a guideline regarding the selection of control parameters and hardware parameters is provided. Simulation and experiment results validate the effectiveness of the proposed mission profile emulator.

Capacitor voltage balancing control offers an internal conduction loss balancing mechanism among SMs. An analytical evaluation validates that the balanced conduction loss distribution is independent of the control, modulation and loading conditions of the MMC. However, due to parameter mismatch and the low switching frequency operation of the MMC, switching losses are not evenly distributed among SMs. Thus, a power loss balancing control is proposed in this project. The switching loss differences among SMs can be reduced to less than 25%.

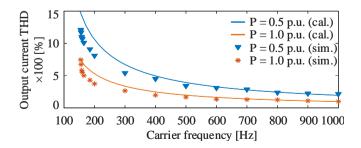

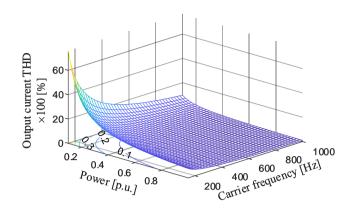

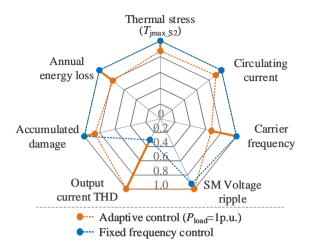

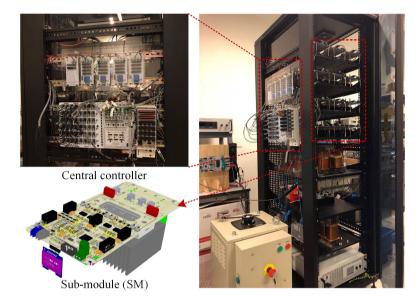

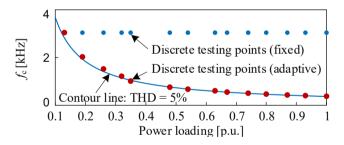

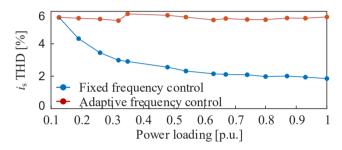

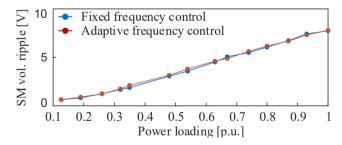

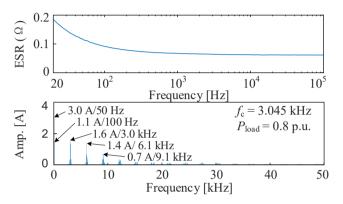

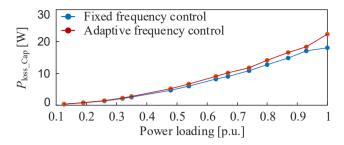

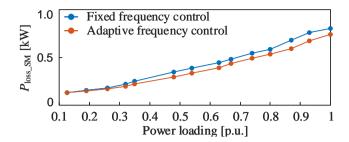

For MMCs connected to the grid, stringent grid codes are supposed to be fulfilled during the operation. In order to limit the output current THD within a specific range, a relatively high switching frequency has to be employed for MMCs with a relatively small number of SMs considering conventionally fixed carrier frequency. Large switching losses can be generated for heavy loading conditions for high voltage rating power devices. In this regard, this Ph.D. project proposed an adaptive control to dynamically adjust the carrier frequency according to the loading conditions of the MMC. The carrier frequency boundaries regarding the output current THD and SM capacitor voltage ripple are first explored. Based on the results, the lowest allowable switching frequency can be applied to the MMC while meeting the requirements of output current THD and SM capacitor voltage ripple. A mission profile-based reliability evaluation is conducted to illustrate the impact of the proposed method on the efficiency, thermal stress, and lifetime of the MMC. A case scenario based on a 15 kVA three-phase MMC is also studied experimentally. The observed power loss reduction of power devices validates the effectiveness of the proposed method.

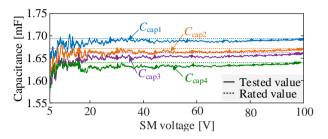

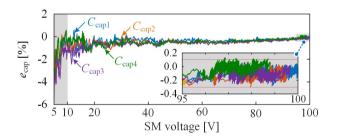

Capacitors are one of the components prone to failure in power electronic converters. When it comes to the MMC, the reliability concern about SM capacitors is much more serious since they typically account for over 50% and 80% of the volume and weight of one SM, respectively. Since the capacitor ages with time, as one of the means to improve reliability, condition monitoring of SM capacitors is important regarding the reliable operation of the MMC. Due to high voltage rating, film capacitors are typically applied in the MMC. One of the end-of-life criteria of film capacitors is typically 5-10% capacitance drop. The tiny capacitance change poses a challenge for the condition monitoring (CM) of film capacitors. In order to enhance the monitoring accuracy, two CM methods are proposed in this Ph.D. project. Firstly, it is based on the DC-side start-up of the MMC. An RC charging circuit formed during the start-up process can be utilized to extract the capacitance values. The impacts of diode tolerance and degradation, bleeding resistor tolerance and time delay are discussed. Experimental validation is provided in the end.

The second condition monitoring method takes full advantages of the SM voltage sensor range. The monitoring accuracy can be significantly improved. The precondition is that the capacitance of the reference SM should be known beforehand by applying existing CM methods but with more accurate sensors or extra measurement circuits. For comparison, an accuracy analysis is conducted. Practical considerations regarding the implementation of these proposed methods are discussed, namely the detection of reference SM capacitance and the impact of the proposed method on the operation of the MMC. Experiments based on capacitors with small capacitance differences (e.g., from 0% to 3.2%) show that the proposed method can achieve the objective of capacitor monitoring with enhanced accuracy, less computational burden, and loading-independent characteristics.

## Resumé

Modulære multilevel konvertere (MMCs) er almindeligvis sammensat af hundredvis af effektelektroniske komponenter og kondensatorer. Deres stadig stigende anvendelse og øget kompleksitet kræver stor opmærksomhed og forskningsbehov, i forbindelse med deres evne til at operere pålideligt. I betragtning af de forskellige konventionelle konverter topologier på henholdsvis to og tre niveauer er de ikke blevet forsket tilstrækkelig i forbindelse med en effektiv forbedring af modulære multilevel konverteres pålidelighed. For at overkomme de nuværende problemstillinger undersøges pålideligheden af sub-moduler indledningsvist i dette projekt og der foreslås udfra dette pålidelighedsforbedringer fra et kontrol perspektiv. To tilstandsovervågningsstrategier for SM-kondensatorer introduceres og valideres eksperimentelt.

For at illustrere begrænsningerne i eksisterende SM-baserede testanordninger, gives der en oversigt over eksisterende testemulatorer. Udfra de nuværende problemstillinger baserer dette Ph.D. projekt en operativ profil emulator for effektelektroniske moduler i modulære multilevel konvertere. Ved at integrere en ekstra SM-baseret spændingsstabilisator er testanordningen i stand til at efterligne strømprofiler og tilstandsprofiler af kontakterne. Samtidigt kan der som følge af afkobling mellem DC-strømforsyningens spænding og den høje spænding af SM-kondensatoren, kan både effekten of spænding reduceres betydeligt i den anvendte strømforsyning. For at lette implementeringen af denne opsætning angives der retningslinjer for valg af både kontrolparametre og hardwareparametre. Effektiviteten af den foreslåede operations profil emulator valideres gennem simuleringer og eksperimentelle resultater.

Gennem afbalanceringskontrol af kondensator spændingen opstår muligheden for en balance mekanisme af det indre ledningstab mellem submoduler. Gennem analytisk evaluering valideres det at den afbalancerede ledningstabsfordeling er uafhængig af styring, modulering og belastningstilstand for modulære multilevel konvertere. Tabet i kontakterne fordeles dog ikke jævnt mellem sub-modulerne, hvilket skyldes en uoverensstemmelse mellem parametrene kontaktstyringsfrekvens af modulære multilevel konvertere. Derfor præsenteres en balance kontrol af effekttabet i dette projekt, hvor forskellene i effekttabet som er grundet tilstandsændringer i kontakterne reduceres til mindre end 25%

For netforbundet modulære multilevel konvertere gælder der strenge net betingelser, som skal overholdes under operation. For at begrænse udgangsstrømmens THD til at være indenfor et specificeret område, skal der anvendes en relativ høj tilstands skifte frekvens for modulære multilevel konvertere med relativ lavt antal sub-moduler, hvor der anvendes en konventionel fast bærefrekvens. Store tab ved tilstandsskift opstår ved store lasttilstande for effektenheder som opererer ved høje spændinger. Derfor præsenterer dette Ph.D. projekt en tilpassende kontrolstrategi til at justere bærefrekvens i forhold til den modulære multilevel konverters lasttilstand. Indledningsvist undersøges bærefrekvensens grænseværdier med hensyn til udgangsstrømmens THD og ripple spændingen af sub-modul kondensaterne. Udfra disse resultaterne kan den lavest tilladelige switching frekvens påføres MMC'en kravende om udgangsstrømmens THD og spændings ripplen af sub-moduls kondensaterne stadig overholdes. En pålideligheds evaluering, som er baseret på operations profiler, er udført for at illustrere hvilken indflydelse den foreslået metode har på effektiviteten, det termiske stress og livstiden af MMC'en. Et case baseret scenario hvori en 15 kVA tre-faset MMC testes eksperimentelt. Gennem reduktionen i det observerede effekttab af effektenhederne valideres effektiviteten af den foreslået metode.

Kodensatorer er en af de komponenter, som indgår i effektkonverterer, som er tilbøjelig til at svigte. I tilfældet hvor disse SM-kondesatorer indgår i modulære multilevel konverteres er dette pålidelighedsproblem langt mere alvorligt, da kondensatorne udgør mere end 50% af volumen og 80% af vægten af et SM. En af de måder hvorpå pålideligheden kan forbedres er gennem tilstandsovervågning af SM kondensatorne, som vil give indblik i den forringet tilstand i takt med at kondensatorne ældes og som kan sikre en pålidelig drift af modulære multilevel konvertere. Som et resultat af de høje operationsspændinger anvendes der ofte filmkondensatorer i modulære multilevel konvertere. Et ofte anvendt livstidskriterie for filmkondensatornes er et fald i dens kapacitans i størrelsesordenen 5-10%. Denne forholdsvis lille kapacitansændring udgør en udfordring ift. tilstandsovervågning og for at forbedre nøjagtigheden af tilstandsovervågningen præsenteres to metoder i dette Ph.D. projekt. Den første metode er baseret på DC-sidens opstart af den modulære multilevel konverter. I opstartsprocessen kan RC opladnings kredsløbet udnyttes til at angive størrelserne af kapacitanserne. Indflydelserne af diodetolerancer og komponentforringelse gennem ældning, diskuteres blødningsmodstandstolerance og tidsforsinkelse. Der gives i slutning en eksperimentel validering.

Den anden tilstandsovervågningsmetode drager fuld fordel sub-modulets spændingssensor interval. Nøjagtigheden af tilstanden kan forbedres markant, hvis kapacitansen af reference sub-modulet er kendt op forhånd. Dette gøres ved at anvende allerede eksisterende tilstandsovervågningsmetoder men hvor der enten anvendes sensorer med større nøjagtighed eller der påføres et ekstra målekredsløb. Praktisk overvejelser ift. implementering af de foreslåede metoder diskuteres, især hvordan reference kapacitansen af SM og hvilken indvirkning denne metode har på den modulære multilevel konverters virkemåde. Der udføres eksperimenter med kondensatorer, hvor kapacitans forskellene er forholdsvis lille (f.eks. fra 0% til 3,2%). Disse eksperimenter viser at den foreslåede metode er i stand til at nå målet ift. en forbedring af nøjagtigheden af tilstandsovervågning af kondensatorer og samtidig opnå mindre beregningsbyrde og bedre belastningsuafhængige egenskaber.

## Preface

This Ph.D. thesis is a summary of the outcomes from the Ph.D. project entitled "Mission Profile Based Control and Reliability Improvement Strategies of Modular Multilevel Converters". This Ph.D. project is mainly supported by Department of Energy Technology, Aalborg University, Denmark and Otto Mønsteds Fond. Special acknowledgement is given to the Center of Reliable Power Electronics (CORPE).

First of all, I would like to take this opportunity to express my deepest gratitude to my supervisor, Professor Huai Wang, for his valuable, insightful and patient guidances and discussions during my Ph.D. study. I would also like to thank my co-supervisor Professor Frede Blaabjerg for his consistent advices, support and encouragement. I am really honored to have the opportunity to work with them.

I am also grateful to Professor Tim Green for his kindness and fruitful discussion during my stay at Imperial College London and broadening my vision in the field of modular multilevel converters.

Special thanks go to Yi Zhang for his support and selfless dedication to the joint Ph.D. project. It has been such a great experience to collaborate with him. I would also like to thank all my local and external colleagues from the Department of Energy Technology, Aalborg University and the Energy Future lab of Imperial College London for their valuable discussions and great hospitality.

Last but not least, I would like to express my sincere gratitude to my family for their unconditional love, support and understanding all the way. They have been always encouraging me to find my own path in life to make me who I am today.

> Zhongxu Wang Aalborg University, October 20, 2019

Preface

## Contents

| A                                       | bstra | ct                            |                                          | iii |

|-----------------------------------------|-------|-------------------------------|------------------------------------------|-----|

| Re                                      | esum  | é                             |                                          | v   |

| Pı                                      | eface | !                             |                                          | ix  |

| I                                       | Re    | port                          |                                          | 1   |

| 1                                       | Intr  | oductio                       | on                                       | 3   |

|                                         | 1.1   | Backg                         | round and Motivation                     | 3   |

|                                         |       | 1.1.1                         | MMC Mission Profile Emulator             | 8   |

|                                         |       | 1.1.2                         | Reliability-Oriented Control of MMCs     | 9   |

|                                         |       | 1.1.3                         | Capacitor Condition Monitoring of MMCs   | 10  |

|                                         | 1.2   | Projec                        | t Objectives and Limitations             | 11  |

|                                         |       | 1.2.1                         | Research Questions                       | 11  |

|                                         |       | 1.2.2                         | Research Objectives                      | 12  |

|                                         |       | 1.2.3                         | Project Limitations                      | 13  |

|                                         | 1.3   |                               | S Outline                                | 13  |

|                                         | 1.4   | List of                       | f Publications                           | 13  |

| 2                                       | Mis   | sion Pr                       | ofile Emulator for Power Modules in MMCs | 15  |

|                                         | 2.1   | Backg                         | round                                    | 15  |

| 2.2 Existing SM Based Testing Solutions |       | ng SM Based Testing Solutions | 16                                       |     |

|                                         |       | ogy and Control Scheme        | 18                                       |     |

|                                         |       | 2.3.1                         | Topology of Mission Profile Emulator     | 18  |

|                                         |       | 2.3.2                         | Control of Mission Profile Emulator      | 21  |

|                                         |       | 2.3.3                         | Control and Hardware Parameter Selection | 22  |

|                                         |       | 2.3.4                         | Practical Considerations                 | 25  |

|                                         | 2.4   | Missie                        | on Profile Emulator Demonstration        | 28  |

|                                         |       | 2.4.1                         | Capacitor Voltage Control                | 29  |

|                                         |       | 2.4.2                         | AC Power Cycling Testing                 | 30  |

|   | 2.5        | 2.4.3 Electro-Thermal Model Validation                        | 31<br>33 |

|---|------------|---------------------------------------------------------------|----------|

| 3 |            | ver Loss Balancing Control of MMCs                            | 37       |

| 3 | 3.1        | Background                                                    | 37       |

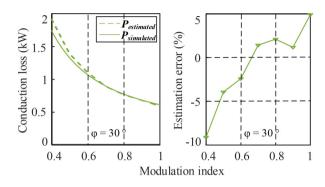

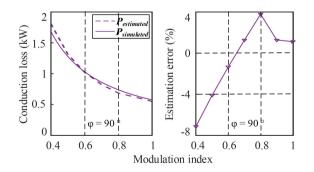

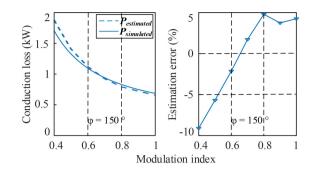

|   | 3.1<br>3.2 | Balanced Conduction Loss Distribution among SMs in MMCs .     | 38       |

|   | 5.2        | 3.2.1 Conduction Loss Estimation                              | 38       |

|   |            | 3.2.2 Case Study: Three-Phase MMC Based Simulation Vali-      | 50       |

|   |            | dation                                                        | 42       |

|   |            | 3.2.3 Case Study: MMC Emulator Based Experimental Vali-       | 74       |

|   |            | dation                                                        | 43       |

|   | 3.3        | Imbalanced Switching Loss Distribution among SMs in MMCs      | 45       |

|   |            | 3.3.1 Low Switching Frequency                                 | 46       |

|   |            | 3.3.2 Parameter Mismatch                                      | 46       |

|   | 3.4        | Power Loss Balancing Control of MMCs                          | 47       |

|   |            | 3.4.1 Switching Loss Model                                    | 47       |

|   |            | 3.4.2 Imbalance Degree Extractor                              | 48       |

|   |            | 3.4.3 PLBC Regulator and Enable Module                        | 49       |

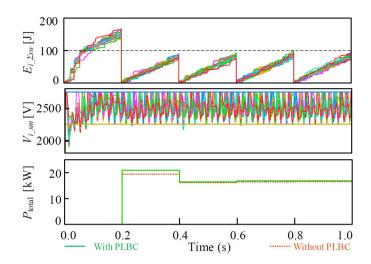

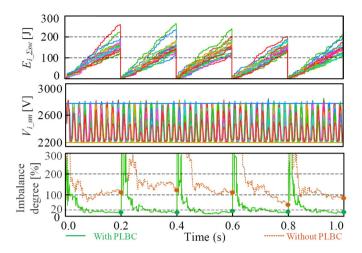

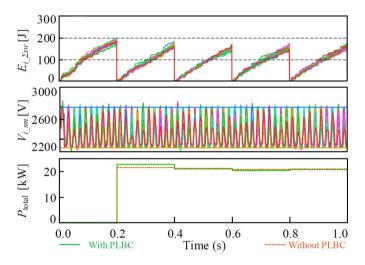

|   |            | 3.4.4 Simulation Validation                                   | 50       |

|   | 3.5        | Summary                                                       | 51       |

| 4 | Ada        | aptive Carrier Frequency Control of MMCs                      | 53       |

| - | 4.1        | Background                                                    | 53       |

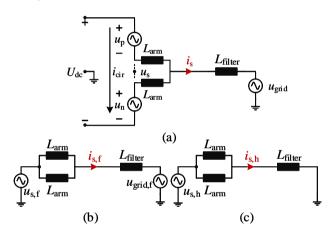

|   | 4.2        | Impact of Carrier Frequency on Harmonics and Capacitor Volt-  |          |

|   |            | age Ripple                                                    | 55       |

|   |            | 4.2.1 Output Current Harmonics                                | 55       |

|   |            | 4.2.2 Capacitor Voltage Ripple                                | 57       |

|   | 4.3        | Adaptive Carrier Frequency Control and Reliability Evaluation | 59       |

|   |            | 4.3.1 Adaptive Carrier Frequency Control                      | 59       |

|   |            | 4.3.2 Power Loss and Thermal Stress Evaluation                | 60       |

|   |            | 4.3.3 Reliability Evaluation                                  | 66       |

|   | 4.4        | Case Study: Three-Phase MMC Based Experimental Validation     | 69       |

|   |            | 4.4.1 Output Current THD and SM Voltage Ripple                | 70       |

|   | 4 -        | 4.4.2 Power Loss                                              | 72       |

|   | 4.5        | Summary                                                       | 75       |

| 5 | Con        | ndition Monitoring of Capacitors in MMCs                      | 77       |

|   | 5.1        | Background                                                    | 77       |

|   | 5.2        | DC-Side Start-Up Based Condition Monitoring                   | 78       |

|   |            | 5.2.1 Operation Principle                                     | 78       |

|   |            | 5.2.2 Practical Considerations                                | 80       |

|   | _          | 5.2.3 Experimental Validation                                 | 83       |

|   | 5.3        | Reference Submodule Based Condition Monitoring                | 85       |

#### Contents

|    |       | 5.3.2   | Operation Principle     | 87  |

|----|-------|---------|-------------------------|-----|

|    |       |         | Accuracy Analysis       | 90  |

|    |       | 5.3.4   | Experimental Validation | 92  |

|    | 5.4   | Summ    | nary                    | 95  |

| 6  | Con   | clusion | n and Outlook           | 97  |

|    | 6.1   | Summ    | nary                    | 97  |

|    | 6.2   | Main    | Contributions           | 99  |

|    | 6.3   | Resear  | rch Perspectives        | 100 |

| Bi | bliog | raphy   |                         | 103 |

|    | •     | ~ •     |                         | 103 |

Contents

# Part I

## Report

## Chapter 1

## Introduction

This chapter presents the background and motivation of the Ph.D. project. The research questions and objectives are discussed. Then, the outline of the Ph.D. thesis is presented to show the flow of this research work.

#### 1.1 Background and Motivation

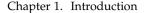

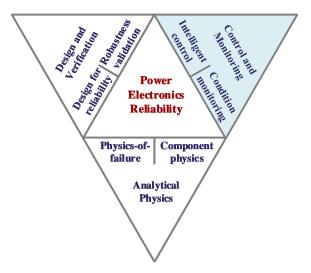

Modular multilevel converter (MMC) is a hot research area in power electronics. Nevertheless, majority of the studies focus on the topology configurations [1, 2], circulating current control[3], voltage control algorithms [4–6], and modulation strategies [7–10]. In practical applications, such as highvoltage direct current (HVDC) transmission [11, 12], offshore wind farms [13, 14] and variable speed drive [15–17], major challenges are: 1) fulfilling stringent reliability requirements while limiting the cost of the MMC system during the design phase in terms of thousands of main components including insulated gate bipolar transistors (IGBTs) and sub-module (SM) capacitors; 2) enhancing the reliability/availability of the MMC system in operation in terms of degradation of main components caused by severe operation environments or mission profiles. Therefore, in 2016, we started the MMC reliability research with two planned Ph.D. research topics, which focus on "design and verification" and "control and monitoring" of the MMC, respectively, according to the power electronics reliability triangle as shown in Fig. 1.1. This presented Ph.D. thesis focuses on the latter one.

The scope of power electronics reliability includes three major aspects. The analytical analysis is to understand the failure mechanism of power electronic products from the physics point of view [19]. Design and verification is to design the reliability and to ensure sufficient robustness of power electronics during the initial design phase [20]. The control and monitoring is targeting to ensure reliable operation of the power electronic system under

Fig. 1.1: Scope of power electronics reliability [18].

particular mission profiles [21, 22]. It means that not only hardware design but also more intelligence should be introduced into future products [18]. This Ph.D. project focuses specifically on the third aspect of the reliability triangle, namely control and monitoring, to enhance the reliability of the MMC. As a matter of fact, reliability is the probability that a system can properly function under a particular loading conditions and within a specific period of time [23]. Therefore, accordingly, attention can be paid to three research directions in order to improve the reliability/availability of the MMC. Firstly, enhancing the physical strength of components or choosing proper components can prolong the lifetime of converter given specific loading conditions. Secondly, relieving the stresses that components are subject to can extend the serving time of the system as well considering the same hardware implementation. Once the components and their stresses are determined, the third option is to conduct preventive maintenances that can push the potential of all major components in the system close to their limits.

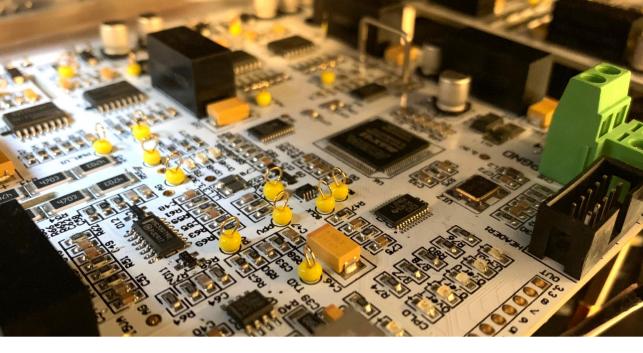

In this regard, this Ph.D. project will focus on three major research topics to achieve the above objectives. The first topic is an SM based mission profile emulator of the MMC. It provides an experimental platform for the two Ph.D. research activities. Meanwhile, by exploring practical electro-thermal stresses that major components are exposed to with a down-scaled laboratory prototype, the testing scheme is able to assist a proper selection of components in the design phase of the MMC. The second part of the Ph.D. project is reliability-oriented control strategies, which are able to actively improve the reliability of the MMC system in operation from a control perspective. 1.1. Background and Motivation

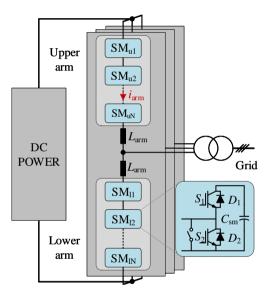

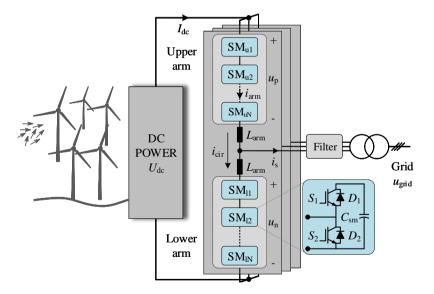

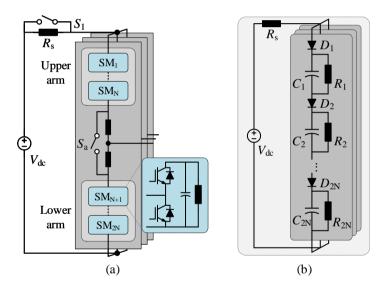

Fig. 1.2: A typical three-phase modular multilevel converter. Source:[J4]

By regulating the current, voltage, switching frequency, modulation and so on, thermal stresses of major components can be reduced or balanced to prolong the reliability and availability of the system as a whole. The last topic is condition monitoring (CM). By evaluating the health status of components to take preventive actions prior to the occurrence of failures, condition-based maintenance can be achieved instead of routine-based schedule to replace aged SMs. Thus, less repair time, lower maintenance cost and longer reliable operational time can be achieved. More detailed explanation of the three research topics are given in the following.

At the beginning of this Ph.D. project, a mission profile emulator which aims to provide an experimental platform for both Ph.D. project research activities will be explored. As we all know, for power electronic converters, mission profile is a combination of stresses that a converter is subject to during its service life [24]. This might involve electrical stresses like current and voltage, internal thermal stresses like junction temperatures [25], and environmental factors like ambient temperature and wind speed for wind power generation applications [24, 26]. Different mission profiles might contribute to different loading conditions and stresses of the components in the system and finally different reliability performance of the converter. Therefore, mission profiles have to be taken into account when conducting the reliability research of a power electronic converter. In this regard, a hardware platform that is capable of emulating practical operation conditions of a converter is very important for experimental validations to mission profile-related reliability research. When it comes to the MMC specifically, an MMC mission profile emulator instead of a three-phase MMC is recommended for experimental validations since the MMC typically operates under high power and high voltage conditions (e.g., several hundreds of Megawatts power level and several hundreds of kilovolts DC bus voltage level [27]). A large testing facility, which is costly and time-consuming to build, is needed if the whole MMC is tested with full power [28]. The modular structure enables that the testing of the MMC can be based on one or a small number of SMs [29] compared with conventional converters, which are typically based on the whole converter, a phase leg or a valve [30]. In other words, the large power requirement in the conventional converter testing is not required for the MMC any more. Thus, an MMC mission profile emulator can facilitate the experimental validation of the reliability research being conducted in the two Ph.D. projects.

Regarding the second research topic, the reliability-oriented control focuses on power modules in the MMC only. For power modules, bond wire lift-off, solder joint fatigue and bond wire heel cracking are recognized as major failure mechanisms and are affected by a variety of stresses, such as voltage, temperature, vibration, humidity, cosmic radiation etc. [31]. Among them, thermal cycling (e.g., temperature swing) has been revealed as one of the most critical failure causes [32]. It is driven by the mismatch of coefficients of thermal expansion between different materials (e.g., between Aluminum bond wires and Silicon chips [33]). Physical disconnection between layers with different materials leads to the wear-out of power devices after a certain number of thermal cycles. When it comes to power modules in the MMC, especially in applications like renewable energy generation (e.g., offshore wind power generation) and motor drives, complicated and variable operation/environmental conditions (i.e., mission profiles) of the converter can directly change the loading of power devices [18]. Severe variable thermal stresses involved in this process can quickly cause the wear-out of the power devices. Therefore, in order to extend the serving time of the power modules, one straightforward and effective way is to reduce the thermal stresses that components are subject to. According to a project called LEISIT conducted in the 1990s, both the reduction of the junction temperature swing amplitude and average junction temperature can extend the life span of a power module, in which the reduction of temperature variation is more effective [32]. This relationship between temperature and lifetime offers an opportunity to enhance the reliability of the converter through reliability-oriented control methods. The above objective can be achieved by re-distributing power losses and further regulating the junction temperature of the power module through applying different strategies like modulations [34], manipulating switching frequency [35], reactive power control [36], circulating current control [37] etc in conventional power converters. Since limited research on the

reliability-oriented control is conducted for the MMC, similar ideas will be part of the research focus of this Ph.D. project.

As an alternative, condition monitoring (CM) can also increase the availability of power electronic converters by scheduling preventive maintenances with less operational cost and longer reliable operational time. Condition monitoring is a process of collecting health status data of a physical system [38]. Preventive maintenance of the monitored system can be scheduled to avoid the occurrence of catastrophic failures once the threshold of particular monitored parameters is reached. It can be seen that two major steps are involved in the process of the CM, namely identifying degradation indicators of failures and detecting physical states of them [22]. For power modules, various device parameters have been identified as the degradation precursor, such as on-state voltage [39], on-state resistance [40], switching transition [41], threshold gate voltage [42, 43], thermal resistance [44], short-circuit current [45], case temperature [46] etc. Nevertheless, the challenge lies in the detection of the above signals. Extra measurement circuits and sensors (e.g., voltage, current or thermal sensors) are usually required in the hardware implementation. These methods might be applicable to conventional two-level converters with a limited number of components to be monitored. However, when it comes to MMC-based applications typically with a large number of SMs, condition monitoring may not be a feasible research direction to go due to: 1) the majority of possible methods for power module condition monitoring need calibrations, hardware sensors, or invasive components as revealed from the above literatures; 2) the increased complexity and the failure of additional sensors and circuits may have impact on the operation of the MMC system; 3) wear-out issue of power modules can be addressed by properly sizing and control based on existing extensive studies. Therefore, this Ph.D. thesis will not focus on the condition monitoring of power modules but limit its scope to the condition monitoring of another major components, namely SM capacitors which account for 50% and 80% of the total volume and weight of an SM [48].

Due to features like high voltage rating, self-healing and excellent ripple current performance, metalized polypropylene film (MPPF) capacitors are typically applied in the MMCs [49]. Its dominant failure mechanisms include moisture, corrosion, and dielectric loss [50]. They will lead to the the wear-out of MPPF capacitors with time. However, there are still lack of capacitor lifetime models that distinguish different failure mechanisms due to electrical, thermal, and humidity aspect stresses, which make the lifetime prediction results in the design phase a relatively high-degree of uncertainty. Condition monitoring of SM capacitors are thus recommended during the operation of MMCs to compensate the shortcomings of lifetime prediction. The reduction of capacitance and increase of equivalent series resistance (ESR) are two typical characterization involved in the process of degradation [51]. The main principles for the estimation of capacitance and ESR always involve the measurement of voltage and current of the capacitor as summarized in [21]. For MMCs, SM capacitor voltage sensors are typically required in the system for capacitor voltage balancing control and can be used to measure the capacitor voltage. It is also possible to calculate the SM capacitor current from the arm current measured by a current sensor and switching signals. The key lies in how to make full use of these signals to estimate the capacitance or ESR easily and accurately.

In summary, based on the above discussions, this Ph.D. project will focus on the MMC mission profile emulator at the beginning, and then will explore the possibilities of reliability-oriented control strategies for power modules and condition monitoring strategies for SM capacitors in the MMC.

#### 1.1.1 MMC Mission Profile Emulator

Among plenty of components in the MMC system, power devices are regarded as one of the most reliability-critical parts [53]. It has been known that thermal stresses (e.g., junction temperature variation and mean junction temperature) have a great impact on the reliability of power devices [54]. Thus, it is of great necessity to carry out the reliability-related testings in the laboratory and in practical applications. In order to see the electro-thermal stress that power semiconductors are subject to, a mission profile emulator is proposed in this project.

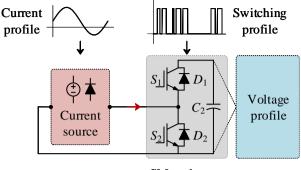

However, the power rating of MMC can rate at Megawatt level. The high voltage and high current operation condition challenges the design and implementation of the testing setup. In addition, it is also significant to maintain key reliability features of SMs as the one in practice, especially the junction temperature of power devices [55, 56]. One straightforward way to meet the above demands is to conduct the testing based on a mission profile emulator, in which the current going through the devices, the switching pattern and the capacitor voltages (blocking voltage of the IGBTs) [57] of an SM can be mimicked. Specifically, the following requirements or mission profiles as shown in Fig. 1.3 are supposed to be mimicked:

- **Current profile**: The arm current of the MMC should be emulated and it is supposed to be applicable to the arm current with DC bias and low harmonic components [58].

- **Switching profile**: Should be able to apply switching profiles with a wide range of switching frequencies (e.g., from kHz to several hundreds Hz or even lower [59]).

- Voltage profile: Voltage profile refers to the SM capacitor voltage, which is the blocking voltage of power devices. It should be the same as the SM in practice to emulate the switching losses of devices.

1.1. Background and Motivation

SM under test

Fig. 1.3: Concept of one SM based testing scheme.

In addition, the current source in Fig. 1.3 is generally achieved by an DC/AC converter, in which a DC power supply is typically required [60]. In order to extend the application scope of the emulator and to facilitate the testing, two requirements in terms of the power supply used in the current source also need to be carefully considered.

- **Reduced voltage rating**: High voltage rating of SMs poses a great challenge to the power supply and the power devices in the current source with much higher voltage ratings. Series connection of power devices is required when this concern is not properly handled and it is not preferable in practical applications.

- **Reduced power rating**: SMs might rate at Megawatt level in practice and the same power rating is required for the power supply if no proper testing topology is used. Thus, power rating of the DC power supply is supposed to be well coped with.

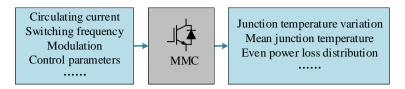

#### 1.1.2 Reliability-Oriented Control of MMCs

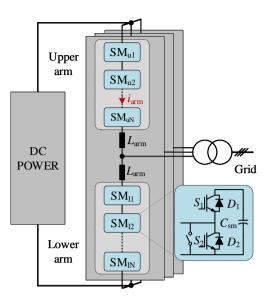

In order to improve the reliability performance of the whole MMC system, most existing methods focus on redundancy [61] and periodic preventive maintenance [62]. In addition, the reliability can also be improved from a control point of view. By changing the behavior of components, the thermal stress can be relieved but with no or minor impact on the control performance of the system. Fig. 1.4 lists the possible control variables affecting the thermal stresses of the MMC components.

Reference [63] evaluated the influence of a series of parameters (e.g., circulating current with first- and second-order harmonics and DC offset voltage) on the power loss redistribution among devices and phases. Conclusions show that negligible amounts of total power loss difference in the devices

Fig. 1.4: Possible parameters for reliability improvement of MMCs.

can be obtained and its inability of regulating the junction temperature. A thermal balancing control embedded in the capacitor voltage balancing algorithm is proposed in [64]. By introducing one temperature loop, simulation results present that the thermal stresses among devices can be balanced. However, the challenge lies in the junction temperature estimation, which can not be accurately implemented in practice [65]. Additionally, the capacitor voltage is also utilized to achieve the sub-module level thermal balancing control, which might be caused by SM capacitor parameter mismatch [66] and low switching frequency of the MMC. By adjusting the average SM capacitor voltage, the switching losses of SMs can be redistributed and the junction temperature of different devices can be regulated [67]. Even though the aforementioned methods contribute to the reduction of thermal stress and reliability improvement of the power devices in the MMC, further research still need to be conducted.

#### 1.1.3 Capacitor Condition Monitoring of MMCs

Besides reliability-oriented control, condition monitoring is another tool to increase the availability of power converters. According to field operation experience, unpredicted failures of key components can cause a shutdown of the whole system. If immediate access to the converter cannot be achieved, such as offshore wind farm applications [68], it might lead to considerable financial loss [38]. Nevertheless, by means of monitoring the health status of key components, the possibility of catastrophic failures can be reduced by identifying the abnormal behavior and severe degradation of key components in advance. Then preventive maintenances can be scheduled to further reduce the operation and maintenance cost [69].

As mentioned in Section 1.1, the condition monitoring strategy will only focus on the SM capacitors in the MMC system. For conventional two-level converters, CM methods can generally be divided into two categories as summarized in [21], namely hardware based method (e.g., voltage or current sensor) and advanced algorithm based method. However, when it comes to MMCs, the large amount of SMs (e.g., can be hundreds in HVDC applications) makes it not preferable to integrate extra measurement circuits into each SM because of the considerably increased cost and reliability concern. Therefore, existing CM methods for MMCs are mainly achieved without additional hardwares. The SM capacitor voltage sensors and the arm current sensors have to be made full use of.

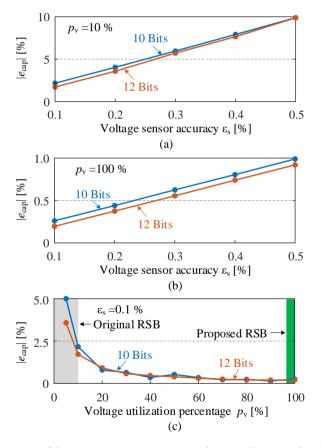

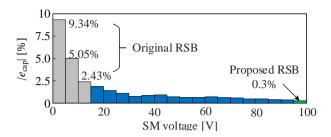

Several state-of-the-art research on the CM of capacitors in the MMC are proposed. By taking full advantage of the bleeding resistor inside SMs, reference [70] proposes an CM method based on the RC discharging curve. This method is easy to implement with light computational load. However, the impact of auxiliary power on the capacitance estimation accuracy is not evaluated since SMs in the MMC normally are self-powered by their local capacitors. Additionally, several approaches based on Kalman filter [71], band-pass filter [72], and recursive least square algorithm [73] are proposed for MMCbased applications. Similar to the reference SM based method in [74], all of them estimate the SM capacitance from the SM voltage ripple. However, the major limitation of these methods is the monitoring accuracy. In general, the SM voltage ripple is limited within 10% of its rated voltage. It means that only one tenth of the voltage sensor range can be fully utilized for the CM purpose. Considering 5% capacitance drop of MPPF capacitors at the end-of-life, the detectable voltage change used for CM is only 0.5% of the voltage sensor range. Given the commonly-used voltage sensor accuracies (e.g., 0.1% or 0.3%) in the market, the aforementioned methods might fail to work. Moreover, the voltage ripple amplitude decreases with the drop of the power loading of the MMC [75], and the monitoring accuracy can be further impaired.

Therefore, in order to address the aforementioned limitations, cost-effective, computational-light condition monitoring methods targeting MPPF capacitors with small capacitance drop are explored in this Ph.D. project. Special attention will be paid to the accuracy enhancement of the CM method.

#### 1.2 **Project Objectives and Limitations**

#### 1.2.1 Research Questions

Based on the above introduction and research motivations regarding various reliability issues of the MMC, the overall question of this Ph.D. project is: *How to improve the reliability performance of modular multilevel converters by control and condition monitoring?* More specifically, the following three research subquestions are to be explored:

- How to emulate the operation conditions of MMCs with a minimum viable down-scaled laboratory prototype used for model validation and testing?

- How to improve the reliability performance of MMCs from a control point of view?

• How to conduct no additional hardware-based, cost-effective and computational light condition monitoring for MMCs?

#### 1.2.2 Research Objectives

Once the above research questions are identified, more detailed research objectives are summarized below,

- Mission profile emulator for MMCs

- In order to provide an experimental platform for both Ph.D. project research activities and to facilitate the reliability-related testings of SMs in practice, this Ph.D. project will explore an SM-based mission profile emulator by taking full advantage of the modular structure of the MMC. It should be able to mimic the key electro-thermal features of a practical SM, such as current profiles and switching profiles. Moreover, solutions to reduce the power rating and voltage rating of the power supply used in current source will be explored in order to facilitate the hardware implementation of the mission profile emulator.

- Reliability-oriented control of MMCs

By taking full advantages of the control freedoms mentioned in Fig. 1.4, this Ph.D. project will explore reliability-oriented control strategies to mitigate the thermal stresses that power modules are subject to. With the knowledge of major stresses, the reliability of the MMC system might be improved by, such as reducing the junction temperature swings, evenly re-distributing the power losses among SMs and so on. At the meantime, the overall system performance, such as efficiency, should better remain unchanged and not deteriorated.

- Condition monitoring for SM capacitors in MMCs

- For the purpose of preventive maintenance with less operation cost and longer reliable operation time, many condition monitoring strategies are proposed for DC-link capacitors in conventional two-level converters. However, it is a challenge to apply them directly to the MMC with many SMs in terms of the involved cost, computational load and reliability issues. In this regard, easy-implemented, computational-light and cost-effective condition monitoring methods will be explored in this Ph.D. project. Meanwhile, considering the small capacitance drop of commonly used film capacitors in the MMC, special attention will be paid to enhancing the monitoring accuracy. Enhancing the richness of degradation precursors and even the way to collect them will contribute to better condition monitoring results and give a bigger picture of the health status of the monitored capacitors from different perspectives.

#### 1.2.3 Project Limitations

The Ph.D. project focuses on the reliability improvement strategies for the MMC, especially from a control and condition monitoring point of view. However, several limitations exist in this project:

- The mission profile emulator considers only the testing of power semiconductors. The electro-thermal behavior and reliability of SM capacitors, which are also one major component prone to failure in the MMC, are not evaluated.

- Due to the existence of DC component in the arm current, thermal stresses of power devices inside one SM are inherently imbalanced. The proposed power loss balancing control focuses only on the sub-module level imbalance instead of the component level.

- Special operation modes are required for the proposed condition monitoring strategies for SM capacitors in this Ph.D. project. CM methods being conducted without special operation modes would be better.

#### **1.3** Thesis Outline

The outcomes of this Ph.D. project are documented by the Ph.D. thesis, which is composed of two main parts, namely Part I-report with six main chapters and Part II-related publications.

Chapter 1 is the introduction of this project with the research background and motivation presented. The project objectives and its limitations are discussed as well. Chapter 2 proposes an SM based mission profile emulator to conduct the testing of the power semiconductors in the MMC. Experimental validation is demonstrated. Chapter 3 and Chapter 4 focus on the reliability improvement strategies from a control perspective. The power loss balancing control is presented in Chapter 3 followed by the adaptive frequency control of MMCs in Chapter 4. Chapter 5 introduces two capacitor condition monitoring strategies for MMCs. Their basic operation principles, flowcharts and practical considerations of implementation and experimental validations are provided. Chapter 6 concludes the project with future research perspectives.

### 1.4 List of Publications

The publications from this Ph.D. project and their relevance to the chapters are shown in Table. 1.1.

Journal Papers

#### Chapter 1. Introduction

| Chapter No. | <b>Relevant Publications</b> |  |  |  |

|-------------|------------------------------|--|--|--|

| 1           | -                            |  |  |  |

| 2           | J1, C5                       |  |  |  |

| 3           | C1, C2, C3                   |  |  |  |

| 4           | C4                           |  |  |  |

| 5           | J3, J4                       |  |  |  |

| 6           | -                            |  |  |  |

Table 1.1: Related publications for each chapter published in the thesis.

- J1. Z. Wang, H. Wang, Y. Zhang, and F. Blaabjerg, "A viable mission profile emulator for power modules in modular multilevel converters" *IEEE Trans. Power Electron.*, vol. 34, no. 12, pp. 11580-11593, Dec. 2019.

- J2. Z. Wang, H. Wang, Y. Zhang, and F. Blaabjerg, "A multi-port thermal coupling model for multi-chip power modules suitable for circuit simulators" *Microelectronics Reliability*, vol. 88-90, no. 5, pp. 519-523, Sep. 2018.

- J3. Z. Wang, Y. Zhang, H. Wang, and F. Blaabjerg, "Capacitor condition monitoring based on the DC-side start-up of modular multilevel converters" *IEEE Trans. Power Electron.*, under review, 2019.

- J4. Z. Wang, Y. Zhang, H. Wang, and F. Blaabjerg, "A reference sub-module based capacitor condition monitoring method for modular multilevel converters" *IEEE Trans. Power Electron.*, under review, 2019.

#### **Conference** Papers

- C1. Z. Wang, H. Wang, Y. Zhang, and F. Blaabjerg, "An analytical essential switching loss estimation method for modular multilevel converters with nearest level modulation" in *Proc. IEEE IECON*, pp. 762-767, Oct. 2017.

- C2. Z. Wang, H. Wang, Y. Zhang, and F. Blaabjerg, "Submodule level power loss balancing control for modular multilevel converters" in *Proc. IEEE ECCE*, pp. 5731-5736, Sep. 2018.

- C3. Z. Wang, H. Wang, Y. Zhang, and F. Blaabjerg, "Balanced conduction loss distribution among SMs in modular multilevel converters" in *Proc. IEEE ECCE Asia*, pp. 3123-3128, Oct. 2018.

- C4. Z. Wang, H. Wang, Y. Zhang, and F. Blaabjerg, "Mission profile based adaptive carrier frequency control for modular multilevel converters for medium voltage applications" in *Proc. IEEE ECCE Asia*, pp. 1848-1853, Aug. 2019.

- C5. Z. Wang, H. Wang, Y. Zhang, and F. Blaabjerg, "A minimum viable mission profile emulator for IGBT modules in modular multilevel converters" in *Proc. IEEE APEC*, pp. 313-318, Mar. 2019.

## Chapter 2

## Mission Profile Emulator for Power Modules in MMCs

In order to provide an experimental platform for the two planned Ph.D. research activities and to facilitate the reliability-related testings of a practical sub-module (SM) in the laboratory, this chapter presents a mission profile emulator for power modules in modular multilevel converters (MMCs) to mimic their thermal stresses and to explore the feasibility for reliability testing as well as thermal model validation. The emulator is able to apply real and practical current profiles and switching profiles to the SM under test. Meanwhile, significantly reduced voltage and power requirements for the dc power supply used in the current source can extend the application scope of this testing setup in terms of the testing of higher voltage rated power devices.

#### 2.1 Background

Power devices are regarded as one of the components prone to failure in power electronic systems as reported in an industry survey [76]. As the key components, the massive application of power modules might introduce reliability concerns to the operation of MMC systems. As electro-thermal stress is an important mechanism resulting in fatigue and failure for power semiconductors [32], the reliability testing of the MMC, especially from a electro-thermal point of view, is pretty important for both laboratory validation and testing prior to field operations of the MMC.

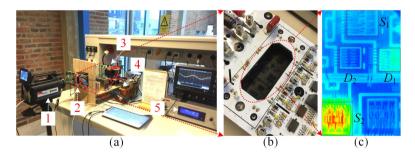

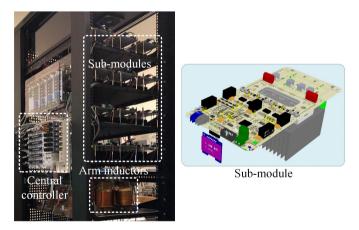

In order to reduce the required resources [29], SM based testing is greatly recommended given that all SMs applied are the same in hardware due to the modular structure of the MMC. To meet the requirements mentioned above, a viable mission profile emulator based on a full-bridge converter and an auxiliary SM is proposed in this Ph.D. project. Its topology and modulation algorithm are presented. For comparison, several existing SM based testing solutions are introduced. In addition, issues regarding the practical implementation of the mission profile emulator, such as control and hardware parameter selection, the carrier frequency selection for the voltage stabilizer, and the impact of current ripple on the power loss, are discussed. Finally, experimental validations are given.

#### 2.2 Existing SM Based Testing Solutions

The state-of-the-art SM based solutions are introduced in this section to illustrate the challenge of SM testing. Their major advantages and limitations are summarized in Table 2.1.

**Table 2.1:** Comparison between the proposed mission profile emulator and other testing schemes when the rated SM voltage is 2 kV. Source: [J1]

| Т                       | esting capabilities                                 | Proposed    | [77]        | [60]        | [78]                            | [29]                            |

|-------------------------|-----------------------------------------------------|-------------|-------------|-------------|---------------------------------|---------------------------------|

| DC power supply voltage |                                                     | Wide range  | 545 V       | $> 2 \ kV$  | = 2 kV                          | —                               |

| Switching profile       | High switching frequency<br>Low switching frequency | $\sqrt[]{}$ |             |             | $\stackrel{\checkmark}{\times}$ | $\stackrel{\checkmark}{\times}$ |

| Current<br>profile      | DC current<br>Second-order current                  | $\sqrt[]{}$ | $\sqrt[]{}$ | $\sqrt[]{}$ |                                 | ×<br>×                          |

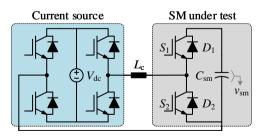

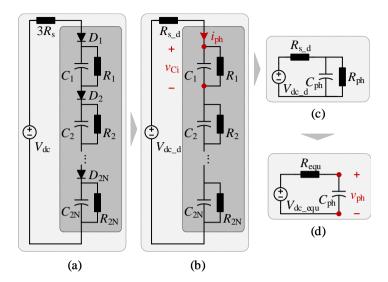

Fig. 2.1: Dual SM based resonant testing scheme.

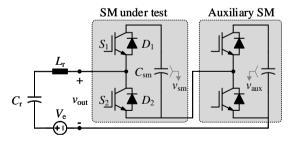

• Dual SM based resonant testing scheme [29]

Resonance between the inductor  $L_r$  and capacitor  $C_r$  generates a sinusoidal current as shown in Fig. 2.1. It can be used as the arm current to stress the SM under test. By switching the auxiliary SM in opposition with the SM under test, DC component of the two SM voltages (i.e.,  $v_{sm}$  and  $v_{aux}$ ) are canceled and only doubled AC voltages exist in the

2.2. Existing SM Based Testing Solutions

output voltage  $v_{out}$ . A smaller inductor  $L_r$  can thus be applied in this setup to fulfill the same arm current ripple requirement of the MMC. However, the resonant circuit can only generate sinusoidal current and is not able to mimic the DC component in the arm current of MMCs.

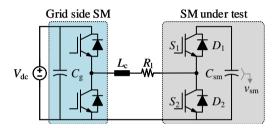

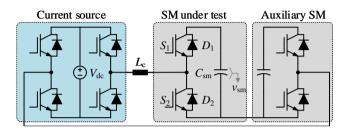

• Dual half-bridge SM based testing scheme [78]

As shown in Fig. 2.2, one half-bridge SM is used to mimic the grid side voltage of the MMC system. The SM under test regulates the current going through the inductor  $L_c$ . However, the setup focuses more on the electrical characteristics of the MMC instead of the thermal performance. It is not applicable to low switching frequency mission profiles (e.g., nearest level modulation (NLM)), where undesirable harmonics might be introduced into the arm current.

Fig. 2.2: Dual half-bridge SM based testing scheme.

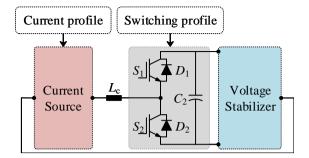

• Full-bridge current source based testing scheme [60]

A full-bridge converter is employed as the current source as shown in Fig. 2.3. It is utilized to track the current profile, where both dc current and low switching profiles can be applied. Nevertheless, the voltage  $V_{dc}$  of the DC power supply has to be higher than the voltage  $v_{sm}$  of the SM under test, which restrains its application, especially for high-voltage power semiconductors.

Fig. 2.3: Full-bridge current source based testing scheme.

• Full-bridge current source dual SM based testing scheme [77]

Chapter 2. Mission Profile Emulator for Power Modules in MMCs

Reference [77] takes advantage of a reverse-connected auxiliary SM as shown in Fig. 2.4. By proper control, the power supply voltage  $V_{dc}$  can be as low as one fifth of the voltage  $v_{sm}$  of SM, and the test capability is correspondingly improved. SMs with five times higher blocking voltage can be tested in this setup. However, it should be noted that the power supply voltage and the voltage of the SM under test are still coupled with each other. The voltage  $V_{dc}$  of the power supply can not be selected independently and should be high enough.

Fig. 2.4: Full-bridge current source dual SM based testing scheme.

#### 2.3 Topology and Control Scheme

Topology, working principle and control strategy of the proposed SM based mission profile emulator are studied in this section. Several design guidelines regarding the control and hardware parameter selection are discussed. Besides, how the current ripple and voltage ripple affect the conduction losses and switching losses of the power devices is investigated. A case study is demonstrated to validate the above analysis.

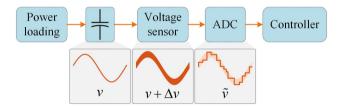

#### 2.3.1 Topology of Mission Profile Emulator

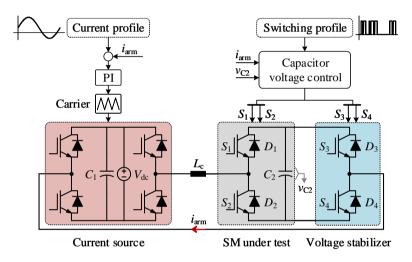

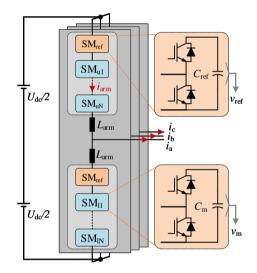

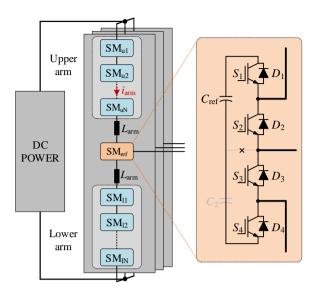

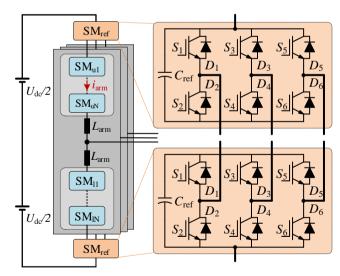

The proposed mission profile emulator consists of four major parts: namely current source, coupling inductor  $L_c$ , SM under test, and a voltage stabilizer as shown in Fig. 2.5.

The detailed circuit diagram is shown in Fig. 2.6. The specific function of the four parts are summarized as given below:

• **Current source**: The current source aims to track the current profile of the SM under test in order to keep the same stress as the SM in a practical MMC. It should be able to mimic a DC-bias, fundamental, and second-order harmonics of the arm current. Proportional integral (PI) controller or proportional resonant (PR) controller can be applied to the current control [79]. 2.3. Topology and Control Scheme

Fig. 2.5: Simplified circuit diagram of the proposed mission profile emulator. Source: [J1]

**Fig. 2.6:** Detailed circuit diagram of the mission profile emulator ( $i_{arm}$  is the arm current,  $v_{C2}$  is the voltage of capacitor  $C_2$ ,  $L_c$  is the coupling inductor and  $V_{dc}$  is the voltage of the DC power supply). Source: [J1]

- **Coupling inductor** *L*<sub>c</sub>: Coupling inductor ensures reactive power flow within the setup to greatly reduce the power rating requirement of the DC power supply. The only active power dissipation in this emulator is the power loss of the system.

- **SM under test**: SM under test is controlled by the switching profile, which cannot be interfered by other controls with extra switching actions.

- Voltage stabilizer: By properly regulating the two auxiliary power devices  $S_3$  and  $S_4$ , the voltage stabilizer is able to keep the voltage  $v_{C2}$  of capacitor  $C_2$  stable at the average voltage of the SM under test. Therefore, almost the same switching loss behavior as in practice can be achieved for SM under test. Note that capacitor  $C_2$  is different from

#### Chapter 2. Mission Profile Emulator for Power Modules in MMCs

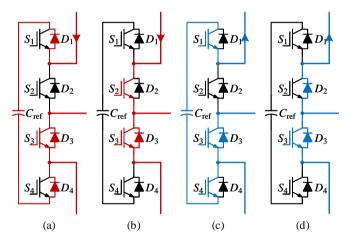

the capacitor applied in the practical SM. The capacitor  $C_2$  serves to maintain the blocking voltage of the power devices only to obtain the similar switching loss behavior as the power devices in real SMs. In addition,  $S_3$  and  $S_1$  share the same gate signal obtained from the switching profile. They are complementary to the gate signals of  $S_2$  and  $S_4$ . Fig. 2.7 shows the ideal current paths in the SM under test.

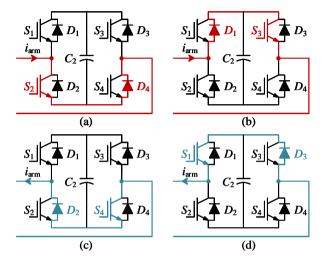

**Fig. 2.7:** Ideal current paths in the SM under test and the voltage stabilizer. (a) Bypass state of SM with a positive current; (b) Insert state of SM with a positive current; (c) Bypass state of SM with a negative current; (d) Insert state of SM with a negative current. Source: [J1]

As it can be seen, the capacitor  $C_2$  is not inserted into the main current path regardless of the switching profile and the current profile. This feature offers two major advantages:

- Since there is always a current path inside the SM under test without passing through the capacitor  $C_2$ , the current profile is thus decoupled with the switching profile. Different practical switching profiles can thus be tested based on the proposed mission profile emulator.

- DC power supply voltage  $V_{dc}$  is decoupled with the high voltage across the capacitor  $C_2$ . It means that the voltage of DC power supply can be as low as possible theoretically under the condition that the coupling inductor  $L_c$  is properly designed accordingly. The reduced voltage requirement of the power supply greatly facilitate the test of SMs rated at high voltage.

## 2.3.2 Control of Mission Profile Emulator

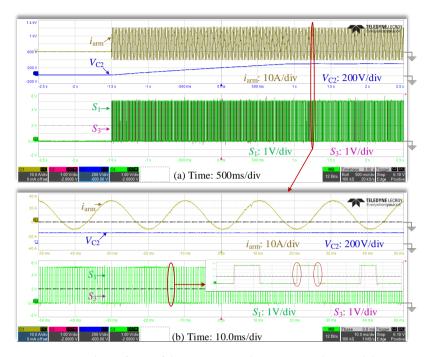

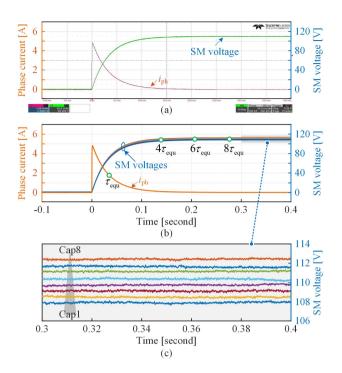

Two main control targets are involved in this part, namely the arm current control and the capacitor voltage control as shown in Fig. 2.6. The current profile can be achieved by a PI controller or a PR controller and is not further discussed in this section. As for the capacitor voltage control, it is essential to the switching loss emulation of SM under test. The voltage of the capacitor  $C_2$  grows in practice due to turn-on delays, which are necessary to avoid short circuit faults between the IGBT devices in the same half-bridge leg. Fig. 2.8 shows how the turn-on delays can get  $C_2$  charged by the non-ideal current paths. Consequently, the capacitor voltage  $v_{C2}$  might deviate from its rated value, especially when a high frequency switching profile is applied. Thus, a capacitor voltage controller is necessary. As the SM under test is strictly regulated by the switching profile, thus the voltage stabilizer has to take the responsibility. Two cases are taken into account regarding different switching mission profiles.

Fig. 2.8: Non-ideal current paths during the turn-on delays. Source: [J1]

## • High Switching Frequency Mission Profile

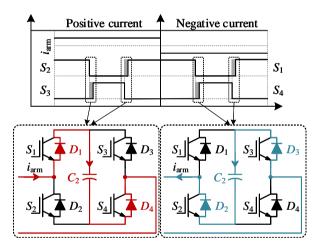

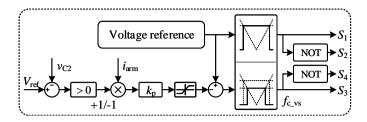

Regarding high switching frequency applications like mission profiles from Phase Shifted Carrier (PSC) modulation, the capacitor voltage control can be achieved by introducing an dynamic adjustment to the original voltage reference as shown in Fig. 2.9. By doing so, the same actual switching frequency can be applied to the power devices in SM under test and the two auxiliary IGBTs with similar switching loss.

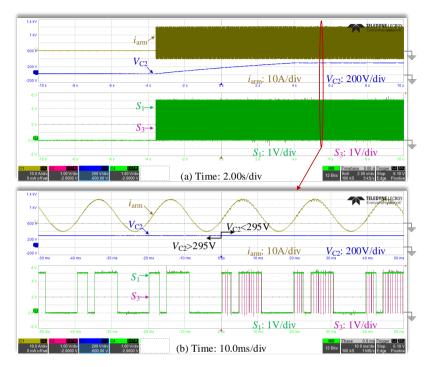

Low Switching Frequency Mission Profile

**Fig. 2.9:** Capacitor voltage control for high switching frequency mission profiles ( $V_{ref}$  is the voltage reference of the capacitor voltage control,  $f_{c_vs}$  is the carrier frequency used in the voltage stabilizer, and  $k_p$  is the control gain). Source: [J1]

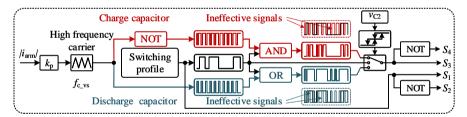

Compared with the control method in Fig. 2.9, less switching transitions can be utilized to control the SM capacitor voltage when the switching profile has low equivalent switching frequency. Thus, the method shown in Fig. 2.10 is proposed. By combining the original switching profile with additional high switching frequency signals, the gate signals for  $S_3$  and  $S_4$  can be obtained. Moreover, it can be seen from Fig. 2.10 that, in some cases, the gate signals of  $S_3$  and  $S_4$  are the same as the original switching profile even after the logic operation, Thus, these additional switching signals are ineffective and are not able to change the capacitor voltage  $v_{C2}$ .

Fig. 2.10: Capacitor voltage control for low switching frequency mission profiles. Source: [J1]

## 2.3.3 Control and Hardware Parameter Selection

In order to meet testing requirements, three major types of components used in the mission profile emulator, namely the power modules, coupling inductor  $L_{\rm C}$  and power supply  $V_{\rm dc}$  needs to be sized accordingly.

## • Control Parameter

As it can be seen in Fig. 2.9 and Fig. 2.10, the control gain  $k_p$  that needs to be well tuned since it determines the current ripple to a great extent. First of all, the current ripple is given as

$$\Delta I = \frac{V_{C2}}{L_c} T_a = k_a |i_{arm}|, \qquad (2.1)$$

#### 2.3. Topology and Control Scheme

where  $V_{C2}$  refers to the capacitor voltage of  $C_2$ ;  $L_c$  refers to the coupling inductance;  $k_a$  is the constant current ripple ratio, which limits the current error caused by the proposed capacitor voltage control;  $T_a$  defines the duration of the additional switching action. The duty ratio introduced by  $T_a$  is equal to  $k_p |i_{arm}|$

$$T_{\rm a}f_{\rm c\_vs} = \frac{k_{\rm a} |i_{\rm arm}| L_{\rm c}f_{\rm c\_vs}}{V_{\rm C2}} = k_{\rm p} |i_{\rm arm}|, \qquad (2.2)$$

where  $f_{c_vs}$  refers to the carrier frequency used in the voltage stabilizer and  $k_p$  is defined as the proportional gain to limit the current ripple

$$k_{\rm p} = \frac{k_{\rm a} L_{\rm c} f_{\rm c\_vs}}{V_{\rm C2}}.$$

(2.3)

By using (2.3), the current error caused by the capacitor voltage control can be limited within  $k_a \times 100\%$  of the actual current.

#### IGBT Modules

It is recommended that all IGBT modules in the current source and the voltage stabilizer are supposed to have higher voltage and current ratings than that of the SM under test. A series of potential SMs with different ratings can be tested by the mission profile emulator. Meanwhile, longer lifetime than the SM under test can be expected for the current source and voltage stabilizer without frequent hardware modification. Moreover, independent cooling system are supposed to be used to avoid thermal coupling with the SM under test.

## • Coupling Inductor L<sub>c</sub> and DC Power Supply

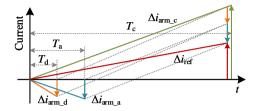

The coupling inductor  $L_c$  and the power supply interacts with each other. The maximum inductance  $L_{c_{max}}$  is determined by the dynamic current tracking performance. The current response should be fast enough to mimic the current profile. By analyzing all possible current variations caused by different reasons as shown in Fig. 2.11, the following relationship holds

$$\begin{aligned}

\Delta i_{arm_c} &= \frac{V_{dc}}{L_c} T_{c_vs} \\

\Delta i_{ref} &= \frac{di_{arm}}{dt} T_{c_vs} \\

\Delta i_{arm_a} &= k_a i_{arm} \\

\Delta i_{arm_d} &= \frac{V_{C2}}{L_c} T_d \\

\Delta i_{arm_c} &\geq \Delta i_{ref} + \Delta i_{arm_a} + \Delta i_{arm_d},

\end{aligned}$$

(2.4)

where  $\Delta i_{arm_c}$ ,  $\Delta i_{ref}$ ,  $\Delta i_{arm_a}$ , and  $\Delta i_{arm_d}$  refer to the current changes caused by the power supply, current reference, capacitor voltage control, and turn-on

#### Chapter 2. Mission Profile Emulator for Power Modules in MMCs

delay, respectively;  $V_{dc}$  refers to the voltage of the DC power supply;  $T_{c_vs}$  is the period of the carrier in the current source;  $T_d$  defines the duration of the turn-on delay.

**Fig. 2.11:** Current changes caused by the DC power supply ( $\Delta i_{arm_c}$ ), current reference ( $\Delta i_{ref}$ ), turn-on delay ( $\Delta i_{arm_d}$ ), and capacitor voltage control ( $\Delta i_{arm_a}$ ) in one carrier period. ( $T_d$  is the period of the turn-on delay,  $T_a$  is the period of the additional switching actions for capacitor voltage control, and  $T_c$  is the duration of one carrier period.) Source: [J1]

The maximum allowed inductance is

$$L_{c_max} = \frac{V_{dc}T_{c_vs} - V_{C2}T_d}{\left(k_a I_0 + \sqrt{\omega^2 T_{c_vs}^2 + k_a^2}I_1 + \sqrt{4\omega^2 T_{c_vs}^2 + k_a^2}I_2\right)}.$$

(2.5)

The requirement of an arm current ripple caused by the Pulse Width Modulation (PWM) decides the minimum inductance  $L_{c_{min}}$  as

$$L_{\rm c_min} = \frac{T_{\rm c_vs} V_{\rm dc}}{4 I_{\rm r_max}},$$

(2.6)

in which  $I_{\rm r}$  max refers to the current ripple amplitude caused by the PWM.

### Switching Profile Classification

Capacitor voltage change caused by two factors (i.e., the turn-on delay and the additional switching actions) decides the classification of the mission profile. The turn-on delays always charge the capacitor  $C_2$  by

$$\Delta v_{\text{C2}\_d\_i} = \frac{1}{C_2} \int_{t}^{t+T_d} |i_{\text{arm}}| dt \approx \frac{T_d}{C_2} |I_{\text{arm}\_i}|, \qquad (2.7)$$

where  $C_2$  is the capacitance;  $\Delta v_{C2\_d\_i}$  refers to the voltage increase caused by the *i*-th turn-on delay;  $T_d$  refers to the duration of turn-on delay;  $I_{arm\_i}$  is the current amplitude during the turn-on delay. Due to a short period of delay, constant current is assumed.

Additional switching actions introduced by the capacitor voltage control can either charge or discharge the capacitor  $C_2$  as

$$\Delta v_{\text{C2}\_a\_i} = \frac{1}{C_2} \int_{t}^{t+T_{a\_i}} |i_{\text{arm}}| dt \approx \frac{k_a L_c}{C_2 V_{\text{C2}}} |I_{\text{arm}\_i}|^2, \qquad (2.8)$$

#### 2.3. Topology and Control Scheme

where  $\Delta v_{C2\_a\_i}$  is the voltage change caused by the *i*-th additional switching action in the time interval of  $T_{a\_i}$ .

Combining (2.7) and (2.8), the capacitor voltage variation in one fundamental period is

$$\Delta V_{\text{C2\_in/de}} = \sum_{i=0}^{N_{a}} \Delta v_{\text{C2\_a\_i}} \pm \sum_{i=0}^{N_{\text{DUT}}} \Delta v_{\text{C2\_d\_i}}$$

$$\approx \frac{f_{\text{c\_vs}}}{f_{1}} \frac{k_{a} L_{\text{arm}}}{C_{2} V_{\text{C2}}} \overline{|i_{\text{arm}}|^{2}} \pm \frac{f_{\text{e\_DUT}}}{f_{1}} \frac{T_{\text{d}}}{C_{2}} \overline{|i_{\text{arm}}|},$$

(2.9)

where  $\Delta V_{\text{C2_in/de}}$  refers to the voltage change in one fundamental period;  $N_a$  is equal to  $f_{c_vvs}/f_1$ ;  $N_{\text{DUT}}$  is the number of the switching transitions of the SM under test in one fundamental period, which is equal to  $f_{e_v\text{DUT}}/f_1$  determined by the mission profile;  $f_1$  is the fundamental frequency, which is 50 Hz in this case study;  $f_{c_vvs}$  refers to the carrier frequency applied in the voltage stabilizer;  $f_{e_v\text{DUT}}$  refers to the equivalent switching frequency of the DUT;  $\overline{|i_{arm}|^2}$  and  $|i_{arm}|^2$  are the average of  $|i_{arm}|^2$  and  $|i_{arm}|$  in one fundamental period.

The time taken to obtain a certain capacitor voltage change  $\Delta V_{C2}$  is

$$T_{\rm in/de} = \frac{\Delta V_{\rm C2}}{f_1 \Delta V_{\rm C2\_in/de}},\tag{2.10}$$

When a minimum  $T_{in/de}$  is set to ensure an reasonable performance of the capacitor voltage control, the carrier frequency obtained from the above equations is the threshold to distinguish different mission profiles.

## 2.3.4 Practical Considerations

MMC has excellent current harmonic performance due to its high equivalent switching frequency [80]. Thus, the current ripple caused by the PWM might contribute to different conduction loss behavior of the power devices in the SM under test and should be evaluated. Moreover, the capacitor voltage  $v_{C2}$  is controlled to be a constant, which is different from the practical SM voltage with ripples. Therefore, the absence of voltage ripple might lead to different switching loss behavior of the power devices and is supposed to be assessed as well. Two case studies based on a full-scale MMC system and the propose mission profile emulator are discussed. Their system parameters are listed in Table 2.2.

#### Impact of Current Ripple on the Conduction Losses

By linearizing the on-state voltage of the power devices as  $V_{\text{on}} = V_{\text{on}_0} + R_{\text{on}} |i_{\text{arm}}|$  with  $V_{\text{on}_0}$  being the on-state zero-current voltage drop and  $R_{\text{on}}$

Table 2.2: Main parameters of IGBTs used in full-scale MMC and the mission profile emulator.

Source:

[J1]

| MMC system            | Full-scale       | Mission profile emulator |

|-----------------------|------------------|--------------------------|

| Power rating          | 30 MVA           | -                        |

| DC link voltage       | 50 kV            | -                        |

| SM number per arm $N$ | 20               | -                        |

| SM capacitor voltage  | 2.5 kV           | 300 V                    |

| Power module          | 5SNA_1200G450350 | F4_50R12KS4              |

| $V_{\rm on_0}$        | 1.5 V            | 1.9 V                    |

| Ron                   | 0.52 mΩ          | 31.6 mΩ                  |

Fig. 2.12: Ideal arm current waveform with DC circulating current and simplified evenlydistributed switching actions. Source: [J1]

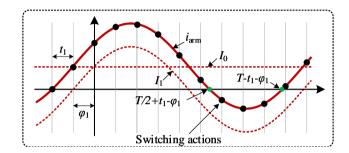

being the equivalent on-state resistance, the sum of the conduction losses of the four semiconductors can be evaluated in one fundamental period as

$$P_{\text{con\_sm}} = \frac{1}{T} \int_{-t_1 - \varphi_1}^{T/2 + t_1 - \varphi_1} V_{\text{on}} |i_{\text{arm}}| dt + \frac{1}{T} \int_{T/2 + t_1 - \varphi_1}^{T - t_1 - \varphi_1} V_{\text{on}} |i_{\text{arm}}| dt$$

$$= P(I_0, I_1) + P(I_{\text{r\_max}})$$

(2.11)

where *T* refers to the fundamental period;  $t_1$  is shown in Fig. 2.12;  $P(I_0, I_1)$  is the conduction loss independent of the current ripple, and  $P(I_{r_max})$  is the conduction loss caused by the current ripple.

The maximum conduction loss error introduced by the ripple current is

$$\frac{P(I_{r_max})}{P(I_0, I_1)} \le \frac{P_{max}(I_{r_max})}{P(I_0, I_1)} = e_{con_max},$$

(2.12)

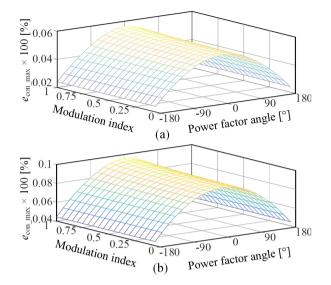

Considering the main device parameters listed in Table 2.2, the maximum conduction loss error is below 0.1% for both scenarios as shown in Fig. 2.13. Thus, the current ripple impact on the conduction loss is negligible.

## • Impact of Voltage Ripple on the Switching Losses

#### 2.3. Topology and Control Scheme

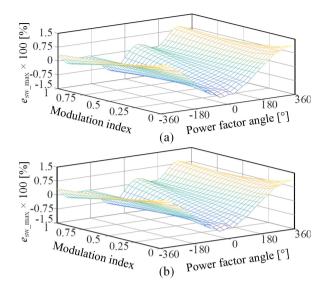

Fig. 2.13: Maximum conduction loss error introduced by the current ripple: (a) Full-scale MMC and (b) Mission profile emulator. Source: [J1]

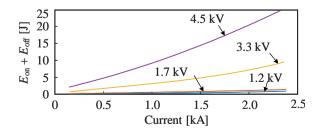

Since the blocking voltage of IGBTs is a constant voltage of  $C_2$  without including voltage ripple, its effect on the switching loss of the SM has to be assessed. The switching energy of the power devices is

$$E_{\rm sw}(i_{\rm arm}, v_{\rm sm}, T_{\rm j}) = E_{\rm sw}(i_{\rm arm}, V_{\rm ref}, T_{\rm ref})[1 + K_{\rm T}(T_{\rm j} - T_{\rm ref})]\frac{v_{\rm sm}}{V_{\rm ref}},$$

(2.13)

in which  $E_{sw}(i_{arm}, V_{ref}, T_{ref})$  is the curve-fitted switching energy obtained from the data-sheet provided information under the junction temperature  $T_{ref}$ and the blocking voltage  $V_{ref}$ ,  $v_{sm}$  refers to the actual SM capacitor voltage,  $K_T$  is a constant temperature coefficient, and  $T_j$  is the junction temperature.

Assuming an even distribution of switching actions of IGBTs in one fundamental period, the total switching loss of IGBTs and diodes ( $E_{sw_on}$ ,  $E_{sw_off}$ and  $E_{sw_rec}$ ) is calculated as  $\sum E_{sw_x}(i_{arm}, v_{sm}, T_j)$ . Thus, the switching energy error caused by omitting voltage ripple in one fundamental period is

$$e_{\rm sw} = \frac{\sum_{1}^{N_{\rm s}} \sum E_{\rm sw_x}(i_{\rm arm}, v_{\rm sm}, T_{\rm j}) v_{\rm sm_ripple}}{\sum_{1}^{N_{\rm s}} \sum E_{\rm sw_x}(i_{\rm arm}, v_{\rm sm}, T_{\rm j}) v_{\rm sm}},$$

(2.14)

where  $N_{\rm s}$  is the number of switching transitions in one fundamental period.

Figs. 2.14 show that the maximum switching loss error is within 1.5% by ignoring the SM voltage ripple (e.g., 10% in this case study). Thus, a constant

**Fig. 2.14:** Maximum switching loss error introduced by the absence of the SM voltage ripple: (a) Full-scale MMC and (b) Mission profile emulator. Source: [J1]

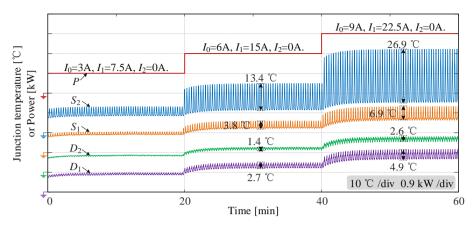

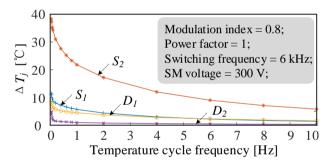

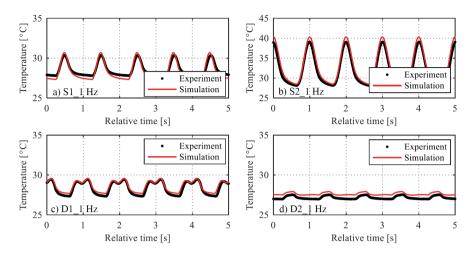

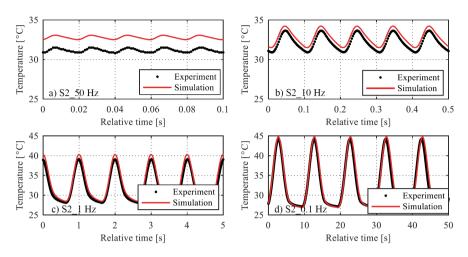

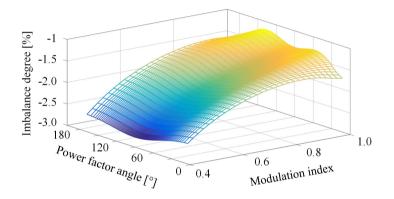

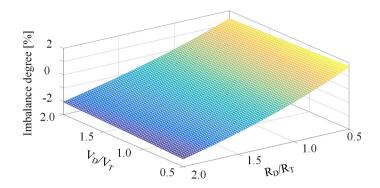

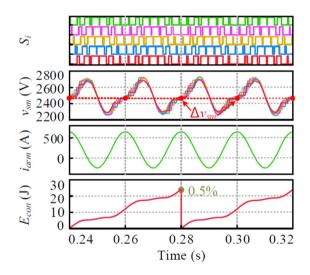

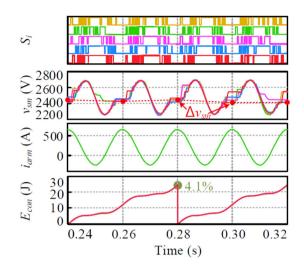

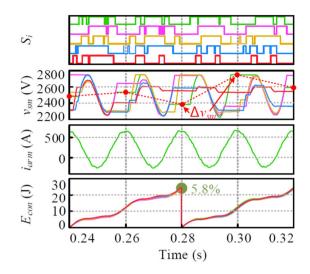

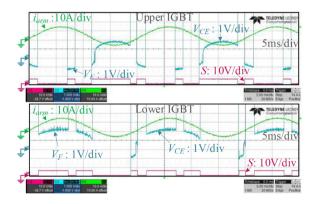

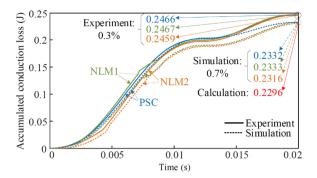

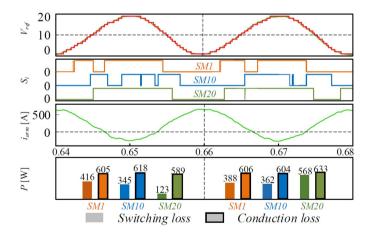

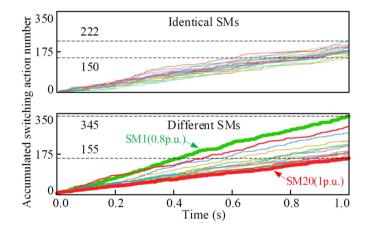

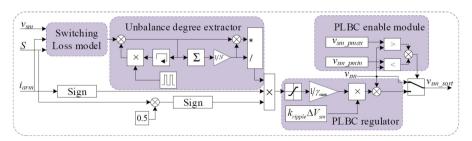

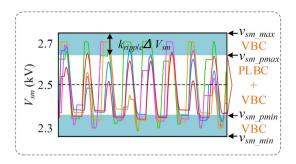

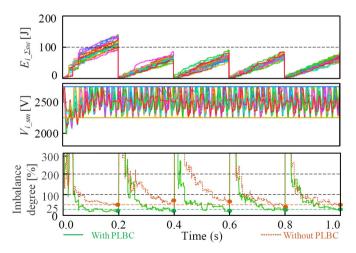

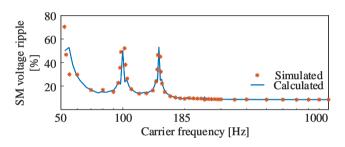

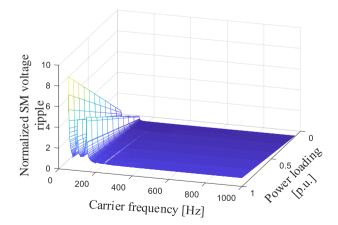

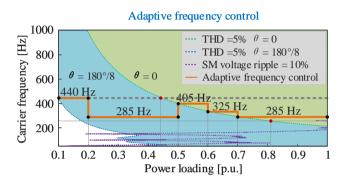

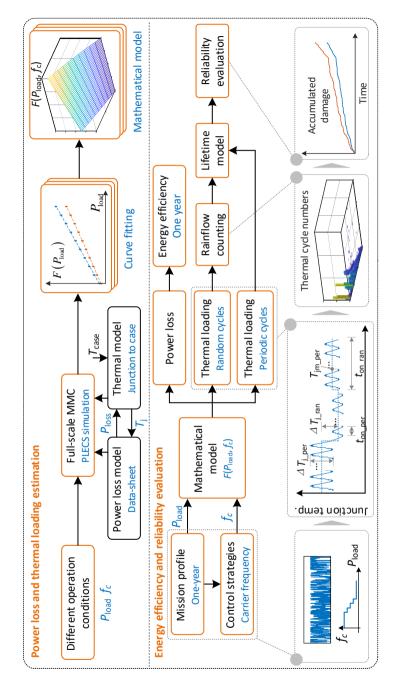

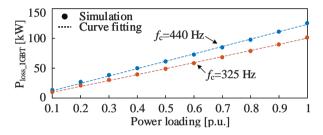

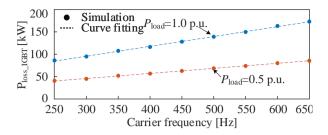

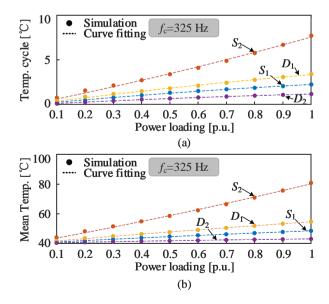

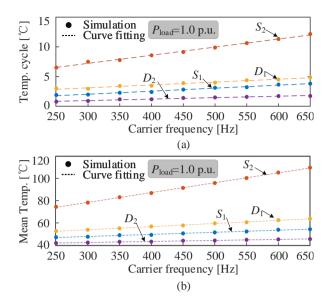

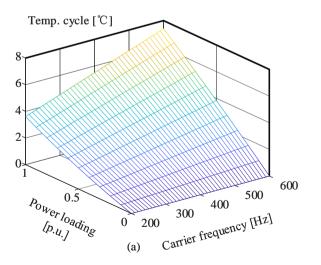

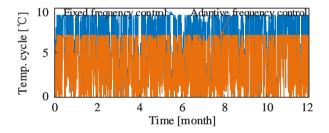

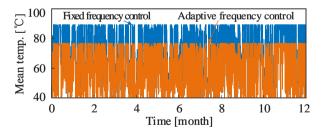

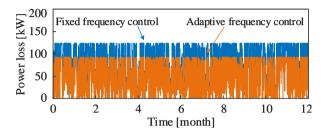

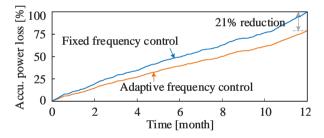

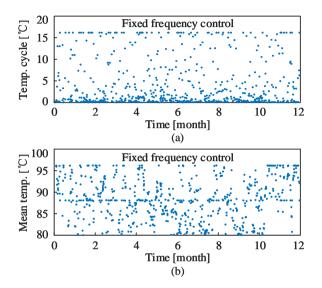

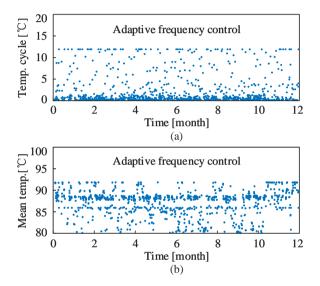

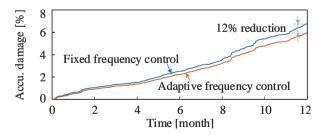

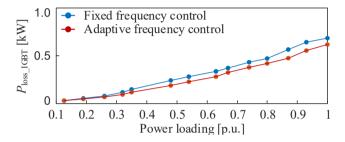

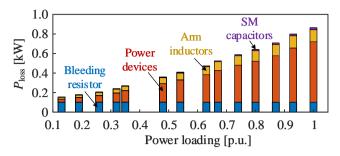

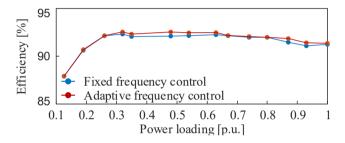

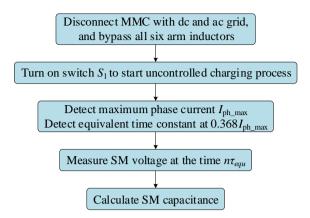

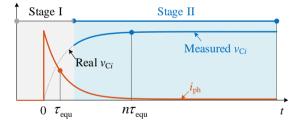

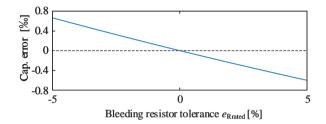

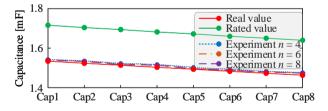

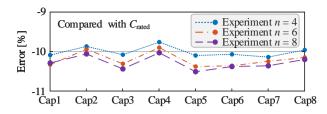

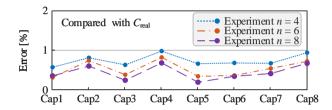

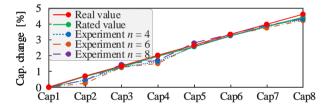

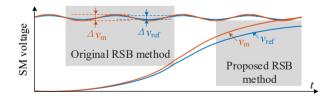

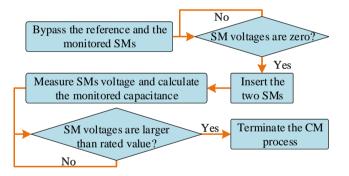

capacitor voltage is a reasonable solution in the mission profile emulator from the switching loss point of view.