## **Aalborg Universitet**

## **Three-phase Resonant DC-link Converter**

Munk-Nielsen, Stig

Publication date:

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Munk-Nielsen, S. (1997). Three-phase Resonant DC-link Converter. Department of Energy Technology, Aalborg University.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Three Phase Resonant DC Link Converters

Analysis and Simulation

Ph.D. Thesis, report no. 1/2

by Stig Munk-Nielsen April 1997

## Three Phase Resonant DC Link Converters Analysis and Simulation

ISBN

87-89179-16-1 (kpl.)

©

1997 Stig Munk-Nielsen

Published by

Institute of Energy Technology

Aalborg University

Printed by

Kopicentralen, Aalborg University

Distribution

Institute of Energy Technology

Aalborg University

Pontoppidansstræde 101

DK-9220 Aalborg Øst

Phone: +45 96 35 80 80 Fax: +45 98 15 14 11

## **Abstract**

The purpose of the project is to develop a three-phase resonant converter suitable for standard speed drives. The motivation for working with resonant converters is found in the problems of the standard converter type used today.

In standard converter type Pulse Width Modulated-Voltage Source Inverter, PWM-VSI, the switches are subject to high current and voltage stress during switching, which causes losses. The fast switching of modern switches reduces switching losses. Unfortunately this produces increased dv/dt and the size of the input/output filters of the PWM-VSI must be increased. The high speed of the switches cannot be fully utilized.

By using a parallel resonant converter the switching happens at low or zero voltage which reduces switch losses. The dv/dt is controlled by the resonant circuit, and it is therefore reduced significantly. The perspective using a resonant converter is high switching frequency combined with a high converter efficiency and low dv/dt.

In the first report several resonant converters are investigated to find a resonant converter that can compete with the standard PWM-VSI converter. Four converters were selected for the theoretical analysis, and the converters are simulated. An evaluation of the resonant converters is made, and one converter is selected for realization.

In the second report the realization of the selected resonant converter is described. This includes analysis, design and test of the converter.

A new control principle, using no additional power electric components, is eliminating the high voltage peaks associated with the resonant circuit. The resonant link voltage peaks are limited below 2.1 times the DC link voltages.

A new principle eliminating former resonant converter stability problems are proposed, implemented and tested. A resonant converter efficiency of 97 [%] was measured. The low dv/dt of the converter makes it possible to drive long cables without filtering. A successful test with a 300 [m] long cable and an induction machine load was carried out.

It is concluded that a stable, high efficiency and high switching frequency three phase parallel resonant converter is realized.

## Preface

This report is the first of two reports which are the basis in my attempt to obtain the Ph.D. degree. The reports are a part of the project named 'Resonans Konverter for Elektrisk Energiomformning' initiated February 1, 1993 and ended April 7, 1997.

The project is financed by the 'Danish Technical Research Council' and also in part by the foundation 'Det Obelske Familiefond'. The project is carried out at Aalborg University, Institute of Energy Technology (IET).

During writing several people have contributed to the report. Four supervisors followed the project and they have made an invaluable contribution, they are Head of Institute, Associate Professor John K. Pedersen and Associate Professor, Ph.D. Frede Blåbjerg from the Institute of Energy Technology, IET and Ph.D. Paul Thøgersen and B.Sc. Ulrik Jæger from Danfoss Drives A/S. I would also like to thank Danfoss A/S who supported the project by a VLT 3008 frequency converter.

I stayed four memorable months in Aachen at 'Institut für Stromrichtertechnik und Elektriche Antribe', where Oscar Apeldoorn and Franz-F. Protiwa were a great source of inspiration, and I thank them and people at ISEA for the very pleasant visit.

At Aalborg University, I would like to thank all the people at IET. In particular all the Ph.D. students and research assistants for interesting discussions, and Birthe Johansen for general help with the text editing. Technician Walter Neumayer has done a lot of laboratory work. During the last phase student Jacob Buck was helping in the laboratory. A special thanks to Ph.D. Peter Nielsen, now employed by Danfoss, for interesting discussions and pleasant company.

Aalborg University April 1997

Stig Munk-Nielsen M.Sc. EE.

## **Table of Contents**

## Abstract

## Preface

## Table of Contents

| 1 | Introduction                                                                                                                |     |

|---|-----------------------------------------------------------------------------------------------------------------------------|-----|

|   | 1.1 Introduction to power electronic and converters                                                                         | . 1 |

|   | 1.2 Undesirable interaction between converter and environment                                                               | . 2 |

|   | 1.3 Introduction to resonant converters                                                                                     |     |

|   | 1.4 Structure of report                                                                                                     |     |

|   | 1.5 Conclusion                                                                                                              | . 4 |

| 2 | Selection of converters for detailed study                                                                                  | 5   |

|   | 2.1 Basic resonant switching principle                                                                                      |     |

|   | 2.2 Parallel resonant DC link                                                                                               | . 6 |

|   | 2.3 Series resonant DC link                                                                                                 | . 7 |

|   | 2.4 Pole commutated DC link                                                                                                 | . 8 |

|   | 2.5 AC resonant link                                                                                                        |     |

|   | 2.6 Survey of converter topologies                                                                                          |     |

|   | 2.7 Discussion                                                                                                              |     |

|   | 2.8 Selection of resonant converters                                                                                        |     |

|   | 2.9 Conclusion                                                                                                              | 14  |

|   |                                                                                                                             |     |

| 3 | Resonant converter specifications                                                                                           | 15  |

|   | 3.1 Resonant converter load specification of dv/dt and maximum terminal voltage                                             | 15  |

|   | 3.2 Resonant converter specification                                                                                        | 16  |

|   | 3.3 Conclusion                                                                                                              | 17  |

| 4 | Non clamped parallel resonant converter                                                                                     | 10  |

| 7 | 4.1 Parallel resonant DC link converter (RDCL)                                                                              |     |

|   | 4.1.1 Link operation of the RDCL                                                                                            |     |

|   | 4.1.2 Simulation of RDCL and introduction to SABER                                                                          | 20  |

|   | 4.1.2 Discussion                                                                                                            |     |

|   |                                                                                                                             |     |

|   | 4.2 Parallel resonant DC link converter with link voltage peak control (RDCLVPC) . 4.2.1 Operation principle of the RDCLVPC |     |

|   | 4.2.2 Simulation of RDCLVPC                                                                                                 |     |

|   | 4.2.3 Discussion                                                                                                            |     |

|   | 4.3 Conclusion                                                                                                              |     |

|   | 4.5 Conclusion                                                                                                              | 33  |

| 5 | Clamped parallel resonant DC link converters                                                                                | 37  |

|   | 5.1 Parallel active clamped resonant DC link converter                                                                      |     |

|   | 5.1.1 Link operation of the ACRDCL                                                                                          | 38  |

|   | 5.1.2 Simulation of the ACRDCL                                                                                              | 41  |

|   | 5.1.3 Discussion                                                                                                            | 45  |

|   | 5.2 Passively clamped parallel resonant DC link converter                                                                   | 45  |

|   | 5.3 Conclusion                                                                                                              |     |

| 6                   | Pai           | rallel resonant PWM converters                                                   | 47        |

|---------------------|---------------|----------------------------------------------------------------------------------|-----------|

|                     | 6.1           | Notch commutated three-phase PWM converter                                       | 47        |

| ,                   | 6.2           | Zero switching loss PWM converter with resonant circuits                         | 48        |

|                     | 6.3           | Modified ACRDCL for PWM operation                                                | 48        |

|                     |               | 6.3.1 Link operation of the MACRDCL                                              | 49        |

|                     |               | 6.3.2 Simulation of the MACRDCL                                                  | 52        |

|                     |               | 6.3.3 Discussion                                                                 | 56        |

|                     | 6.4           | Conclusion                                                                       | 56        |

|                     |               |                                                                                  |           |

| 7                   | PИ            | M VSI converter                                                                  | 59        |

|                     |               | PWM converter                                                                    |           |

|                     | 7.2           | Simulation of PWM-VSI                                                            | 60        |

|                     |               | Conclusion                                                                       |           |

|                     |               |                                                                                  |           |

| 8                   |               | nverter modulation strategies                                                    |           |

|                     | 8.1           | Delta modulation                                                                 |           |

|                     |               | 8.1.1 Delta current modulator                                                    |           |

|                     |               | 8.1.2 Adjacent state current modulator                                           |           |

|                     |               | 8.1.3 Sigma delta modulator                                                      | 66        |

|                     |               | 8.1.4 Selection of modulation strategy                                           | 67        |

|                     | 8.2           | Pulse width modulation                                                           | 67        |

|                     |               | 8.2.1 Stator flux oriented asynchronous vector modulation                        | 67        |

|                     |               | 8.2.2 Link optimized stator flux oriented asynchronous vector modulation, LOSFAV |           |

|                     |               |                                                                                  | 70        |

|                     |               | 8.2.3 PWM used in resonant link converters with oscillating link                 | 72        |

|                     | 8.3           | Conclusion                                                                       | 73        |

|                     |               |                                                                                  |           |

| 9                   | Per           | rformance and characteristics of converters                                      | <i>75</i> |

|                     |               |                                                                                  |           |

| 10                  | Co            | nclusion                                                                         | <i>79</i> |

|                     | 10            | .1 Revision of the initial problem                                               | 79        |

|                     | 10            | .2 Evaluation                                                                    | 79        |

|                     | 10            | .3 Selection of converter for further work                                       | 81        |

|                     |               | ,                                                                                |           |

| Bi                  | blio          | graphy                                                                           | 83        |

| 4.                  |               | A Dunit wint nor on the state of                                                 | 00        |

| $A_{I}$             | <i>pp.</i> 2  | A Basic serial resonant circuit                                                  | 89        |

| 1                   | nn i          | B Selection of resonant link components                                          | 01        |

| $\Delta \mathbf{I}$ | υ <b>ρ.</b> 1 | B Selection of resonant link components                                          | 91        |

| 4                   | nn (          | C Derivation of voltage peak control algorithm used in the RDCLV.                | PC        |

| 2 <b>1</b> <u>1</u> | op.C          | Converter                                                                        |           |

|                     |               |                                                                                  | 73        |

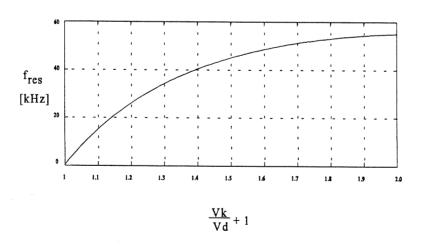

| Α                   | nn.           | D ACRDCL Converter link frequency dependency on clamp factor                     | 97        |

|                     | PP.           | = 1101= 0= 000.0100 mm, equality depositionely on elamp judger 111111            |           |

| Α                   | pp.           | E Definition of performance index DF and THD                                     | 101       |

|                     |               |                                                                                  |           |

| A                   | pp.           | F Single phase equivalent circuit of three-phase converter                       | 103       |

|                     |               |                                                                                  |           |

| E                   | Ingl          | ish summary                                                                      | 105       |

|                     |               |                                                                                  |           |

| 7                   | ani           | sh summary                                                                       | 107       |

## 1

## Introduction

In this chapter first an introduction to power electronics and variable speed drives is made. Next the standard converter used in the variable speed drives is described. The converter performance is discussed and then the resonant converter is introduced. Finally, a description of the report structure is made.

## 1.1 Introduction to power electronic and converters

Electronics has for many years been in rapid development with the result that electronic components are capable of conducting high currents and blocking high voltages. The components are controlled with low voltage signals and often direct from a micro chip with a powerful calculation unit. Combination of easy controlled power components and powerful calculation chips has emerged a new field of electronics called power electronic.

The new generations of power electronic components are characterized by: smaller size, higher current and voltage levels, easy control and integration with micro electronic.

Today power electronics is widely used to convert electrical energy, and it is used in places as household, industry and utility systems. The power range is from a few VA to hundreds of MVA. Conversion of electrical energy using power electronics is of course not ideal, but it offers so great advantage that the application area is still increasing. Power electronic converters replace mechanical converters, and the development of power electronic itself results in new converters that replace older generations.

A major application area of power electronic converters is speed drives. This type of drive is typically available in the power range from 1-500 [kVA] and used in the industry. In 1993 the estimated world market value of converters was £7bn /7/. The power used by power electronics drives world-wide was estimated to 35 [GW] in 1993. Converters used in open loop and servo drives had a value of 61 % from world market value.

More than 50% of the applications used standard induction machines. The market of speed drives is growing fast. From 1993 to 2000 the open loop drive market value is expected to grow 100% and the servo drives 150% /7/.

Variable speed drives are found in industry for mills, winders, hoists, fans, and pumping applications. The most used machines in speed drives today are induction machines. Other types of three-phase machines might be popular, but many of them are controlled by the same type of speed drive as induction machines.

The induction machine dominates the market today, and in the near future no other machine is seemed to take over. The resonant converter application is therefore selected to be a variable

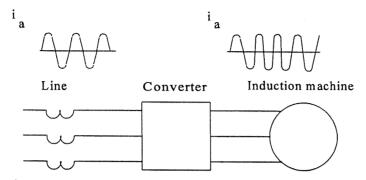

speed drive used for controlling standard induction machines. The drive is shown in Fig. 1.1.

Fig. 1.1 View of speed drive system with induction machine load

The converter type dominating today consists of a rectification unit, a stiff DC link voltage, and an inverter(PWM-VSI¹), and it has been the same over more than two decades. The converter is today considered mature. However, despite the development of the converter it has some undesirable qualities. There are limitations of switching frequency due to switching loss and high level of electromagnetic interaction due to high dv/dt.

## 1.2 Undesirable interaction between converters and environment

There are two undesired main interactions between the converter and its environment, one is the heat flow and the other arises from electromagnetic interaction.

Main reasons of heat flow are:

Converter losses

- switching losses in power electronic components

- conduction losses in power electronic components

Losses in load machine generated by converter

- non-sinusoidal converter output voltage

Losses in electrical network generated by converter

- non-sinusoidal converter input currents

Main reasons of electromagnetic interaction are:

Distorted converter input current

Conducted and radiated emission from the converter

Because high EMI<sup>2</sup> can cause disturbance or mal function of other electrical equipment connected to the electrical network, there are made EMI regulations. The sources of EMI are many and interference level is depending on converter topology selection, layout, and operation mode/33/.

One source of importance is the capacitive coupling between switching elements and ground. The capacitive coupling generates common mode currents,  $i_c$ :

$$i_c = C \frac{dv}{dt}$$

(1.1)

<sup>&</sup>lt;sup>1</sup> Pulse Width Modulated Voltage Source Inverter, PWM-VSI

<sup>&</sup>lt;sup>2</sup>ElectroMagnetic Interaction, EMI

The capacitance should be minimized, and the dv/dt limited, to lower the level of common mode current.

A summarization of the above discussion and statements covering the most used converter type in electrical machine drives today is showed in Table 1.1. The converter is a PWM-VSI.

| Desired converter improvement           | How to improve                                                        | Future importance                                                                          |  |

|-----------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|

| low switching loss                      | increase switching speed of components                                | increase due to higher energy                                                              |  |

| low conduction loss                     | use low on state voltage components                                   | costs                                                                                      |  |

| near sinusoidal input/output<br>voltage | increase converter switching frequency and components switching speed | increase due to increased<br>energy costs and attention<br>towards low harmonic<br>content |  |

| low dv/dt, low EMI                      | decrease component switching speed                                    | increase due to new EMI regulations                                                        |  |

**Table 1.1** Desired converter improvements for the PWM-VSI converter, and how to improve performance. And expected further importance of each performance parameter.

From Table 1.1. it can be seen that the improvement of PWM-VSI converter performance includes both a decrease and an increase of power electronic component switching speed. This contradiction creates a dilemma. The problem has been present from the beginning of power electronics, but due to the increased attention to harmonic content, energy costs, and EMI, it gets harder to make PWM-VSI converters for speed drives that have satisfactory performance.

## 1.3 Introduction to resonant converters

Much research has been done to increase the performance of the PWM-VSI converter by adding auxiliary circuits, but none of them has been satisfactory. In 1986 a new type of converter was proposed by D.Divan "The Resonant DC-Link Inverter - A New Concept in Static Power Conversion" /1/. This converter uses the principle of zero voltage switching for the power electronic components which means that the switching loss ideally is zero, and the dv/dt is low compared to PWM-VSI. The zero switching loss allows high switching frequency, and in fact the switching frequency can be raised a factor of ten compared to the PWM-VSI.

Table 1.2. shows a performance comparison between PWM-VSI and the resonant converter proposed in /1/.

| Desired converter                       | Relative performance of converters |                    |  |  |

|-----------------------------------------|------------------------------------|--------------------|--|--|

| performance improvement                 | PWM-VSI                            | Resonant converter |  |  |

| low switching loss                      | _                                  | +                  |  |  |

| low conduction loss                     | +                                  | •                  |  |  |

| near sinusoidal input/output<br>voltage | 0                                  | 0                  |  |  |

| low dv/dt, low EMI                      |                                    | +                  |  |  |

**Table 1.2** Performance comparison between PWM-VSI and resonant converters. Rating: 0 no difference, + better, - worse.

Table 1.2. shows that resonant converters have potential to be a competitor with the PWM-VSI, and this is the basis for further investigation of the resonant converter.

## 1.4 Structure of report

In the project a resonant converter is chosen for realization, and in this report the selection is done. This involves an investigation of different resonant converter topologies carried out using papers as source. The very broad view obtained is used to select a particular converter topology which is the parallel resonant converter topology, and this is done in Chapter 2. The resonant converter performance must compete with the standard PWM-VSI performance, and there is made a set of specifications that the resonant converter must fulfil. The resonant converter specifications are described in Chapter 3. Next step is a theoretical analysis and simulation of four selected parallel resonant converters which is done in Chapter 4, 5, and 6. In Chapter 7 a PWM-VSI converter is simulated so its performance can be compared with the resonant converters. In Chapter 8 the modulation strategies used in the resonant converters are described. In Chapter 9 the converter performance parameters are put into tables that makes it easier to compare the converter performance. In Chapter 10 the converters are compared and one converter is selected for realization. The realization and further work are described in the second project report.

## 1.5 Conclusion

In this chapter an introduction to power electronics and the application area is given. An important application is variable speed drives, low and medium power range. Improvement of power electronic components increases the variable speed drives performance and this increases the application areas. Expectations of a growth of 100% on the open loop drive marked value are expected from 1993 to 2000. Increasing energy costs and EMI demands increase the need of high converter efficiency and low distorted input and output voltage. A relatively new type of converter, the resonant converter, has potential performance improvement, relative to the standard PWM-VSI converter. The fact that the resonant converter has the potential to be a superior competitor, to the PWM-VSI, is the basis for further investigation of the resonant converters.

## 2

## SELECTION OF CONVERTERS FOR DETAILED STUDY

This chapter gives first a short introduction to soft switching and then describes different resonant converters. The purpose of the description is to select a few resonant converters that seem the most useful, in low to mid. power range area, variable speed drive applications. The selected converters are described later in the report. A detailed description of all the resonant converters reported in papers would be overwhelming time-consuming, and therefore the different converters are sorted in groups of converters that shear a particularly fundamental circuit configuration. Then by evaluating the different particular circuit configurations the number of converters to be looked at is reduced. Four fundamental circuit topologies are described:

Parallel resonant DC link: Serial resonant circuit is energized by DC voltage source and the

resonant circuit is placed in the converter link.

Series resonant DC link: Serial resonant circuit is energized by DC current source and the

resonant circuit is placed in the converter link.

Pole commutated DC link: A resonant commutating circuit is connected to the centre of

each converter leg which is energized by a DC voltage source.

ACresonant link converter: The link voltage and current are AC quantities and serial or

parallel resonant circuit can be used.

When the topology is selected, a few converters are selected for a comprehensive study, and a more specific list of performance and characteristic parameters can by set up in the next chapter.

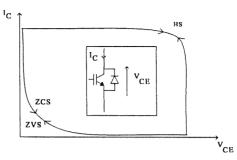

## 2.1 Basic resonant switching principle

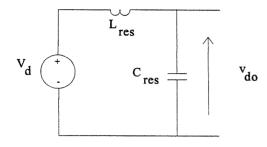

A resonant converter has one or more resonant circuits, a circuit could be a L-C serial or a parallel circuit. Using resonans it is possible to obtain ZCS¹ or ZVS², and compared with HS³ the switching losses and dv/dt or di/dt are lower. But there are higher conduction losses, and the circulating energy of the resonant circuit causes losses. A serial resonant circuit is shown in Fig. 2.1.

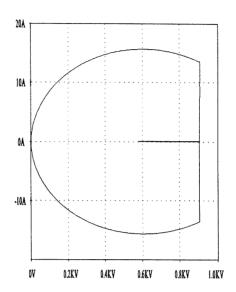

With correct initialization values of the components the voltage above the capacitor  $v_{do}$  is oscillating between 0 and  $2V_d$ , the time domain equations of the circuit are shown in appendix A. If the voltage is fed into an inverter bridge and the inverter switching happens, then the resonant voltage reaches zero, the switching loss is ideally zero. The switching trajectories of ZCS, ZVS, and HS are shown in Fig. 2.2.

<sup>&</sup>lt;sup>1</sup>Zero Current Switching, ZCS

<sup>&</sup>lt;sup>2</sup> Zero Voltage Switching, ZVS

<sup>&</sup>lt;sup>3</sup> Hard Switching, HS

Fig. 2.1 Serial resonant circuit

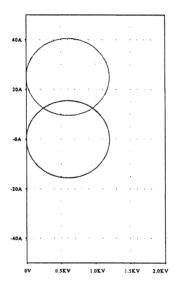

Fig. 2.2 The switching trajectories of ZCS, ZVS and HS.

The switching trajectories shown imply that there are switching losses using ZCS and ZVS. This problem is not considered in this report. It is assumed that the ZCS and ZVS are without loss. If hard switching is used it assumed the switching time is infinite small and loss less.

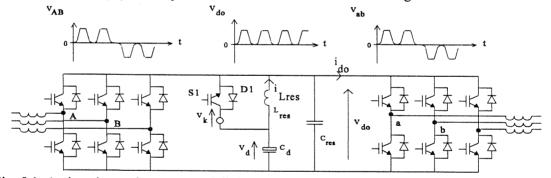

## 2.2 Parallel resonant DC link

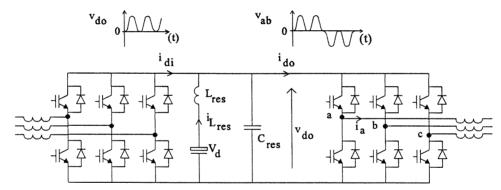

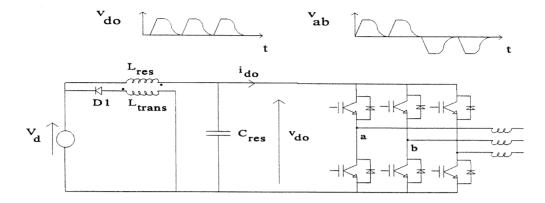

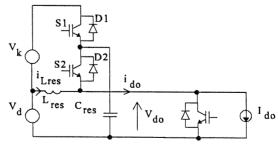

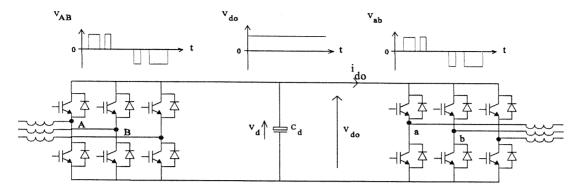

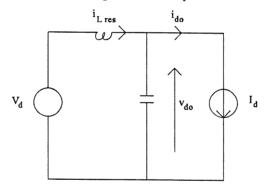

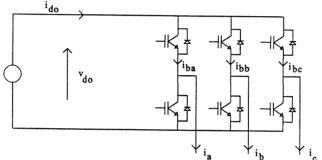

The parallel resonant DC link converters have an oscillating link voltage that oscillates between zero voltage and a peak voltage. During the zero voltage period the converter switches can be turned on and off without switching loss. Fig 2.3 shows a parallel resonant converter without any link voltage clamp circuits. The switches in the converter must be

Fig. 2.3 Parallel resonant DC link converter

synchronized with the link zero voltage periods. This strategy eliminates the possibility of regular PWM<sup>4</sup>, and instead a discrete pulse modulation DPM<sup>5</sup> must be used. In /1/ DPM is described, and it is concluded that the DPM theoretically has a performance comparative with

PWM-VSI if the resonant switching frequency is more than 4 times higher. The spectral performance of the resonant converter is worsened because the link frequency is dependent on the link current.

Fig. 2.4 shows the resonant link voltage  $v_{do}$  and inductor current  $i_{Lres}$ . The figure shows an example of an increase in the resonant capacitor energy due to link current changes.

The result of the energy increase is a higher resonant link voltage amplitude. The energy is removed from the resonant components (inductor  $L_{res}$ ) by the antiparallel diodes in the converter bridge, and the energy removal introduces an increased zero voltage interval. The zero voltage

<sup>&</sup>lt;sup>4</sup> Pulse Width Modulation, PWM

<sup>&</sup>lt;sup>5</sup> Discrete Pulse Modulation, DPM

interval also increases when the resonant inductor energy is increasing as shown in Fig. 2.4. The resonant switching frequency is often chosen to be higher than 20 [kHz]. By the resonant frequency is meant the average switching frequency of the inverter switches. The loss less switching has been reported using IGBT with a switching frequency of 65 [kHz] /35/.

The spectral performance of the resonant converter is dependent on the modulation index  $m=\hat{V}_{ab}/V_d$ . When a comparison of total harmonic distortion, THD, is done in /2/ it shows that DPM converter's spectrum performance is decreased at lower voltages.

Compared to hard switching converters with a stiff DC voltage link, the voltage peak to peak amplitude could be more than twice the DC voltage. The peak voltage is often limited by an auxiliary circuit/35/. A high peak voltage across the terminals has several disadvantages:

- High voltage rating of converter switches

- Stress on machine insulation which causes breakdown

The converters with link voltage clamp circuits typically have a clamp level of 1.3-1.5 relative to the DC link voltage. The active devices in the clamp circuits are typically the most stressed components in the converter. They have to work very close to the resonant frequency of the resonant components, whereas the switching frequency of the converter switches is lower. Clamp circuits without active components have been designed /22/ where the clamp level is 2.1 times Vd. Therefore, high voltages are still impressed on the inverter switches and machine insulations if the active clamp is avoided.

Resonant inverters which use soft switching could easily have a dv/dt lower than 500 [V/ $\mu$ s] and low values of dv/dt for diodes turning off. Hard switching of IGBT has dv/dt easily greater than 2 [kV/ $\mu$ s] and diode turn off has even higher dv/dt. Diode dv/dt higher than 10 [kV/ $\mu$ s] has been measured in the laboratory.

Low dv/dt is a desirable feature, /11/ advices a dv/dt lower than 1300  $[V/\mu s]$  for inverter feeding standard 400 [V] induction machines.

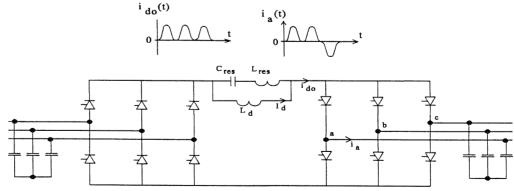

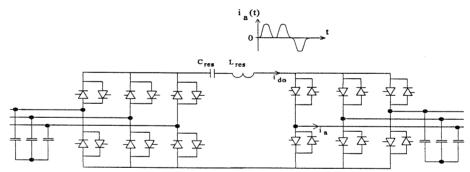

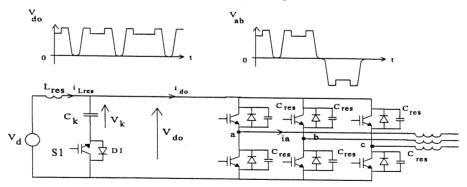

## 2.3 Series resonant DC link

The series resonant DC link converter uses the principle of ZCS where loss less switching is obtained. The converter is closely related to the thyristor converter and the link voltage is bipolar which demands switches with symmetrical voltage blocking capability. The DC link current is oscillating between zero and minimum twice the DC link current, which is supplied by a DC-inductor, L<sub>d</sub>. The converter must always form a current path for the inductive DC link current and inductive loads demand a capacitor filter. Fig 2.5 shows the series resonant DC link converter.

Fig. 2.4 Series resonant DC link converter.

One advantage is the low number of active components compared to the parallel resonant

topology. The converter is born with the possibility of rectification with unity power factor and bi directional power flow. When using a parallel resonant topology, the AC voltage rectification is often done by diodes that eliminate the controlled switches, the bidirectional power flow and the unity power factor correction options. Only 12 thyristors are needed for a full bridge three-phase AC to AC conversion while using a parallel resonant converter 12 transistors and 12 diodes are used.

The firing of the thyristors must be synchronized with the link zero current periods and again DPM is used. Spectral performance is dependent of the switching frequency. Normally the switching frequency is limited to 30 [kHz] due to relative slow switching times of thyristors /24/. Modern high speed thyristors have a turn off time around 10 [µs] /25/.

The link current stress is minimum twice the DC inductor current and the conduction loss is then relatively high compared to parallel resonant converters.

One general drawback of the serial converter is the necessary filter capacitance on the AC sides /26/. The interaction of the filter capacitance and the motor load inductance cause high frequency oscillations on the load current. Further on the ac capacitor is bulky. A passive 1st order filter can be used to reduce the high frequency oscillation to an acceptable level at the expense of extra components and ohmic power dissipation/26/. This solution makes the size of the converter very dependent on the load.

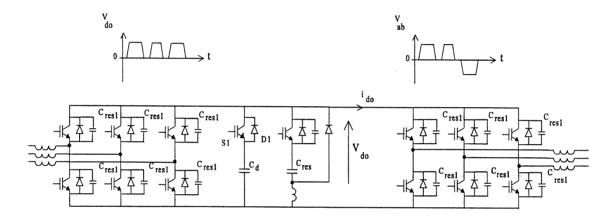

## 2.4 Pole commutated DC link

The pole commutated converter has a voltage stiff DC link, but the converter switches are switched under zero voltage conditions, and therefore low switching losses are obtained. To obtain ZVS an auxiliary resonant circuit is used. Each converter branch uses one circuit and the auxiliary circuit has three terminals, two are connected to the DC link terminals and the third terminal is connected to the branch terminal. The name 'pole' appears from that. An auxiliary pole resonant commutated converter/27/ is shown in Fig. 2.6.

Fig. 2.5 Auxiliary pole resonant commutated converter

Unlike the parallel and series resonant DC link converters the pole commutated converter is able to perform PWM. Another advantage is that the main load current is not flowing through the resonant elements, and in this way the current stress on the resonant inductor is relatively small. On the other hand the resonant frequency must be high to yield a good PWM modulation band width. This is explained in the following paragraph.

The auxiliary commutation circuit must be synchronized with the switching of the converter switches, and the auxiliary commutation circuit which forms a resonant circuit has three main states ensuring ZVS of the converter switch. The states are:

- State 1. Initialization of resonant circuit

- State 2. A resonant cycle changing the branch potential from zero voltage to dc link voltage or opposites from dc link voltage to zero voltage

- State 3. The resonant inductor discharges to zero current.

The total time required for the three states sets a minimum and maximum pulse width time and this sets a limitation of the PWM performance. Compared to hard switching converters the voltage stress on the converter switches is the same and the dv/dt of the output voltage is smaller.

There is a trade off between a low dv/dt and a small minimum, pulse width duration. An increased resonant frequency given by  $L_{res}$  and  $C_{res}$ , increases the dv/dt but lowers the minimum pulse width. This will give a better spectral performance. The pole commutated converters obtain a spectral performance close the to PWM-VSI for a given switching frequency/27/.

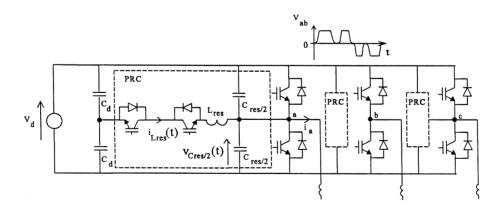

## 2.5 AC resonant link

The AC resonant link has a serial or a parallel resonant circuit operating at high frequency. The link voltages and currents are both AC quantities, and therefore bidirectional converter switches are necessary. The bidirectional switch in one package is not available yet. Today, it has to be buildt from several discrete devices, and often it is necessary to add snubbers to make the switch work properly /30/. The converter switches are turned on at ZCS or ZVS to obtain small switching losses. Fig 2.7 shows a serial AC resonant link.

Fig. 2.6 Series resonant AC link converter.

Using an AC link decreases the amount of energy stored in the link. The DC link capacitor or inductor used in the earlier described topologies is eliminated, but the resonant components must handle the total power flow through the converter. A high VA rating is needed for the components /4/. The AC link converter must be operated in such a way that the energy demand of the load side is supplied by the input converter. The energy flow control through the converter must ideally be controlled instantly. In the real world this is not possible, but with fast signal processors and a high link frequency the energy flow can be controlled satisfactorily/31/. The coordination of rectifier and inverter is complex and the large number of switches to be controlled makes the realization of the converter difficult.

## 2.6 Survey of converter topologies

The topologies performance and characteristics are put into Table 2.1 and Table 2.2. The tables offer a comparison between the topologies and the PWM -VSI hard switched converter.

Table 1. High level properties

| Table 1. Eigh                      | lable I. High level properties |        |                         |               |          |                     |                        |                              |                      |

|------------------------------------|--------------------------------|--------|-------------------------|---------------|----------|---------------------|------------------------|------------------------------|----------------------|

|                                    |                                |        |                         | Device number | number   | Link dev            | Link device count      | Input filter                 | Output filter        |

| Converter topology                 | Input                          | Output | Link type               | Switches      | Diodes   | Switches,<br>diodes | Passive components L,C | Passive<br>components<br>L,C | Passive components*2 |

| Parallel res.<br>DC link           | Diode or<br>DPM                | DPM    | Voltage<br>res. DC link | 6<br>12       | 12       | min. 0              | 1L,2C                  | 3F                           | 0                    |

| Series<br>res. DC link             | DPM                            | DPM    | Current<br>res. DC link | 12*1          | 0        | min. 0              | 2L,1C                  | 3C                           | 3C                   |

| Aux. Pole<br>commutated<br>DC link | Diode or<br>PWM                | PWM    | DC voltage              | 12<br>24      | 18<br>24 | 0                   | 6L,14C<br>3L,14C       | 3L                           | 0                    |

| AC serie<br>res. link              | DPM                            | DPM    | AC current              | 24*!          | 0        | 0                   | 1L,1C                  | 3С                           | 3C                   |

| Sinusoidal<br>PWM-VSI              | Diode or<br>PWM                | PWM    | DC voltage              | 6<br>12       | 12       | 0                   | 1L<br>1C               | 3F                           | 0                    |

|                                    |                                |        |                         |               |          |                     |                        |                              |                      |

Use thyristors

Inductive load assumed

Table 2. Medium level properties

| Approx.<br>main switch<br>I stress *2 |                          | >2                     |                                    | na                    | general .             |

|---------------------------------------|--------------------------|------------------------|------------------------------------|-----------------------|-----------------------|

| Approx. main switch V stress *2       | 1.3-2                    | 1.2                    |                                    | na                    |                       |

| Max. output<br>voltage*1              | \_=\                     | current                | 1                                  | current               | 1                     |

| Control<br>complex-<br>ness           | moderate<br>complex      | very<br>complex        | moderate<br>complex                | very<br>complex       | simple                |

| Converter<br>power<br>level*3         | middle                   | middle,<br>high        | middle,<br>high                    | middle,<br>high       | middle,<br>high       |

| Typical switching frequency [kHz]     | 20-60                    | <30                    | <20                                | <30                   | 1 -<br>18 kHz         |

| Main<br>switch<br>switching           | SAZ                      | ZCS                    | SAZ                                | SCS                   | Hard                  |

| Switch<br>type                        | Uni-<br>directional      | Uni-<br>directional    | Uni-<br>directional                | Bi-<br>directional    | Uni-<br>directional   |

| Typical<br>switch<br>elements         | IGBT,<br>MOS-FET         | Thyristor              | IGBT                               | Thyristor             | IGBT,<br>MOS-FET      |

| Input                                 | Diode<br>DPM             | DPM                    | Diode<br>PWM                       | DPM                   | Diode<br>PWM          |

| Converter topology                    | Parallel res.<br>DC link | Series<br>res. DC link | Aux. Pole<br>commutated<br>DC link | AC serie<br>res. link | Sinusoidal<br>PWM-VSI |

The output voltages are normalised using the DC link voltage as base value The voltage/current stress is relative to the sinusoidal PWM-VSI Power level: middle 1-100 [kVA], high > 100 [kVA]

## 2.7 Discussion

In this section a discussion of the topologies presented in this chapter is made.

#### Serial resonant AC link

The AC serial resonant link converter has no suitable bidirectional switches and the realization of bidirectional switches must be done by discrete components. /29/,/30/ use additional snubber circuits for the switch realization. The snubber causes high losses /29/. Comparing the converter size, then the AC resonant link eliminates the need of energy storage that ensures a voltage or current offset. With no energy storage the rectifier must deliver the needed power that is demanded by the inverter. This control strategy of the AC resonant link converter is complex to realize. If the same control strategy is applied to a DC parallel resonant link converter, the capacitance of the DC link capacitor is reduced considerably /15/. It seems that the size advantage of the AC serial resonant link is small, if any at all. No further investigation of AC resonant link converter is done.

#### Serial resonant DC link

The serial resonant DC link converter uses more filter components than the parallel resonant DC link converter, and with inductive loads there are problems with resonance between the load and filter /24/. To eliminate the resonans a 1st order filter could be used /26/ at the expense of loss and extra components. The serial resonant DC link has a relatively low number of switches and diodes because thyristors are used. However, this switch type limits the link frequency to 30 [kHz]. The converter seems promising for high power applications using thyristors /24/, but for medium power applications with demands of low THD a parallel resonant seems to offer a better performance. The need of a capacitive output filter and the problems of resonant with inductive loads are a major drawback, no further investigation of serial resonant DC link converters is done.

## Pole commutated DC link converter

The pole commutated DC link converter has a spectral performance close to hard switched VSI-PWM and no additional voltage stress. Therefore, it has superior performance compared to the parallel resonant DC link converter performance. Comparing the component number in the converters the pole commutated DC link converter uses twice the number of switches and diodes. The number of passive components is increased too. In /28/ a combination of the pole commutated DC link and parallel resonant DC link converter is proposed. A converter that uses three switches and three diodes is made. The converter has good spectral performance and does not use extremely many components relative to the PWM-VSI. This converter is disregarded here due to high component count. For high power application the pole commutated DC link converter must be reconsidered.

#### Parallel resonant DC link

The parallel resonant DC link converter is very similar to the PWM-VSI converter comparing the number of components used. It is the DC voltage link converter of the resonant converters that uses the smallest number of components. The main disadvantages are the high link voltage amplitude that is twice the link voltage of the PWM-VSI converter. If the high link voltage is not accepted, there must be added auxiliary circuits to clamp the voltage amplitude, or there must be found new ways to limit the link amplitude voltage without using clamp circuits.

The switching frequency must be at least four times higher than the PWM-VSI switching frequency to obtain the same output voltage and current quality. Further on is the spectral performance more dependent of the load conditions that PWM is. At low modulation index is the spectral performance of the resonant converter decreased somewhat compared to PWM. The

resonant converter has little switching loss and therefore the switching frequency is usually higher than 20 [kHz]. Using a switching frequency of 20 [kHz] the resonant converter spectral performance should be equal to a 4-5 [kHz] PWM converter.

## 2.8 Selection of resonant converters

Some basic requirements to the selected converter are:

- Voltage link

- Low DC link voltage peaks

- Good spectral performance for low and high modulation index

- Low number of devices

The voltage link is preferable to current link because it eliminates capacitive filters.

Of the resonant converter topologies described here the parallel resonant converter topology is judged to be closest to the desired requirements. This is of course a subjective opinion. It is discussed how good the fundamental circuit configuration of the parallel resonant converter in 2.2 fulfils the basic requirements, and from this a few converters are selected to work further on.

Voltage link: All the converters have a voltage link.

Low DC link voltage peaks: It is shown that the fundamental circuit configuration in Fig. 2.1 has a load dependent peak link voltage which is undesirable. The link voltage must be controlled in order to limit the voltage ratings of the converter components and to keep the link voltage peak amplitude constant to avoid sub-output voltage harmonics.

Good spectral performance for low and high modulation index: It is mentioned in several papers that the DPM converter has a relative worse output voltage quality than the PWM converter, at low modulation indexes.

Low number of devices: The fundamental circuit configuration in Fig. 2.1 only adds two extra components relative to the standard PWM and this is a desirable feature. It is desired to keep the number of power electronic auxiliary components low, but as it will be shown, the number of components is increasing with the desire of fulfilling the upper requirements.

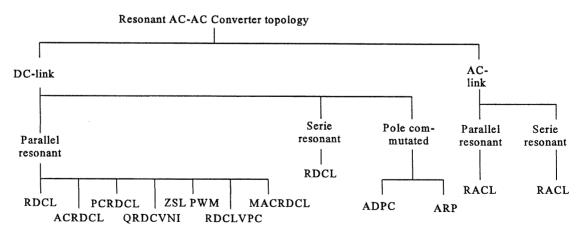

In Fig.2.8 the different converters that have been described in the papers used in this chapter are shown, and there are added two converters that have not been found described in any paper. They are described later. Under the Figure there is an explanation of the concentrated names

Fig. 2.7 Overwiew of converters dealt with in this report

Parallel resonant converters

RDCL: Resonant DC Link,/1/

ACRDCL: Active Clamped Resonant DC link,/35/,/23/ PCRDCL: Passive Clamped Resonant DC link,/22/

QRDCVNI: Quasi Resonant DC link Voltage Notch Inverter,/5/,/14/

ZSLPWM: Zero Switching Loss PWM,/15/

RDCLVPC: Resonant DC link Voltage Peak Control

MACRDCL: Modified Active Clamped Resonant DC Link

Serial resonant converters

RDCL: Resonant DC Link,/24/,/26/

Pole commutated converters

ARCP: Auxiliary Resonant Commutated Pole,/27/,/28/

AC resonant link converters

RACL: Resonant AC link,/30/,/29/,31/

The following converters of the parallel resonant converter are selected for a detailed study including a theoretical description and a converter simulation, and there is a short explanation why the converter is selected:

RDCL: Is the fundamental converter the parallel resonant converters.

RDCLVPC: Eliminates the need of link clamp components while maintaining control of

peak link voltage, the control principle is new. A high efficiency is expected.

ACRDCL: Has the lowest resonant peak voltage.

MACRDCL: Is a modified ACRDCL resonant converter which is pulse width modulated

and expected to have superior output voltage quality.

The parallel resonant converters shown in Fig. 2.8, which is not simulated, are only described briefly, due to the time a deeper analysis takes. The standard PWM-VSI is simulated in order to compare the performance of the resonant converters.

### 2.9 Conclusion

Initially in the chapter the basic resonant switching principle is described. Then four different resonant converter topologies are described, the purpose is to select a topology for further work. The selection of topology is based on a paper study. This is a fast way to obtain a general overview. On this very general knowledge the parallel resonant converter topology is selected for further study. Seven parallel resonant converters are described in the following chapters. Because it is very time-consuming to make a full analysis (based on idealized components) and simulation of the converters, only four converters retrieve this treatment. The remaining converters are only described very briefly. The four converters' performance is compared to each other. As the intention with the report is to find a converter with a superior performance relative to the PWM-VSI converter, the PWM-VSI converter is also simulated. A comparison of the resonant converters is made on the basis of the specifications found in the next chapter. The highest rated converter is going to be realized.

## 3

## Resonant converter specifications

In the next chapters an investigation of the resonant converters selected in chapter 2 is done. The investigation of the resonant converters must give a picture of each converter's performance. In this chapter the performance and the characteristic parameters used in the evaluation of the resonant converters are chosen.

The resonant converter is, as described in chapter 2, used in a variable speed drive, and the load is a standard induction machine. There is, in this chapter, made an investigation of which type of converter output voltages there should be applied to the induction machine. The investigations are used to specify the demands to the resonant converters' performance.

## 3.1 Resonant converter load specification of DV/DT and maximum terminal voltage

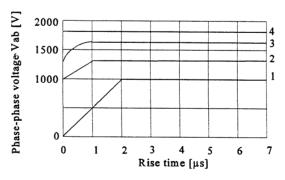

Since the introduction of speed drives that generate high voltage pulses and dv/dt in the output voltage, there has been an increasing need of knowing what level of voltage stress induction machines can withstand. The allowable level of voltage stress has been discussed in /11/ where is is referred to investigations made at the Technical University of Dresden, initiated by ZVEI¹. Their results show from a questionnaire to machine manufacturers that standard low voltage electrical machines can be stressed by output phase-phase voltage peak values of 1300 [V] and dv/dt of 1300 [V/ $\mu$ s]. The results from /11/ are shown in Fig. 3.1, and curve 1 is according to DIN VDE 0530 Part 1. Supplementary sheet. Curve 2. is according to a manufacturer questionnaire and curve 3,4 is special machine designs for high voltage.

Fig. 3.1 Phase-Phase voltage peaks versus voltage rise time /11/.

Curve 1 is in /11/ judged as too pessimistic and this curve is therefore not used as reference. From the results shown in Fig. 3.1 curve 2 the resonant converter should generate phase-phase voltage peaks less than 1300 [V] and with a dv/dt lower than 1300 [V/ $\mu$ s], this curve is used as

<sup>&</sup>lt;sup>1</sup>Zentralverband Elektrotechnik- und Elektroindustrie, ZVEI

reference. Lower dv/dt can be desirable where long cable can cause voltage reflections.

## 3.2 Resonant converter specification

One important feature of the PWM-VSI drives is the simplicity of the converter, only few components besides the switches are necessary. The main current paths in the converter are kept short to decrease stray inductance. Switching speed is set by the converter switches and drive circuits. Examples of rise times and fall times of modern IGBT's aregiven in /10/. Voltage rise times are measured from 70-400 [ns] and fall times from 100 - 1000 [ns] depending on drive circuits of the tested IGBT's. The antiparallel diodes generate also high dv/dt during turn off, and it can be higher than the dv/dt generated by the IGBT. dv/dt of  $10 \text{ [kV/\mu s]}$  has been measured in the laboratory. The dv/dt is minimized by choosing soft turn off diodes.

Short rise times can give voltage reflections and long cables amplify this effect/11/. Some ways of overcoming these problems are:

- An output filter reduces cable loss and insulation stress /12/.

- Integrate the converter as part of the machine /9/.

- Lower the dv/dt generated by the converter voltage

The first solution has some disadvantages, it creates losses and uses space. Second solution solves the problem with voltage reflections due to long cables, but the machine windings are still subject to high dv/dt. Third solution eliminates the problem of VSI converters by designing a converter that generates low dv/dt.

The resonant converter is well-suited for the third solution because it generates low dv/dt. The sinusoidal wave form of the resonant converter makes the combination of switching frequency higher than 20 [kHz] and low dv/dt possible.

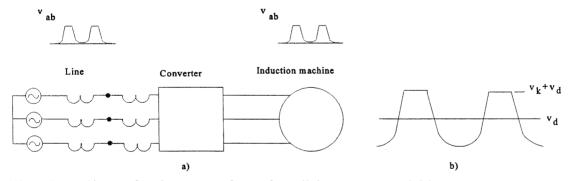

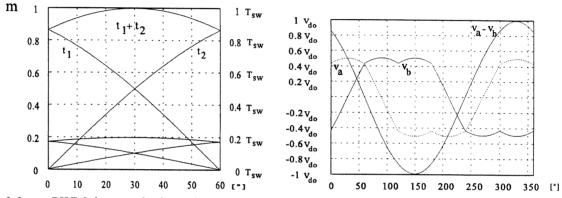

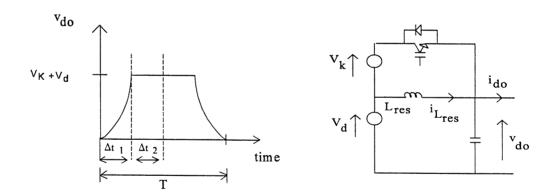

Fig. 3.2 a Shape of voltage wave form of parallel resonant speed drive.

**b** Zoom on resonant voltage wave form.

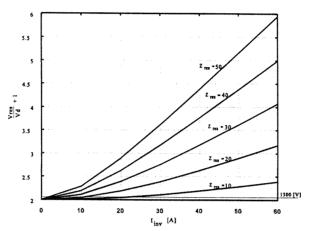

Typical voltage wave forms of the clamped parallel resonant converter are shown in fig. 3.2.a and 3.2.b. The peak voltage is a sum of the clamp voltage and the DC voltage level of the DC link. Clamp voltage  $V_k$  will vary somewhat, in practice from 0.3 $V_d$  to 1.2 $V_d$ , depending on the converter type, Vd is the link DC link voltage.  $V_d = 1.1V_{ab}\sqrt{2}$ ,  $V_d = 620$  [V],  $V_{ab} = 400$  [V] allowing 10 % overshoot.

### Selection of resonant link frequency

It is desirable to have a high switching frequency keeping the voltage quality of the resonant converter competitive with the hard switched PWM converter. The PWM converter switching frequency is often limited by the power dissipation in the power electronic components. A PWM

converter switching frequency of 5 [kHz,] is considered close to the switching frequency used in industrial converters in the power range of 10 [kVA].

The resonant converter must have a link frequency,  $f_{res}$ , at least seven time higher than the PWM- VSI switching frequency,  $f_{sw}/38$ / to have a comparative performance. A factor of  $f_{res}/f_{sw}$ =ten should ensure, the resonant converter using Delta Modulation, a superior output voltage quality at higher modulation index. The demand to the resonant converter is a resonant link frequency of least 50 [kHz].

The converter output dv/dt is determined by the resonant frequency. Is it assumed the resonant circuit is ideal and not loaded, then the maximum output dv/dt is easily calculated. Dv/dt is obtained by differentiating the voltage equation found for the resonant capacitor in appendix A.

$$\frac{dv}{dt} = V_d 2 \pi f_{res}$$

(3.1)

Using a  $V_d$ = 620 [V] and a maximum dv/dt = 1300 [V/ $\mu$ s] the resonant link frequency can be 333 [kHz]. Using a resonant frequency of 50 [kHz], the dv/dt=195 [V/ $\mu$ s].

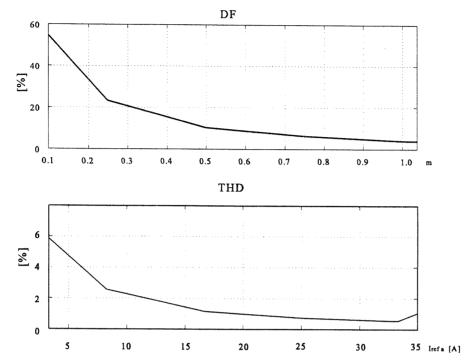

### **Specification**

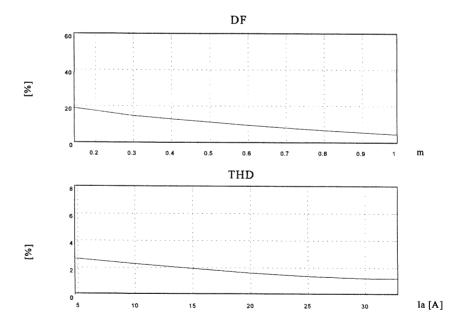

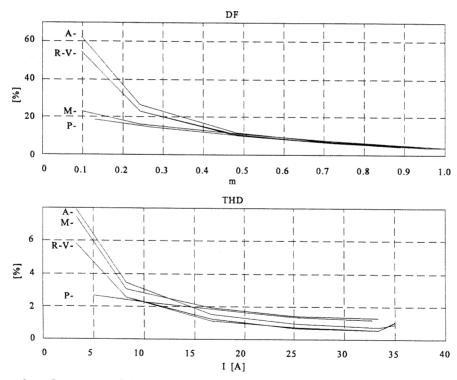

One should expect superior performance from the resonant converter considering dv/dt and switching losses compared to the PWM converter. On voltage and current quality, expressed by DF and THD, defined in App. E, the resonant converter should have almost similar performance as the PWM converter.

The desired specifications for a resonant converter are

- Output voltage, V = 400 [V] RMS

- Link voltage,  $V_d = 620$  [V] including 10% overshoot of input voltage

- Peak output voltage maximum 1300 [V]

- $Dv/dt < 1300 [V/\mu s]$

- Resonant link frequency, f<sub>res</sub> in the area of 50 333 [kHz]

- Distortion factor of inverter output voltage, DF similar to a PWM converter working a 5 [kHz] if the resonant converter link frequency is 50 [kHz].

The selection of converters is done on basis of the fulfilment of the given specifications. Besides this, a set of characteristic parameters is used. The performance and characteristic parameters of converters are plotted into a table in chapter 9. In chapter 10 the table and gained experience are used to select a resonant converter realization.

### 3.3 Conclusion

In the chapter a set of specifications for a resonant converter is selected. The purpose of the specifications is to enable a judgement of the resonant converters, selected for analysis. There is a problem of finding specifications, because the converter application, a speed drive for induction machines, is not very specific. The specifications are found in papers dealing with inverter output voltage influence on induction machines. There are made specifications of DC link voltage level, output voltage dv/dt, resonant link frequency and the output voltage DF should be equal to a 5 [kHz] PWM-VSI.

## 4

## Non clamped parallel resonant converters

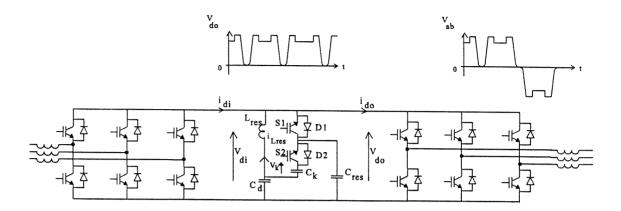

This chapter describes two converters, the first is proposed by Divan /1/ in 1989 and it is called RDCL<sup>1</sup>. Earlier in chapter two, this converter was found to possess a promising approach of applying zero voltage switching in three-phase converters.

The RDCL converter operation is described and the link resonant circuit operation is analyzed. The analysis of the RDCL results in a new converter, the new converter is the second converter described in this chapter. With the second converter it is possible to limit the peak output voltage to two times the DC link voltage and to make the link peak voltage load undependent. The new converter does not introduce extra power devices, the name of the converter is RDCLVPC<sup>2</sup>.

## 4.1 Parallel resonant DC link converter (RDCL)

Parallel resonant DC link converters have an oscillating link voltage as shown in Fig. 2.3. The frequency of the link voltage is ideally given by the natural resonant frequency of the resonant circuit. To obtain zero switching loss of the converter switches, the switches are restricted to switch at the instant the link voltage is zero. To secure zero voltage switching there must be a synchronization between the link oscillations and the inverter switches.

The resonant link oscillation must be sustained over time. If the link oscillation is not sustained, the link voltage  $v_{do}$  might not reach zero voltage, and the zero voltage switching ability is lost. It is necessary to be aware of the factors that influence on the resonant link oscillation.

The resonant link oscillation can be altered by removing or adding energy to the resonant link components. If sufficient energy is removed from the oscillating resonant link, the  $v_{do}$  does not reach zero voltage.

Resonant link energy is changed if the link current  $i_{do}$  changes. If  $i_{to}$  is decreasing, the resonant link energy increases, the resonant link energy could decrease during a resonant period due to the load current. The difference in time constants between the load and the resonant link is huge. Because of the big difference in time constant the  $i_{do}$  only changes little during the resonant period, the increase of resonant link energy due to decreasing load current is small. The resonant link is discharged if the  $i_{do}$  is increasing. Here one must ensure that the resonant link contains enough energy to complete a resonant cycle where  $v_{do}$  reaches zero voltage.

The real world circuit always has losses. The resonant link must therefore be added energy to ensure that the  $v_{do}$  reaches zero voltage. The resonant link energy is normally added in the zero voltage period, and this is done by short circuiting the converter bridge. During the short circuit

Resonant DC Link converter, RDCL

<sup>&</sup>lt;sup>2</sup>Resonant DC Link Voltage Peak Control converter, RDCLVPC

the resonant inductor L<sub>res</sub> is charged.

The huge changes of resonant link energy happen due to the converter switching. The converter switching can impress huge current on the resonant link and this could result in very high  $v_{do}$  amplitudes. The high  $v_{do}$  could be damaging to converter switches and load. The load situations are therefore dealt with in the following paragraphs.

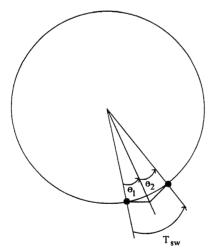

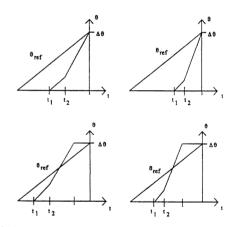

Analyzing the resonant circuit, a time solution of the second order differential equations that describe the voltage and current is often used. Another method is to use the phase plane analyze. Phase plane analy makes it easier to discover general patterns of behaviour. Both the time solution and phase plane analysis are used in this report.

## 4.1.1 Link operation of the RDCL

### **No Load Condition**

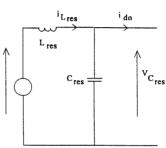

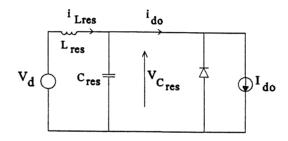

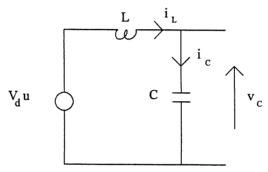

Looking at no load condition, it is the behaviour of the DC link that is at concern. The equivalent circuit used is shown in Fig. 4.1. At no load steady state operation the impact of initial conditions is investigated. An investigation of the initial conditions could lead to a way of controlling the resonant link voltage of the RDCL converter.

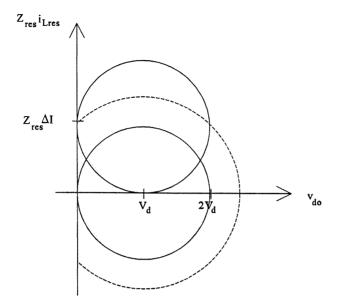

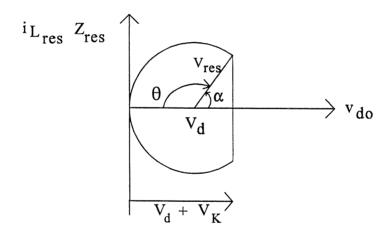

The circuit is subjected to a step voltage  $V_d$  and the initial conditions are given by  $I_{0_{Lres}}$  and  $V_{0_{Cres}}$ . In the phase plane the Fig. 4.1. An equivalent circuit trajectory describes a circle with a radius  $V_{res}$ :

$$V_{res} = \sqrt{(V_{0_{cres}} - V_d)^2 + (Z_{res} I_{0_{res}})^2}$$

(4.1)

in steady state. If a loss element is present, the phase plot trajectories describe a spiral with a shrinking radius.

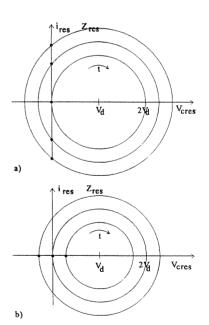

Fig. 4.2.a shows different phase plots at different  $I_{0_{Lres}}$  and  $V_{0_{Cres}} = 0$ . The trajectories begin at  $(v_{Cres}, i_{Lres}Z_{res}) = (0, I_{0_{Lres}}Z_{res})$ .

If the absolute value of  $I_{0_{Lres}}$  increases, the energy absorbed by the resonant circuit increases. It is not possible to decrease  $V_{res}$  to a value lower than  $V_d$  by altering  $I_{0_{Lres}}$ .

Fig. 4.2b shows different phase plots at different  $V_{0_{Cres}}$  and  $I_{0_{Lres}} = 0$ . The trajectories begin at  $(v_{Cres}, i_{Lres} Z_{res}) = (V_{0_{Cres}}, 0)$ , the amplitude of  $V_{0_{Cres}}$  determines the amplitude of  $V_{res}$ .

If  $V_{0_{Cres}}$  is positive, the amplitude of  $V_{res}$  is decreasing because there is less energy in the resonant circuit. Otherwise, if  $V_{0_{Cres}}$  is negative, the  $V_{res}$  is increasing.

Fig. 4.2. Phase plane plots for steady state operation and different initial conditions.

- a) Different initial current

- b) Different initial voltage

In steady operation the trajectories are centered on  $V_d$  at the horizontal axis. In a steady state load situation the trajectories are symmetric around  $i_{do}Z_{res}$ , here  $i_{do}$  is zero.

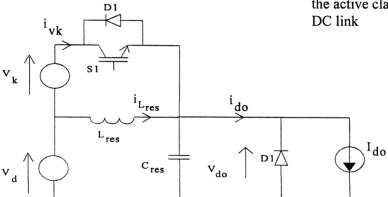

### **Load Condition**

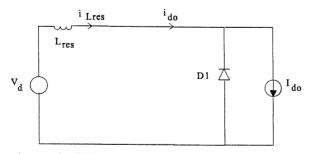

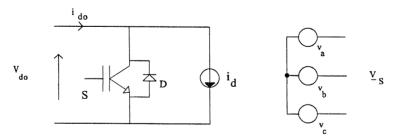

What happens in load situations of the resonant DC link converter link? The three-phase inductive load is assumed to have a time constant so large that the load current is considered constant during a few oscillations of the DC resonant link voltage. The single phase equivalent circuit considered is shown in Fig. 4.3.

A load current  $I_{do}$  is impressed on the resonant cycle. The current change happens at zero voltage ( $v_{Cres} = 0$ ). The component values of the DC voltage and resonant circuit are shown in Table 4.1.

Fig. 4.3. Single phase equivalent of RDCL with load.

| $V_d$ Resonant capacitor ( $C_{res}$ ) Resonant inductor ( $L_{res}$ ) | 600 [V]<br>100 [nF]<br>150 [μΗ] |

|------------------------------------------------------------------------|---------------------------------|

| Load current (I <sub>do</sub> )                                        | 40 [A]                          |

| Resonant impedance $(Z_{res})$ $f_{res}$                               | 38.7 [Ω]<br>41 [kHz]            |

Table 4.1. Specification of parameter values used in simulation shown in Fig. 4.4.

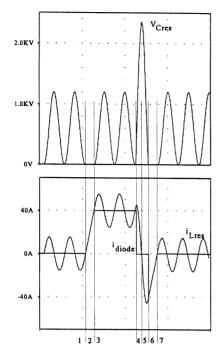

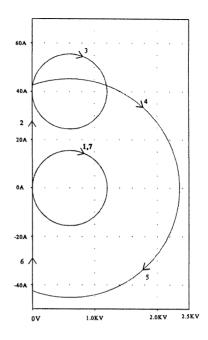

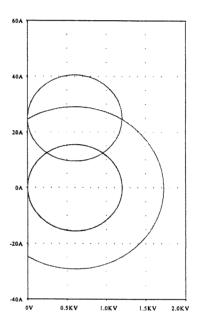

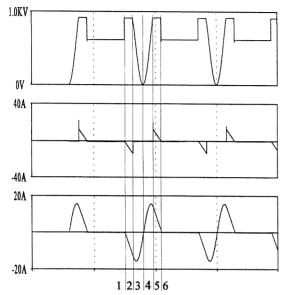

A simulation result is shown in Fig. 4.4a and Fig. 4.4b. It shows  $i_{Lres}$  and  $v_{Cres}$  and a phase-plane plot that shows  $i_{Lres}$  versus  $v_{Cres}$ .

The resonant cycle is divided into seven modes. Initially in mode 1 the resonant circuit is impressed  $V_d$ . The final mode number 7 is identical to mode 1. Between the two modes a current pulse  $(I_{do})$  is impressed.

Fig. 4.4a. A load change in the resonant circuit. Time plots of  $V_{cres}$ ,  $i_{diode}$  and  $i_{Lres}$

**Fig. 4.4b.** Phase plane plots of  $i_{Lres}$  versus  $V_{cres}$

Mode 1 Steady state operation current amplitude value is  $V_d/Z_{res}$ . Voltage amplitude is  $2V_d$  [V]. Phase displacement is  $\phi = \pi/2$  [rad].

Mode 2 When the load current is impressed, the diode D1 forms a current path.  $V_{C_{res}}$  is zero and  $i_{L_{res}}$  is built up at a current rate  $di_{L_{res}}/dt = V_d/L_{res}$  Fig. 4.5 show the components conducting current. The link circuit is no longer forming a resonant circuit. The inductor current increases until it equals the  $I_{do}$  current. Energy is moved from  $V_d$  to  $L_{res}$ ,  $E = \frac{1}{2}L_{res}I_{do}^2$ .

Fig. 4.5. Commutation interval of the resonant circuit.

Mode 3 Then D1 stops conduction,  $V_d$  is across  $L_{res}$ . The y-coordinate of the new circle center is increased to  $I_{do}Z_{res}$ . The phase displacement is given by  $\phi = 2\pi I_{do}/V_d$  [rad].

**Mode 4**  $I_{do}$  changed to a zero value. The initial conditions for the resonant cycle are  $(I_{0_{Lres}} Z_{res} = I_{do} Z_{res})$ ,  $(V_{0_{res}} = 0)$ . Energy stored in  $L_{res}$  is moved to  $C_{res}$  the capacitor is charged and id  $V_{res}$  increased.

**Mode 5** Energy is moved from  $C_{res}$  to  $L_{res}$ .

Mode 6 Diode D1 begins to conduct, energy in  $C_{res}$  is zero. Energy  $E = \frac{1}{2}LI_{do}^2$  earlier absorbed from the source,  $V_d$  is transferred back. Fig. 4.5 shows the components conducting. Note  $I_{do}$ =0.

**Mode** 7 Diode D1 stops conducting and a steady state trajectory with  $V_{res} = V_d$  is obtained.

## 4.1.2 Simulation of RDCL and introduction to SABER

The chapter contains a brief introduction to the simulator and how to build simulation programs. Next a description of the implementation of the RDCL is presented in the simulation program. Simulation results are shown and parameters are extracted.

Simulation of the resonant converter shown in Fig.2.3 is limited to the resonant link and the inverter part. The used simulator deals with models that can describe the real world component behaviour closely. Due to the complexity of the component models, long simulation times are required. The objective of simulation is to gain knowledge about the converter behaviour, adequate to make a comparison to other converter technologies.

It is chosen to use the basic component models in this report. Switches and diodes are equivalent to variable resistors. The three-phase load is a R-L load.

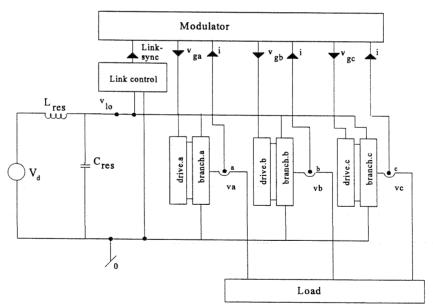

The simulation program, SABER, offers the user a possibility of building a simulation program from modules. The modules contain standard components and the users own algorithms and control actions. Very often different converter topologies consist of the same modules. Some modules are even the same at different converters. When developing the converter simulation program, each converter is divided into modules in such a way the modules can be used in other converters. The RDCL converter is shown in Fig. 4.6 using the modules implemented in the simulation program.

Fig. 4.6. Components and modules used in simulation of the RDCL converter.

The function of each module is described. The link\_control module generates the signal that synchronizes the zero voltage link state with the switching of the inverter switches. The drive modules have the same function as a real drive circuit. The ideal switches can easily be replaced by an advanced IGBT model.

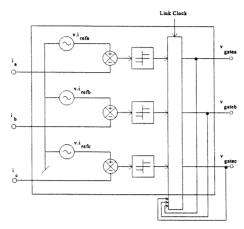

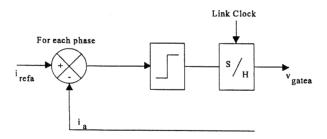

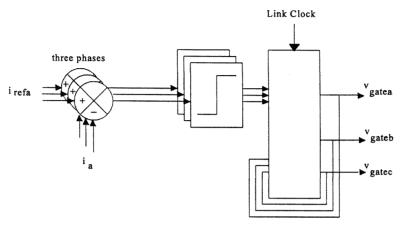

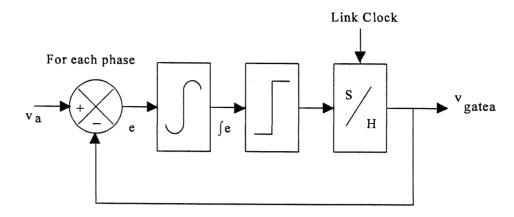

The implemented modulation is an ASCM<sup>3</sup> described in 8.1.2. Fig. 4.7 shows the modulator module.

Fig. 4.7. Current regulated delta modulator module.

The converter data for the simulation are shown in Table 4.2.

| $V_d$ Load impedance Resonant capacitor ( $C_{res}$ ) Resonant inductor ( $L_{res}$ ) | 620 [V]<br>7.6 [ <b>Ω</b> ]<br>150 [nF]<br>60 [μH] |

|---------------------------------------------------------------------------------------|----------------------------------------------------|

| Resonant impedance $(Z_{res})$ $f_{res}$ $f_1$                                        | 20 [Ω]<br>53.5 [kHz]<br>50 [Hz]                    |

Table 4.2 Converter data used in simulation of RDCL

The resonant link component values are selected in appendix B.

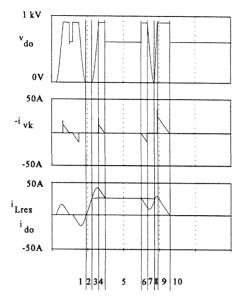

The RDCL converter is simulated for two fundamental periods of 50 [Hz]. The simulation time of 40 [ms] was about 25 [min]. The simulation was carried out on an HP735-99 [MHz] work station.

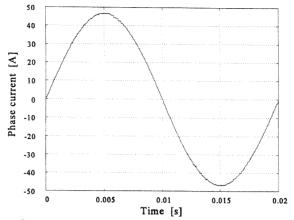

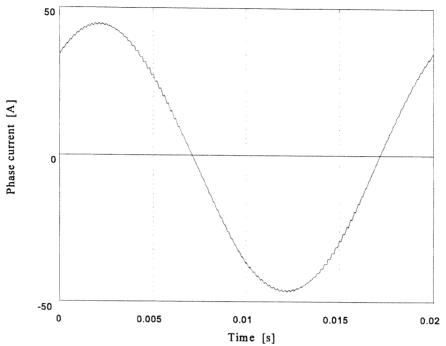

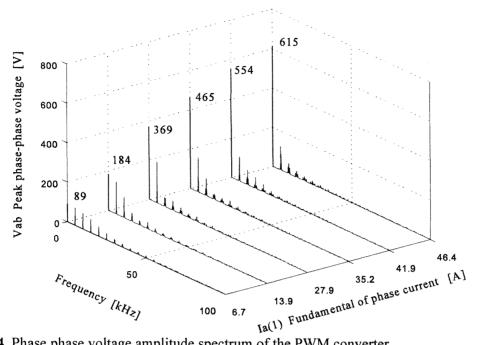

The modulation index  $m = \hat{V}_{ab}/V_d$  is changed from 0.1 to 1.05, with the load impedance of 7.6  $[\Omega]$  there is the following realationship between the phase current and modulation index.

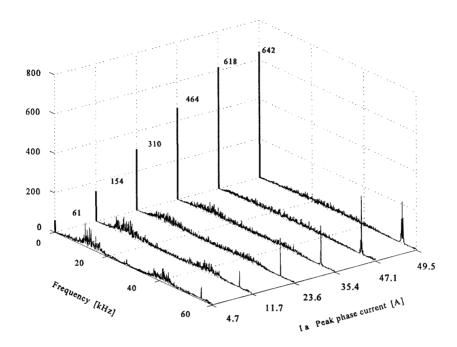

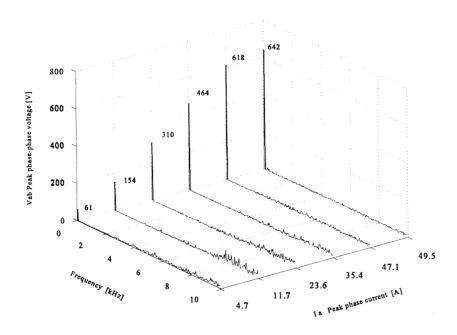

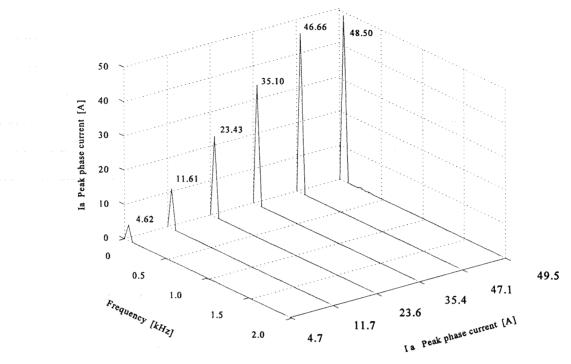

| 1 <sub>a</sub> [A] | 4.7 | 11.7 | 23.6 | 35.4 | 47.1 | 49.5 |

|--------------------|-----|------|------|------|------|------|

| m                  | 0.1 | 0.25 | 0.5  | 0.75 | 1.0  | 1.05 |

<sup>&</sup>lt;sup>3</sup>Adjacent State Current Modulator, ASCM

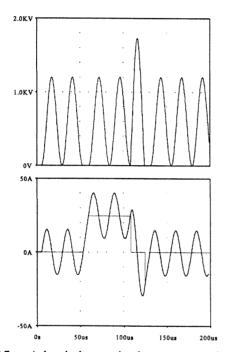

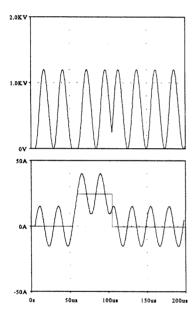

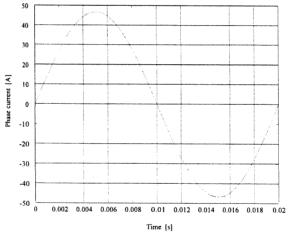

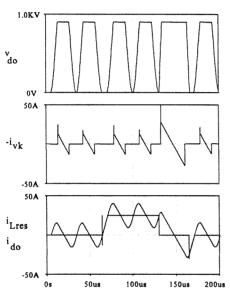

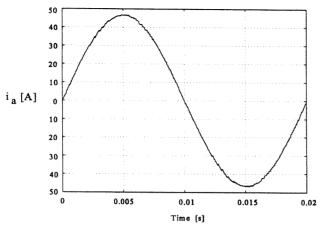

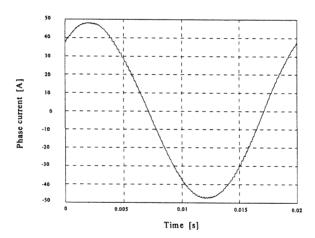

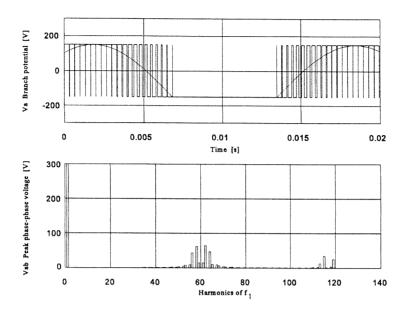

Fig. 4.8 Phase current of RDCL converter

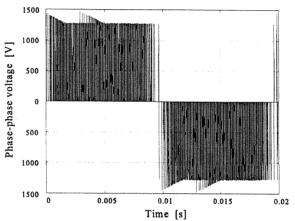

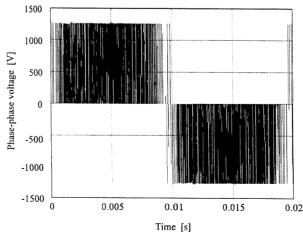

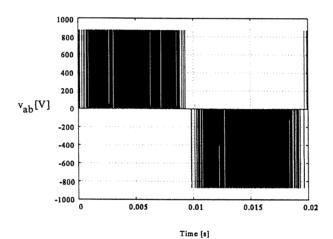

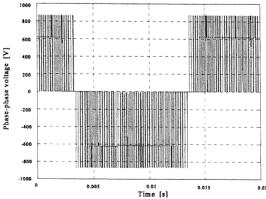

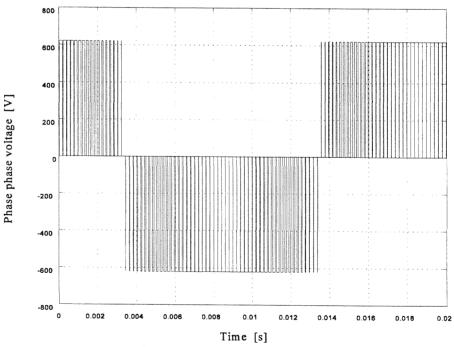

Fig 4.9 Phase-phase voltage of RDCL converter

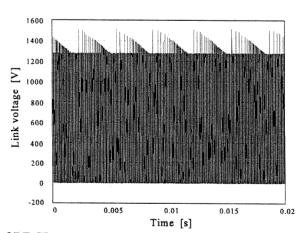

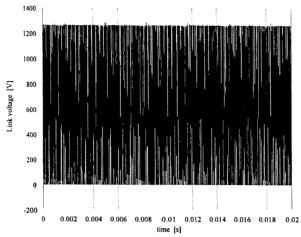

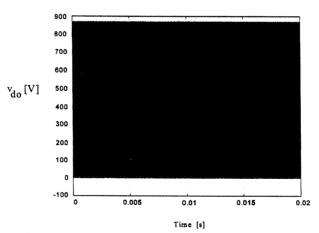

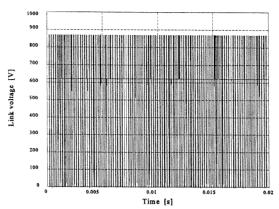

4.10 Link-voltage of RDCL converter

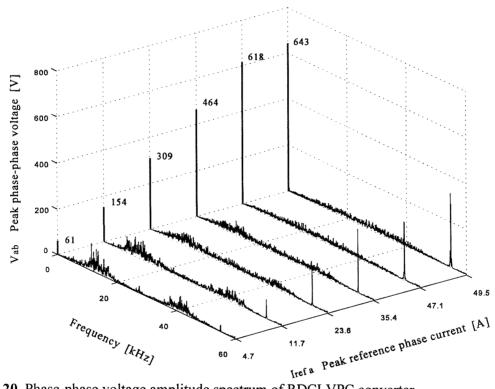

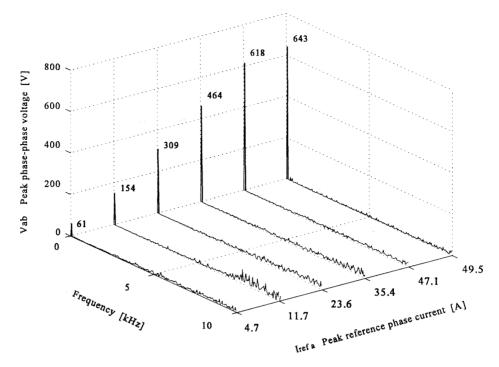

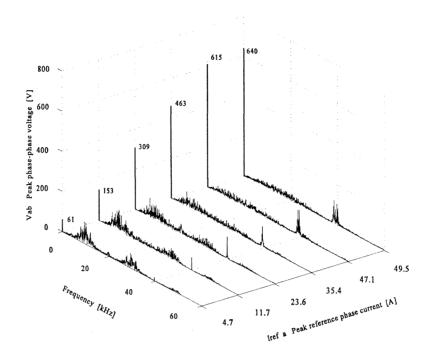

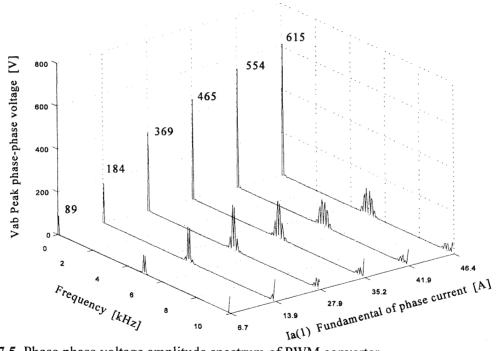

Fig 4.11 Phase-phase voltage amplitude spectrum of RDCL converter

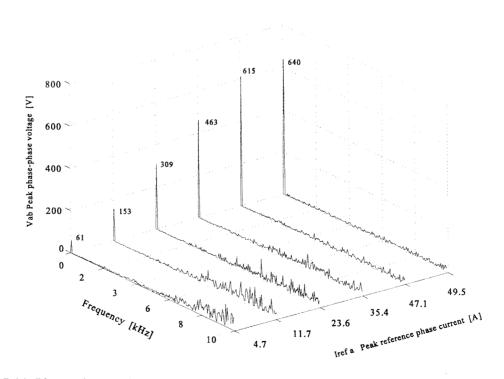

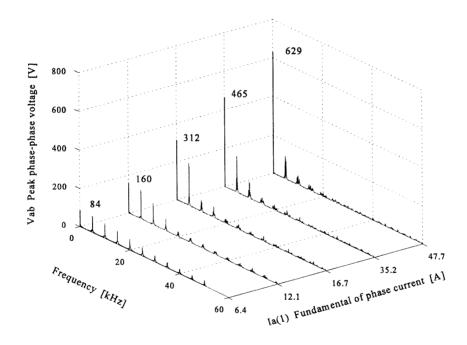

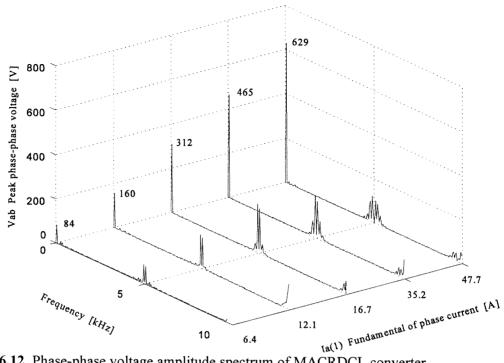

Fig. 4.12 Phase-phase voltage amplitude spectrum of RDCL converter

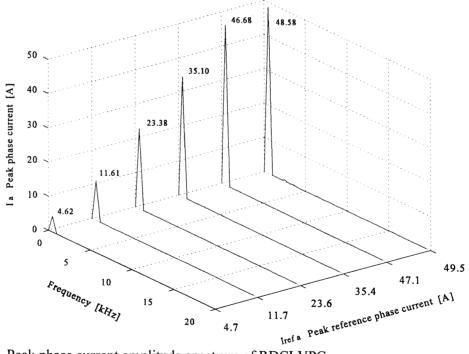

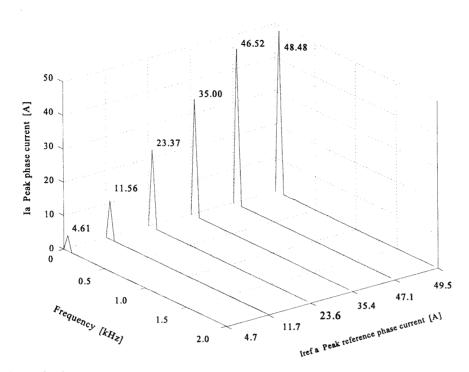

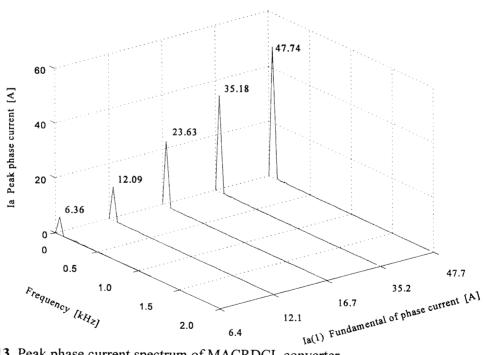

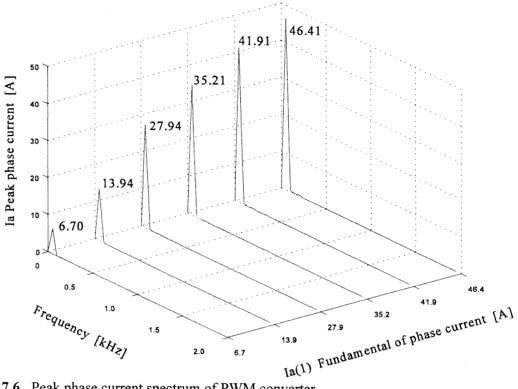

Fig. 4.13 Peak phase current amplitude spectrum of RDCL

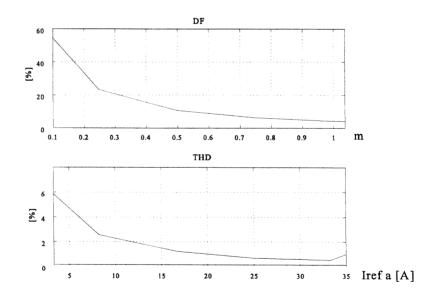

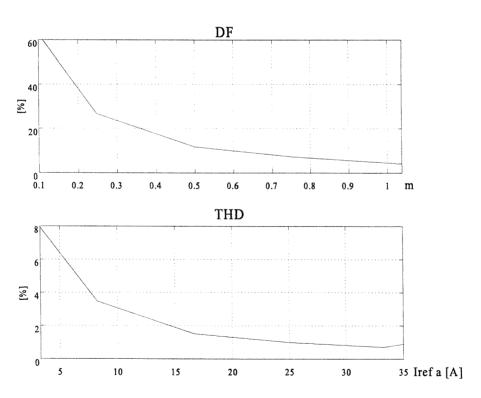

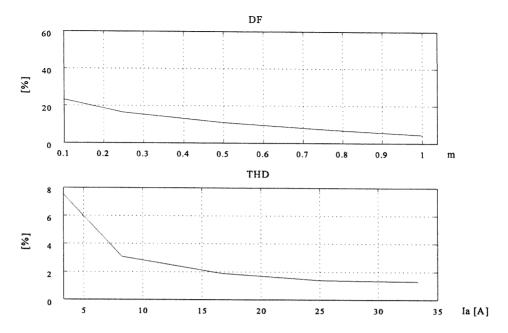

**Fig. 4.14** DF and THD of the RDCL as function og modulation index and the effective phase current.

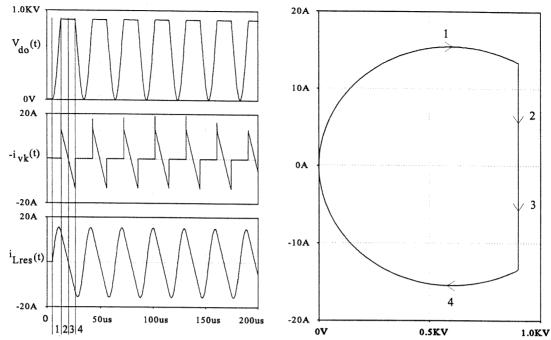

| I <sub>eff</sub> phase a                            | 33.01 [A] |

|-----------------------------------------------------|-----------|

| I <sub>eff</sub> phase a ref.                       | 33.30 [A] |

| $V_{(1)}$ fundamental of $v_{ab}$ , $V_d = 620 [V]$ | 618 [V]   |

| V <sub>lo</sub> peak link voltage amplitude         | 1519 [V]  |

| DF                                                  | 4.28 [%]  |

| THD                                                 | 0.54 [%]  |

| Cos (φ)                                             | 0.8       |

**Table 4.3** Calculated key numbers from the converter simulation.

#### 4.1.3 Discussion

The description of the RDCL converter link has shown that at no load the resonant link voltage oscillates between 0 and 2V<sub>d</sub> using the proper initial conditions. This gives the opportunity of turning the inverter switches on/off at zero voltage and in this way eliminating the switching losses. If the resonant link is loaded, it is still possible to obtain the zero voltage condition but the peak voltage is dependent on the load current. A high load current change generates a high resonant voltage peak which for the simulated converter was 1519 [V] at nominal current. It is desirable to make the link voltage peak undependent of the load current. The peak voltage can be limited by selection a low resonant impedance but peak current is then increased. It is discovered that a way to control the link voltage is to select proper initial conditions of the resonant capacitor voltage. This way of controlling the link voltage peak is investigated further in the chapter 4.2. The RDCL output voltage load dependency is properly also generating subharmonic due to the voltage changes, but due to the long simulation time this is not investigated further. The frequency spectrum of the output voltage shows that there are switching frequencies below 3 [kHz], and this is quite typical for this type of modulator used, but considered the average switching frequency is around 20 [kHz], this is not good compared to PWM converters. Therefore, in chapter 6 the possibility of making a resonant PWM converter is investigated.