# **Aalborg Universitet**

A Compact P Contact Resistance Model for Characterization of Substrate Coupling in Modern **Lightly Doped CMOS Processes**

Shen, Ming; Mikkelsen, Jan H.; Jensen, Ole Kiel; Larsen, Torben

Published in:

European Microwave Week 2012 Conference Proceedings

Publication date: 2012

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Shen, M., Mikkelsen, J. H., Jensen, O. K., & Larsen, T. (2012). A Compact P Contact Resistance Model for Characterization of Substrate Coupling in Modern Lightly Doped CMOS Processes. In *European Microwave* Week 2012 Conference Proceedings EuMA.

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: July 03, 2025

Permission from European Microwave Association must be obtained for non-personal use of this file. It includes reprinting/republishing this material for advertising or promotional purposes, creating new collective works for resale or redistribution to servers or lists, or reuse of any copyrighted components of this work in other works.

# A Compact P<sup>+</sup> Contact Resistance Model for Characterization of Substrate Noise Coupling in Modern Lightly Doped CMOS Processes

Ming Shen, Jan H. Mikkelsen, Ole K. Jensen and Torben Larsen Department of Electronic Systems, Aalborg University, Aalborg 9220, Denmark

Abstract—Compact modeling of P<sup>+</sup> contact resistances is important for characterization of substrate noise coupling in mixed-signal System on Chips (SoCs). Existing contact resistance models can handle uniformly doped bulk or epitaxial substrates. However, compact contact resistance models feasible for modern lightly-doped CMOS processes with P-well layers are still unavailable. This paper presents a new compact resistance model aiming at solving this problem. A Conformal Mapping(CM) method was used to derive the closed-form expressions for the resistances in the model. The model requires no fitting factors, and it is scalable to layout/substrate parameters. The proposed model can also be used to predict noise coupling in terms of S-parameters. The model validation has been done by both EM simulations and measurements, and satisfactory agreement is found between the modeled and measured resistances as well as S-parameters.

#### I. INTRODUCTION

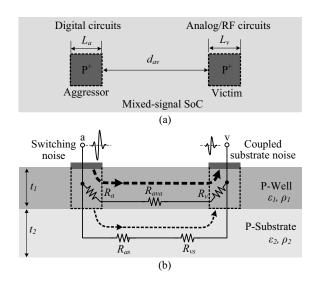

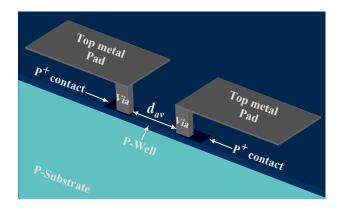

The growing demand for powerful yet low cost electronic devices has resulted in an increasing need for mixed-signal System-on-Chips (SoCs). SoCs require mixed integration of both digital circuits and analog/RF circuits on the same chip. However, the analog circuits in mixed-signal SoCs often suffer from substrate noise interference generated by the digital circuits [1]. Substrate noise coupling through P<sup>+</sup> contacts is one of the three most significant noise coupling mechanisms leading to the interference [2], [3]. Fig. 1 illustrates the coupling between P+ contacts located in digital and analog circuits on a mixed-signal SoC. The switching noise generated by the digital circuits is coupled through the P<sup>+</sup> contact (Aggressor) into the P-well and substrate. This noise propagates to reach analog circuits sharing the same substrate, here represented as a P<sup>+</sup> contact (Victim), and deteriorate the circuit performance. Compared to other coupling mechanisms, including the source/drain-bulk junction capacitive coupling and impact ionization caused by hot electron effects, the coupling effect of P<sup>+</sup> contacts is much more significant for current CMOS processes and is expected to remain so for future technologies [3], [4]. Various modeling approaches have been proposed and they can be categorized into two groups: electromagnetic methods and compact models [1], [3], [5]–[8]. Compact models can provide the insights into the dependence of the coupling on the layout/substrate parameters. Owing to its scalable feature compact models are efficient for large scale SoCs and consequently has attracted significant research attention [1], [3], [8].

Fig. 1. (a) Top-view and (b) cross section view of two  $P^+$  contacts implemented using a modern lightly doped CMOS process with a P-well layer. The proposed circuit model for the structure is also shown.

Compact contact resistance models for substrate noise characterization were proposed as early as 1993 [1]. However the early models are only feasible for epitaxial substrates. Another model, proposed in 2006, is able to handle both epitaxial and uniform bulk substrates [3]. However, it requires three fitting factors that need to be extracted from measurements. Thus the noise analysis has to be postponed to the postlayout design stage, resulting in longer design cycle and higher costs. One of the latest compact contact resistance models was proposed in 2007 [8]. It needs no fitting factors and can be used for both uniform bulk and epitaxial substrates. However, it is still infeasible for modern standard lightly doped CMOS processes that are increasingly used for mixedsignal SoCs. Unlike uniform bulk or epitaxial substrates, lightly doped substrates of standard CMOS processes have a thin P-well layer on the P-substrate (Fig. 1(b)). The Pwell layer introduces a current constriction effect which has significant impact on the coupling between the P<sup>+</sup> contacts [9]. Existing compact contact resistance models do not include the parameters of the P-well  $(\rho_1, \epsilon_1)$  and  $t_1$ ), and therefore can not effectively characterize the coupling. To obtain accurate coupling predictions and help the SoC designers solve the

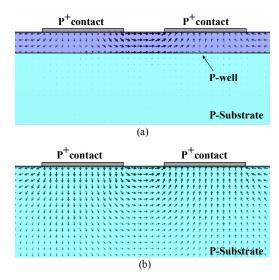

Fig. 2. The cross section view of the simulated currents between two P<sup>+</sup> contacts on (a) a typical lightly doped CMOS process with a P-well layer and (b) on a uniform bulk substrate. The parameters used for the simulation are:  $L_a=20~\mu\mathrm{m},~L_v=20~\mu\mathrm{m},~d_{av}=10~\mu\mathrm{m},~t_1=5~\mu\mathrm{m},~t_2=200~\mu\mathrm{m},~\rho_1=0.2~\Omega-\mathrm{cm}$  and  $\rho_2=20~\Omega-\mathrm{cm}$ .

noise issues, new contact resistance models feasible for lightly doped substrates with a P-well layer are highly desired.

This paper proposes a two-port resistive network as shown in Fig. 1(b) to model the resistance between the contacts. The constriction effects introduced by the P-well layer are characterized using a Conformal Mapping approach. The model is based on the investigation of the physical geometry of the contact layout, taking into account all the layout and substrate parameters shown in Fig. 1(b). Thus it requires no fitting factors.

# II. THE CONTACT RESISTANCE MODEL

The proposed circuit model is shown in Fig. 1(b).  $R_{ava}$ ,  $R_{as}$ and  $R_{vs}$  represent the resistances between the dashed surfaces (Fig.1(b)).  $R_a$  and  $R_v$  model the current constriction effects for the aggressor and victim, respectively. The aggressorvictim contact resistance between port a and v,  $R_{av}$ , is divided into two parallel parts (Fig. 1(b)): the resistances in the P-well layer  $(R_a, R_v \text{ and } R_{ava})$  and the resistances in the P-substrate  $(R_{as}, R_{vs})$ . That is  $R_{av} = (R_a + R_{ava} + R_v)||(R_{as} + R_{vs})$ . This is based on the fact that the resistivity of the P-well is usually one or two orders of magnitude lower than that of the P-substrate. Thus the majority of the noise current flows horizontally from the aggressor to the victim in the P-well, while a small part of the current is coupled to the P-substrate at the area beneath the contacts. Fig. 2 illustrates the simulated current flows between two P<sup>+</sup> contacts on a typical lightly doped CMOS process with a P-well layer and on a uniform bulk substrate, respectively. It can be seen that the currents in the case with P-well are remarkably constricted in the Pwell layer, while the currents in the case without P-well are spreading in a much larger region in the P-substrate [10].

To simplify the analysis, his paper approximates the layout

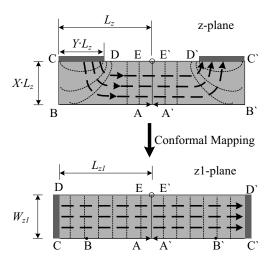

Fig. 3. Conformal mapping for the calculation of the constriction resistance of a contact on a thin film.

of the square contacts in Fig. 1 using circular contacts. The approximation is based on the condition that the circular contacts have the same area as the corresponding square contacts. That is  $r_a = L_a/\sqrt{\pi}$  and  $r_v = L_v/\sqrt{\pi}$ , where  $r_a$  and  $r_v$  are the radii of the circular contacts approximating the square aggressor and victim contact (with side length  $L_a$  and  $L_v$ ), respectively. The same approximation has been widely used in previous work, and it has been proven that the approximation error is acceptable for practical use [8].

# A. Calculating $R_{ava}$ , $R_a$ and $R_v$

Based on the contact approximation, the dashed blocks in the P-well are approximated as two cylinders with radii of  $r_a$  and  $r_v$ , respectively. As the relationship  $R=\rho_1\epsilon_1/C$  stands for homogeneous mediums, the resistance between the lateral surfaces of the cylinders  $(R_{ava})$  can be easily derived from the capacitance between the surfaces [11]

$$R_{ava} = \frac{\rho_1}{2\pi t_1} \operatorname{acosh} \left[ \frac{1}{2} \left( \frac{D^2}{r_a r_v} - \frac{r_a}{r_v} - \frac{r_v}{r_a} \right) \right], \quad (1)$$

where  $D=d_{av}+r_a+r_v$ .  $\rho_1$  and  $t_1$  are the resistivity and thickness of the P-well, respectively. It should be noted that  $R_{ava}$  in (1) does not include the constriction resistances ( $R_a$  and  $R_v$ ) in the areas close to the contacts. In this paper, this error is corrected by equivalently extending the real distance  $(d_{av})$  with an equivalent distance  $L_e$  for each of the contacts. This is achieved using a Conformal Mapping approach.

The top figure in Fig. 3 shows the cross section view of two identical co-planar contacts (C-D and C'-D') on a conductive layer.  $L_z$  represents half of the distance between the contacts plus the side length of the contacts. X and Y represent the ratio of the contact width and the thickness of the conductive layer. Simple expressions for the current flow lines (long dashed lines with arrows) and the equipotential surfaces (short dashed lines) at the constriction areas are usually unavailable in the original plane z [12], [13]. Hence the resistance between the two contacts can not be easily

derived. However, using Conformal Mapping, the contacts in the z-plane can be mapped to a new plane z1 (bottom figure in Fig. 3) with new distance  $L_{z1}$  and contact width  $W_{z1}$ , where the structure is simple and the resistance can be easily derived. Since the mapping is conformal, the current flows and equipotential surfaces are kept perpendicular to each other. This guarantees that the resistance value between the contacts in the z1-plane is the same as that in the z-plane. Therefore the equivalent distance for constriction resistance correction of the contact C-D can be easily found as

$$L_e = XL_zL_{z1}/W_{z1} - (1 - Y)L_z. (2)$$

In the case of X << 1, and Y < 0.5,  $L_e$  can be approximated as [12], [13]

$$L_e \approx \frac{Y}{X} - \frac{2}{\pi} \ln \left[ \sinh(\frac{Y\pi}{2X}) \right],$$

(3)

and for the case of X<<1, and Y>0.5,  $L_e$  can be approximated as [13]

$$L_e \approx K(p)/K'(p) - (1 - Y)/X,$$

(4)

where K is the complete elliptic integral of first kind and  $p = \tanh[\pi(1-Y)/2X]$ . In addition,  $K'(k) = K(\sqrt{1-k^2})$ .

Using (1) and (3) or (4) the resistance between the contacts in the P-well  $(R_{avw}=R_a+R_v+R_{ava})$  in Fig. 1(b) can be found by

$$R_{avw} \approx \frac{\rho_1}{2\pi t_1} \operatorname{acosh} \left[ \frac{1}{2} \left( \frac{D_1^2}{r_a r_v} - \frac{r_a}{r_v} - \frac{r_v}{r_a} \right) \right],$$

(5)

where  $D_1 = d_{av} + L_{ea} + L_{ev} + r_a + r_v$  is the extended distance between the contacts.  $L_{ea}$  and  $L_{ev}$  are the equivalent distances to correct the constriction resistances  $(R_a \text{ and } R_v)$  for the aggressor and victim, respectively.

## B. Calculating $R_{as}$ and $R_{vs}$

A typical P-substrate is usually two or three orders thicker than the P-well . Thus the current in the P-substrate spreads over a much larger region than the thin P-well (Fig. 2(a)). This leads to different calculations of  $R_{as}$  and  $R_{vs}$  compared to the case of  $R_{ava}$ . A simple expression of the contact spreading resistance on a uniform bulk substrate has been reported in [8]. It is used here to calculate the contact spreading resistances in the P-substrate:

$$R_{as} \approx \frac{\rho_2}{4r_a} \left[ 1 - \frac{2}{\pi} asin \left( \frac{r_a}{r_a + d_{av}} \right) \right].$$

(6)

Similarly,  $R_{vs}$  is formed using the same expression as (6) for  $R_{as}$  with  $r_a$  replaced by  $r_v$ .

## III. MODEL VALIDATION

#### A. EM simulation validations

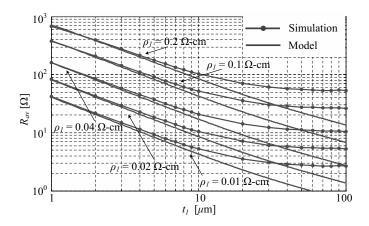

The proposed model has been validated firstly by EM simulations using CST STUDIO SUITE<sup>TM</sup>. The geometry in Fig. 1 is used for the simulations and the modeled and simulated results for substrates with five different P-well resistivities (ranging from  $0.01~\Omega-{\rm cm}$  to  $0.2~\Omega-{\rm cm}$ ) are shown in Fig. 4.

Fig. 4. Modeled and EM-simulated contact resistance versus thickness of the P-well. The parameters used for the simulation are:  $L_a=20~\mu\mathrm{m}$ ,  $L_v=40~\mu\mathrm{m}$ ,  $d_{av}=20~\mu\mathrm{m}$ ,  $t_2=200~\mu\mathrm{m}$  and  $\rho_2=20~\Omega\mathrm{-cm}$ .

TABLE I PROCESS PARAMETERS

|             | t [ $\mu$ m] | $\epsilon/\epsilon_0$ | $\rho [\Omega\text{-cm}]$ |

|-------------|--------------|-----------------------|---------------------------|

| P-Well      | 1.2          | 12                    | 0.11                      |

| P-Substrate | 300          | 12                    | 20                        |

It can be seen that the modeled resistances match the simulated results very well especially for small thicknesses. The relative error is <5% when the thickness is less than  $5\,\mu \rm m$ , which is the case for most currently available lightly doped CMOS processes [9]. For relatively thicker P-wells, deviations between the modeled and simulated results are observed. This is because the approximation of horizontal current flow in the P-well layer is less accurate for thick P-well layers. The results shown in the figure also indicate that this model can be used for a wide range of substrates with different resistivities.

#### B. Experimental validations

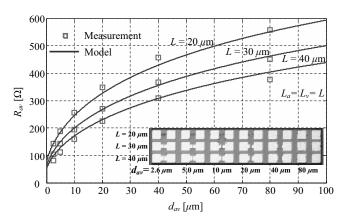

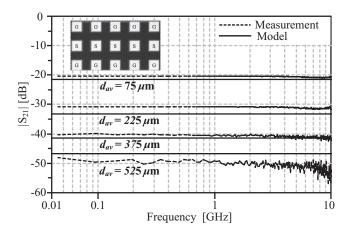

Two test chips fabricated using a standard 0.18  $\mu$ m CMOS process were used to validate the proposed model. The process parameters are given in Table I. The microphotographs of the test chips for verification of contact resistances and noise coupling in terms of S-parameters are shown in the embedded figures in Fig. 6 and Fig. 7, respectively. Pads on top metal layer are used for on-wafer resistance and S-parameter measurements. An example of the 3-D layout of the test fixture (cross section view) is shown in Fig. 5. The aggressor and victim contacts are connected to the pads on the top metal layer (metal-6) using vias. As the resistivities of the vias and metal pads are remarkably lower than those of the P-well and P-substrate, their resistances are neglected in the measurements.

The measured and calculated contact resistances versus distance of  $P^+$  contact pairs with three different side lengths are shown in Fig. 6. It can be seen that the agreement between the modeled and the measured results is fairly good. The relative estimation error is less than 6.5% for all the results. Fig. 7 shows the measured and calculated  $|S_{21}|$  between contact pairs with four different distances. As shown in the embedded figure

Fig. 5. The cross section view of an example layout showing the connection of the  $P^+$  contacts to the measurement pads.

Fig. 6. Measured and modeled resistances versus distance of P<sup>+</sup> contacts with different side lengths. The embedded figure is the microphotograph of the test chip. The parameters of the CMOS process are:  $t_1=1.2~\mu m,\, t_2=300~\mu m,\, \rho_1=0.11~\Omega-{\rm cm}$  and  $\rho_2=20~\Omega-{\rm cm}$ .

in Fig. 7, G-S-G pads are used for S-parameter measurements. The connection of the contacts to the top metal signal pads is the same as shown in Fig. 5. The ground pads only consist of metal-6 and are connected using two  $10\text{-}\mu m$  wide metal-6 strip lines. Fig. 7 shows that the calculated results have quite good agreement with the measured results. The predict error of the coupling is within 5 dB for the results except for the case of  $d_{av}=525~\mu m$  from 3 to 10 GHz. It should be noted that the coupling for this case is very weak (-50 dB), and the relatively big error might be due to the lower measurement accuracy for weak coupling signals.

#### IV. CONCLUSION

A compact resistance model for  $P^+$  contacts is proposed in this paper. The model can handle lightly doped substrates with a thin P-well layer, which are common in modern deep submicron CMOS processes for the implementations of mixed-signal SoCs. The model is scalable to layout/substrate parameters, while requiring no fitting factors. Test chips fabricated using a standard 0.18  $\mu$ m CMOS process have been used for experimental verifications. Measured results show that the modeled contact resistances are accurate with estimation errors less than 6.5%. It has also been demonstrated that the noise

Fig. 7. Measured and modeled  $|S_{21}|s$  of P<sup>+</sup>contact pairs with different distances. The side lengths for the aggressor and victim are both 75  $\mu m$  The embedded figure shows the layout of the test chip.

coupling of contacts in mixed-signal SoCs can be accurately predicted using this model. This can be useful to solve the substrate noise issues in the early SoC design stage and reduce the design cost.

#### REFERENCES

- D. Su, M. Loinaz, S. Masui, and B. Wooley, "Experimental Results and Modeling Techniques for Substrate Noise in Mixed-Signal Integrated Circuits," *IEEE J. Solid-State Circuits*, vol. 28, no. 4, pp. 420–430, Apr. 1993

- [2] C. Mohamed, B. Barelaud, and E. Ngoya, "Physical Analysis of Substrate Noise Coupling in Mixed Circuits in SoC Technology," in Proc. European Microwave Integrated Circuits Conference (EuMIC), Paris, France, Sep. 2010, pp. 274 –277.

- [3] H. Lan, T. Chen, C. Chui, P. Nikaeen, J. Kim, and R. Dutton, "Synthesized Compact Models and Experimental Verifications for Substrate Noise Coupling in Mixed-Signal ICs," *IEEE J. Solid-State Circuits*, vol. 41, no. 8, pp. 1817–1829, Aug. 2006.

- [4] M. Badaroglu, P. Wambacq, G. Van der Plas, S. Donnay, G. Gielen, and H. De Man, "Impact of Technology Scaling on Substrate Noise Generation Mechanisms," in *Proc. IEEE Custom Integrated Circuits Conf. (CICC04), San Jose, CA*, Oct. 2004, pp. 501 504.

- [5] N. Verghese and D. Allstot, "Computer-aided Design Considerations for Mixed-Signal Coupling in RF Integrated Circuits," *IEEE J. Solid-State Circuits*, vol. 33, no. 3, pp. 314 –323, Mar. 1998.

- [6] R. Gharpurey and R. Meyer, "Modeling and Analysis of Substrate Coupling in Integrated Circuits," *IEEE J. Solid-State Circuits*, vol. 31, no. 3, pp. 344–353, Mar. 1996.

- [7] A. van Genderen, N. van der Meijs, and T. Smedes, "Fast Computation of Substrate Resistances in Large Circuits," in *Proc. European Design* and Test Conference, Paris, France, Mar. 1996, pp. 560 –565.

- [8] S. Kristiansson, F. Ingvarson, and K. Jeppson, "Compact Spreading Resistance Model for Rectangular Contacts on Uniform and Epitaxial Substrates," *IEEE Trans. Electron Devices*, vol. 54, no. 9, pp. 2531– 2536, Sep. 2007.

- [9] S. Hazenboom, T. Fiez, and K. Mayaram, "A Comparison of Substrate Noise Coupling in Lightly and Heavily Doped CMOS Processes for 2.4-GHz LNAs," *IEEE J. Solid-State Circuits*, vol. 41, no. 3, pp. 574 – 587, Mar. 2006.

- [10] G. Norberg, S. Dejanovic, and H. Hesselbom, "Contact Resistance of Thin Metal Film Contacts," *IEEE Trans. Compon. Packag. Technol.*, vol. 29, no. 2, pp. 371 –378, Jun. 2006.

- [11] D. Cheng, "Field and Wave Electromagnetics," 2nd ed. Prentice Hall, 1989.

- [12] P. Hall, "Resistance Calculations for Thin Film Patterns," *Thin Solid Films*, vol. 1, no. 4, pp. 277–295, Jan. 1968.

- [13] —, "Resistance Calculations for Thin Film Rectangles," *Thin Solid Films*, vol. 300, no. 1, pp. 256–264, May 1997.