### **Aalborg Universitet**

### **Real-time specifications**

David, A.; Larsen, K.G.; Legay, A.; Nyman, Ulrik; Traonouez, L.-M.; Wasowski, A.

Published in:

International Journal on Software Tools for Technology Transfer

DOI (link to publication from Publisher): 10.1007/s10009-013-0286-x

Publication date: 2015

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

David, A., Larsen, K. G., Legay, A., Nyman, U., Traonouez, L.-M., & Wasowski, A. (2015). Real-time specifications. International Journal on Software Tools for Technology Transfer, 17(1), 17-45. https://doi.org/10.1007/s10009-013-0286-x

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

Downloaded from vbn.aau.dk on: September 10, 2024

Software Tools for Technology Transfer manuscript No. (will be inserted by the editor)

## Real-Time Specifications \*

Alexandre David $^1$  and Kim. G. Larsen $^1$  and Axel Legay $^2$  and Ulrik Nyman $^1$  and Louis-Marie Traonouez $^2$  and Andrzej Wąsowski $^3$

- <sup>1</sup> Computer Science, Aalborg University, Denmark, e-mail: adavid@cs.aau.dk, kgl@cs.aau.dk, ulrik@cs.aau.dk

- <sup>2</sup> INRIA/IRISA, Rennes Cedex, France, e-mail: axel.legay@irisa.fr, louis-marie.traonouez@irisa.fr

- <sup>3</sup> IT University of Copenhagen, Denmark, e-mail: wasowski@itu.dk

Received: date / Accepted: date

Abstract A specification theory combines notions of specifications and implementations with a satisfaction relation, a refinement relation, and a set of operators supporting stepwise design. We develop a specification framework for real-time systems using Timed I/O Automata as the specification formalism, with the semantics expressed in terms of Timed I/O Transition Systems. We provide constructs for refinement, consistency checking, logical and structural composition, and quotient of specifications — all indispensable ingredients of a compositional design methodology.

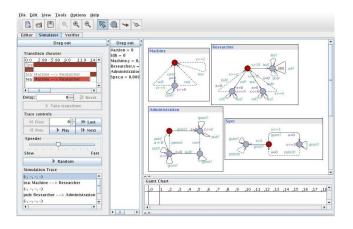

The theory is implemented in the new tool ECDAR. We present symbolic versions of the algorithms used in ECDAR, and demonstrate the use of the tool using a small case study in compositional verification.

**Key words:** Real-time systems, Stepwise-Refinement, Compositional Verification

### 1 Introduction

Many modern systems are big and complex assemblies of numerous components. The components are often designed by independent teams, working under a common agreement on what the interface of each component should be. Consequently, compositional reasoning [41], the mathematical foundations of reasoning about interfaces, is an active research area. It supports inferring properties of the global implementation from the components, or advisedly designing and reusing components.

In a logical interpretation, interfaces are specifications, while components that implement an interface are understood as models/implementations. Specification theories may support various features including (1) refinement, which allows us to compare specifications as well as to replace a specification by another one in a larger design, (2) logical conjunction, expressing the intersection of the set of requirements expressed by two or more specifications, (3) structural composition, which allows us to combine specifications, and (4) a quotient operator that is dual to structural composition. We shall see that quotient is useful to perform incremental design and to reason about assumptions and guarantees. Also, the operations have to be related by compositional reasoning theorems, guaranteeing both incremental design and independent implementability [32].

Building good specification theories is the subject of intensive studies [20,31]. One successfully direction is the theory of interface automata [31, 32, 45, 52]. In this framework, an interface is represented by an input/output automaton [50], i.e. an automaton whose transitions are typed with *input* and *output*. The semantics of such an automaton is given by a two-player game: the input player represents the environment, and the output player represents the component itself. Contrary to the input/output model proposed by Lynch [50], this semantic offers an optimistic treatment of composition: two interfaces can be composed if there exists at least one environment in which they can interact together in a safe way. In [34], a timed extension of the theory of interface automata has been introduced, motivated by the fact that time can be a crucial parameter in practice, for example in embedded systems. While [34] focuses mostly on structural composition, in this paper we go one step further and build a game-based specification theory for timed systems that embeds the four features listed above.

$<sup>^{\</sup>star}$  This paper is an extended version of the work previously presented in [24,23,26]. The main additions are (1) a unified presentation, (2) a deeper link between the theory and the tool, (3) proofs of theorems, and (4) the description of case studies.

We represent specifications by timed input/output automata [42], i.e., timed automata whose sets of discrete transitions are split into input and output transitions (see Section 4). Contrary to [34] and [42], we distinguish between implementations and specifications by adding conditions on the models. This is done by assuming that the former have fixed timing behaviour and they can always advance either by producing an output or delaying. We also provide a game-based methodology to decide whether a specification is consistent, i.e. whether it has at least one implementation. The latter reduces to deciding existence of a strategy that despite the behaviour of the environment will avoid states that cannot possibly satisfy the implementation requirements.

Our theory is equipped with a refinement relation (see Section 5). Roughly speaking, a specification  $S_1$  refines a specification  $S_2$  iff it is possible to replace  $S_2$ with  $S_1$  in every environment and obtain an equivalent system that satisfies the same specifications. In the input/output setting, checking refinement reduces to deciding an alternating timed simulation between the two specifications [31]. In our timed extension, checking such simulation can be done with a slight modification of the theory proposed in [15]. As implementations are specifications, refinement coincides with the satisfaction relation. Our refinement operator has the model inclusion property, i.e.,  $S_1$  refines  $S_2$  iff the set of implementations satisfied by  $S_1$  is included in the set of implementations satisfied by  $S_2$ . We also propose a logical conjunction operator between specifications (see Section 6). Given two specifications, the operator will compute a specification whose implementations are satisfied by both operands. The operation may introduce error states that do not satisfy the implementation requirement. Those states are pruned by synthesizing a strategy for the component to avoid reaching them. We also show that conjunction coincides with shared refinement, i.e., it corresponds to the greatest specification that refines both  $S_1$  and  $S_2$ .

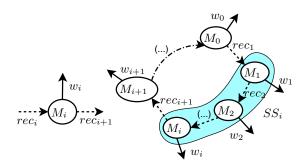

Following [34], specifications interact by synchronizing on inputs and outputs. However, like in [42,50], we restrict ourselves to input-enabled systems. This makes it impossible to reach an immediate deadlock state, where a component proposes an output that cannot be captured by the other component. Here, in checking for compatibility of the composition of specifications, one tries to synthesize a strategy for the inputs to avoid the error states, i.e., an environment in which the components can be used together in a safe way. Our composition operator is associative and the refinement is a precongruence with respect to it (see Section 7). We propose a quotient operator dual to composition (see Section 8). Intuitively, given a global specification T of a composite system as well as the specification of an already realized component S, the quotient will return the most liberal specification X for the missing component, i.e. X is the largest specification such that S in parallel with X refines T.

Our methodology has been implemented in a new tool ECDAR that is an extension of UPPAAL-TIGA [9] (see Section 9). It builds on timed input/output automata, a symbolic representation for timed input/output transition systems. We show that conjunction, composition, and quotienting can be reduced to simple product constructions allowing for both consistency and compatibility checking to be solved using the zone-based algorithms for synthesizing winning strategies in timed games [51, 17. So while our theory is clearly new, our reduction allows us to exploit well-established algorithms and implementations which makes it robust. Finally, refinement between specifications is checked using a variant of the recent efficient game-based algorithm of [15]. The potential of our tool is illustrated on two case studies, each of them showing the utility of the various features of our theory (see Sections 10 and 11).

### 2 Introductory Example

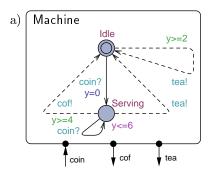

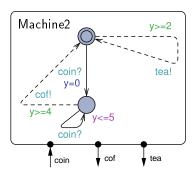

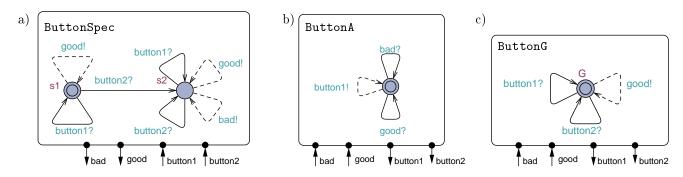

We will now give a rough overview of the theory using an example. Consider a vending machine that can serve tea or coffee. Its specification is shown in Fig. 1(a). We use the syntax of timed I/O automata [42]. The dashed edges represent outputs and the solid ones correspond to inputs. In the example, tea! is an output and coin? is an input. The machine waits for coins and serves either tea or coffee with different timing constraints. It can also serve free tea after two time units. A possible implementation of this machine is given in Fig. 1(b).

Our models share the following characteristics:

- Both specifications and implementations are deterministic. This assumption reflects our experience of working with engineers, who prefer to create deterministic specifications. It also allows to create a theory with good properties for compositional reasoning.

- Output transitions of the implementation Implementation must arrive at a fixed moment in time and cannot be delayed. We say that an implementation is output-urgent. Specifications are allowed to be imprecise about timing of outputs, while implementations have fixed timing. Intuitively, this means that not only the choice of action, but also the timing (of outputs) is deterministic. We do not restrict the timing of inputs as the environment may well be not predictable.

- In Implementation, we can observe that each time the output tea! from Idle to Idle is taken, Clock y is reset. Without this reset, the time would be stopped and the execution would be stuck in the location Idle. A desirable property is that either a component can delay or it must be able to produce some output. This property, called independent progress, guarantees that the progress of time can happen without relying on the environment.

Figure 1: a) Specification of a coffee and tea Machine, b) an implementation that refines the specification and c) a Researcher that uses the Machine. Initial locations are double circled. Transition guards are written in green and clock resets in blue, while location invariants are in purple.

- Both specifications and implementations are assumed to be input-enabled. This is a natural requirement that a component cannot prevent the environment from sending an input. Instead we should be able to describe the failure of the system, when an unexpected input arrives. This assumption is made in many specification theories [49,38,56,61,53].

Implementations relate to specifications through refinement. More precisely, our implementation model Implementation refines our specification Machine in the sense that whenever Implementation wants to produce an output, that output is allowed by Machine, and Implementation accepts all the inputs specified by Machine. Then an implementation is reusable in any environment which accepts the specification. Also an implementation will not produce more interactions than what the specification allows in such an environment. We will see later that checking refinement reduces to a two-player game where the attacker plays delays and outputs on Implementation, and inputs on Machine, while the defender responds with outputs and delays on Machine, and inputs from Implementation.

More generally, the refinement can be used to compare specifications. Thanks to the assumptions of determinism and input-enabledness, our refinement coincides with implementation set inclusion, that is Specification  $A_S$  refines Specification  $A_T$  if and only if the set of implementations of  $A_S$  is included in the set of implementations of  $A_T$ .

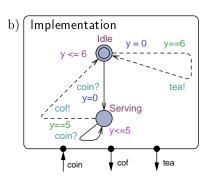

Consider now the specification of UniSpec in Fig. 2. A good university produces patents as a result of receiving grants. Observe the timing constraints that constrain how often the university should produce patents. Our objective is to refine this specification by another one that is more precise regarding the behavior of the researchers and administration staff of the university. We consider researchers who will publish, if provided with tea and coffee, an administration that will turn grants into coins (to fund tea and coffee) while turning publications into patents, and a coffee machine that accepts coins and produces hot beverages for the researchers. In order to reason about each component individually, we will split

Figure 2: Specification of the university component (UniSpec).

the university specification into multiple specifications that we will combine using composition operators. The resulting specification shall then be checked against the original one using refinement.

The specifications for the coffee machine and the researcher are given in figures 1(a) and 1(c), respectively. We assume that researchers publish more efficiently if drinking coffee than when drinking tea. Furthermore, researchers dislike tea, so if tea is served after a long period of waiting (15 units of time) the subsequent behaviour is undefined—supposedly due to irritation. Publications are produced with the output pub!.

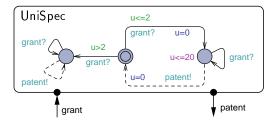

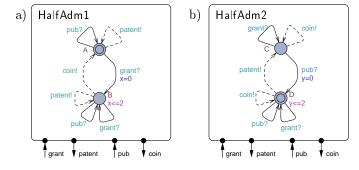

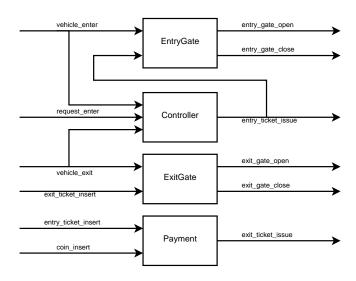

The case of the administration is somewhat more complicated. Indeed, administration should not only turn grants into coins, but also turn publications into patents a conjunction of two requirements. We will model each requirement individually and then compute their conjunction, i.e, the specification that represents the set of their common implementations: Administration is the conjunction of HalfAdm1 and HalfAdm2, both presented in Fig. 3. Observe that both specifications are input enabled and allow patents and coins as outputs. Given grants (grant?), resp. publications (pub?), coins are produced within 2 time units (with coin!), resp. patents (with patent!). In general, conjunction can introduce bad behaviors in specifications, i.e, behaviors that cannot be implemented because they do not respect properties such as independent progress. In our theory such behaviors will be pruned using a game-based technique.

Figure 3: Two conjuncts that together model the Administration component.

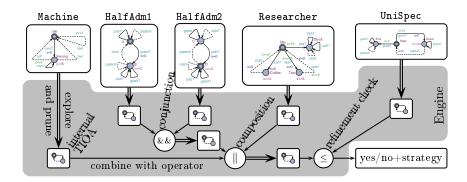

We are now ready to compose our specifications in order to derive a refinement of the university model. Fig. 4 gives the overview of this refinement check. We put in parallel the components for the researcher, the coffee machine, and the administration. Our verification engine then checks if this composition refines the specification of our university. The verification is done in a compositional manner in the sense that every component is explored locally, bad behaviour is eliminated (pruned), and combined with the appropriate operator, shown in the figure.

Slightly surprisingly, the refinement check of Fig. 4 fails. It turns out that since the machine allows the researchers to get free tea, they can publish for free, which can give patents for free—a scenario that has not been anticipated in the specification.

### 3 Related Work

The objective of this section is mainly to survey a stateof-the art for interface theory, not to make an exhaustive list of all existing timed specification theories.

It has been argued [31,27,32] that games constitute a natural model for interface theories: each component is represented by an automaton whose transitions are typed with *input* and *output* modalities. The semantics of such an automaton is given by a two-player game: the input player represents the environment, and the output player represents the component. Contrary to the input/output model proposed by Lynch and Tuttle [50], this semantic offers (among many other advantages) an optimistic treatment of composition: two interfaces can be composed if there exists at least one environment in which they can interact together in a safe way. Gamebased interfaces were first developed for untimed systems [32,28] and implemented in tools such as TICC[2] and CHIC [21] for both synchronous and asynchronous models. The first dense time extension of the theory of interface automata has been developed in [34], motivated by the fact that real time is a crucial parameter in some systems. The theory, which extends timed input/output automata [42], was later implemented in TICC, but using discretized real time only [29]. The idea is similar to the untimed case: components are modeled using timed input/output automata (TIOAs) with a timed game semantics [17]. The theory of [34] has never been completed, in the sense that it lacks support for conjunction and refinement (in contrast to the one presented here). The usefulness of such theories for compositional design of real time systems is thus limited. While tooling is not the focus of this paper, let us mention that, elsewhere [14], we show how the ECDAR tool and our timed interface theory can be used to solve problems that are beyond the scope of classical UPPAAL timed input/automata extensions [13,11].

In [45] Larsen proposes modal automata, which are deterministic automata equipped with transitions of the following two types: may and must. The components that implement such interfaces are simple labeled transition systems. Roughly, a must transition is available in every component that implements the modal specification, while a may transition need not be. Recently [12] a timed extension of modal automata was proposed. This series of works, which generalizes an early attempt [19], embeds all the operations presented in the present paper. However, modalities are orthogonal to inputs and outputs, and it is well-known [47] that, contrary to the game-semantic approach, they cannot be used to distinguish between the behaviors of the component and those of the environment.

Among other modeling languages for specification, one find those that use logical representations such as Timed Computational Tree Logic (TCTL), Metric Temporal Logic (MTL), or duration. While such logics are generally convenient to reason on individual requirements [54], they are generally not suited for operations such as structural composition and quotient. To the best of our knowledge, the expressiveness relation between logical formalism and timed I/O automata or timed modal specifications remains unknown. There are also timed extensions of languages such as CSP. A comparison between CSP (and related process algebra languages) and interface theories can be found in [8].

Finally, let us add that numerous authors have studied interface theories and component based design. Among them, one finds a series of very practical works that do not study quotient and conjunction, but rather focus on richer composition operations and specific models of computation for interconnection and software design [1, 36, 37]. Another example is the series of more recent papers that focus on composition and performance analysis or scheduling for embedded systems [40]. While our theory is certainly more general, it would be of interest to learn from those models and the case studies they handle in order to extend our composition operation.

There are of course other tools and theories for timed systems. As an example, another tool supporting refinement is PAT [57,58]. Unlike ECDAR, it builds on CSP

Figure 4: Illustration of the steps performed in a concrete refinement check. The gray box represents the part carried out internally by the verification engine.

with a failure, divergence, and refusal semantics, which makes a direct comparison difficult. However, the CSP theory does not support quotienting nor simple conjunction of specifications. And thus, in contrast to ECDAR, PAT does not support assume/guarantee reasoning about systems. This related work survey only the position of our work in the interface theory setting.

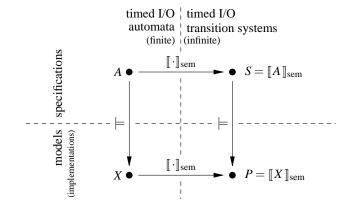

### 4 Specifications and Implementations

We use four classes of objects in our theory—specifications, and models (implementations) together with their respective behavioral semantics as transition systems. Two kinds of relations are used between the four classes: operational semantics and satisfaction. Fig. 5 shows an overview of the four classes of objects and relations between them.

We distinguish specifications and models. In the left part of Fig. 5, a specification A and a model X can be related through a satisfaction relation  $\models$ , relating models and specifications. The left half of Fig. 5, shows syntactic objects (specifications and implementations), while the right half shows the semantic objects (specification semantics and implementation semantics). Horizontal arrows point from syntactic objects to their semantics. Vertical arrows point from specifications downwards to their models (both in the syntactic and the semantic halves).

Traditionally specifications are logical formulas, and models are witnesses of consistency of these formulas. This is the view that most of the model-checking [22, 7] research takes. In our case, specifications are timed games [51], resembling timed automata [3]. Since these are symbolic finite representations describing continuous state behavior, it is convenient to distinguish another semantic layer, which describes this behavior operationally. Thus we will say that the semantics of a specification A (respectively of an implementation X) is given by a Timed I/O Transition System  $[\![S]\!]_{\text{sem}}$  (respectively of a Timed I/O Transition System  $[\![S]\!]_{\text{sem}}$ ). Our transition systems are very similar to those induced

Figure 5: Semantic Layer's in our specification theory

by processes in [63], except that their discrete actions are split into inputs and outputs, like in I/O automata [49]. Unlike in I/O automata we give them a game semantics, not the language semantics.

Throughout the presentation of our specification theory, we continuously switch the mode of discussion between the semantic and syntactic levels. In general, the formal framework is developed for the semantic objects, Timed I/O Transition Systems (TIOTSs in short) [39], and enriched with syntactic constructions for Timed I/O Automata (TIOAs), which act as a symbolic and finite representation for TIOTSs. However, the theory for TIOTSs does not rely in any way on the TIOAs representation—one can build TIOTSs that cannot be represented by TIOAs, and the theory remains sound for them (although we would not know how to manipulate them symbolically).

**Definition 1.** A Timed I/O Transition System (TIOTS) is a tuple  $S = (St^S, s_0, \Sigma^S, \rightarrow^S)$ , where  $St^S$  is an infinite set of states,  $s_0 \in St$  is the initial state,  $\Sigma^S = \Sigma_i^S \oplus \Sigma_o^S$  is a finite set of actions partitioned into inputs  $(\Sigma_i^S)$  and outputs  $(\Sigma_o^S)$ , and  $\rightarrow^S : St^S \times (\Sigma^S \cup \mathcal{R}_{\geq 0}) \times St^S$  is a transition relation. We write  $s \xrightarrow{a} Ss'$  instead of  $(s, a, s') \in \rightarrow^S$ , and we write  $s \xrightarrow{a} S$  if  $\exists s'.s \xrightarrow{a} Ss'$ , and use i?, o! and d to

range over inputs, outputs and  $\mathcal{R}_{\geq 0}$  respectively. Transitions that are labelled by actions (inputs or outputs) are called *discrete* transitions, while transitions labelled by real values are called *timed* transitions. In addition any TIOTS satisfies the following:

[time determinism] if  $s \xrightarrow{d} S's'$  and  $s \xrightarrow{d} S''$  then s' = s'' [time reflexivity]  $s \xrightarrow{0} S's$  for all  $s \in St^S$

[time additivity] for all  $s, s'' \in St^S$  and all  $d_1, d_2 \in \mathcal{R}_{\geq 0}$ , we have  $s \xrightarrow{d_1 + d_2} Ss''$  iff  $s \xrightarrow{d_1} Ss'$  and  $s' \xrightarrow{d_2} Ss''$  for an  $s' \in St^S$ .

We only work with deterministic TIOTSs in this paper: for all  $a \in \Sigma \cup \mathcal{R}_{\geq 0}$  whenever  $s \xrightarrow{a} S's'$  and  $s \xrightarrow{a} S's''$ , we have s' = s'' (determinism is required not only for timed transitions, but also for discrete transitions). In the rest of the paper, we often drop the adjective 'deterministic'. Of course, this definition of determinism does not prevent from issuing several actions from the same state, the only restriction is that one given action can only take the system to a deterministic location.

For a TIOTS S and a set of states X, we write:

$$\operatorname{pred}_a^S(X) = \left\{ s \in St^S \ \big| \ \exists s' \! \in \! X. \ s \xrightarrow{a} \! s' \right\} \tag{1}$$

for the set of all a-predecessors of states in X. We write  $\mathsf{ipred}^S(X)$  for the set of all input predecessors, and  $\mathsf{opred}^S(X)$  for all the output predecessors of X:

$$\operatorname{ipred}^{S}(X) = \bigcup_{a \in \Sigma^{S}} \operatorname{pred}_{a}^{S}(X) \tag{2}$$

$$\operatorname{opred}^S(X) = \bigcup_{a \in \Sigma_{>}^S} \operatorname{pred}_a^S(X) \ . \tag{3}$$

Also  $\mathsf{post}_{[0,d_0]}^S(s)$  is the set of all time successors of a state s that can be reached by delays smaller or equal to  $d_0$ :

$$\operatorname{post}_{[0,d_0]}^S(s) = \left\{ s' \in St^S \mid \exists d \in [0,d_0]. \, s \xrightarrow{d} Ss' \right\} \tag{4}$$

Following [51] we will later use these operators to find strategies for safety and reachability objectives imposed on TIOTSs.

We shall now introduce a finite syntactic symbolic representation for TIOTSs in terms of Timed I/O Automata (TIOAs). Let Clk be a finite set of clocks. A clock valuation over Clk is a mapping  $u \in [Clk \mapsto \mathcal{R}_{\geq 0}]$ . Given  $d \in \mathcal{R}_{>0}$ , we write u + d to denote a valuation such that for any clock r we have (u+d)(r)=x+d iff u(r)=x. We write  $u[r \mapsto 0]_{r \in c}$  for a valuation which agrees with u on all values for clocks not in c, and returns 0 for all clocks in c. Let op be the set of relational operators:  $op = \{<, \leq, >, \geq\}$ . A guard over Clk is a finite conjunction of expressions of the form  $x \prec n$ , where  $\prec$  is a relational operator and  $n \in \mathbb{N}$ . We write  $\mathcal{B}(Clk)$  for the set of guards over Clk using operators in the set op, and  $\mathcal{U}(Clk)$  for the subset of upper bound guards using only the operators  $\{<,\leq\}$ . We also write  $\mathscr{P}(X)$  for the powerset of a set X.

**Definition 2.** A Timed I/O Automaton (TIOA) is a tuple  $A = (Loc, q_0, Clk, E, Act, Inv)$  where Loc is a finite set of locations,  $q_0 \in Loc$  is the initial location, Clk is a finite set of clocks,  $E \subseteq Loc \times Act \times \mathcal{B}(Clk) \times \mathscr{P}(Clk) \times Loc$  is a set of edges,  $Act = Act_i \oplus Act_o$  is a finite set of actions, partitioned into inputs and outputs respectively, and  $Inv : Loc \mapsto \mathcal{U}(Clk)$  is a set of location invariants.

If  $(q, a, \varphi, c, q') \in E$  is an edge, then q is an initial location, a is an action label,  $\varphi$  is a constraint over clocks that must be satisfied when the edge is executed, c is a set of clocks to be reset, and q' is a target location. We denote  $NextInv(q') = Inv(q') \lor (\bigvee_{r \in c} \{r \ge 0\})$  the invariant of the next location that restrict the guard of the edge. Examples of TIOAs have been shown in the introduction.

We define the semantic of a TIOA  $A = (Loc, q_0, Clk, E, Act, Inv)$  to be a TIOTS  $[\![A]\!]_{\text{sem}} = (Loc \times (Clk \mapsto \mathcal{R}_{\geq 0}), (q_0, \mathbf{0}), Act, \rightarrow)$ , where  $\mathbf{0}$  is a constant function mapping all clocks to zero, and  $\rightarrow$  is the largest transition relation generated by the following rules:

$$(q, a, \varphi, c, q') \in E \quad u \in \left[ Clk \mapsto \mathcal{R}_{\geq 0} \right]$$

$$u \models \varphi \land \quad u[r \mapsto 0]_{r \in c} \models Inv(q')$$

$$(q, u) \xrightarrow{a} (q', u[r \mapsto 0]_{r \in c})$$

$$q \in Loc \quad u \in \left[ Clk \mapsto \mathcal{R}_{\geq 0} \right] \quad d \in \mathcal{R}_{\geq 0} \quad u + d \models Inv(q)$$

$$(q, u) \xrightarrow{d} (q, u + d)$$

The TIOTSs induced by TIOAs, according to the above rules, satisfy the axioms of Definition 1: time determinism, time reflexivity, time additivity. Moreover, in order to guarantee determinism of  $[\![A]\!]_{\text{sem}}$ , the TIOA A has to be deterministic: for each action—location pair only one transition can be enabled at the same time.

This can be checked algorithmically with a standard check for disjointness of guards of transitions with the same action. For each location q and each action  $a \in Act$ , check whether all its guards are mutually exclusive. Formally, let  $G_{q,a}$  be the set of strengthened guards of all a transitions leaving q:

$$G_{q,a} = \{ \varphi \land NextInv(q') \mid \text{whenever } (q, a, \varphi, c, q') \in E \}$$

(5)

To guarantee determinism check for each pair  $\psi_1, \psi_2 \in G_{q,a}$  whether the conjunction  $Inv(q) \wedge \psi_1 \wedge \psi_2$  is inconsistent, and do that for all locations.

We assume that all TIOAs below are deterministic.

### 4.1 Specifications

We will now introduce our notions of specifications and implementations.

**Definition 3 (Specification).** A TIOTS  $P = (St^P, p_0, \Sigma^P, \rightarrow^P)$  is a specification semantics if each state  $s \in St^P$  is input-enabled: for each input  $i? \in \Sigma_i^P$  there exists a state  $s' \in St^P$  such that  $s \stackrel{i?}{=} Ps'$ .

A TIOA A is a specification iff its semantics  $[A]_{sem}$ is input-enabled.

The assumption of input-enabledness, also seen in many specification theories [49, 38, 56, 61, 53], reflects our belief that an input cannot be prevented from being sent to a system, but it might be unpredictable how the system behaves after receiving it. A standard way of modeling a disallowed input in such a setting is to redirect it to a special universal state, where all actions are enabled the behaviour of the system becomes unpredictable after reaching this state.

Input-enabledness encourages explicit modeling of this unpredictability, and compositional reasoning about it; for example, it allows asking if an unpredictable behaviour of one component induces unpredictability of the entire system.

In practice, tools should not require the users to specify input-enabled automata, as this quickly becomes tedious. There are however good strategies for making automata input-enabled. First, absent inputs can be interpreted as ignored inputs, corresponding to location loops in the automaton that can be added automatically. Second, absent inputs can be interpreted as unavailable ("blocking") inputs, which are modeled by adding implicit transitions to a designated error location (for example a universal location as suggested above). Later, in Section 7, we will call such a state strictly undesirable and give a rationale for this name.

In order to check that a TIOA A induces an inputenabled TIOTS  $[A]_{sem}$ , decide for each location  $q \in$  $Loc^A$  and each input action  $i? \in Act$  if a disjunction of guards of outgoing transitions labelled by i? is entailed by Inv(q). Formally, if  $G_{q,i}$ ? is the set of strengthened guards (see (5)) of all i?-transitions leaving q, then in order to check if i? is always enabled in location q, check

$$Inv(q)$$

entails  $\bigvee_{\psi \in G_{g,i}} \psi$  (6)

To check if the entire specification automaton is inputenabled just repeat the check for all location—input pairs.

### 4.2 Implementations

The role of specifications in a specification theory is to abstract, or underspecify, sets of possible implementations. We will assume that implementations of timed systems have fixed timing behaviour (outputs occur at predictable times) and systems can always advance either by producing an output or delaying. This is formalized using axioms of output-urgency and independent-progress

Definition 4 (Implementation). A TIOTS  $P = (St^P,$  $p_0, \Sigma^P, \xrightarrow{P}$ ) is an implementation semantics if it is a specification semantics that fulfills the output urgency and independent progress conditions, so if for each state

$p \in St^P$  we respectively have:

[output urgency]  $\forall p', p'' \in St^P$  if  $p \xrightarrow{o!} p'$  and  $p \xrightarrow{d} p''$ then d = 0 (and thus, due to determinism p = p'') [independent progress] either  $(\forall d \geq 0. \ p \xrightarrow{d}^{P})$  or  $\exists d \in \mathcal{R}_{\geq 0}. \exists o! \in \Sigma_{0}^{P}. \ p \xrightarrow{d} p'$  and  $p' \xrightarrow{o!}^{P}.$

A TIOA A is an implementation iff A is a specification and its semantics,  $[A]_{sem}$ , fulfills independent progress and output urgency.

Independent progress is one of the central properties in our theory: it states that an implementation cannot ever get stuck in a state where it is up to the environment to induce the progress of time. So in every state there is either an output transition (which is controlled by the implementation) or an ability to delay until an output is possible. Otherwise a state can delay indefinitely. An implementation cannot wait for an input from the environment without letting time pass.

Remark 1. Our notion of implementation remains at the theory level. Generating executable code and taking robustness into account is not the topic of this paper. However, one could exploit existing works [5] to generate robust C code from a given timed automaton.

In Section 9 we describe how to check for independent progress and other important properties of specifications.

### 4.3 Specifications as Timed Games

Specifications are interpreted as two-player real-time games between the *output player* (the component) and the input player (the environment). The input player plays with actions in Acti and the output player plays with actions in  $Act_0$ . A strategy for a player is a function that defines his move at any state (either delaying or playing a controllable action). As we will explain in the following sections, strategies for output (respectively input) can be interpreted as implementations (respectively compatible environments).

A strategy is called *memoryless* if the next move depends solely on the current state. We only consider memoryless strategies, as these suffice for safety games [30]. For simplicity, we only define strategies for the output player (i.e. output is the verifier). Definitions for the input player are obtained symmetrically.

**Definition 5.** A memoryless strategy  $f_o$  for the output player on the TIOA A is a partial function  $St^{[A]}_{sem} \mapsto$  $Act_0 \cup \{delay\},$  such that

- $-\operatorname{If}\ f_o(s)\in Act_0\ \operatorname{then}\ \exists s'.s \xrightarrow{f_o(s)} {}^Ss'.$   $-\operatorname{If}\ f_o(s)=\operatorname{delay}\ \operatorname{then}\ \exists s''.s \xrightarrow{d} {}^Ss''\ \operatorname{for\ some}\ d>0,\ \operatorname{and}$  $f_o(s'') = \text{delay}.$

The game proceeds as a concurrent game between the two players. Then, by applying a strategy  $f_o$  the output player restricts the set of reachable states from the semantics. This defines the outcome of the strategy, such that for a state  $s \in St^{\llbracket A \rrbracket_{sem}}$ ,  $\mathsf{Outcome}(s,f_o)$  is the set of states defined inductively by:

- $-s \in \mathsf{Outcome}(s, f_o),$

- if  $s' \in \mathsf{Outcome}(s, f_o)$  and  $s' \xrightarrow{a} s''$ , then  $s'' \in \mathsf{Outcome}(s, f_o)$  if one the following conditions holds:

- 1.  $a \in Act_i$ ,

- 2.  $a \in Act_o$  and  $f_o(s') = a$ ,

- 3.  $a \in \mathcal{R}_{\geq 0}$  and  $\forall d \in [0, a[.\exists s'''. s' \xrightarrow{d} s''']$  and  $f_o(s''') = \mathsf{delay}$ .

In a safety game, the winning condition is to avoid a set Bad of "bad" states. A strategy  $f_o$  is a winning strategy from state s if and only if  $\mathsf{Outcome}(s,f_o)\cap\mathsf{Bad}=\emptyset$ . A state s is winning if there exists a winning strategy from s, and the game is winning if and only if the initial state is winning. Solving this game is decidable [51,17,24].

### 5 Satisfaction, Refinement and Consistency

A notion of refinement allows to compare two specifications as well as to relate an implementation to a specification. Refinement should satisfy the following substitutability condition. If P refines Q, then it should be possible to replace Q with P in every environment and obtain an equivalent system.

We study these kind of properties in later sections. It is well known from the literature [31,32,15] that in order to give these kind of guarantees a refinement should have the flavour of *alternating (timed) simulation* [4].

**Definition 6 (Refinement \leq).** A TIOTS  $S = (St^S, s_0, \Sigma, \rightarrow^S)$  refines a TIOTS  $T = (St^T, t_0, \Sigma, \rightarrow^T)$ , written  $S \leq T$ , iff there exists a binary relation  $R \subseteq St^S \times St^T$  containing  $(s_0, t_0)$  such that for each pair of states  $(s, t) \in R$  we have:

- 1. whenever  $t \xrightarrow{i?} Tt'$  for some  $t' \in St^T$  then  $s \xrightarrow{i?} Ss'$  and  $(s', t') \in R$  for some  $s' \in St^S$

- 2. whenever  $s \xrightarrow{o!} Ss'$  for some  $s' \in St^S$  then  $t \xrightarrow{o!} t'$  and  $(s',t') \in R$  for some  $t' \in St^T$

- 3. whenever  $s \xrightarrow{d} S' s'$  for  $d \in \mathcal{R}_{\geq 0}$  then  $t \xrightarrow{d} Tt'$  and  $(s', t') \in R$  for some  $t' \in St^T$

A specification automaton  $A_1$  refines another specification automaton  $A_2$ , written  $A_1 \leq A_2$ , iff  $[A_1]_{\text{sem}} \leq |A_2|_{\text{sem}}$ .

It is easy to see that the refinement is reflexive and transitive, so it is a preorder on the set of all specifications (and, of course, also on the set of all specification semantics). Refinement can be checked for specification

Figure 6: A coffee machine specification that refines the coffee machine in Fig. 1.

automata by reducing the problem to a specific refinement game, and using a symbolic representation to reason about it. We discuss details of this process in Section 9.

Fig. 6 shows a coffee machine that is a refinement of the one in Fig. 1. It has been refined in two ways: one output transition has been completely dropped and one state invariant has been tightened.

Since our implementations are a subclass of specifications, we simply use *refinement* as an implementation relation:

**Definition 7 (Satisfaction).** An implementation semantics TIOTS P satisfies a specification semantics S, written  $P \models S$ , iff  $P \leq S$ . An implementation I satisfies a specification A iff  $\llbracket I \rrbracket_{\text{sem}} \models \llbracket A \rrbracket_{\text{sem}}$ . We write  $\llbracket A \rrbracket_{\text{mod}}$  for all semantic models of A, so  $\llbracket A \rrbracket_{\text{mod}} = \{P \mid P \text{ is a TIOTS and } P \models \llbracket A \rrbracket_{\text{sem}} \}$ .

From a logical perspective, specifications are like formulae, and implementations are their models. This analogy leads us to a classical notion of consistency, as existence of models.

**Definition 8 (Consistency).** A specification semantics TIOTS S is consistent if there exists an input-enabled TIOTS P such that  $P \models S$ , and P is an implementation semantics. A specification A is consistent if its specification semantics,  $[\![A]\!]_{\text{sem}}$ , is consistent.

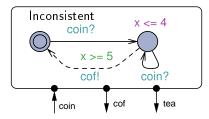

All specifications shown until now are consistent. An example of an inconsistent specification can be found in Fig. 7: notice that the invariant in the second state  $(x \le 4)$  is stronger than the guard  $(x \ge 5)$  on the cof! edge; therefore this state does not fulfill the independent progress condition, and it cannot be implemented.

We also define a soundly stricter, more syntactic, notion of consistency, which requires that all states are consistent:

**Definition 9 (Local Consistency).** A state s of a specification semantics S is *locally consistent* if it fulfills independent progress. S is locally consistent iff ev-

Figure 7: An inconsistent specification.

ery state  $s \in St^S$  is locally consistent. A specification A is locally consistent if  $[A]_{sem}$  is locally consistent.

**Lemma 1.** Every locally consistent specification semantics S is consistent in the sense of Def. 8.

Proof (Lemma 1). Let us begin with defining an auxiliary function  $\delta$  which chooses a delay and an output for every locally consistent state s:

$$\delta_{s} = \begin{cases} d & \text{for some } d \text{ such that } s \xrightarrow{d} S s' \\ & \text{and } \exists o!. s' \xrightarrow{o!} S \\ +\infty & \text{if } \forall d \geq 0. s \xrightarrow{d} S \end{cases}$$

(7)

Note that  $\delta$  is a function, so it always gives a unique value of a delay for any state s, thus in the first case we mean that an arbitrary fixed value is chosen out of uncountably many possible values. It is immaterial for the proof which of the many values is chosen. It is important however that  $\delta$  is time additive in the following sense: if  $s \xrightarrow{d} s'$  and  $d \le \delta_s$  then  $\delta_{s'} + d = \delta_s$ . It is always possible to choose such a function  $\delta$  due to time additivity of  $\rightarrow^S$ , and local consistency of S.

We want to synthesize a TIOTS  $P = (St^P, p_{s_0}, \Sigma^P, \rightarrow^P)$ , where  $St^P = \{p_s \mid s \in St^S\}, \Sigma^P = \Sigma^S$  with the same partitioning into inputs and outputs, and  $\rightarrow^P$  is the largest transition relation generated by the following rules:

$$\frac{s \xrightarrow{i?}^{S} s' \quad i? \in \Sigma_{i}^{S}}{p_{s} \xrightarrow{i?}^{P} p_{s'}} \tag{8}$$

$$\frac{s \xrightarrow{o!} Ss' \quad o! \in \Sigma_0^S \quad \delta_s = 0}{p_s \xrightarrow{o!} p_{s'}} \tag{9}$$

$$\frac{s \xrightarrow{d} Ss' \quad d \in \mathcal{R}_{\geq 0} \quad d \leq \delta_s}{p_s \xrightarrow{d} Pp_{s'}} \tag{10}$$

Since P only takes a subset of transitions of S, the determinism of S implies determinism of P. The transition relation of P is time-additive due to time additivity of A sem and of  $\delta$ . It is also time-reflexive due to the last rule  $(0 \le \delta_s)$  for every state s and  $\rightarrow^S$  was time reflexive). So P is a TIOTS.

The new transition relation is also input-enabled as it inherits input transitions from A, which was input

enabled. The second rule guarantees that outputs are urgent (P only outputs when no further delays are possible). Moreover P observes independent progress. Consider a state  $p_s$ . Then if  $\delta_s = +\infty$  clearly  $p_s$  can delay indefinitely. If  $\delta_s$  is finite, then by definition of  $\delta$  and of P, the state  $p_s$  can delay and then produce an output. Thus P satisfies conditions of Def. 8.

Now, the following relation  $R \subseteq St^P \times St^S$  witnesses  $P \models S$ :

$$R = \left\{ (p_s, s) \mid p_s \in St^P \text{ and } s \in St^{\mathbb{I}A} \right\}$$

(11)

This is argued using an unsurprising coinductive argument. Obviously,  $(p_{s_0}, s_0) \in R$ . Now for any  $(p_s, s) \in R$ :

- If  $s \xrightarrow{i?} S'$  with  $i? \in \Sigma_{\mathrm{i}}^S$ , then according to rule 8

- $p_s \xrightarrow{i?} {}^P p_{s'}.$  If  $p_s \xrightarrow{o!} {}^P p_{s'}$  with  $o! \in \Sigma_0^S$ , then according to rule 9

- If  $p_s \stackrel{d}{\underset{c}{\longrightarrow}} p_{s'}$  with  $d \in \mathcal{R}_{\geq 0}$ , then according to rule 10

This proves that R is a refinement relation.

It follows directly that:

Corollary 1. Every locally consistent specification is consistent (in the sense of Def. 8).

We shall see later (Figure 8) that the implication opposite to the one of Corollary 1 does not hold. To establish local consistency, or independent progress, for a TIOA, it suffices to check for each location if the supremum of all solutions of its invariant exists, whether it satisfies the invariant itself and allows at least one enabled output transition.

Prior specification theories for discrete time [45] and probabilistic [16] systems reveal two main requirements for a definition of implementation. These are the same requirements that are typically imposed on a definition of a model as a special case of a logical formula. First, implementations should be consistent specifications (logically, models correspond to some consistent formulae). Second, implementations should be fully specified (models cannot be refined by non-models), as opposed to proper specifications, which should be underspecified. For example, in propositional logics, a model is represented as a complete consistent term. Any implicant of such a term is also a model (in propositional logics, it is actually equivalent to it).

Our definition of implementation satisfies both requirements, and to the best of our knowledge, is the first example of a proper notion of implementation for timed specifications. As the refinement is reflexive we get  $P \models P$  for any implementation and thus each implementation is consistent as per Def. 8. Furthermore each implementation cannot be refined anymore by any underspecified specifications:

**Lemma 2.** Any locally consistent specification semantics S refining an implementation semantics P is an implementation semantics as per Def. 4.

Proof (Lemma 2). Observe first that S is already locally consistent, so all states of S warrant independent progress. We only need to argue that they also verify output urgency.

Without loss of generality, assume that  $[\![S]\!]_{\text{sem}}$  only contains states that are reachable by (sequences of) discrete or timed transitions.

If S only contains reachable states, every state of S has to be related to some state of P in a relation R witnessing  $S \leq P$  (output and delay transitions need to be matched in the refinement; input transitions also need to be matched as P is input enabled and S is deterministic). This can be argued for using a standard, though slightly lengthy argument, by formalizing reachable states as a fixpoint of a monotonic operator.

Now, that we know that every state of S is related to some state of P consider an arbitrary  $s \in St^S$  and let  $p \in St^P$  be such that  $(s,p) \in R$ . Then if  $s \xrightarrow{o!} Ss'$  for some state  $s' \in St^S$  and an output  $o! \in \Sigma_o^S$ , it must be that also  $p \xrightarrow{o!} p'$  for some state  $p' \in St^P$  (and  $(s',p') \in R$ ). But since P is an implementation, its outputs must be urgent, so  $p \not\stackrel{d}{\longrightarrow} P$  for all d > 0, and consequently  $s \not\stackrel{d}{\longrightarrow} S$  for all s > 0. We have shown that all states of S have urgent outputs (if any) and thus S is an implementation.

Corollary 2. Any locally consistent specification S refining an implementation P is an implementation itself.

We conclude the section with the first major theorem. Observe that every preorder  $\preceq$  is intrinsically complete in the following sense:  $S \preceq T$  iff for every smaller element  $P \preceq S$  also  $P \preceq T$ . This means that a refinement of two specifications coincides with inclusion of sets of all the specifications refining each of them:

$$S \le T \quad \text{iff} \quad \{P \mid P \le S\} \subseteq \{P \mid P \le T\} \tag{12}$$

However, since out of all specifications only the implementations correspond to real world objects, another completeness question is more relevant: does the refinement coincide with the inclusion of implementation sets? This property, which does not hold for preorders in general, turns out to hold for our refinement:

Theorem 1 (Refinement Is Thorough). For any two locally consistent specifications A, B we have that

$$A < B \text{ iff } \llbracket A \rrbracket_{\text{mod}} \subset \llbracket B \rrbracket_{\text{mod}} \tag{13}$$

We split the proof of Theorem 1 into two lemmas.

**Lemma 3 (Soundness).** For all locally consistent specification semantics S and T, if  $S \leq T$  then for any implementation semantics P,  $P \models S$  implies  $P \models T$ .

*Proof (Lemma 3).* This lemma is a special case of the transitivity of the refinement relation. Consider an implementation semantics P of S. Then  $P \leq S$  and  $S \leq T$ , implies P < T, which proves that  $P \models T$ .

**Lemma 4 (Completeness).** For all locally consistent specification semantics S and T, if for any implementation semantics P,  $P \models S$  implies  $P \models T$ , then  $S \leq T$ .

In the following we write  $p \models s$  for states p and s of TIOTS P (respectively S) meaning that there exists a relation R' witnessing  $P \models S$  that contains the pair of states (p, s).

*Proof (Lemma 4).* Assume that every model of S is a model of T. Consider the relation  $R \subseteq St^S \times St^T$ :

$$R = \{(s,t) \mid \text{for each implementation TIOA } P$$

it holds that  $(p_0^P \models s \implies p_0^P \models t)\}$ , (14)

where  $p_0^P$  denotes the initial state of P. We shall argue that R witnesses  $S \leq T$ . It follows directly from the definition of R and the assumption on model inclusion that  $(s_0, t_0) \in R$ . Now consider a pair  $(s, t) \in R$ . There are two cases to be considered:

- For any input i? there exists  $t' \in St^T$  such that  $t \xrightarrow{i?} Tt'$ . We need to show existence of a state  $s' \in St^S$  such that  $s \xrightarrow{i?} Ss'$  and  $(s', t') \in R$ .

Observe that due to input-enabledness, for the same i?, there exists a state  $s' \in St^S$  such that  $s \stackrel{i?}{=} \mathbb{I}^S \mathbb{I}_{\text{sem}} s'$ . We need to show that  $(s',t') \in R$ . By Theorem 1 we have that there exists an implementation semantics P with initial state  $p_0^P$  such that  $p_0^P \models s'$  (technically speaking, s may be a non-initial state of S, but then we can consider a version of S with initial state changed to s to apply Theorem 1, concluding existence of the implementation P as above).

We will now argue that arbitrary implementation semantics (not only P) satisfying the state s' also satisfies t'. So consider an implementation semantics  $Q \models S$  and its initial state  $q_0^Q$  such that  $q_0^Q \models s'$ . We show that  $q_0^Q \models t'$ .

Create an implementation Q' by merging Q and P above and adding a fresh state  $q_0^{Q'}$  with all the same transitions like the initial location of P (so targeting locations of the P-part), except for the transition labeled by i?, which should go to  $q_0^Q$ ; so:  $q_0^{Q'} \xrightarrow{i?} Q' q_0^Q$  and otherwise  $q_0^{Q'} \xrightarrow{a} Q' p$  whenever  $p_0^P \xrightarrow{a} P p$  for  $a \neq i$ ?. The transitions for all the other states of Q' are like in P and Q, depending to which of the two implementation semantics the state originally belonged. Now  $q_0^{Q'} \models s$  as  $p \models s$  and it follows all evolutions of p for  $a \neq i$ ? and  $q \xrightarrow{i?} Q' q_0$  and  $q_0 \models s'$ . By assumption, every implementation semantics of s is also an

implementation semantics of t, so  $q_0^{Q'} \models t$  and consequently  $q_0 \models t'$  as  $q_0^{Q'}$  is deterministic on i?.

Summarizing, for any implementation  $q_0 \models s'$  we were able to argue that  $q_0 \models t'$ , thus necessarily  $(s',t') \in R$ .

Consider any action a (which is an output or a delay) for which exists s' such that  $s \xrightarrow{a} S s'$ . Similarly as above, one can construct (and thus postulate existence) of an implementation P containing  $p \in St^P$  such that  $p \models s$  which has a transition  $p \xrightarrow{a} P p'$ . Since then also  $p \models t$  we have that there exists  $t' \in St^T$  such that  $t \xrightarrow{a} Tt'$ . It remains to argue that  $(s', t') \in R$ . This is done in the same way as with the first case, by considering any model of s', then by extending it deterministically to a model of s, concluding that it is now a model of t and the only a-derivative, which is p', must be a model of t'. Consequently  $(s', t') \in R$ .

A complete refinement in the above sense is also sometimes called *thorough* (see e.g. [6]). The restriction of the theorem to locally consistent specifications is not a serious one. As we shall see later (Theorem 2), any consistent specification can be transformed into a locally consistent one preserving the set of implementations.

### 6 Consistency and Conjunction

### 6.1 Consistency

We will now study how consistency and refinement interact with time lock errors (violation of independent progress) in specifications. In particular we will give an operational characterization of Def. 8.

An immediate error occurs in a state of a specification semantics if the state disallows progress of time and output transitions—such a specification will break if the environment does not send an input. For a specification semantics S we define the set of immediate error states  $\operatorname{err}^S \subseteq \operatorname{St}^S$  as:

$$\mathsf{err}^S \!=\! \left\{ s \, \big| \, (\exists d. \, s \not \stackrel{d}{\longrightarrow}) \text{ and } \forall d \, \forall o! \, \forall s'. s \xrightarrow{d} s' \text{ implies } s' \not \stackrel{o!}{\longrightarrow} \right\}$$

It follows that no immediate error states can occur in implementations, or in locally consistent specifications.

In general, immediate error states in a specification do not necessarily mean that a specification cannot be implemented. Fig. 8 shows a partially inconsistent specification, a version of the coffee machine that becomes inconsistent if it ever outputs tea. The inconsistency can be possibly avoided by some implementations, which would not implement delay or output transitions leading to it. More precisely an implementation will exist if there is a strategy for the output player in a safety game to avoid  $\operatorname{err}^S$ .

Figure 8: A partially inconsistent specification.

We will solve the safety game, by seeking states which can delay until a safe move, without passing through any unsafe states (or states from which a spoiling move exists). We first define the safe timed predecessor operator [33,51,17], which gives all the states that can safely delay until an output into X while avoiding the set of unsafe states Y:

$$\mathsf{Pred}_{\mathsf{t}}^{S}(X,Y) = \{ s \in \mathit{St}^{S} \mid \exists d_{0} \in \mathcal{R}_{\geq 0}. \, \exists s' \in X. \, s \xrightarrow{d_{0}} Ss' \\ \text{and } \mathsf{post}_{[0,d_{0}]}^{S}(s) \subseteq \overline{Y} \} \quad (15)$$

Since in our game it is possible to play by delaying indefinitely (not necessarily until an output is possible), we need another operator,  $\mathsf{Idle}_\mathsf{t}$ , that captures states that can delay indefinitely without passing through unsafe states. This operator is analogous to the above one, except that it delays indefinitely. Again, Y denotes the unsafe states:

$$\mathsf{Idle}_{\mathsf{t}}^S(Y) = \{ s \in St^S \mid \forall d \in \mathcal{R}_{\geq 0}. \, \exists s' \in \overline{Y}. \, s \xrightarrow{d} s' \} \quad (16)$$

Now the set of safe states is computed as the greatest fixpoint of the following operator  $\pi$ , which is an adjustment of the standard *controllable predecessors* operator [33,51] that accounts for infinite delay moves:

$$\begin{split} \pi(X) &= \overline{\mathsf{err}^S} \ \cap \ \left[ \mathsf{Idle}^S_{\mathsf{t}} \left( \mathsf{ipred}^S(\overline{X}) \right) \right. \\ & \left. \cup \mathsf{Pred}^S_{\mathsf{t}} \left( \mathsf{opred}^S(X), \mathsf{ipred}^S(\overline{X}) \right) \right] \end{aligned} \tag{17}$$

The  $\pi$  operator formalizes a two player game, when both players choose a delay, possibly zero, and a move to be made. The move with a shorter delay is executed. If the two delays are equal then the move is nondeterministic, and thus the operator computing the strategy requires that both moves have to be non-losing.

The set of all consistent states  $\mathsf{cons}^S$  (i.e. the states for which the environment has a winning strategy) is defined as the greatest fixpoint of  $\pi$ :  $\mathsf{cons}^S = \pi(\mathsf{cons}^S)$ , which is guaranteed to exist by monotonicity of  $\pi$  and completeness of the powerset lattice due to the theorem of Knaster and Tarski [59]. For transition systems

enjoying finite symbolic representations, automata specifications included, the fixpoint computation converges after a finite number of iterations [51,17].

**Lemma 5.** A specification semantics  $S = (St^S, s_0^S, \Sigma^S, \rightarrow^S)$  is consistent iff  $s_0^S \in \mathsf{cons}^S$ .

Correctness of the fixpoint characterization of winning strategies for safety games has first been observed in [51]. We have updated the theorem to our setting (which allows idling as a possible move). Below we provide a proof for this extended version.

Proof (Lemma 5). First, assume that  $s_0 \in \mathsf{cons}^S$ . Show that S is consistent in the sense of Def. 8. In a similar fashion to the proof of Lemma 1 we first postulate existence of a function  $\delta$ , which chooses a delay and an output for every consistent state s:

$$\delta_s = \begin{cases} d' & \text{if } \exists s', s'' \in \text{cons}^S. \ s \xrightarrow{d'} {}^S s' \text{ and } \exists o!. \ s' \xrightarrow{o!} {}^S s'' \\ +\infty & otherwise \end{cases}$$

(18)

For each state  $s \in \mathsf{cons}^S$  the value of  $\delta_s$  can be defined, since either  $s \in \mathsf{Idle_t}(\mathsf{ipred}^S(\mathsf{cons}^S))$  or  $s \in \mathsf{Pred_t}(\mathsf{opred}^S(\mathsf{cons}^S), \mathsf{ipred}^S(\mathsf{cons}^S))$ . In the former case it must be able to delay indefinitely through states in  $\mathsf{cons}^S$  (and thus  $\delta_s$  postulating the infinite delay is reasonable), in the latter case it can delay until an output predecessor of a state in  $\mathsf{cons}^S$ , without leaving  $\mathsf{cons}^S$  during the delay. Note that  $\delta$  is a function, so it always gives a unique value of a delay for any state s, thus in the first case we mean that an arbitrary fixed value is chosen out of possibly uncountably many values for d'. It is important however that  $\delta$  is time additive in the following sense: if  $s \xrightarrow{d} s'$  and  $d \leq \delta_s$  then  $\delta_{s'} + d = \delta_s$ . It is always possible to choose such a function  $\delta$  due to time additivity of  $\to^S$ , and the fact that  $\mathsf{cons}^S$  is a fixpoint of  $\pi$ .

We show this by constructing an implementation semantics  $P = (St^P, p_0, \Sigma^P, \rightarrow^P)$  such that  $St^P = \{p_s \mid s \in St^S\}$ ,  $\Sigma^P = \Sigma^S$  with the same partitioning in the inputs and outputs,  $p_0 = p_{s_0}$  and the transition relation is the largest relation generated by the following rules:

- 1.  $p_s \xrightarrow{o!} {}^P p_{s'}$  iff  $s \xrightarrow{o!} {}^S s'$  and  $s' \in \mathsf{cons}^S$  and  $\delta_s = 0$

- 2.  $p_s \xrightarrow{i?} p_{s'} \text{ iff } s \xrightarrow{i?} s'$

- 3.  $p_s \xrightarrow{d} {}^P p_{s'}$  iff  $s \xrightarrow{d} {}^S s'$  and  $d \leq \delta_s$

Observe that the construction of P is essentially identical to the one in the proof of Lemma 1 above. It can be argued in almost the same way as in the above proof, that P satisfies the axioms of TIOTSs and is an implementation semantics. Here one has to use the definition of  $\pi$  in order to see that the side condition in the first rule, that is  $s' \in \mathsf{cons}^S$ , does not introduce a violation of independent progress.

It remains to argue that  $P \models S$ . This is done by arguing that the following relation R:

$$R = \left\{ (p, s) \in St^P \times St^S \mid p_s = p \right\} \tag{19}$$

witnesses the refinement of S by P.

For the opposite direction, assume that S is consistent and show that  $s_0 \in \mathsf{cons}^S$ . Since S is consistent, then there exists an implementation semantics P and  $P \models S$ , witnessed by a satisfaction relation R. Without loss of generality consider an implementation, which only has reachable states, and all its states are related to some states of S in R (so R is a total relation). Consider the following subset of states of S:

$$X = \{ s \in St^S \mid (p, s) \in R \text{ for some state } p \text{ of } P \}$$

(20)

Obviously  $s_0^S \in X$ . It suffices to show that X is a post-fixed point of  $\pi$ . Then  $s_0 \in X \subseteq \pi(X) \subseteq \mathsf{cons}^S$ , since  $\mathsf{cons}^S$  is the greatest such (post-) fixed point.

Remember that  $(p,s) \in R$  for some state p of P. Also p satisfies independent progress. We consider two cases:

- p can delay indefinitely:  $\forall d. \ p \xrightarrow{d} p'$  for some state p'. But then also  $s \xrightarrow{d} s'$  for some state  $s' \in St^S$  and  $(p',s') \in R$ . So we have that all  $s' \in X$ . To show that  $s \in \pi(X)$  we need to see that  $s' \in \overline{err^S}$  and  $s \in \mathsf{Idle}^S_{\mathsf{t}}(\mathsf{ipred}^S(\overline{X}))$ . For the former this is quite obvious, as s must satisfy independent progress, if p does. For the latter assume that  $s \xrightarrow{d} s' \xrightarrow{i?} s''$  for some  $s'' \in \overline{X}$ . It must be that  $p \xrightarrow{d} p'$  for some state  $p' \in St^P$ , since p can delay indefinitely, and by satisfaction  $(p',s') \in R$ . Then also  $p' \xrightarrow{i?} p''$  for some state p'' and  $(p'',s'') \in R$  by satisfaction. But then  $s'' \in X$ , which contradicts our assumption that  $s'' \in \overline{X}$ . Thus all timed successors of s avoid unsafe states as per definition of  $\mathsf{Idle}^S_{\mathsf{t}}(\mathsf{ipred}^S(\overline{X}))$ .

- p can delay until a safe output:  $\exists d_0 \in \mathcal{R}_{\geq 0}$ .  $p \xrightarrow{d_0} p'$   $\xrightarrow{o!} p''$  for some states p' and p''. Then by satisfaction  $s \xrightarrow{d_0} s' \xrightarrow{o!} s''$  for some states s' and s'', such that (p', s'),  $(p'', s'') \in R$ , so s',  $s'' \in X$ . To argue that  $s \in \operatorname{Pred}_{\mathbf{t}}^S(\operatorname{opred}(X), \operatorname{ipred}(\overline{X}))$  it remains to show that  $\operatorname{post}_{[0,d_0]}^S(s) \cap \operatorname{ipred}^S(\overline{X}) = \emptyset$ . So assume the opposite:  $s \xrightarrow{\hat{d}} \hat{s}' \xrightarrow{i?} \hat{s}''$  for some delay  $\hat{d} \leq d_0$  and states  $\hat{s}'$ ,  $\hat{s}''$  with  $\hat{s}'' \in \overline{X}$ . Since p is time additive we have that  $p \xrightarrow{\hat{d}} \hat{p}'$  for some state  $\hat{p}' \in St^P$  and by satisfaction  $\hat{p}' \xrightarrow{i?} \hat{p}''$  for some state  $\hat{p}''$ ; witnessing that  $\hat{s}'$ ,  $\hat{s}'' \in X$ , which contradicts our assumption. Thus it must be that  $s \in \operatorname{Pred}_{s}^{F}(\operatorname{opred}(X), \operatorname{ipred}(\overline{X}))$ . □

**Corollary 3.** Consistency can be soundly established for any specification A by applying the above procedure that establishes Lemma 5 for  $[\![A]\!]_{\text{sem}}$ .

The set of (in)consistent states can be computed for timed games, and thus for specification automata, using controller synthesis algorithms [17]. We discuss it briefly in Section 9.

The inconsistent states can be pruned from a consistent S leading to a locally consistent specification. Pruning is applied in practice to decrease the size of specifications.

For a consistent specification semantics  $S = (St^S, s_0^S, \Sigma^S, \rightarrow^S)$  we define the pruned specification semantics  $S^{\Delta} = (\cos^S, s_0, \Sigma^S, \rightarrow^{S^{\Delta}})$ , where  $\rightarrow^{S^{\Delta}} = \rightarrow^S \cap (\cos^S \times (\Sigma^S \cup \mathcal{R}_{>0}) \times \cos^S)$ .

**Theorem 2.** Let S be a consistent specification semantics.  $S^{\Delta}$  is locally consistent and  $[\![S]\!]_{\text{mod}} = [\![S^{\Delta}]\!]_{\text{mod}}$ .

Proof (Theorem 2). All the inconsistent states (that do not fulfill the independent progress condition) are removed from the pruned specification semantics, so obviously  $S^{\Delta}$  is locally consistent.

Then, as we proved in Lemma 5, if we consider an implementation P of S and the set  $X = \{s \in St^S \mid (p,s) \in R \text{ for some state } p \text{ of } P\}$  of the states from S that are related to some state in P, then this set of states is consistent:  $X \subseteq \mathsf{cons}^S$ . This allows to use the same refinement relation R to show that  $P \subseteq S$  iff  $P \subseteq S^\Delta$ .

For specification automata pruning is realized by applying a controller synthesis algorithm, obtaining a maximum winning strategy, which can then be presented as a specification automaton itself.

### 6.2 Conjunction

Consistency guarantees realizability of a single specification. It is of further interest whether several specifications can be *simultaneously* met by the same component, without reaching error states of any of them. We formalize this notion by defining a logical conjunction for specifications.

**Definition 10 (Product**  $\times$ ). Let  $S = (St^S, s_0^S, \Sigma, \rightarrow^S)$  and  $T = (St^T, s_0^T, \Sigma, \rightarrow^T)$  be two specification semantics. A product of S and T, written  $S \times T$ , is defined to be the specification semantics  $(St^S \times St^T, (s_0^S, s_0^T), \Sigma, \rightarrow)$ , where the transition relation  $\rightarrow$  is the largest relation generated by the following rule:

$$\frac{s \xrightarrow{a}^{S} s' \quad t \xrightarrow{a}^{T} t' \quad a \in \Sigma \cup \mathcal{R}_{\geq 0}}{(s, t) \xrightarrow{a} (s', t')}$$

(21)

In general, a result of the product may be locally inconsistent, or even inconsistent. To guarantee consistency we apply a consistency check to the result, checking if  $(s_0, t_0) \in \mathsf{cons}^{S \times T}$  and, possibly, pruning the inconsistent parts:

**Definition 11 (Conjunction**  $\wedge$ ). For specifications S and T over the same alphabet, such that  $S \times T$  is consistent, define  $S \wedge T = (S \times T)^{\triangle}$ .

Conjunction is commutative, associative and it is the greatest lower bound for locally consistent specifications in the following sense:

**Theorem 3.** For any locally consistent specification semantics S, T, and U over the same alphabet:

1.  $S \wedge T \leq S$  and  $S \wedge T \leq T$ 2.  $(U \leq S)$  and  $(U \leq T)$  implies  $U \leq (S \wedge T)$ 3.  $[S \wedge T]_{\text{mod}} = [S]_{\text{mod}} \cap [T]_{\text{mod}}$ 4.  $[(S \wedge T) \wedge U]_{\text{mod}} = [S \wedge (T \wedge U)]_{\text{mod}}$

All the above facts naturally translate to syntactic specifications (TIOAs).

We omit the (fairly standard) proof for the first claim. Intuitively the claim holds because  $S \times T$  transitions are strictly transitions of S (and of T) and because the pruning producing  $(S \times T)^{\Delta}$  only removes output and delay transitions (which are allowed to be dropped by the refinement). It never removes input transitions from reachable states.

The third claim follows from the first two and the fact that the refinement coincides with model inclusion. The fourth claim follows from repetitive application of the third claim (and the fact that set intersection is the least upper bound in every powerset lattice). We only give a detailed proof for the second claim below.

Proof (Theorem 3.2). Assume that the relation  $R_1$  witnesses  $U \leq S$ , and relation  $R_2$  witnesses  $U \leq T$ . First, show that the following set X is a post fixed point of  $\pi$ :

$$X = \{(s,t) \mid \exists u \in St^U.\, (u,s) \in R_1 \text{ and } (u,t) \in R_2\} \quad (22)$$

Then we know that then  $(s,t) \in X \subseteq \pi(X) \subseteq \mathsf{cons}^{S \times T}$ , so all states in X are states of the conjunction.

Consider an arbitrary pair (s,t) in X, such that  $(u,s) \in R_1$  and  $(u,t) \in R_2$  for some state  $u \in St^U$ . Show that  $(s,t) \in \operatorname{err}^{S \times T}$ . This is easily seen ad absurdum. By Lemma 1 we know that there exists an implementation P and its state p such that  $p \models u$ . Since P is an implementation semantics it satisfies independent progress. So p can delay independently, or until an output. By satisfaction u can do the same, and by refinement both s and t can do the same. By construction of the product (s,t) can thus do the same, and it cannot be that  $(s,t) \in \operatorname{err}^{S \times T}$ .

Similarly, show  $(s,t) \in \mathsf{Idle}^{S \times T}_{\mathsf{t}} \left( \mathsf{ipred}^{S \times T}(\overline{X}) \right) \cup \mathsf{Pred}^{S \times T}_{\mathsf{t}} \left( \mathsf{opred}^{S \times T}(X), \mathsf{ipred}^{S \times T}(\overline{X}) \right)$ . This is again argued by the properties of u (and the fact that U is consistent). Consider the state u witnessing that  $(s,t) \in X$ . Since U is consistent, it must be that u either admits delaying indefinitely, or it delays until an output.

- Assume that for each delay d there exists a state u' such that  $u \xrightarrow{d} u'$  then, by refinement and construction  $(s,t) \xrightarrow{d} (s',t')$  for some  $(s',t') \in X$ . Since u is locally consistent, all intermediate successors states are implementable thus intermediate time successors of (s,t) cannot be in ipred (x,t). Formally, consider an intermediate successor (x,t) of (x,t) and thus  $(x,t) \xrightarrow{d'} (s'',t'')$  for some (x,t) with (x,t) (x,t) error and (x,t) for some (x,t) of (x,t) of (x,t) for (x,t) of (x,t) of (x,t) for (x,t) of (x,t) of (x,t) for (x,t) of (x,t) of (x,t) of (x,t) for (x,t) of (x,t)

some  $(s''', t''') \in \overline{X}$  we get a contradiction as by refinement it must be that  $u'' \xrightarrow{i?} u'''$  and u''' witnesses that  $(s''', t''') \in X$ .

- If u cannot delay indefinitely, then it can delay until an output (by local consistency). We use an almost identical argument that then both s and t must be able to do this, and so must their product. Avoiding  $\mathsf{ipred}^{S \times T}(\overline{X})$  is argued ad absurdum exactly like in the previous case. So we conclude that X describes a consistent part of the product.

Now it remains to show that U indeed refines the part of  $S \times T$  induced by X. This is a standard proof by arguing that the following relation R is a refinement relation:

$$R = \{(u, (s, t)) \in St^U \times X \mid (u, s) \in R_1 \text{ and}$$

$(u, t) \in R_2\}$  (23)

Since  $X \subseteq \mathsf{cons}^{S \times T}$ , we have that R also witnesses refinement of  $S \wedge T$  by U.

We turn our attention to syntactic representations again. Consider two specifications TIOAs  $A_1 = (Loc_1, q_0^1, Clk_1, E_1, Act^1, Inv_1)$  and  $A_2 = (Loc_2, q_0^2, Clk_2, E_2, Act^2, Inv_2)$  with  $Act_i^1 = Act_i^2$  and  $Act_o^1 = Act_o^2$ . Their conjunction, denoted  $A_1 \wedge A_2$ , is the TIOA  $A = (Loc, q_0, Clk, E, Act^1, Inv)$  given by:  $Loc = Loc_1 \times Loc_2, q_0 = (q_0^1, q_0^2), Clk = Clk_1 \uplus Clk_2, Inv((q_1, q_2)) = Inv(q_1) \wedge Inv(q_2)$ . The set of edges E is defined by the following rule:

- If

$$(q_1, a, \varphi_1, c_1, q_1') \in E_1$$

and  $(q_2, a, \varphi_2, c_2, q_2') \in E_2$ ,

then  $((q_1, q_2), a, \varphi_1 \land \varphi_2, c_1 \cup c_2, (q_1', q_2')) \in E$

It might appear as if two systems can only advance on an input if both are ready to receive an input, but because of input enabledness this is always the case.

The following theorem lifts all the results from the TIOTSs level to the symbolic representation level:

**Theorem 4.** Let  $A_1$  and  $A_2$  be two specification automata, we have  $[\![A_1]\!]_{\text{sem}} \wedge [\![A_2]\!]_{\text{sem}} = [\![A_1 \wedge A_2]\!]_{\text{sem}}$ .

### 7 Compatibility and Composition

We shall now define structural composition, also called parallel composition, between specifications. We follow the optimistic approach of [34], i.e., two specifications can be composed if there exists at least one environment in which they can work together. Parallel composition is made of three main steps. First, we compute the classical product between timed specifications [42], where components synchronize on common inputs/outputs. The second step is to identify incompatible states in the product, i.e., states in which the two components cannot work together. The last step is to seek for an environment that can avoid such error states, i.e., an environment in which the two components can work together in a safe

way. Before going further, we would like to contrast the structural and logical composition.

The main use case for parallel composition is in fact dual to the one for conjunction. Indeed, as observed in the previous section, conjunction is used to reason about internal properties of an implementation set, so if a local inconsistency arises in conjunction we limit the implementation set to avoid it in implementations. A pruned specification can be given to a designer, who chooses a particular implementation satisfying conjoined requirements. A conjunction is consistent if the output player can avoid inconsistencies, and its main theorem states that its set of implementation coincides with the intersection of implementation sets of the conjuncts.

In contrast, parallel composition is used to reason about external use of two (or more) components. We assume an independent implementation scenario, where the two composed components are implemented by independent designers. The designer of any of the environment components can only assume that the composed implementations will adhere to original specifications being composed. Consequently if an error occurs in parallel composition of the two specifications, the *environment* is the only entity that possibly has the power to avoid it. Thus, following [31], we say that a composition is useful, and composed components are compatible, if the input player has a strategy in the safety game to avoid error states in the composition. The main theorem will state that if an environment is compatible with a useful specification, it is also compatible with any of its refinements, including implementations.

We now propose our formal definition for parallel composition. We consider two specification semantics  $S = (St^S, s_0^S, \Sigma^S, \rightarrow^S)$  and  $T = (St^T, s_0^T, \Sigma^T, \rightarrow^T)$ , and we say that they are composable iff their output alphabets are disjoint  $\Sigma_0^S \cap \Sigma_0^T = \emptyset$ . We say that two specifications are composable if their semantics are composable.

As we did for conjunction, before defining the parallel composition we first introduce a suitable notion of product.

**Definition 12 (Parallel product**  $\otimes$ ). The parallel product of S and T, which roughly corresponds to the one defined on timed input/output automata [42], is the specification  $S \otimes T = (St^S \otimes St^T, (s_0^S, s_0^T), \Sigma^{S \otimes T}, \rightarrow^{S \otimes T})$ , where the alphabet  $\Sigma^{S \otimes T} = \Sigma^S \cup \Sigma^T$  is partitioned in inputs and outputs in the following way:  $\Sigma_i^{S \otimes T} = (\Sigma_i^S \setminus \Sigma_o^T) \cup (\Sigma_i^T \setminus \Sigma_o^S), \Sigma_o^{S \otimes T} = \Sigma_o^S \cup \Sigma_o^T$ .

The transition relation of the product is the largest relation generated by the following rules:

$$\frac{s\overset{\underline{a}}{\longrightarrow}^S s' \qquad a\in \underline{\Sigma}^S\setminus \underline{\Sigma}^T}{(s,t)\overset{\underline{a}}{\longrightarrow}^{S\otimes T}(s',t)} [\text{indep-I}]$$

$$\frac{t\overset{\underline{a}}{\longrightarrow}^T t' \qquad a\in \underline{\Sigma}^T\setminus \underline{\Sigma}^S}{(s,t)\overset{\underline{a}}{\longrightarrow}^{S\otimes T}(s,t')} [\text{indep-r}]$$

$$s\overset{\underline{a}}{\longrightarrow}^S s' \qquad t\overset{\underline{a}}{\longrightarrow}^T t'$$

$$a\in \mathcal{R}_{\geq 0}\cup \underline{\Sigma}_i^{S\otimes T}\cup (\underline{\Sigma}_i^S\cap \underline{\Sigma}_o^T)\cup (\underline{\Sigma}_o^S\cap \underline{\Sigma}_i^S)}{(s,t)\overset{\underline{a}}{\longrightarrow}^{S\otimes T}(s',t')} [\text{sync}]$$

Observe that if we compose two locally consistent specifications using the above product rules, then the resulting product is also locally consistent. Since we normally work with consistent specifications in a development process, immediate errors as defined for conjunction are not applicable to parallel composition. Moreover, unlike [34], our specifications are input-enabled, and there is no way to define an error state in which a component can issue an output that cannot be captured by the other component. However, the absence of "model-related" error states allows us to define more elaborated errors, specified by the designer. Those cannot easily be considered in [34].